Lab 7 - ECE 421L

Tutorial 5 – Design, layout, and simulation of a ring oscillator

In this tutorial we designed, layout, and simulated the operation of a ring oscillator.

One of the goals of this tutorial is to teach how to use arrays and buses

Copy the library, Tutorial_4, into a new library called Tutorial_5.

Ensure,

when you copy, that “update instances” is selected so that the new

library doesn’t reference cells in the other libraries.

As always, put the new library in $HOME/CMOSedu

Create a new schematic cell view called ring_osc.

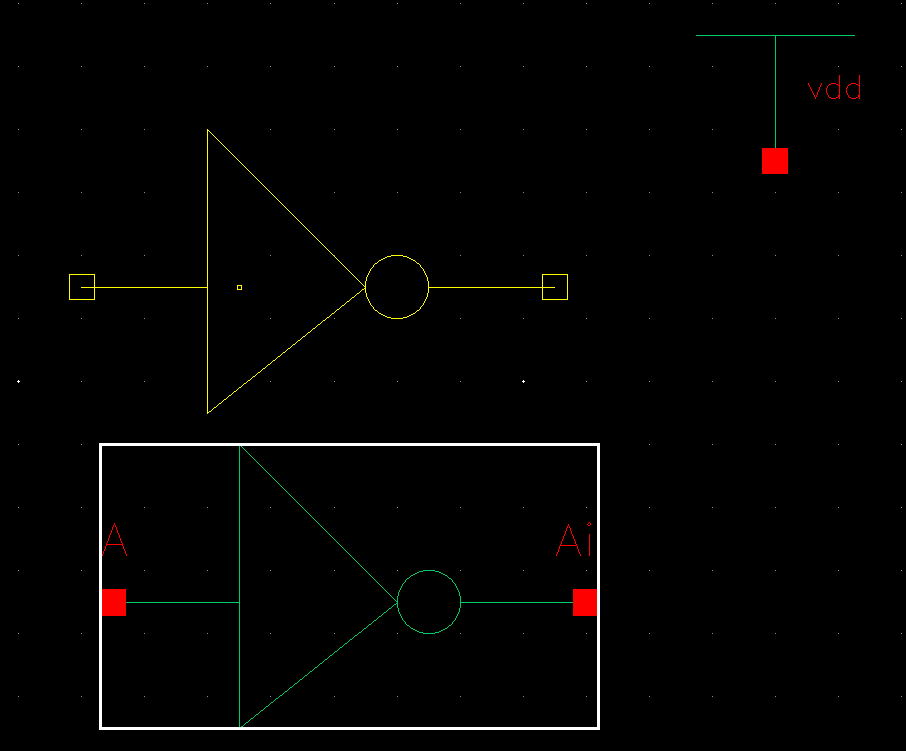

In this cell view place the inverter symbol that was created in tutorial 3.

Also place the vdd supply net symbol, see below.

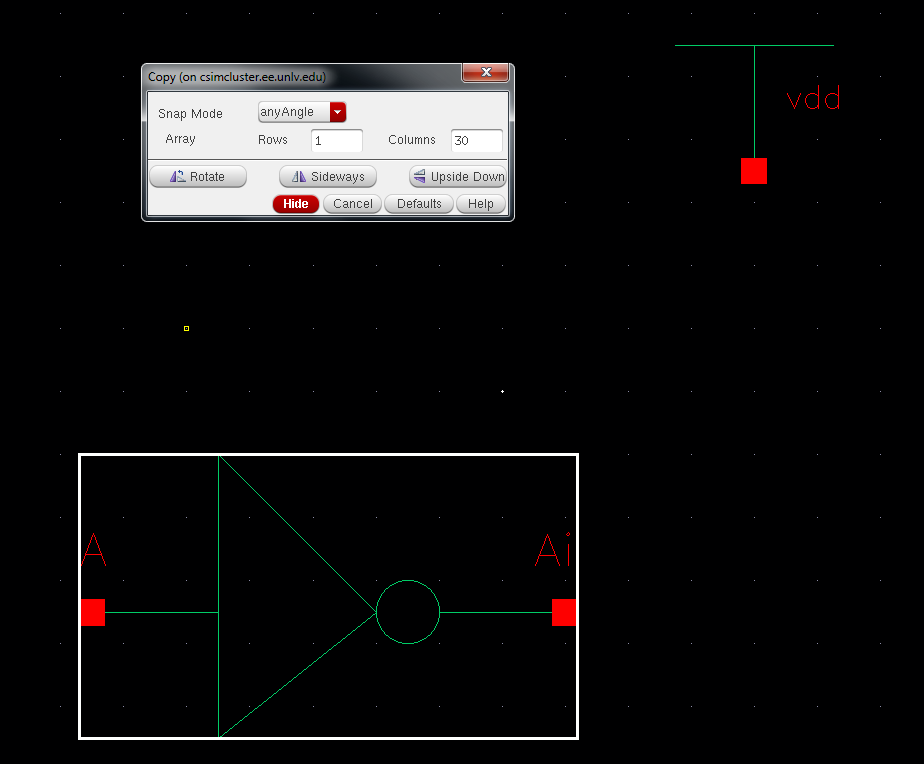

Next press c (for copy) and the inverter (to copy the inverter).

Before placing the copy of the inverter press F3 (special options).

We’ll make a 31 stage ring oscillator so select 30 columns as seen below (to add 30 inverters to the existing one).

Instantiate the (first copied) inverter on the output of the existing inverter.

Repeat for the second copied inverter to get the following.

Note

that if we wanted a wire between the inverters we could have added the

wire on the output of the first inverter and then copy both the

inverter and wire.

Add a wire connecting the output of the last inverter to the input of the first inverter.

Label the wire osc_out as seen below.

Check and Save the schematic.

Now start the ADE.

Set the MOSFET models (Setup -> Model Libraries).

Set the vdd! to 5 V (Setup -> Stimuli), or add a vdc (but not both as discussed in Tutorial_3),

Select the outputs to plot (select osc_out)

Set the analysis to a transient with a length of 200 ns.

Save the State (Cellview) and “Netlist and Run” the simulation.

The output is steady at 2.5V!

In a real circuit noise would kick-start the oscillations.

Let’s do this in the simulation by adding an initial condition.

Select a node voltage of 0 and click on the wire labeled osc_out results in what is seen below (you may have to access the menu again to view this condition).

Save the state of the simulation.

After saving the state and simulating again we get

which is what we expect a ring oscillator to do ;-)

Save the state and close the ADE.

Let’s make the schematic more pleasant to look at.

Delete all of the inverters and the wires except for the first inverter.

Change the inverters name from I0 to I0<1:31> (an array of 31) and display the name (value).

Now use the wide wire (W) to connect to the input and output of the symbol.

Use the wire label (l) to add names as seen below.

The input of I0<1> is osc_out and its output is out<1>

The input of I0<2> is out<1> and its output is out<2>

The input of I0<3> is out<2> and its output is out<3>

The input of I0<31> is out<30> and its output is osc_out

The schematic is exactly the same as the one we drew earlier but clearly nicer to look at (more concise).

Re-simulating this ring oscillator gives the exact same results as seen above.

Save and close all cell views.

Create layout view for the ring oscillator and place two inverter layouts in the cell next to each other.

DRC the layout.

Add rectangles of metal between vdd!, Ai of the first inverter and A of the second inverter, and gnd! as seen below (where e was pressed

and the stop display level was set to 0 to hide the layout of the inverter).

DRC the layout.

Set the stop display level back to 10 and delete the right inverter.

Next select press c (to copy) and select the entire layout.

Press F3, special options, and set the number of columns to 30 (as was done above).

Place the inverters end-to-end as seen below.

DRC the layout

Next add m2_m1 vias at the left and right of the layout as seen below.

Next add a rectangle on metal2 connecting these two vias.

Below is the result where the stop display level is set to 0.

DRC the layout.

Add pins for gnd!, vdd! (both have a direction of inputOutput), and osc_out (set the direction to output).

Put vdd! and gnd! pins on the metal1 layer and osc_out on the metal2 layer.

DRC the layout.

Run extraction on the layout.

Save and close the layout view.

Open the extracted view and run an LVS.

The LVS fails.

Why? Looking at the information in si.out file above we see that terminals are not matched.

We used a pin for osc_out in the layout but not in the schematic.

Let’s add a pin to the schematic (and then Check and Save).

Make sure that the pin’s direction is output (so it matches the layout).

Also note that the wire connection between the pin and the bus (wide wire) must be labeled as seen.

Check and Save the schematic.

Close the schematic and open the ring_oscillator’s extracted view.

Run the LVS to see that the layout and schematic match.

It’s useful to compare the simulation results of both a layout and a schematic.

Delete the vdd symbol in the ring oscillator schematic.

Create a symbol for the ring oscillator.

Save and close all cell views.

Create a new schematic cell view call sim_ring_osc.

Please the ring_osc and vdd symbols in this cell.

Add a wire to the output of the ring_osc symbol labeled osc_out as seen below.

Check and Save the schematic.

We get two warnings (floating net/wire)

Use Check -> Find Markers then press ignore twice and close the window.

Check and Save again to verify no warnings/errors.

Launch the ADE and enter the models, stimuli, outputs to plot, etc. as we did above.

Don’t forget to set the osc_out to have an initial condition of 0.

When finished save the state.

Netlist and Run (hit the green button) to see the following.

Let’s simulate the extracted view.

As before use Setup -> Environment to enter extracted before schematic.

To get the following results.

Just to verify that we are actually using the extracted cell view use Simulations -> Netlist -> Display

Save and close everything.

Remember

that if you save the simulation state with extracted before schematic

(above) changes to the schematic won’t appear in the simulation results.

Rather Spectre will continue to simulate the extracted view. To fix this simply remove extracted above.

Save and close everything. This concludes Tutorial 4.

In this lab we made an equivalent, more concise, schematic by instantiating an inverter and naming the inverter using an arrayed name (I0<3:0> see image below).

Connect a wide-wire (bus) as seen below and connect it to input and output pins.

Name the pins as seen below.

This schematic equivalent to the one seen above but obviously more concise.

Create a symbol for the schematic.

Using this symbol we create a simulation schematic below.

All four inverters' inputs are tied together to an input pulse source.

The out<0> is not connected to a load while out<3> is connected to a 100fF load.

The out<1> is connected to a 1 pF load while out<2> is connected to a 500 fF load.

Simulating this schematic results in the following.

Note that the capacitive load influences the delay and rise/fall times. The bigger the capacitor is, the longer that delay time will be.

Next, we create bit operations for several different kinds of gates. We then create a symbol for each.

NAND Schematic

NAND Symbol

NOR Schematic

NOR Symbol

AND Schematic

AND Symbol

inverter Schematic

inverter Symbol

OR Schematic

OR Symbol

Next, we create 8-bit input/output array equivalents for several different kinds of gates. We then create a symbol for each. And finally, design a simulation circuit and simulate that gates that we've created.

8 NAND Schematic

8 NAND Symbol

8 NAND Simulation Schematic

8 NAND Simulation Waveforms

8 NOR Schematic

8 NOR Symbol

8 NOR Simulation Schematic

8 NOR Simulation Waveforms

8 AND Schematic

8 AND Symbol

8 AND Simulation Schematic

8 AND Simulation Waveforms

8 inverter Schematic

8 inverter Symbol

8 inverter Simulation Schematic

8 inverter Simulation Waveforms

8 OR Schematic

8 OR Simulation Schematic

8 OR Simulation Waveforms

Note that in the results of simulation of all the gates, we have verified that the operations are correct. Also, we have verified that the bigger the capcitive load will be, the longer the delay will be and cause undesirable behavior in the operation of the gates.

Next examine the following schematic.

This is the schematic of a 2-to-1 DEMUX/MUX (and the symbol).

We simulated the operation of the DEMUX/MUX by connecting two different inputs A and B and by switching the select line

Note that the reuslts of the simulation showed the output of the multiplexer switching from A to B as the select line switches from HI to LOW

We can also use the multiplexer as a demultiplexer by swtiching the direction of its input and output pins. We have created a symbol for the DEMUX seen below.

We verify that the demultiplexer is working by the simulation circuit below. Note that input Z is being redirected into output A and B by the Select line

Resulting waveform from the simulation shows that the demultiplexer is operating as it should

Next we extend the mux/demux into an 8-bit wide word 2-to-1 DEMUX/MUX schematic and symbol.

Note that we included

an inverter in your design so the cell only needs one select input, S

(the complement, Si, is generated using an inverter).

From

the simulation below it can be seen that the multiplxer is operating as

it should. Notice inputs A and B are switched at the middle of the

waveform.

Finally, we draft the schematic of the full-adder seen in Fig. 12.20 using 6u/0.6u devices (both PMOS and NMOS).

We created an adder symbol for this circuit (see the symbol used in lab6).

We then extend the bit FA into an 8-bit adder schematic and symbol.

For

how to label the bus so the carry out of one full-adder goes to the

carry in of another full-adder we reviewed the ring oscillator schematic

discussed in Cadence Tutorial 5.

Finally we simulate the operation of the 8-bit adder by setting the input vector waveform as its inputs. In order to do this, we have followed the document seen here.

Results of the simulation below have verified that the 8bit Full Adder is working as expected

We then lay out this 8-bit adder cell (*note* that this is the only layout required in this lab).

but first we layout our single bit full adderThis ends lab 7. We've covered all of the basic building blocks used in an ALU.

Finally, we backed up our design lab7vi.zip directory and other files for future study.