Shadden Abdalla

Speaking at the Governor’s Signing of a bill to fund a new engineering building at UNLV.

Contact: shadden.abdalla@unlv.edu

Welcome to my CMOSedu page!

I was born and raised in Las Vegas and am currently a third year undergraduate student pursuing my Bachelor’s degree in Electrical Engineering at the University of Nevada Las Vegas Honors College. I am also the President of UNLV’s IEEE Student Chapter.

Join UNLV IEEE: https://unlv.campuslabs.com/engage/organization/IEEE

I enjoy building circuits on LTSpice, PCB design, wirebonding, soldering, programming FPGA’s in Quartus using schematics and HDL languages, working on and analyzing circuits, and coding in C++. I also find great interest in circuit design. More than anything, I love learning, and I strive to learn more about electrical and computer engineering every day.

Currently (Summer '18): I am learning chip design using Cadence Virtuoso!

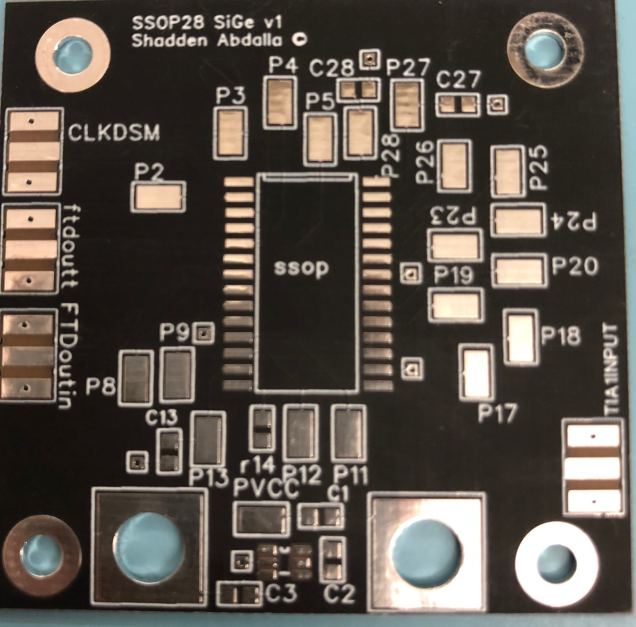

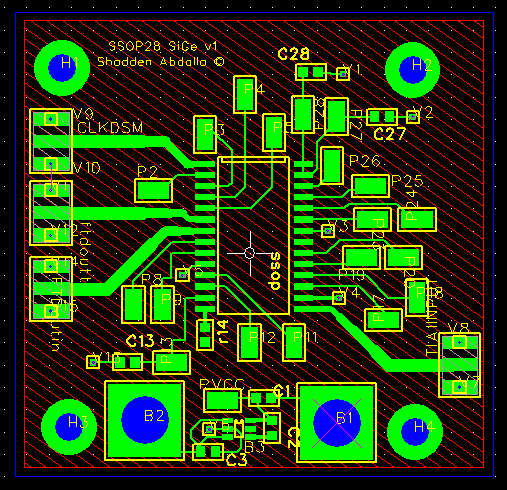

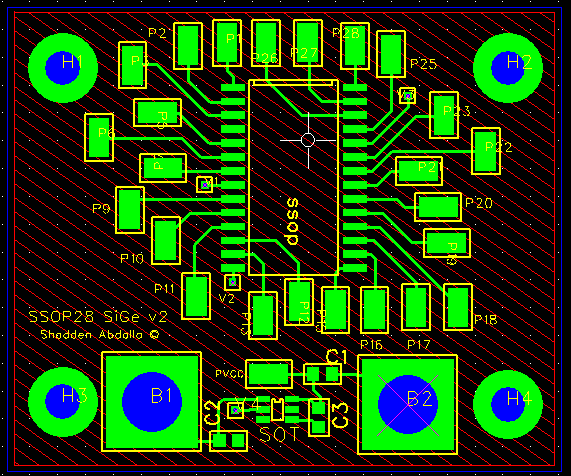

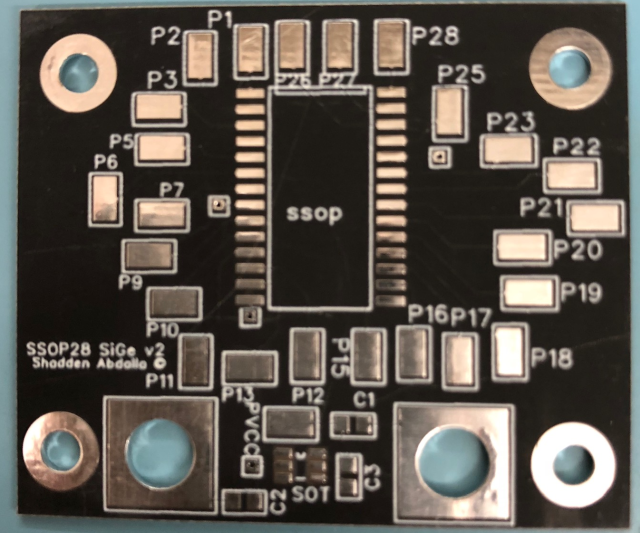

Here are some of my PCB designs and finished PCB boards, used to test chips we make in the lab.

(listed from oldest to newest):

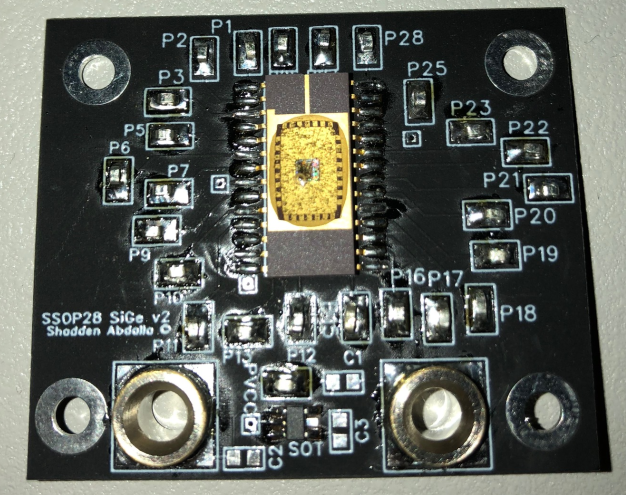

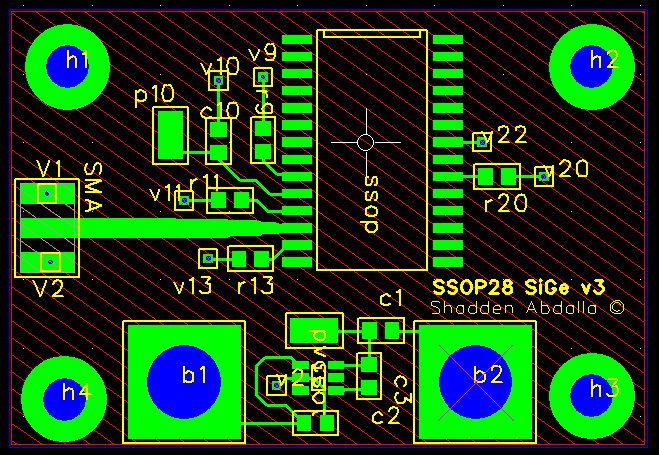

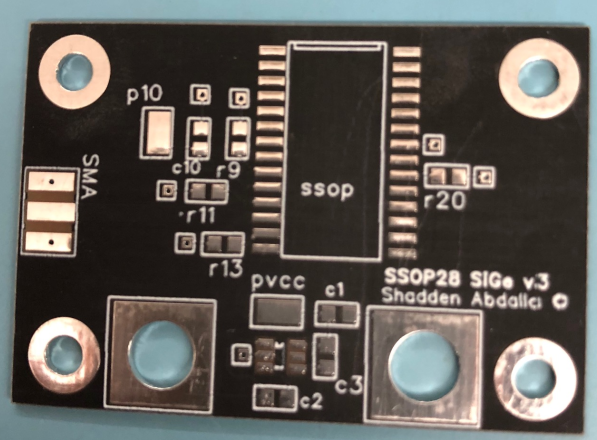

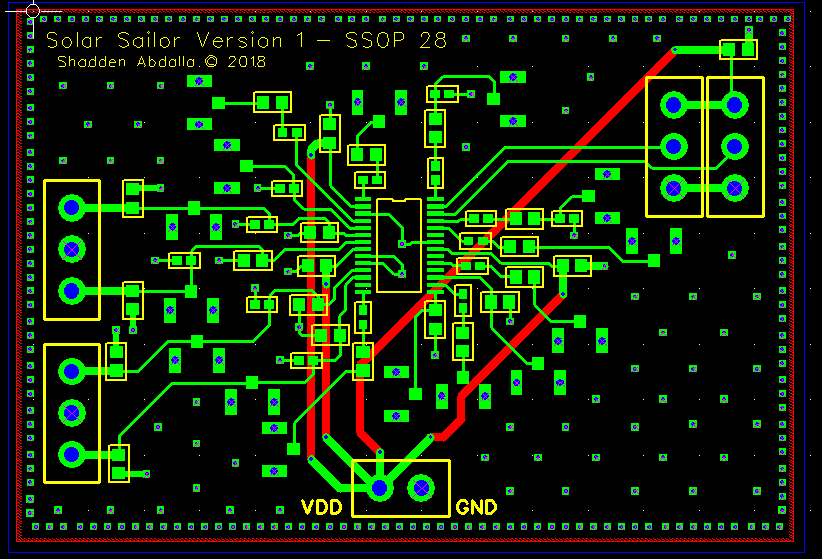

1. For testing the Starboy Chip – SiGe on a SSOP 28 package, (AMS S35 / 2.5 x 2.5 mm chip) :

Version 1:

Version 2:

Version 3:

Below is the design, original PCB and soldered PCB.

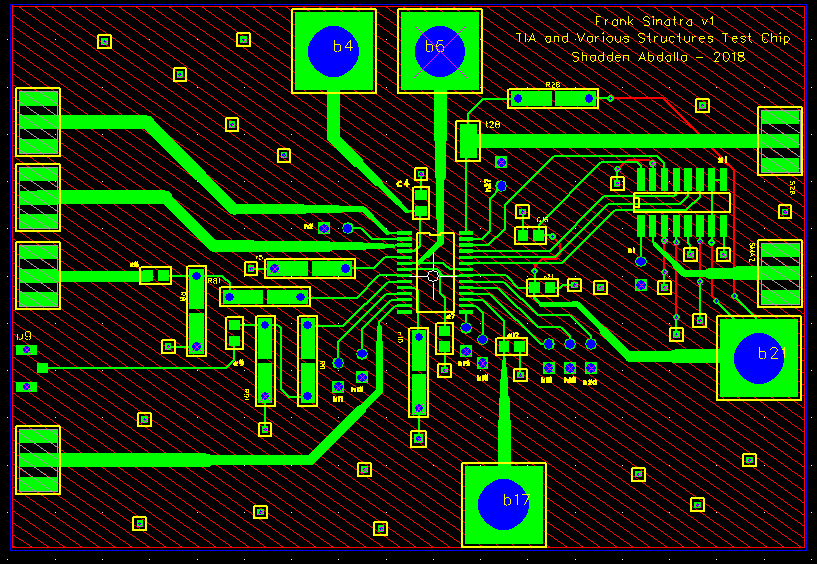

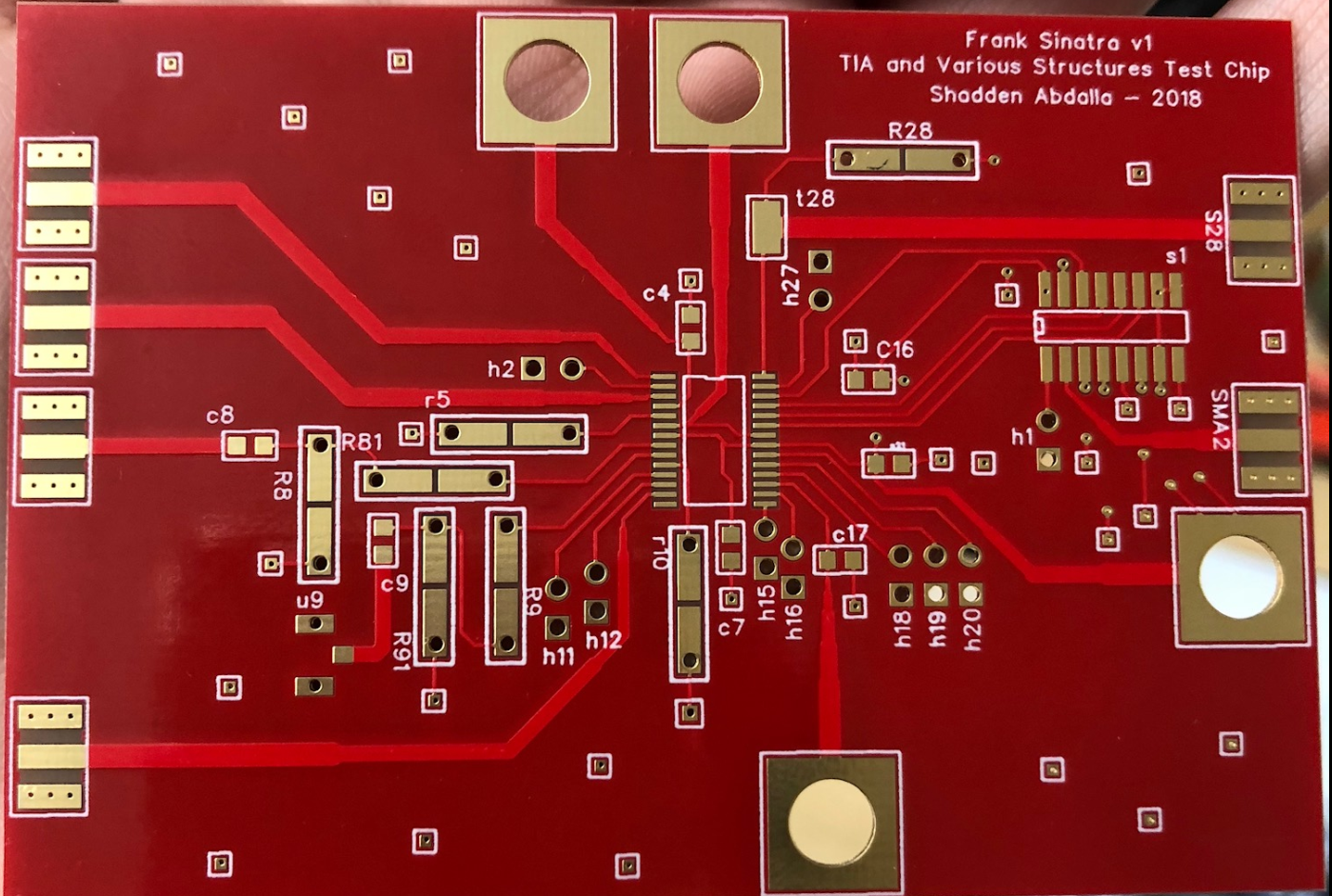

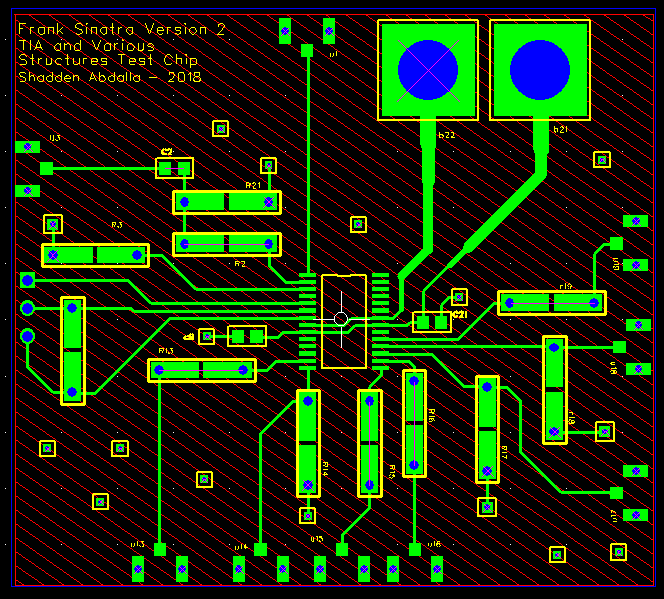

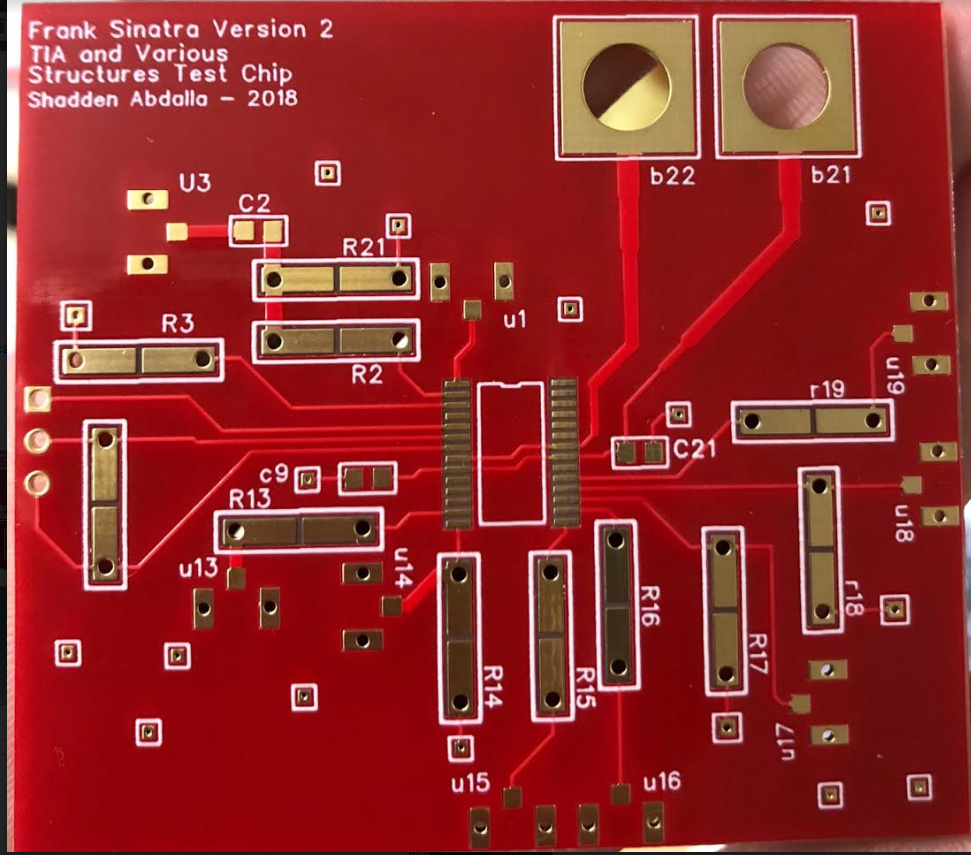

For the “Frank Sinatra” TIA test chip with various test structures (AMS 0.35 SiGe S35 process)

Version 1:

Version 2:

Version

1: Version 2:

Version

1: Version 2:

Return to Dr. Baker's Students