High Speed Fast Transient Digitizer (HSFTD)

Eric Monahan April 9, 2018

Project Members:

R. Jacob Baker (rjacobbaker@gmail.com)

James Mellott (mellott@unlv.nevada.edu)

Eric Monahan (emonahan9999@gmail.com)

Angsuman Roy (angsumanroy@gmail.com)

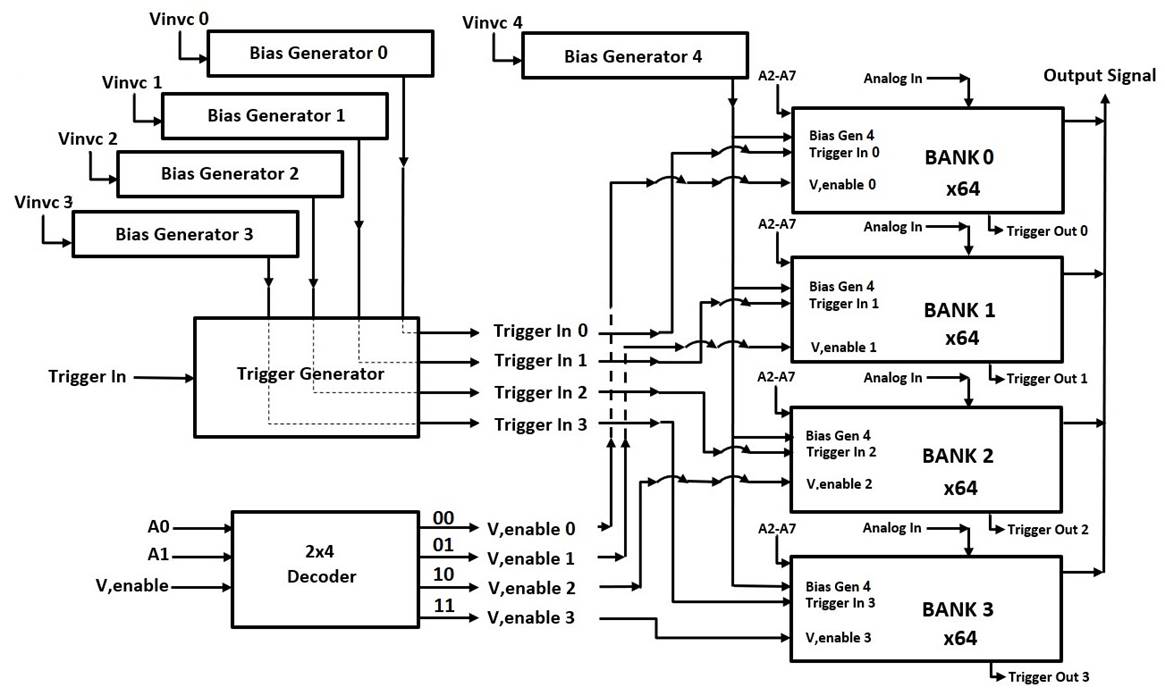

The High Speed Fast Transient Digitizer

(HSFTD) is a test chip designed with Cadence Virtuoso

and Spectre using the ams

AG 0.35 µm SiGe-BiCMOS Process Design Kit (PDK). The design was sent for fabrication on April 9, 2018.

The HSFTD is designed

to sample in time and at a fast rate a high-speed analog or transient input

signal. The reconstructed, captured signal can then be readout at a much slower

rate, for example, around three orders of magnitude. This approach eliminates

quantization error in the captured signal and allows slow, low cost,

analog-to-digital converters to be used such as those found in

microcontrollers. The design uses four interleaved sampling banks, each

containing 64 unit cells acting as sequentially triggered capture and hold

stages with a typical simulated maximum sampling frequency of 17.1 GHz. The

capture stages are initiated via four trigger signals separated by a time delay

equal to one-fourth of a unit cell propagation delay. The sampling rate can

also be adjusted by tuning a bias generator's external control voltage or

changing the value of an off-chip bias resistor. The effective sampling rate of

17.1 GHz results in data captured at 58 ps per unit

cell with a minimum capture window of 15 ns for all 256 unit cells. The typical

analog input voltage range is from 0 V to 2.2 V with an output range from 2 V

to 4.8 V. At room temperature, the RMS value of the thermal noise in the design

is limited by an 85.75 fF hold capacitor with kT/C noise resulting in a thermal noise floor of 220 µV,RMS. The amount of degradation of the unit cell hold

capacitor's voltage over time due to leakage is 2.5 mV/100 µs. All values were

determined via simulations.

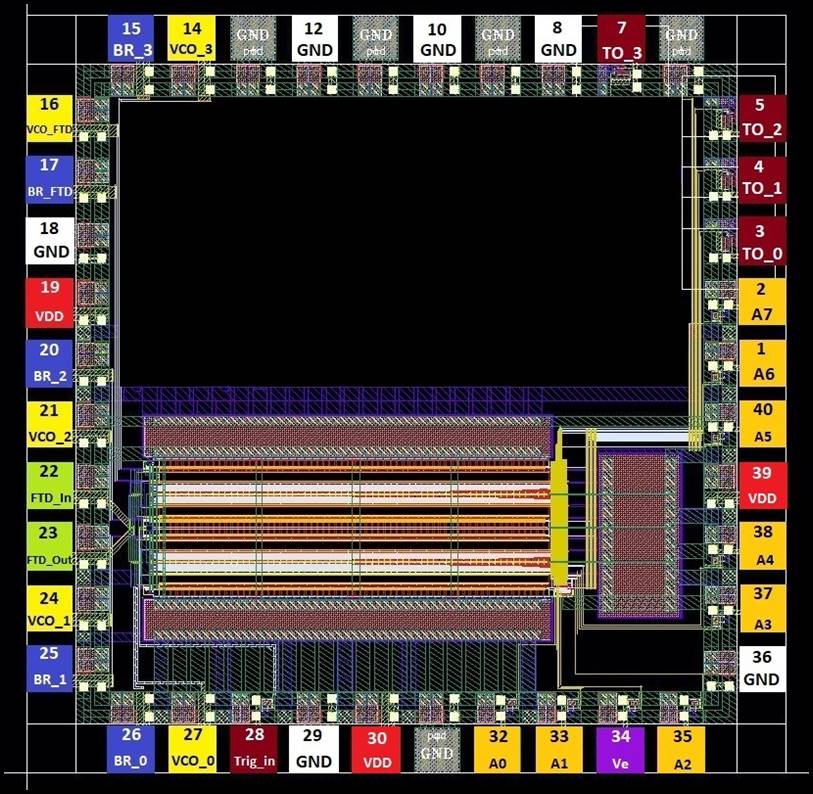

IC PADFRAME AND KEY

HSFTD Bonding Diagram for QFP-44

HSFTD PIN TABLE

HSFTD Block Diagram

A detailed explanation of the

HSFTD design and operation can be found in my thesis, High

Speed Fast Transient Digitizer Design and Simulation.