Lab 4 - ECE 421L

Lab Description

The purpose of this lab is to analyze the I-V curves of the MOSFET devices. This includes the NMOS and PMOS transistors.Prelab

To prepare for the lab, we finished tutorial 2 found here on the CMOSedu website.

Lab

Simulating the IV Operation:

During the first part of the lab, we simulated the I-V curves of the MOSFETs.

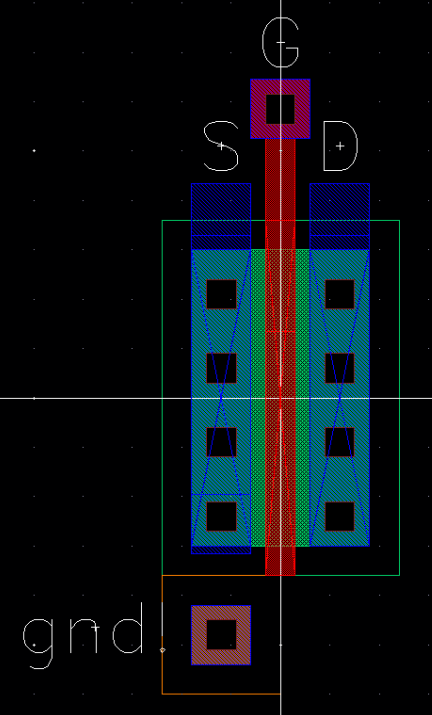

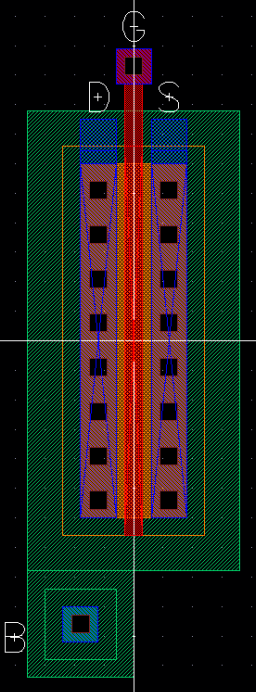

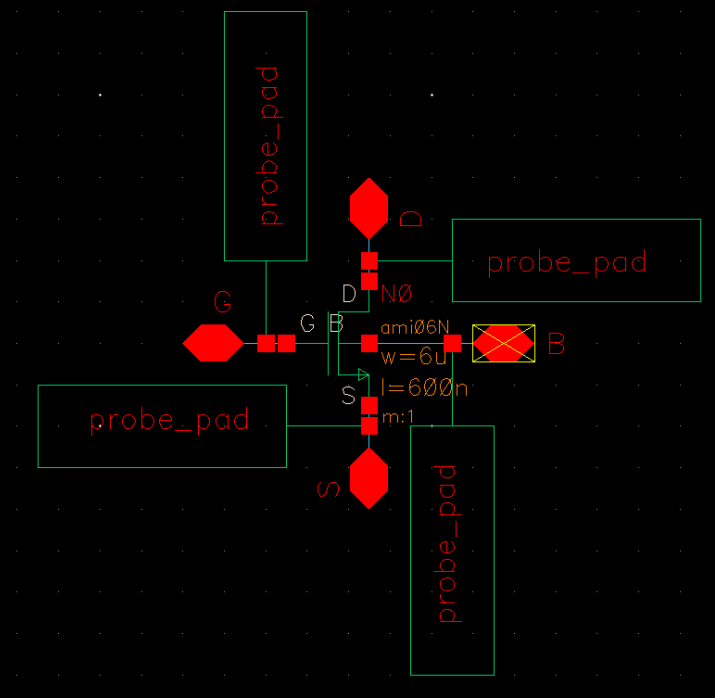

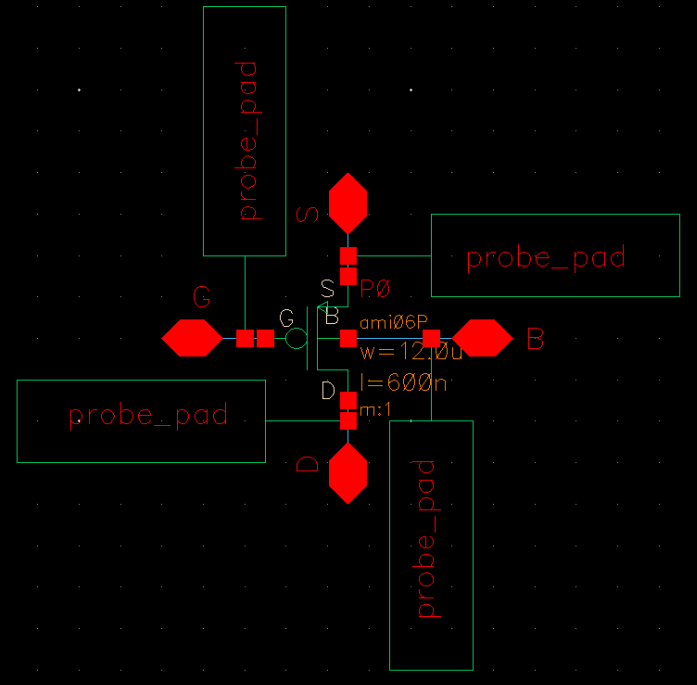

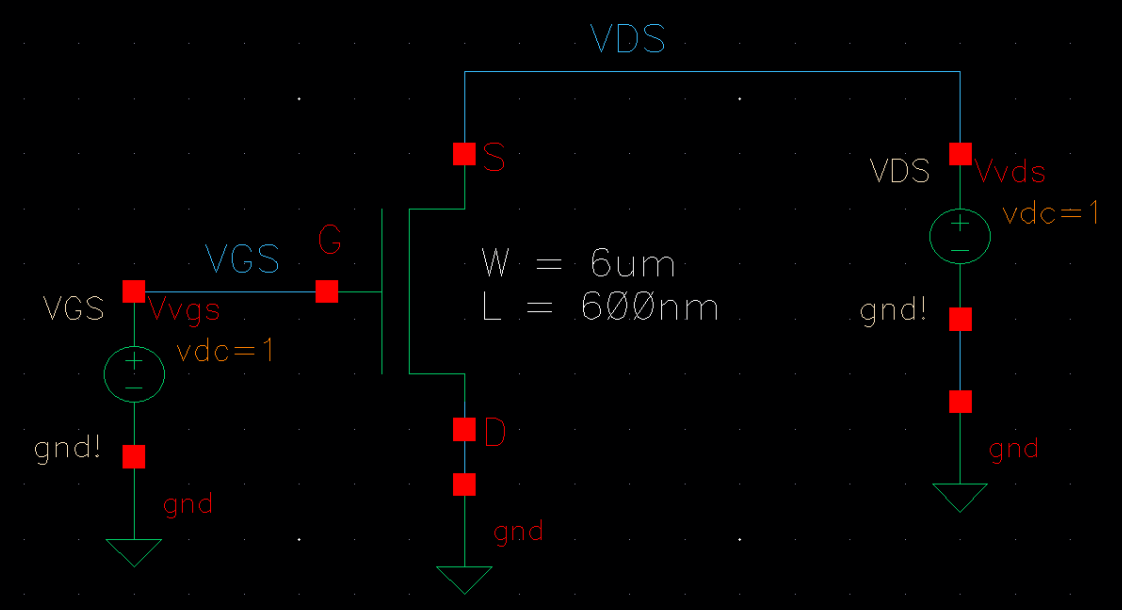

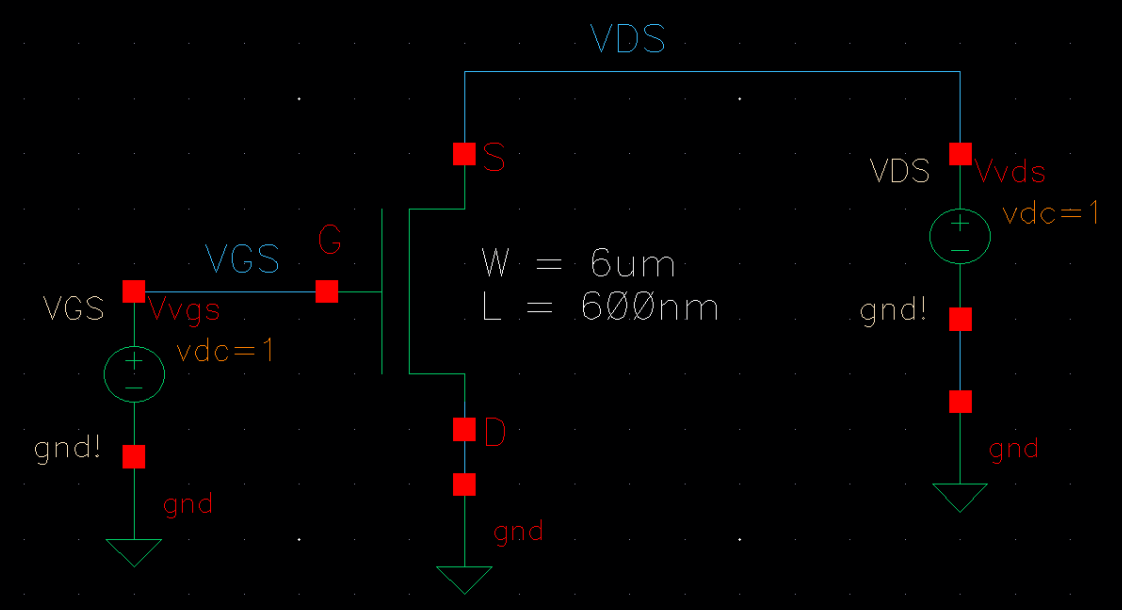

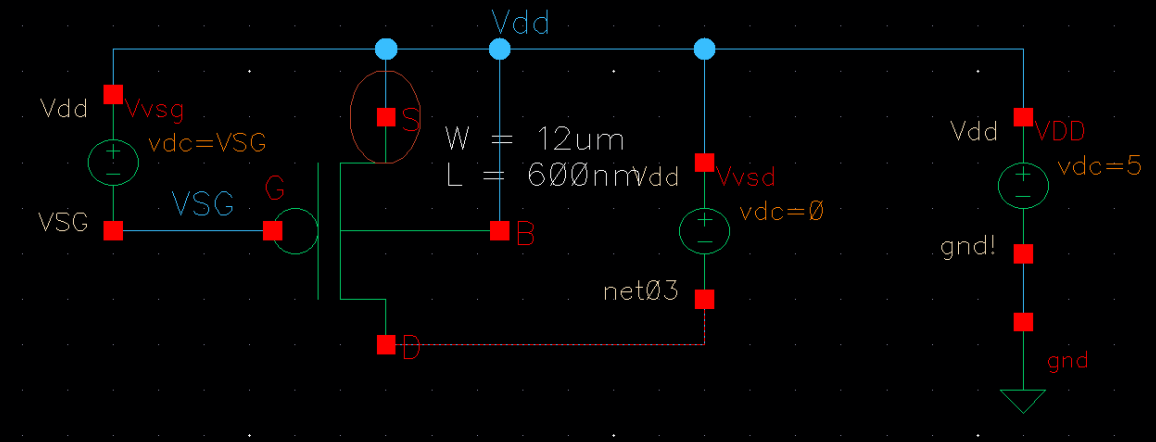

We used the nmos and pmos available under the NCSU_Analog_Parts library. The NMOS used for simulation

has a width of 6µm and a length of 600nm. The PMOS used for simulation has a width of 12µm and a length

of 600nm.

To simulate our transistors, a circuit is built to set the drain-to-source/source-to-drain voltages and the

gate-to-source/source-to-gate voltages. The circuit is made as followed:

For NMOS:

For PMOS:

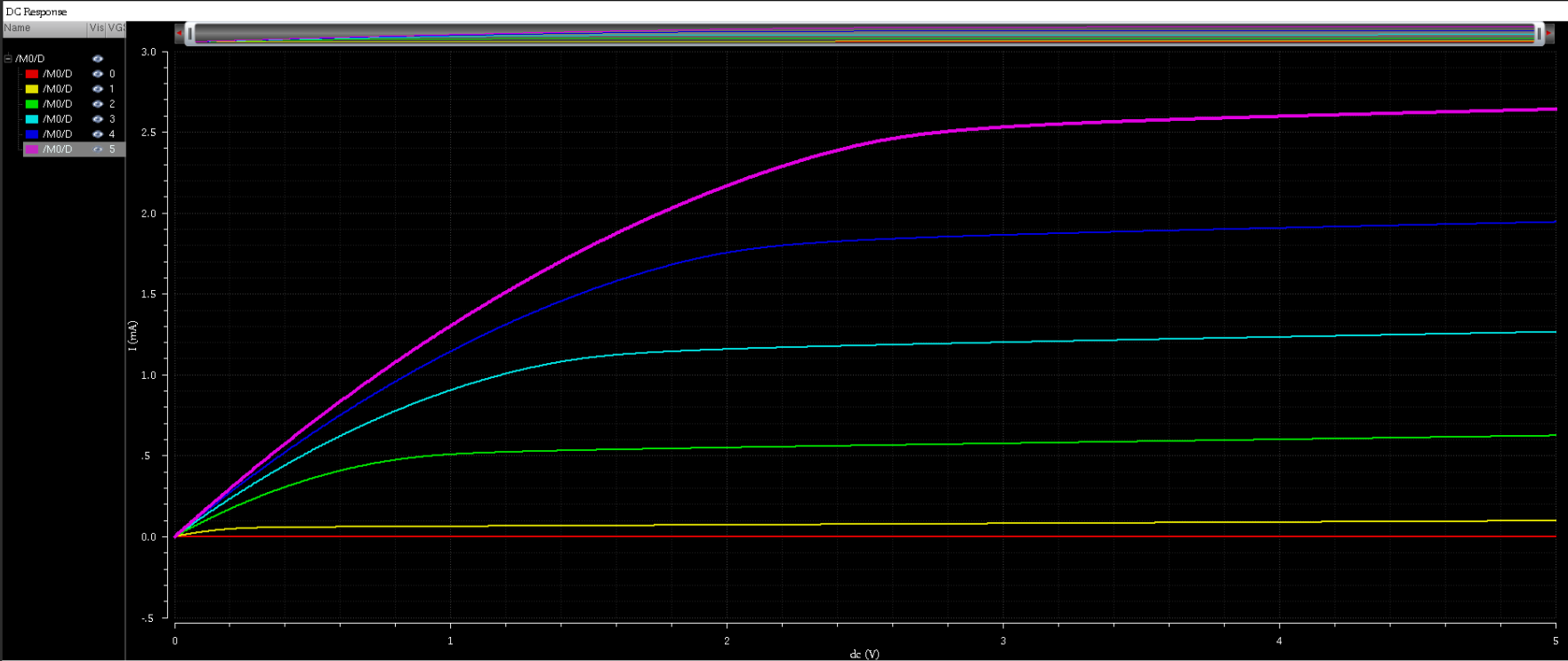

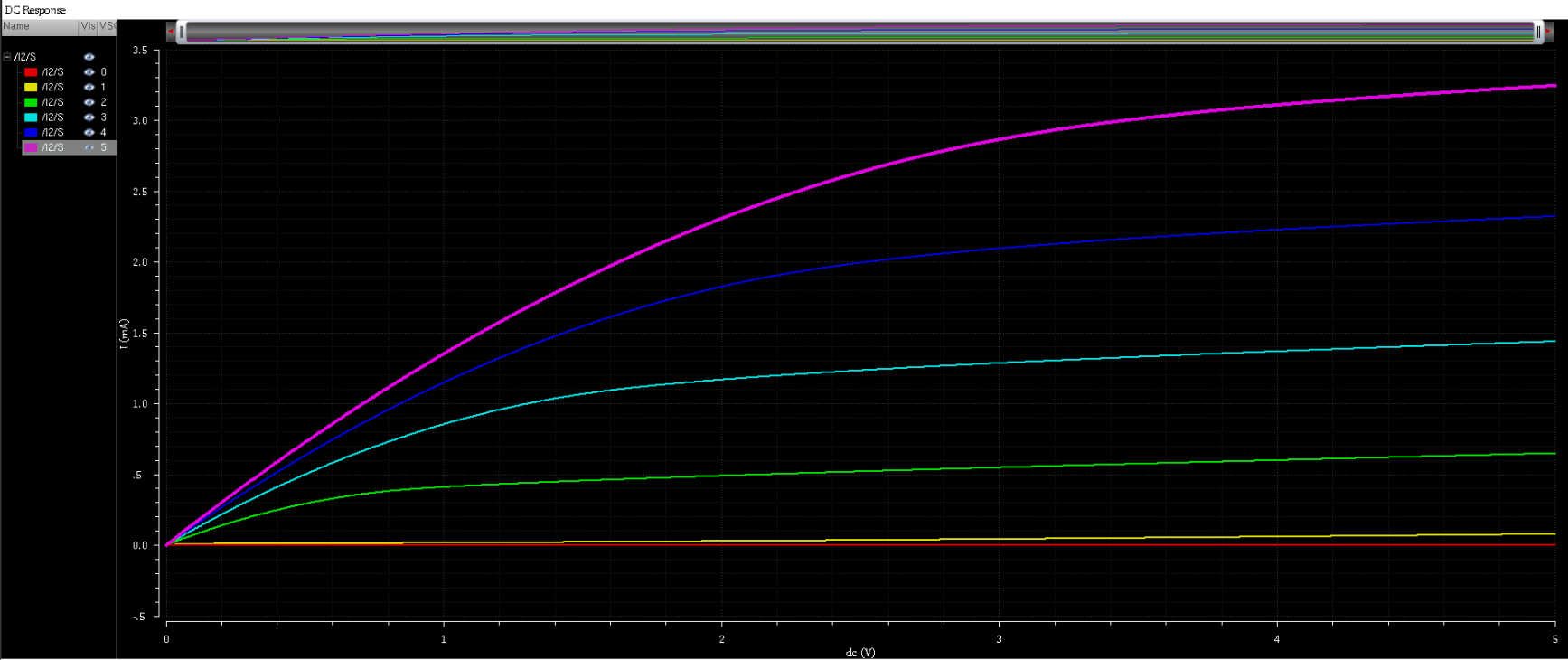

Now we simulate the drain-to-source current for the NMOS and the source-to-drain current for the PMOS.

We first start by simulating the currents by sweeping Vds for the NMOS and Vsd for the PMOS, effectively graphing

Ids/Isd versus Vds/Vsd. This is done from 0V to 5V in 1mV increments, and is done for six different Vgs/Vsg values

(0V, 1V, 2V, 3V, 4V, 5V, & 6V). The results are shown below.

For NMOS:

For PMOS:

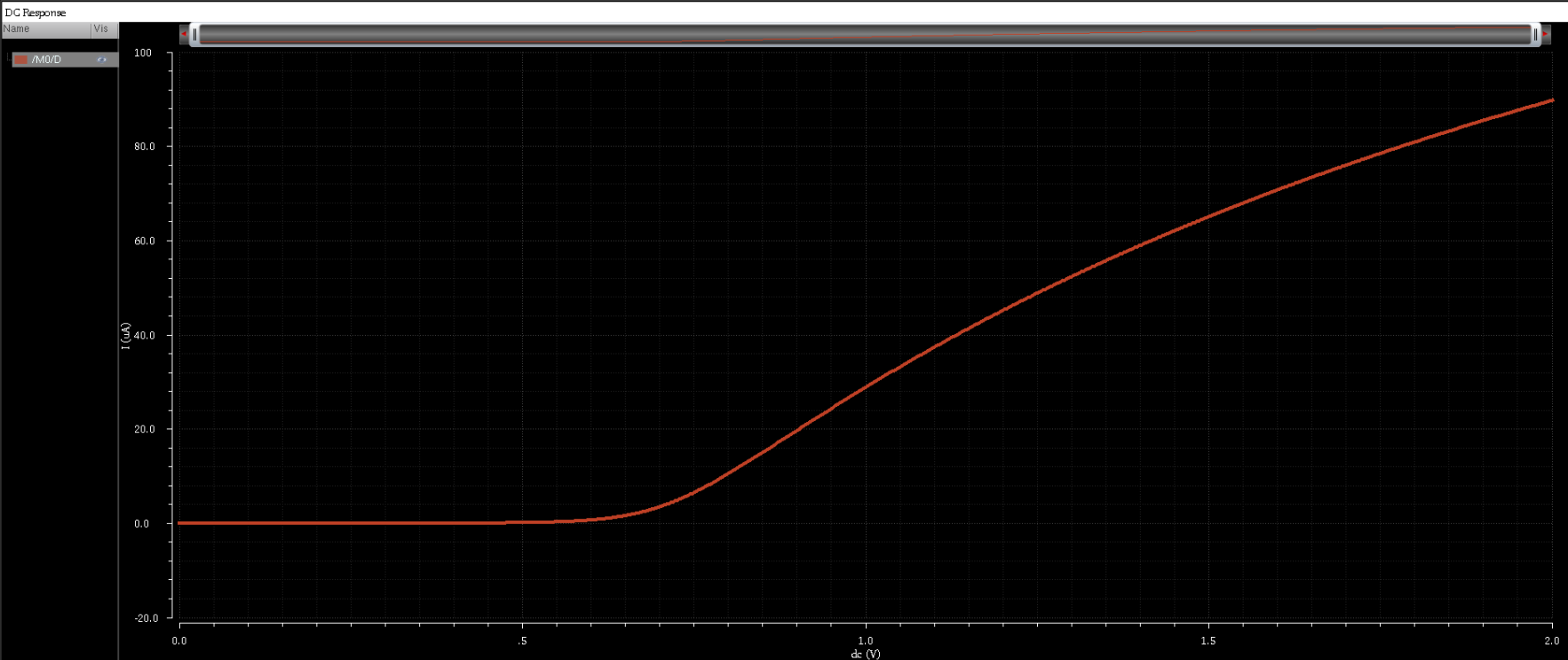

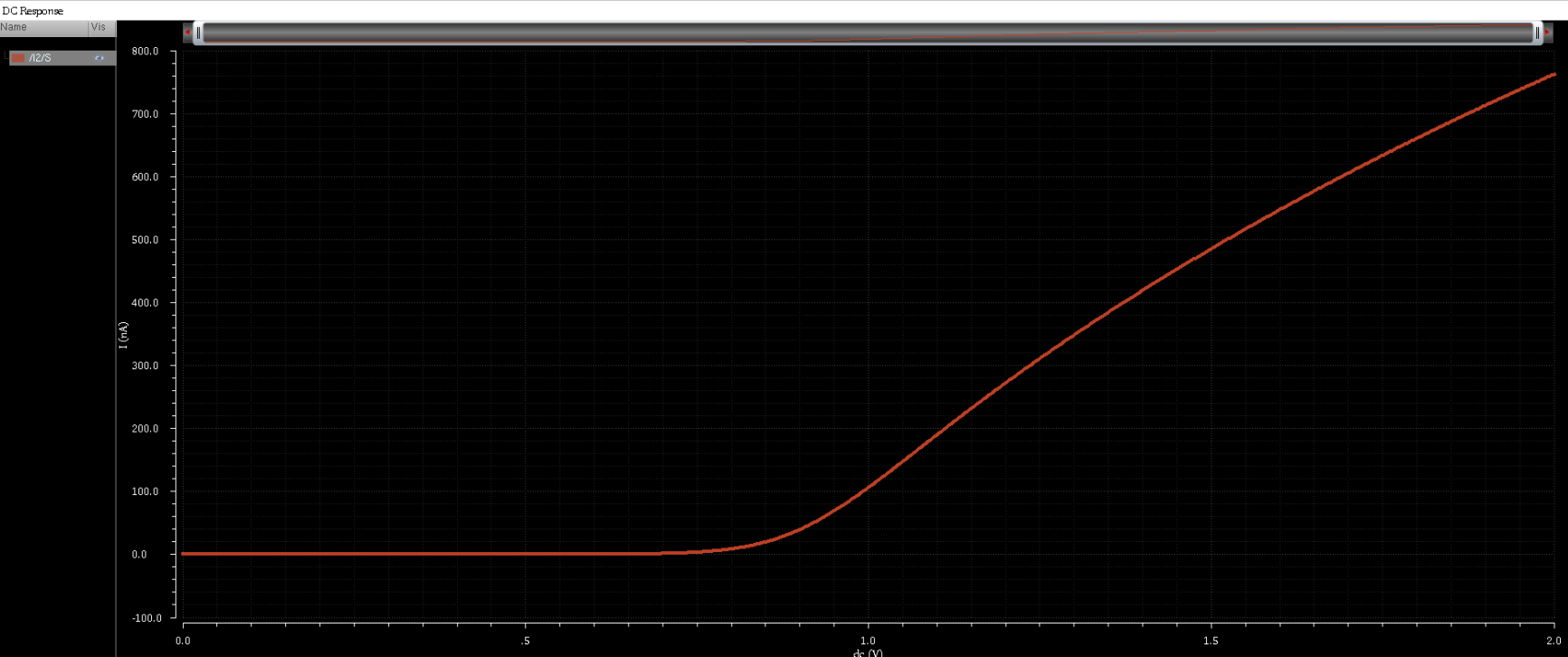

Now we simulate the currents while sweeping Vgs/Vsg from 0V to 5V in 1mV increments. This time, the voltages Vds/Vsd is

held at a constant 100mV.

For NMOS:

For PMOS:

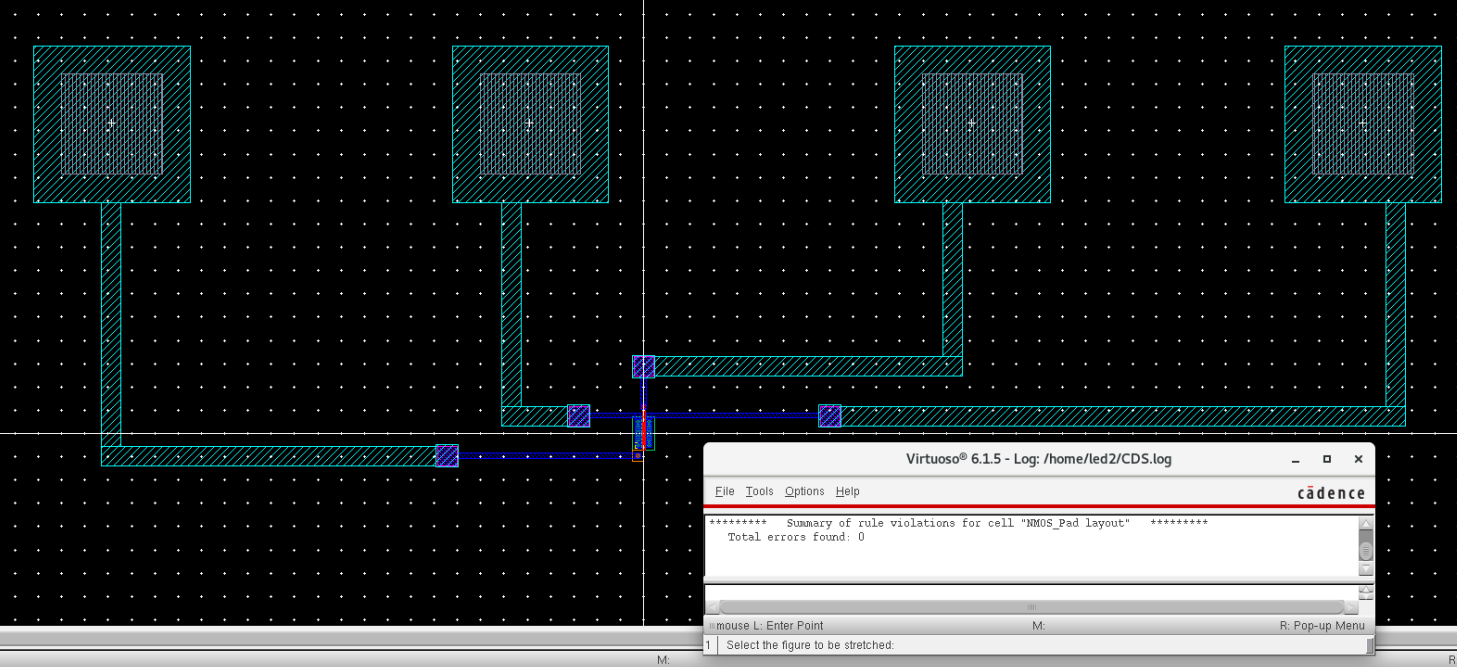

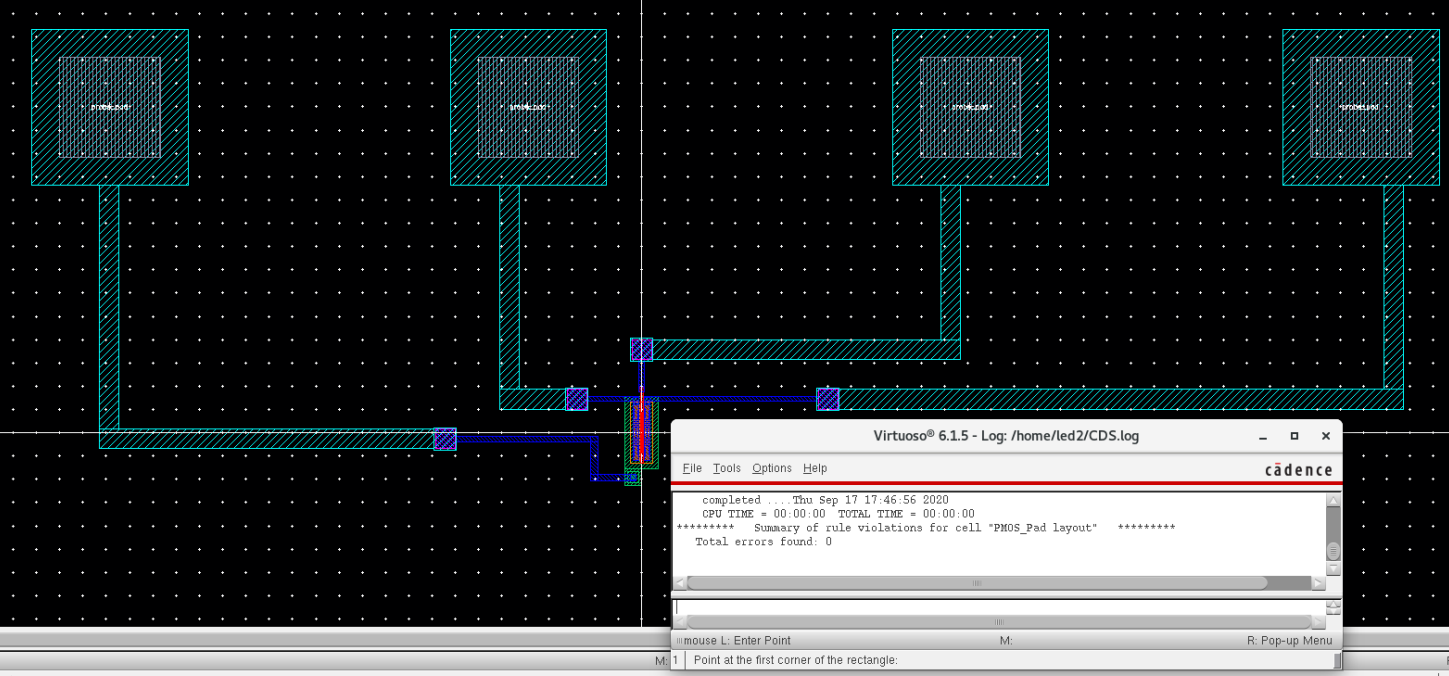

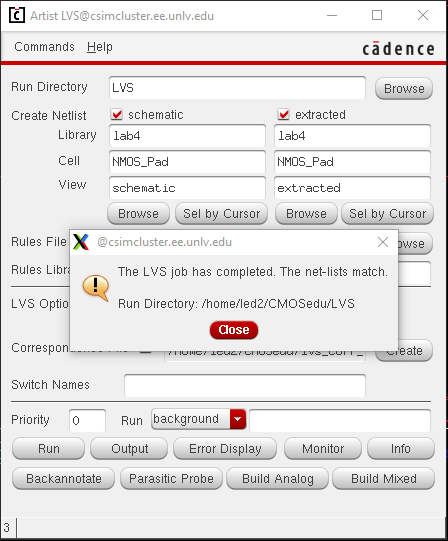

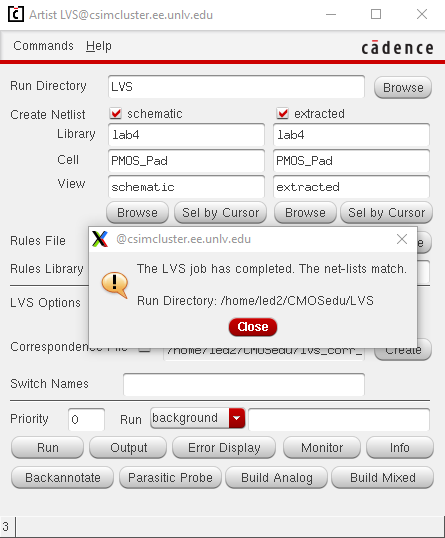

Layout of MOSFET for testing:

Now we create a layout for the NMOS and PMOS. Our goal is to connect these layouts to test pads in order to test the

transistors.