Lab Project - EE 421L

Authored

by Martin Jaime,

email: jaimem5 at the UNLV students domain

Date November 30, 2016

Objective:

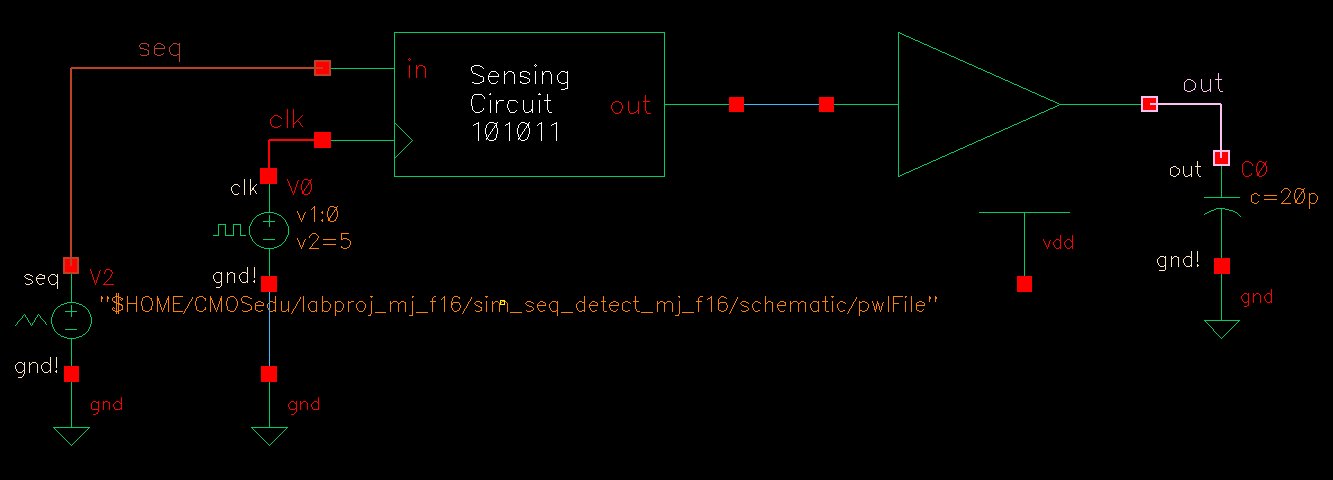

- Design a circuit that takes a serial input and detects (outputs a high logic signal called detect) the sequence 101011

- The inputs to your circuit are clk and in

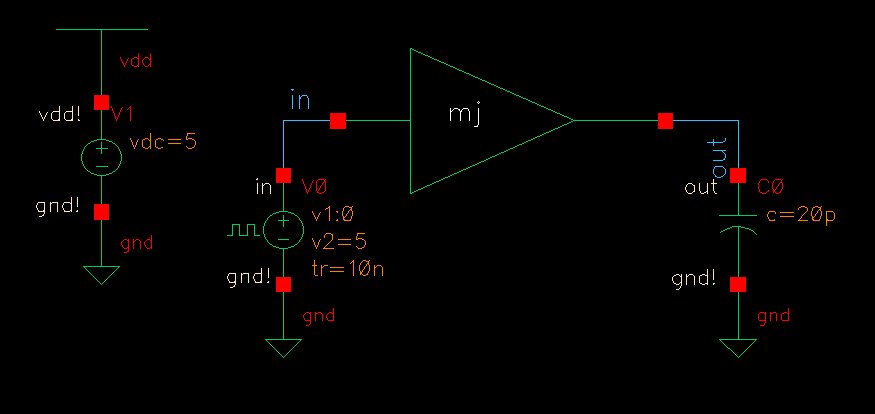

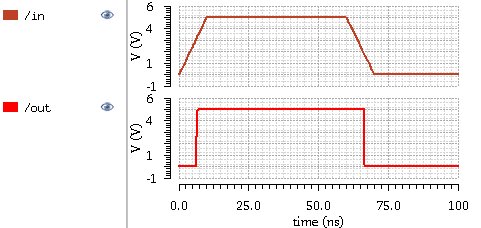

- Make sure that the output of your design, detect, is buffered before connecting to a pad

Project Lab Report

Conceptually,

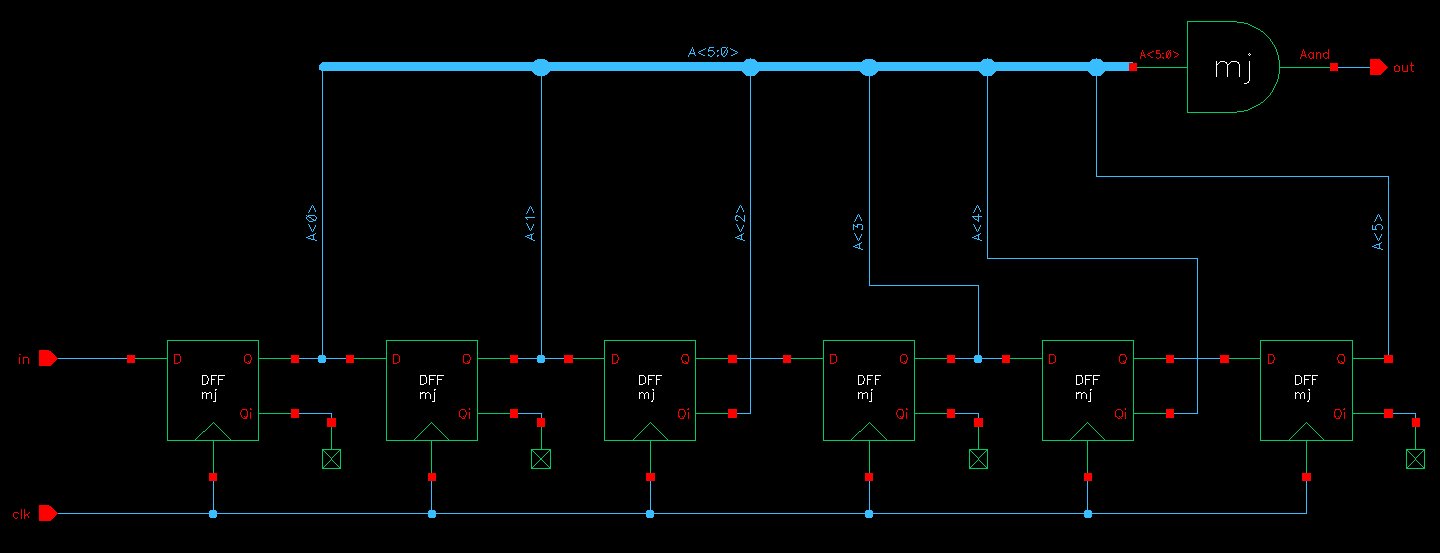

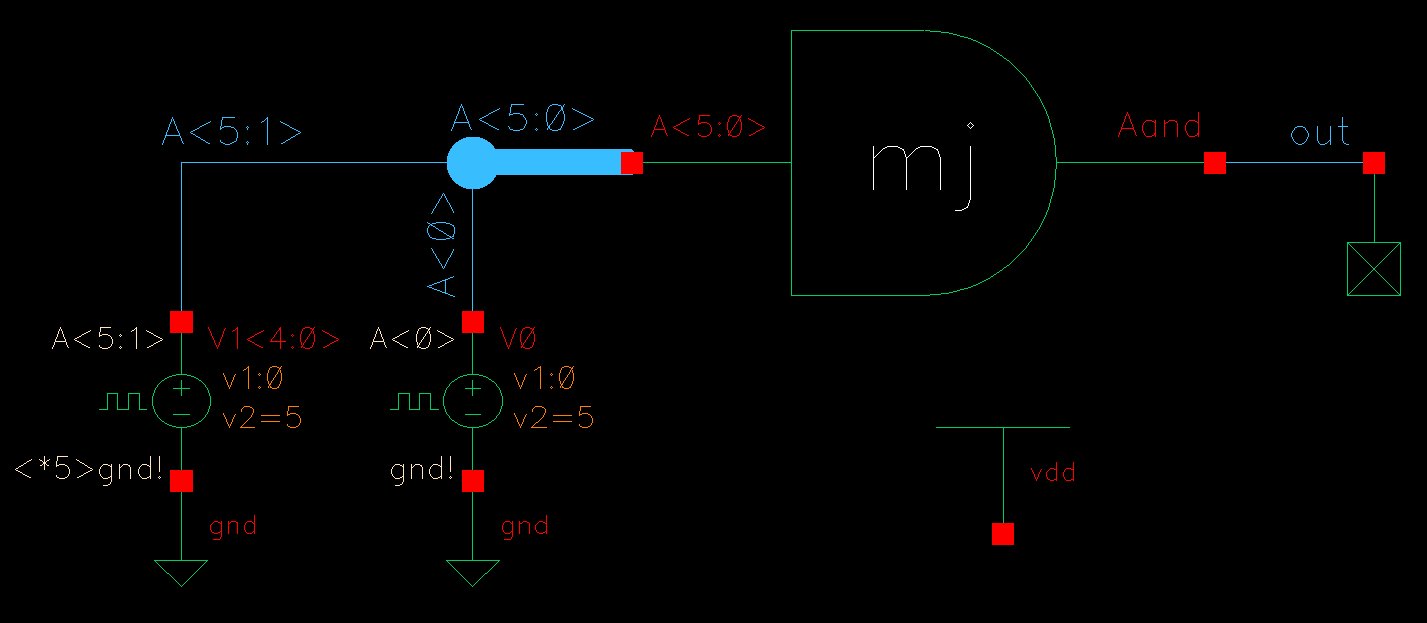

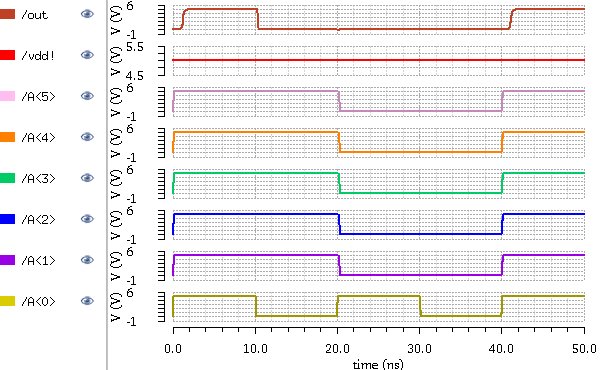

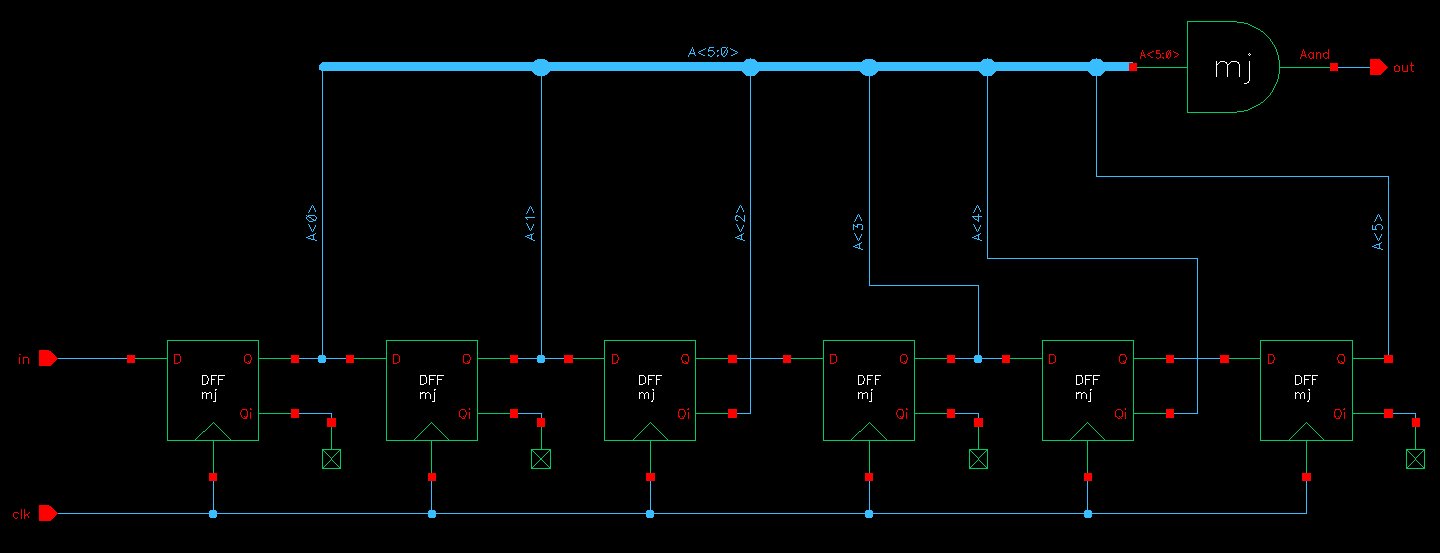

the detector circuit consists of a clocked 6-bit shift register that

will serially read a sequence, and compare it to the expected value.

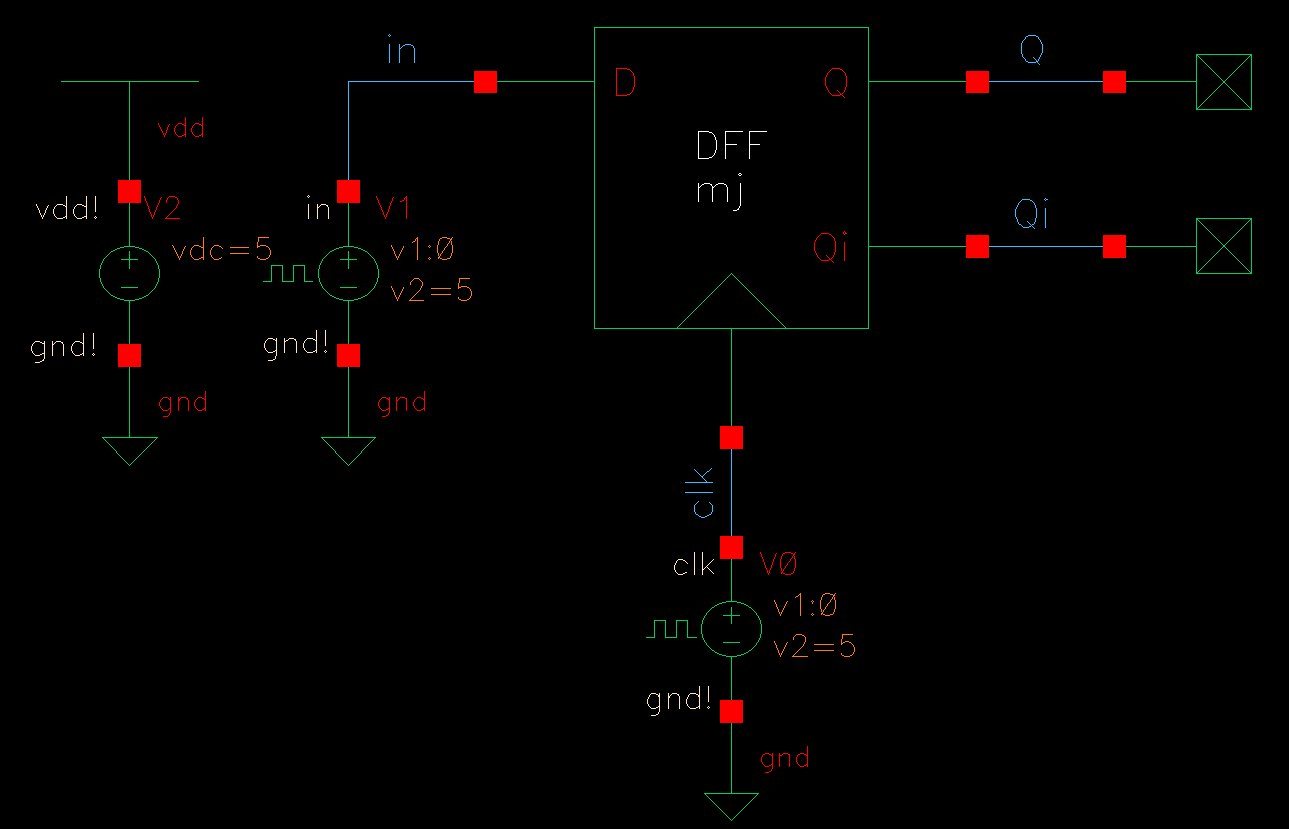

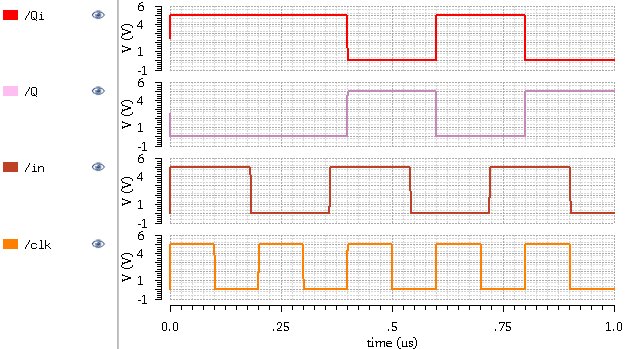

Since the register records the data in D flip-flops, we can check the

sequence by

detect = A*B'*C*D'*E*F

Therefore, the output of the register should be ANDed together into a

six input AND gate. Fortunately, D flip-flops have complementary

outputs, so no additional inverters are required. The output of the AND

gate will be a logic '1' when the shift register contains the logic

value '101011'. The following is the schematic used for the sequence

detector illustrated with logic gates.

Schematic of sequence detector.

- Modules:

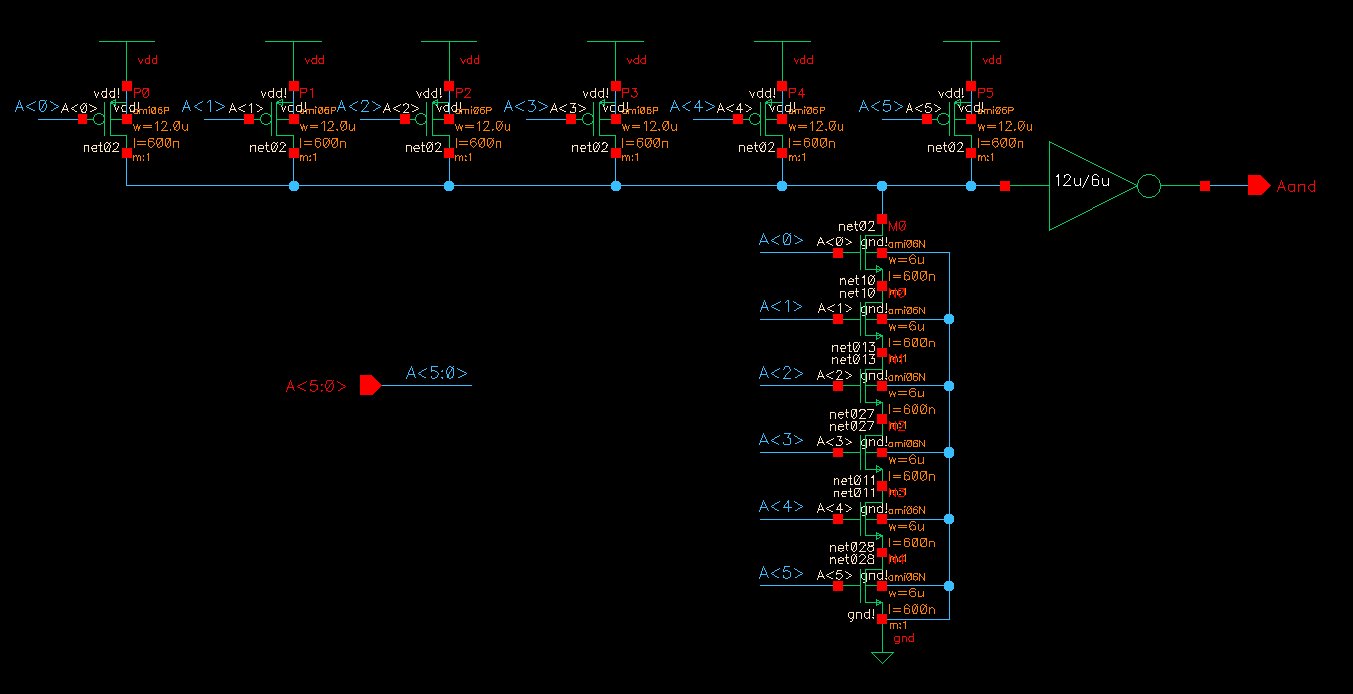

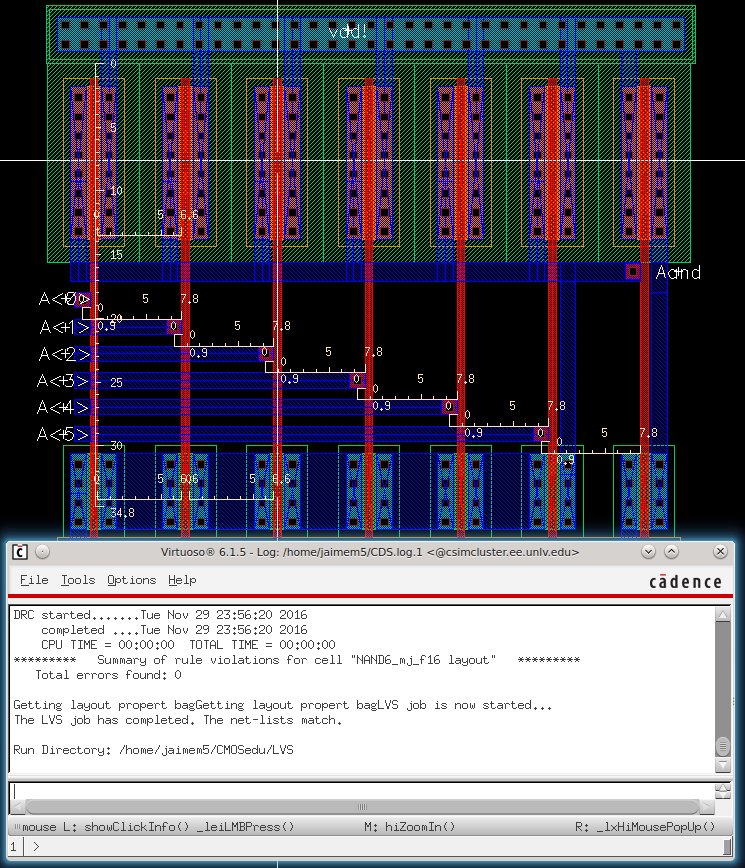

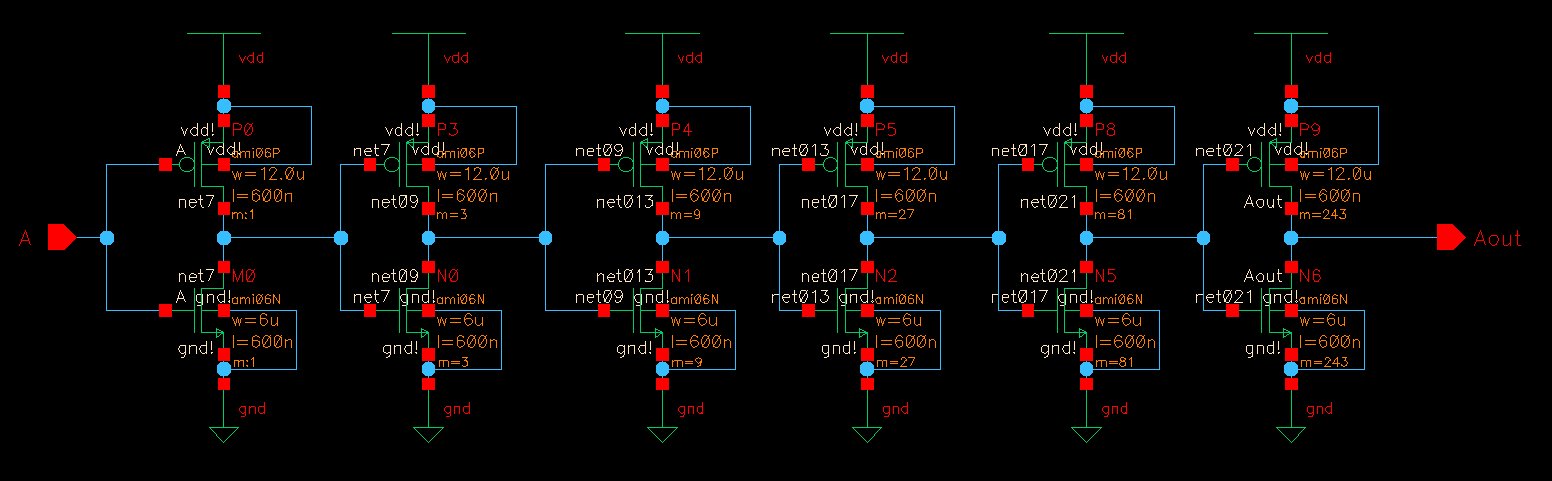

- The 6 input NAND gate was designed as the NAND gate is commonly

implemented, with additional inputs, and an inverter at the output.

Note that the schematic was wired with arrayed nets for simplicity.

All backed up work can be found at https://github.com/martinjaime/CMOSedu-Reports

EE421L Lab Student Listing | My Lab Directory | EE421 Home Page