The

use of Inherent Connections in Cadence from CMOSedu.com

Cadence

has an inherent connection flow that can be useful in mixed-signal

design.

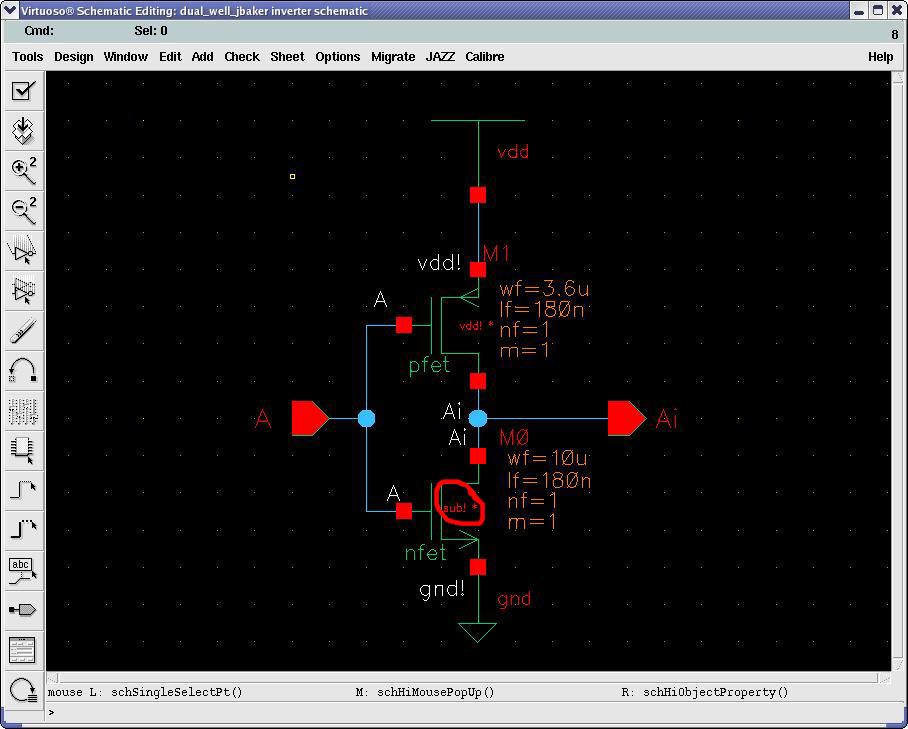

Below is an inverter using 3-terminal MOSFET

symbols.

Note that the fourth terminal of the NMOS is inherently connected to

sub!

The

use of inherited connections is also common in MIM capacitors which may

be

placed over the nwell

(e.g., tied to vdd!) or

over

the

p-substrate (e.g., tied to gnd!).

To

connect the body of the NMOS above to gnd!

(so the

inverter’s schematic and layout LVS without errors)

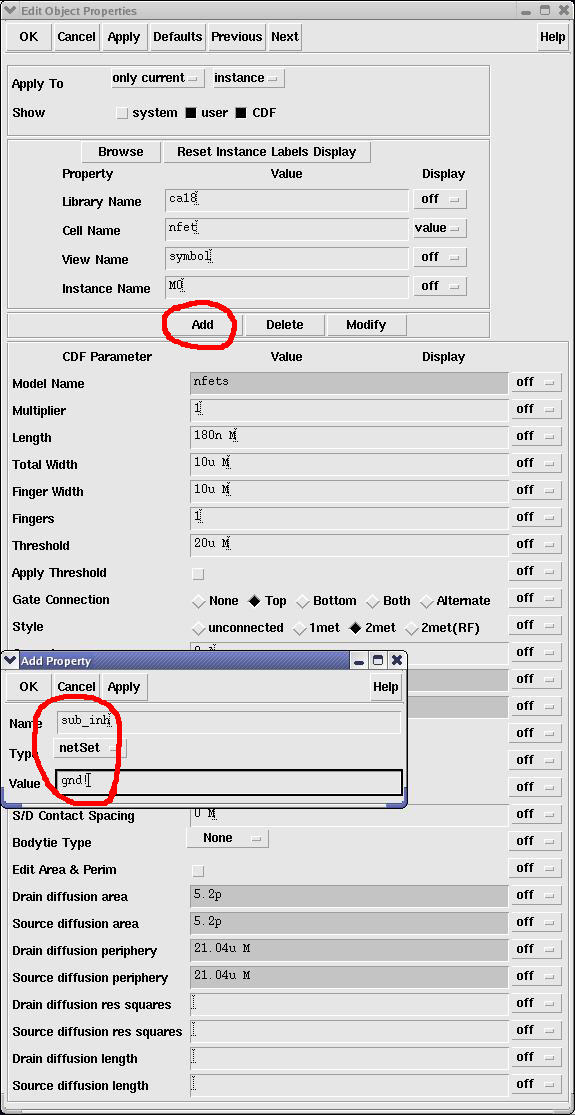

1.

Edit the NMOS’s Object

Properties (using

the bind key q)

2.

Click the Add CDF

button

3.

Set the Name to sub_inh,

the Type to netSet,

and the

Value to gnd!

Note

that if the substrate were at a negative potential you would set the

value to

this potential, say vss! Again, other symbols that use

inherent

connections, such as a MIM capacitor, follow this procedure for setting

their

connection.