TDC and other

test structures

Contributors:

Vikas Vinayaka (vinayaka@unlv.nevada.edu)

Sachin P Namboodiri (puruss1@unlv.nevada.edu)

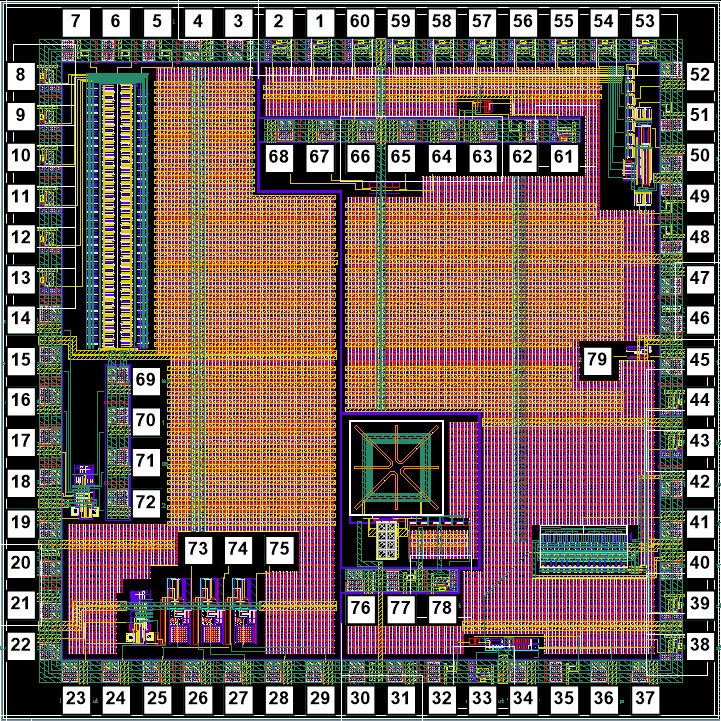

Chip organization

This chip is design using AMS .35µm SiGe

process. It comprises the following circuits:

1) 2 TDC architectures

2)

An averaging circuit

3)

A wide swing op-amp

4)

A transimpedence amplifier (TIA)

5)

A 4-bit flash ADC

6)

An LC oscillator

7) A comparator

Figure 1. Complete Layout

TDC 1

|

Signal name |

Pin# |

|

Start |

51 |

|

Stop |

49 |

|

Reset |

48 |

|

b0-b9 |

2(B0),1(B1),60-53(B2-B9) |

TDC 2

|

Signal name |

Pin# |

|

Start |

5 |

|

Stop |

7 |

|

Reset |

6 |

|

b0-b5 |

8-13 |

LC Oscillator

|

Signal name |

Pin# |

|

VDD |

76 |

|

Reset |

77 |

|

Oscillator

output |

78 |

Wide swing Opamp

|

Signal name |

Pin# |

|

Vb1 |

70 |

|

Vb2 |

72 |

|

Vb3

|

14 |

|

Vb4 |

16 |

|

Vpcas |

71 |

|

Vncas |

15 |

|

Vbiasp |

69 |

|

Vp |

18 |

|

Vm |

17 |

|

Out |

19 |

Sense amplifier/Pre-amplifier (for comparator)

|

Signal name |

Pin# |

|

Sa_Clk |

62 |

|

Sa_Inm |

63 |

|

Sa_Inp |

66 |

|

Sa_Outp |

61 |

|

Pa_Inm |

67 |

|

Pa_Inp |

68 |

|

Pa_Outm |

64 |

|

Pa_Outp |

65 |

TIA

|

Signal name |

Pin# |

|

In |

79 |

|

Out |

45 |

4-bit Flash ADC

|

Signal name |

Pin# |

|

Ext_Clk_In |

32 |

|

Clk_Div2_Out |

33 |

|

Vin_VCO |

34 |

|

VCO_En |

35 |

|

VCO_Rrange |

36 |

|

VCO_Rlow |

37 |

|

ADC_In |

41 |

|

Vrefp |

42 |

|

Vrefm |

40 |

|

b0 |

38 |

|

b1 |

39 |

|

b2 |

43 |

|

b3 |

44 |

TIA Averager

|

Signal name |

Pin# |

|

Avg_Out |

23 |

|

tia3_Out |

24 |

|

tia3_Vb |

25 |

|

tia2_Out |

26 |

|

tia2_Vb |

27 |

|

tia1_Out |

28 |

|

tia1_Vb |

29 |

|

tia3_In |

73 |

|

tia2_In |

74 |

|

tia1_In |

75 |

Power Supply

|

Signal name |

Pin# |

|

VDdw |

4,21 |

|

vdde |

47,31 |

|

gnd |

3,20,30,46 |