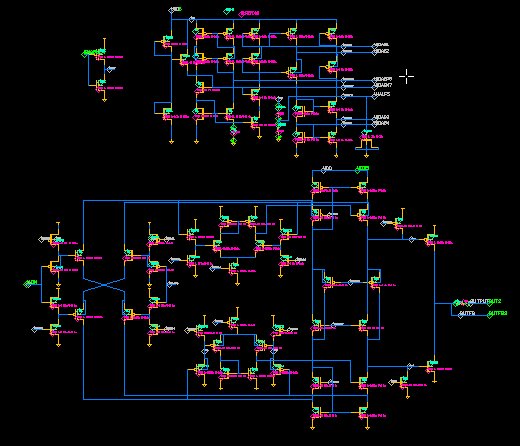

High-speed

Low-power Op-amp for use in a 10-bit DAC

Below

is the schematic of a

high-speed op-amp used as part of a DAC. 128 DACs are used on the chip

so the

entire 10-bit DAC must fit in a small area (around 200 um

square.)

The

load was 60 pF (maximum) with

a resistance of 10k (minimum.) The settling time was 30 ns (maximum)

and the

quiescent power draw less than 500 uA.

The op-amp was

designed and laid out by Jake Baker in Tower's 0.35 um (TS35) process

January/February 2000.