Lab 3 - ECE 421L

Quinton Micheau

9/3/2020

micheauq@unlv.nevada.edu

Lab 3

This week's laboratory will cover how to complete the layout view of

the 10-bit DAC we designed in the previous week.

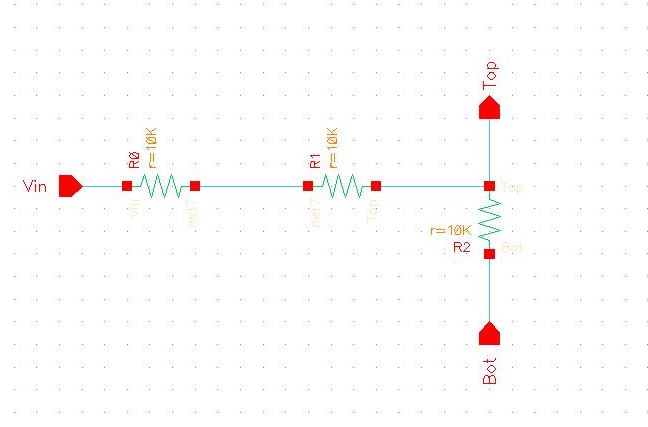

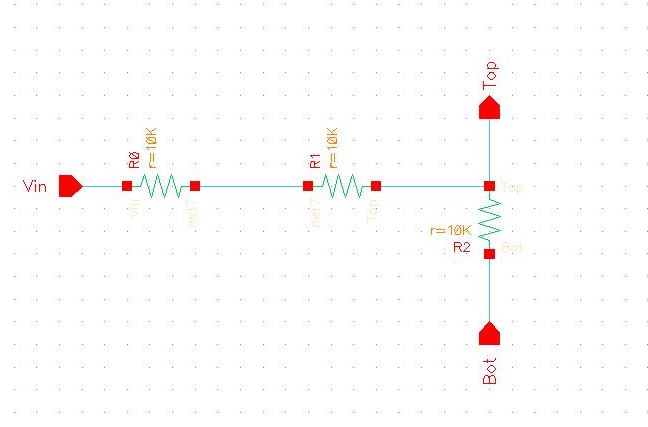

The DAC functions as a voltage devider so we need to construct a n-well equivalent layout of the 2R_R schematic shown below:

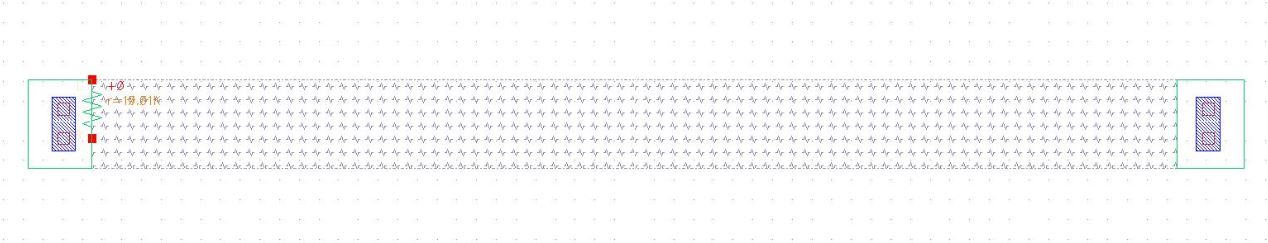

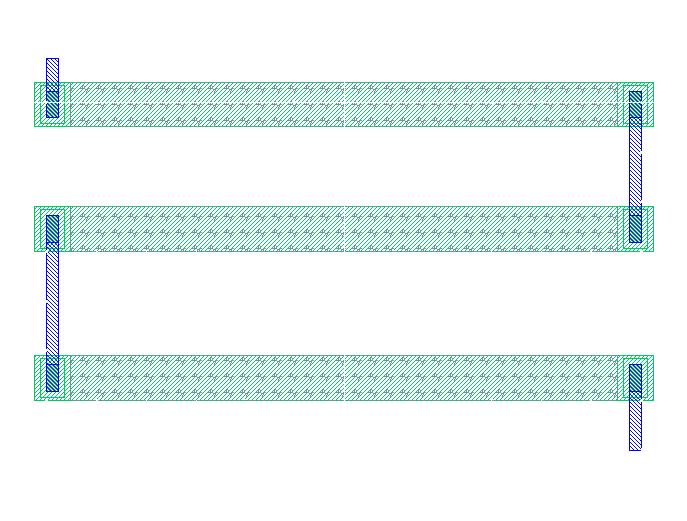

Following Tutorial_1, I designed an 10.01k n-well resistor shown below:

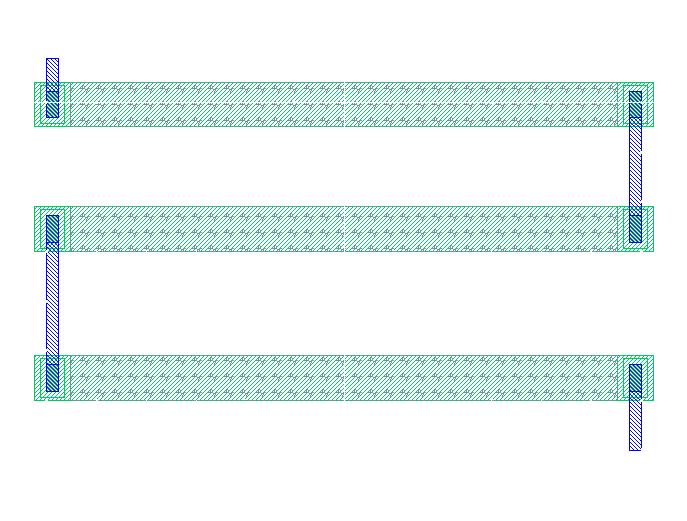

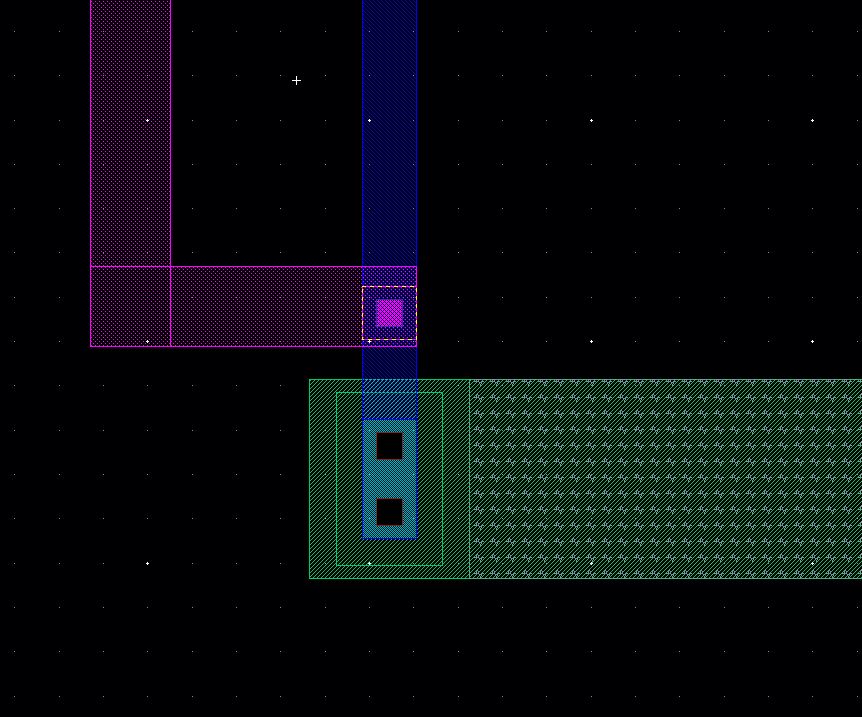

I combined these n-well resistors in an orientation that will give the same results as the 2R_R resistor:

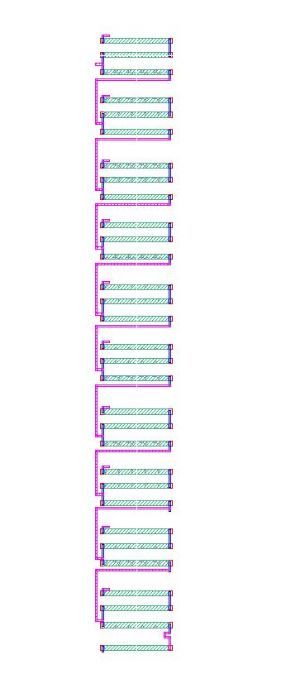

The

schematic we are drawing the layout for has 10 pins and each of the

above modules are a component for a single pin. Therefore, we need to

combine 10 of the above layout in order to complete our layout of the

10-bit DAC. Below is the layout for the 10-bit DAC using n-well

resistors and connecting them with metal_2.

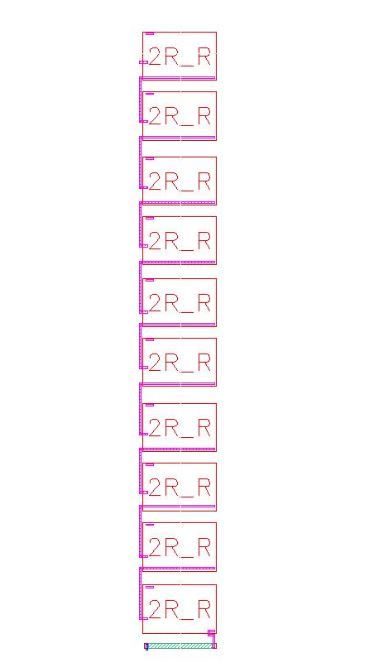

Changing the layer view shows that our 10-bit DAC is built from individual 2R_R's we designed previously.

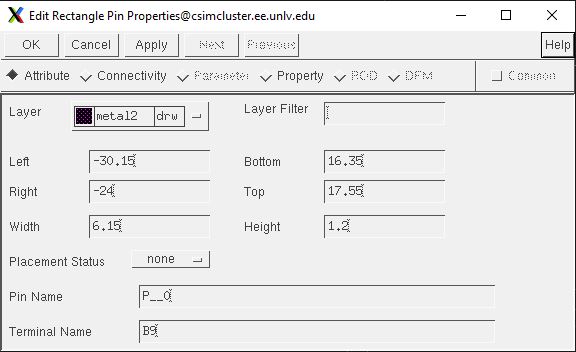

Each 2R_R block has a corresponding pin B0-B9:

Metal_1 and metal_2 are connected via the instance M1_M2 found in the appropriate ami library.

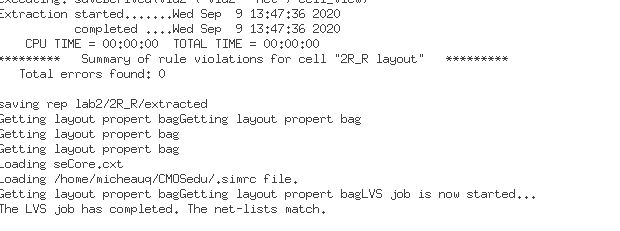

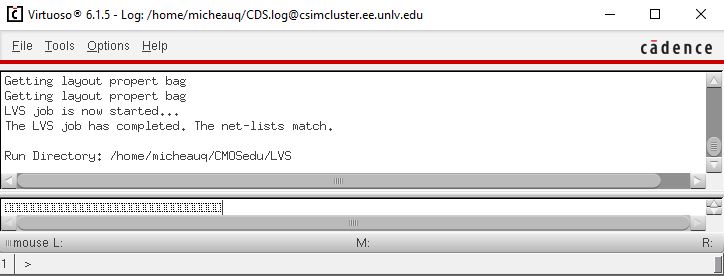

Finally,

in order to ensure that our layout and schematic are compliant with the

Cadence design rules, a DRC was run as well as an LVS verification.

Both results showed that the layout is indeed the same as the schematic

and that the design follows the rules.

Zip file for the above schematics

Return to EE 421L Labs