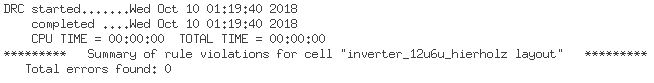

Lab 5 - EE 421L

Allis Hierholzer

hierholz@unlv.nevada.edu

10/10/18

Pre-Lab:

- Back-up all work from the lab and the course

- Go through Tutorial 3

Lab Description:

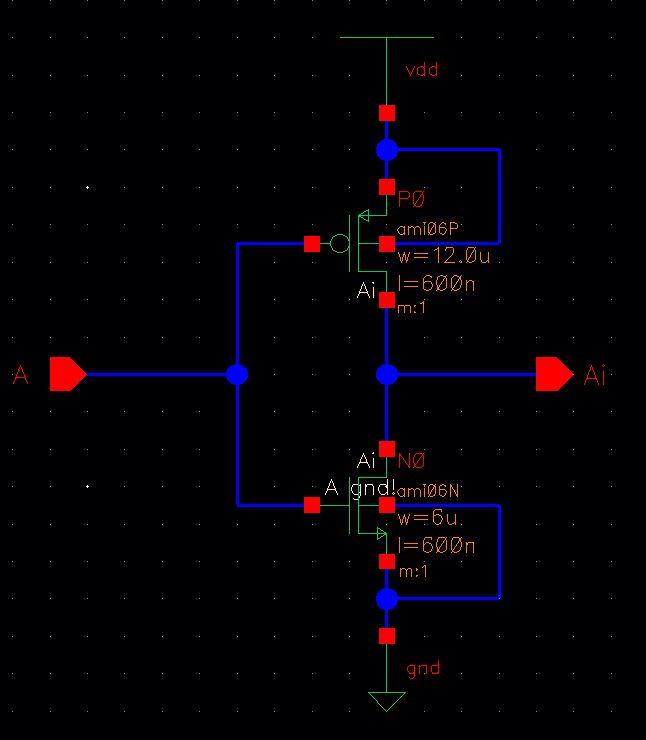

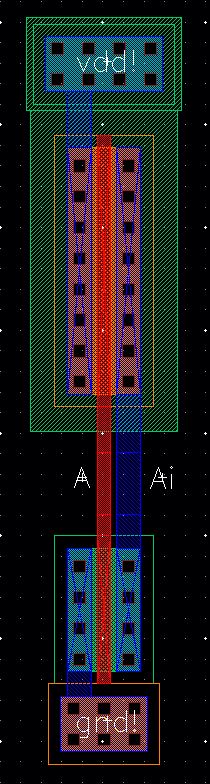

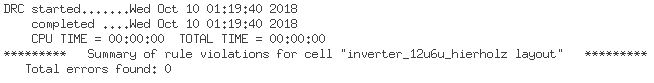

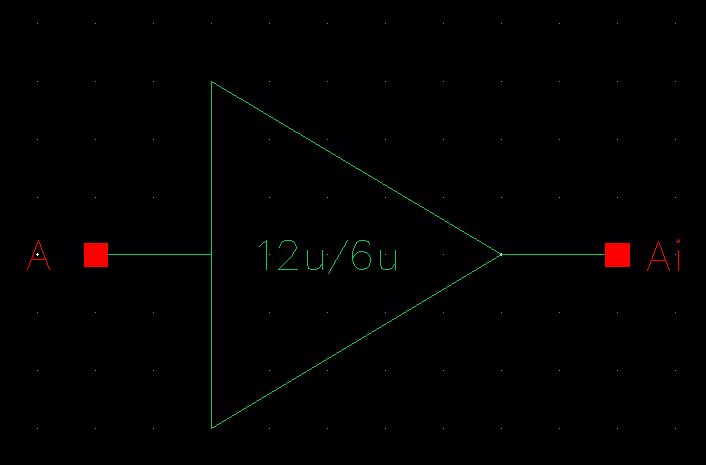

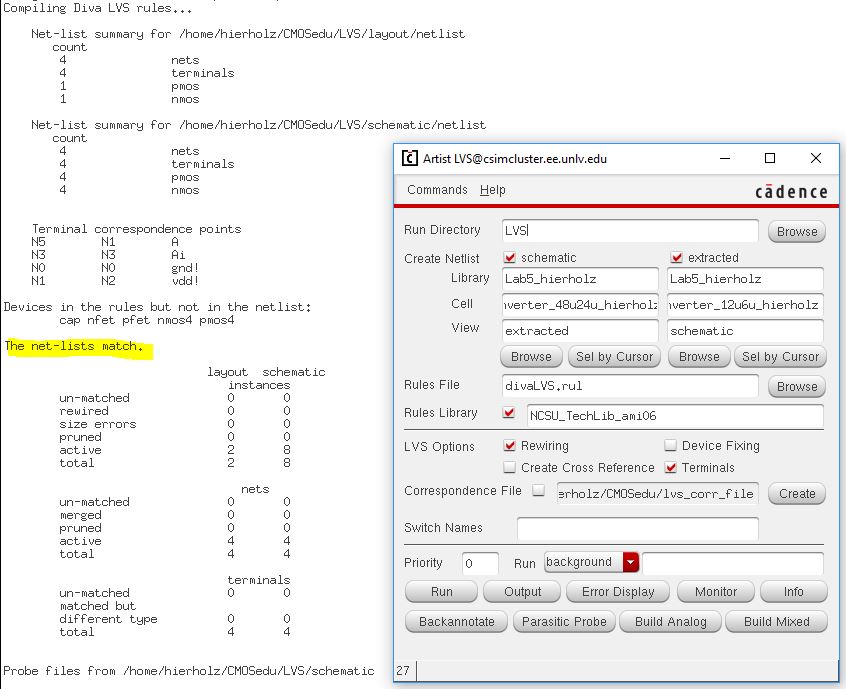

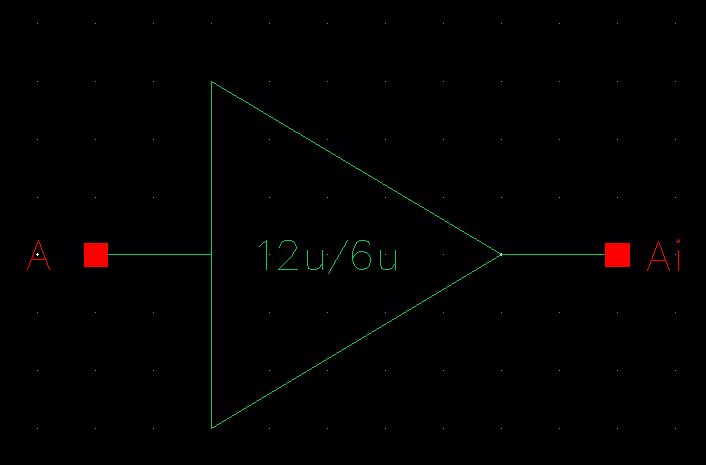

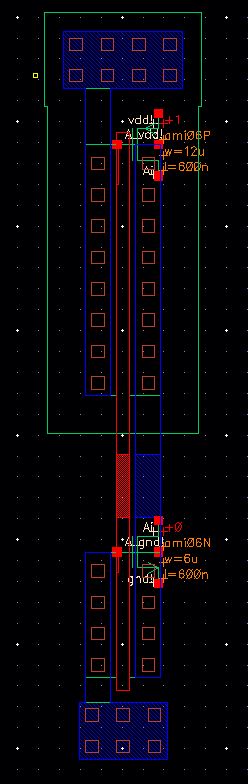

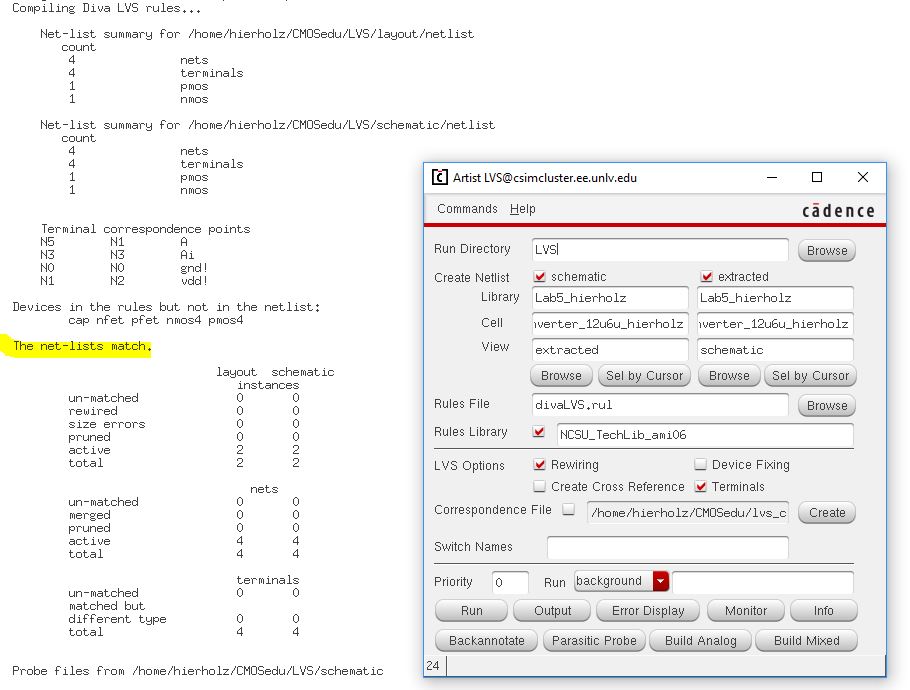

- This lab focuses on designing a CMOS inverter and running its simulation

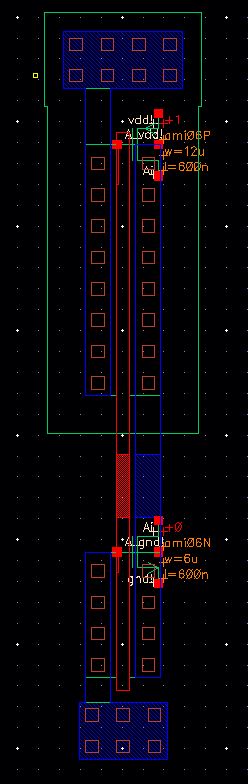

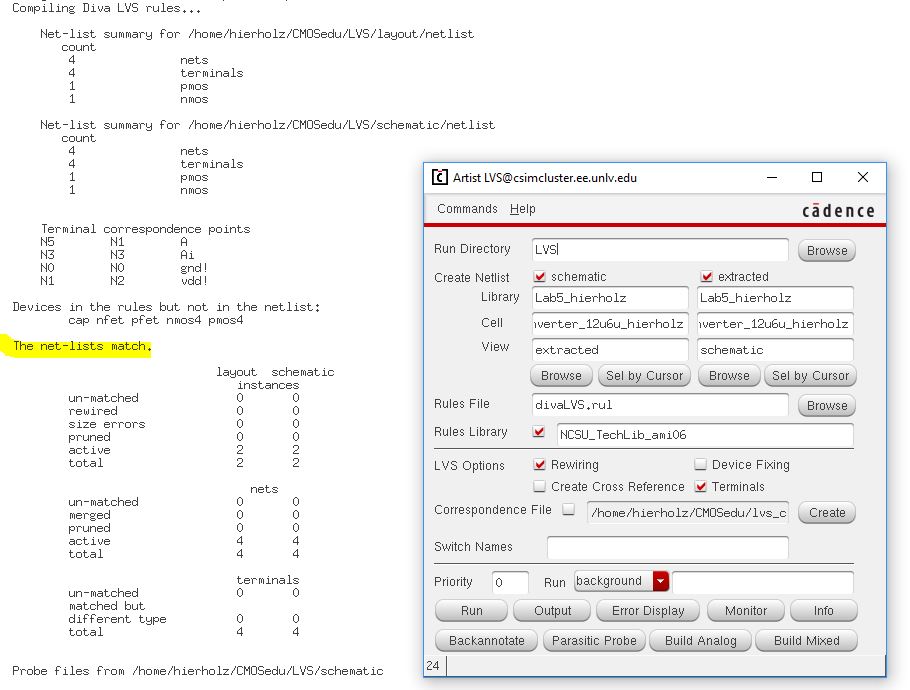

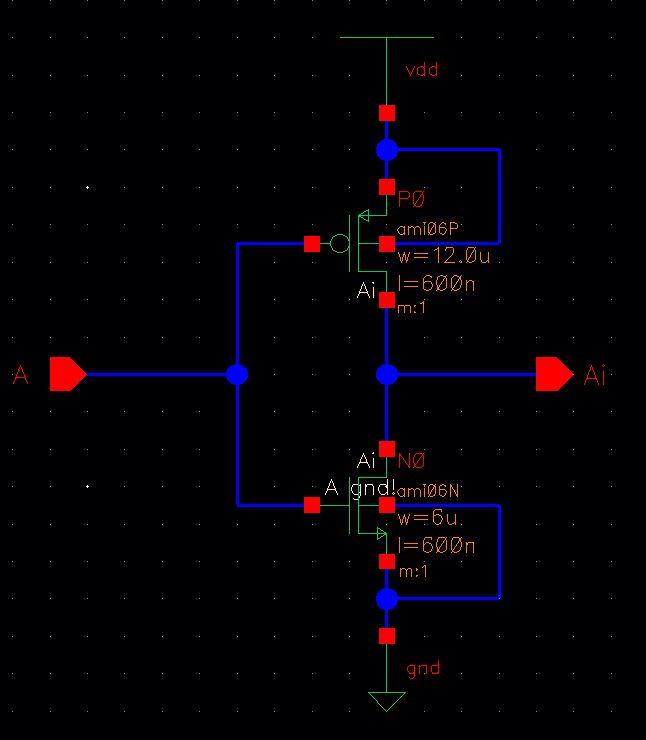

- Create

an inverter with size 12u/6u ( = width of the PMOS / width of the NMOS with both devices having minimum lengths of 0.6u)

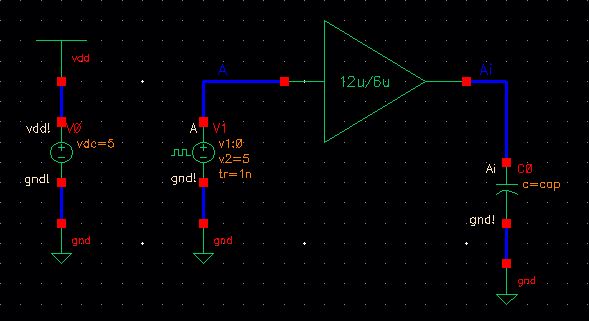

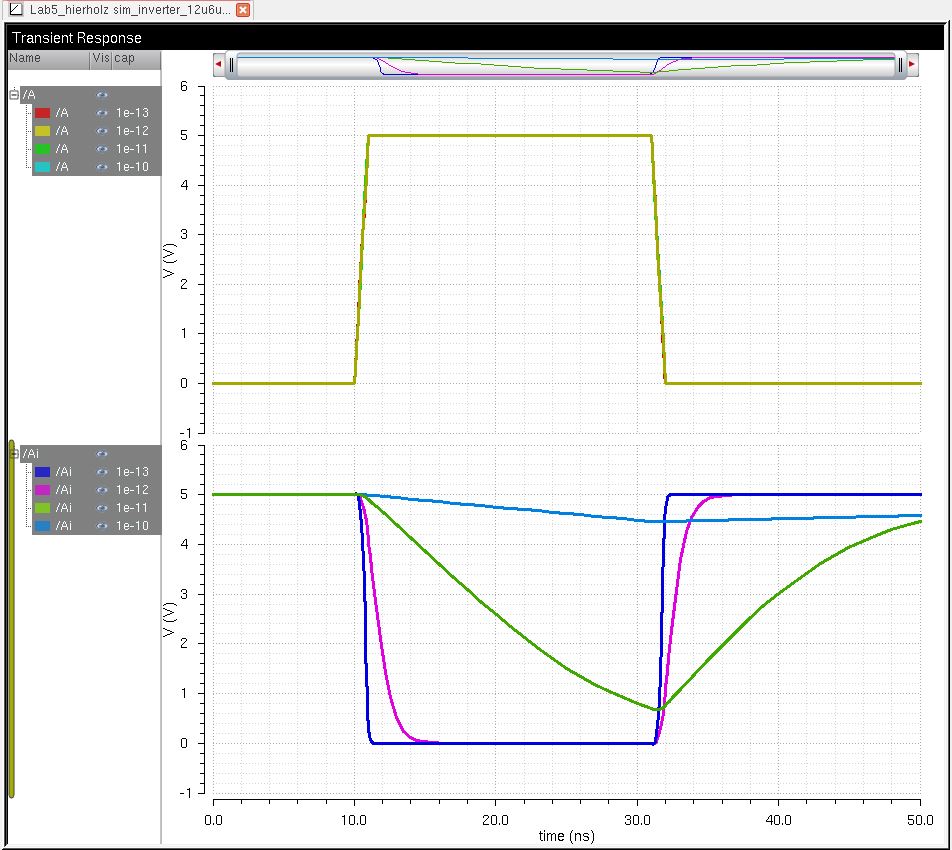

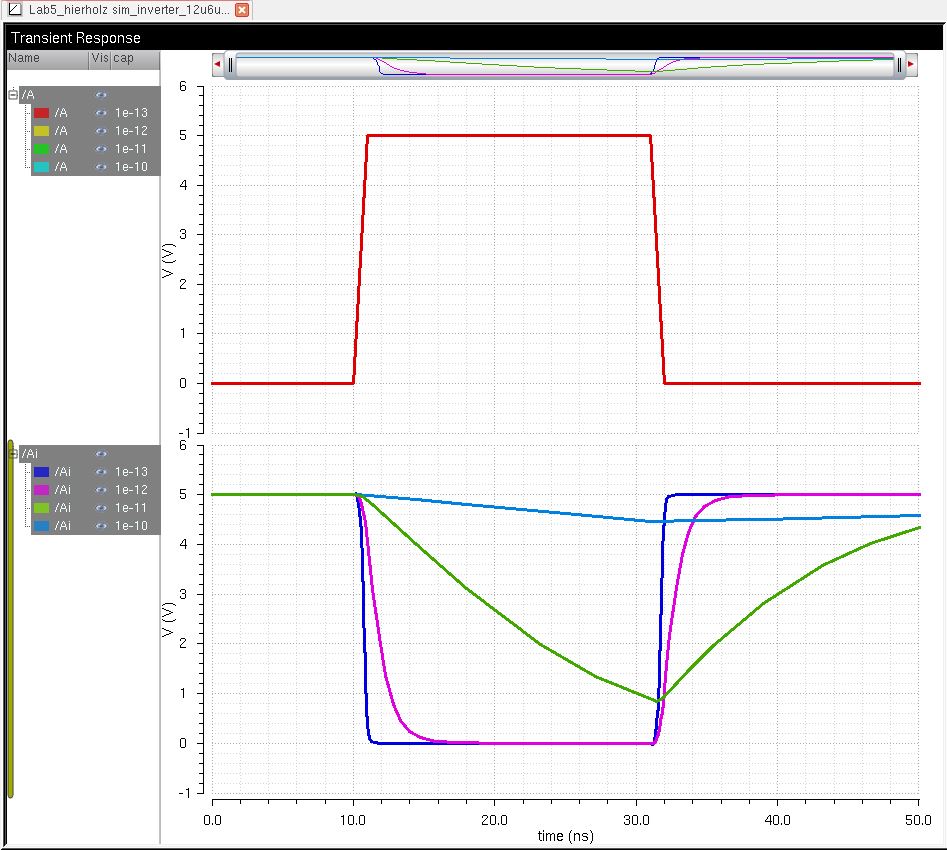

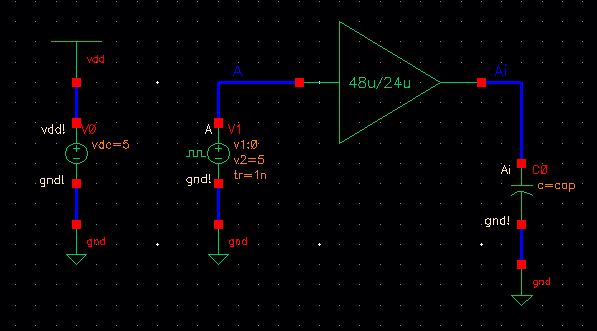

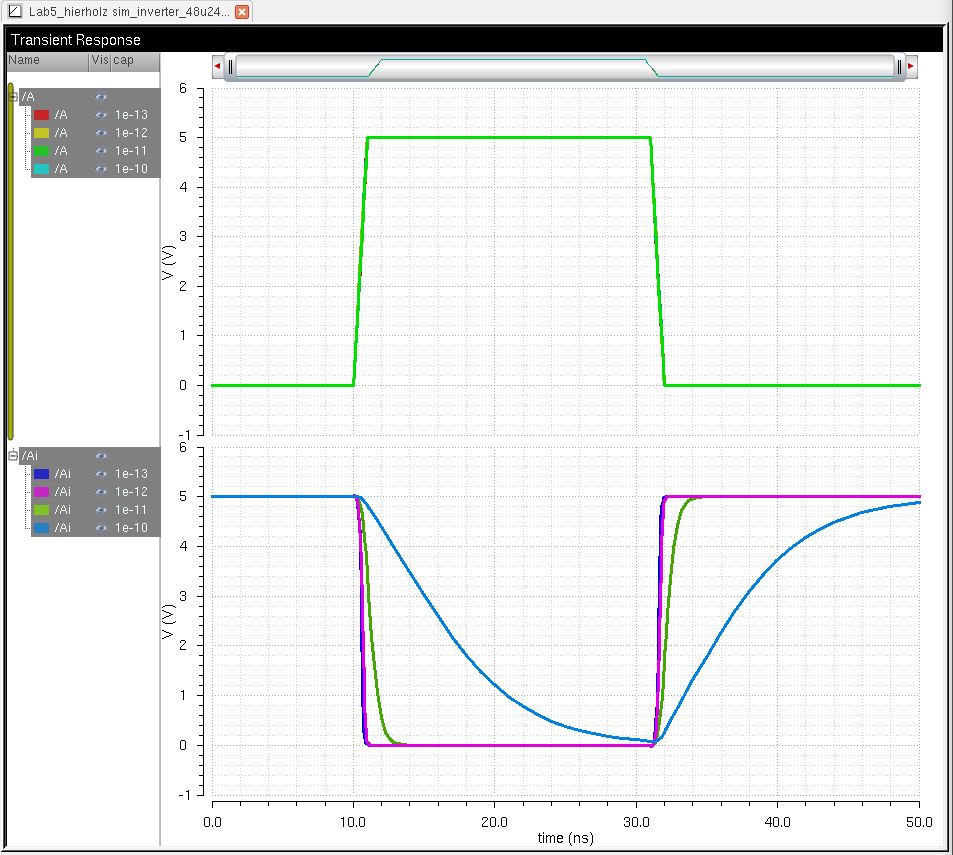

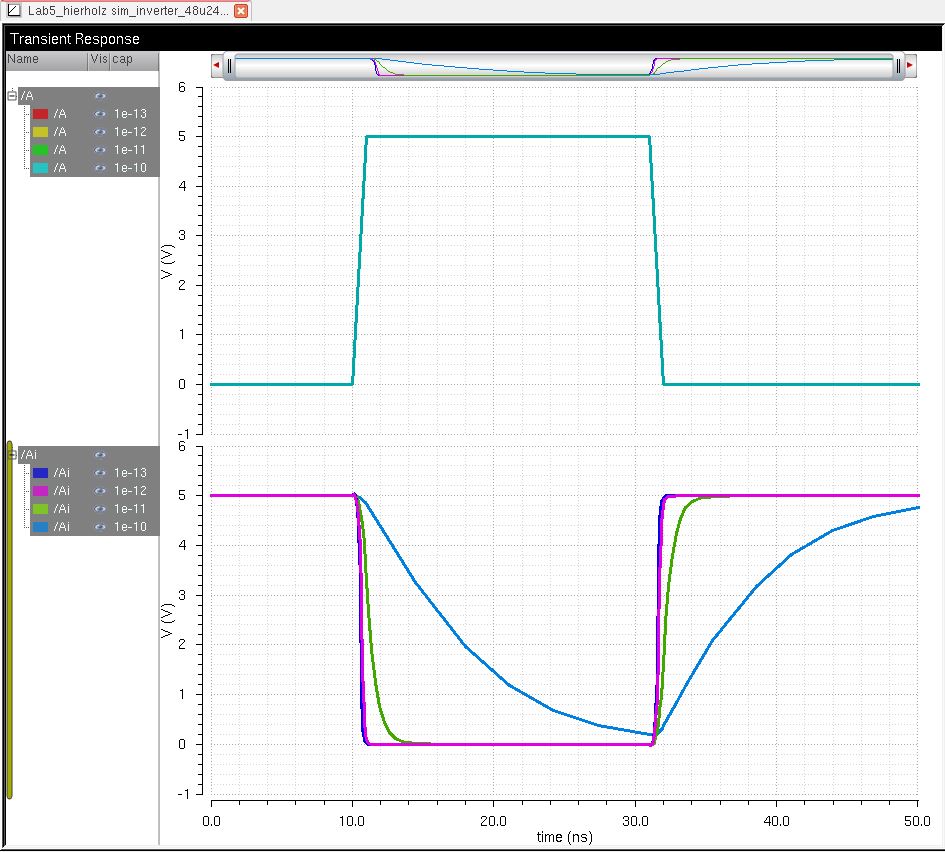

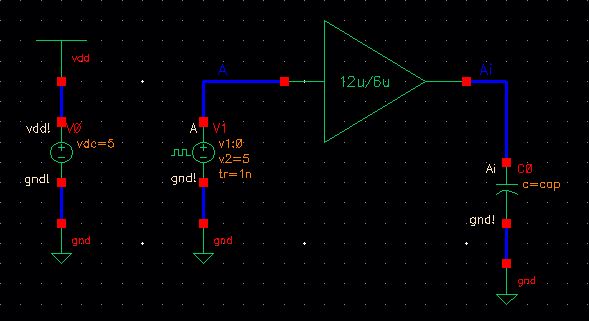

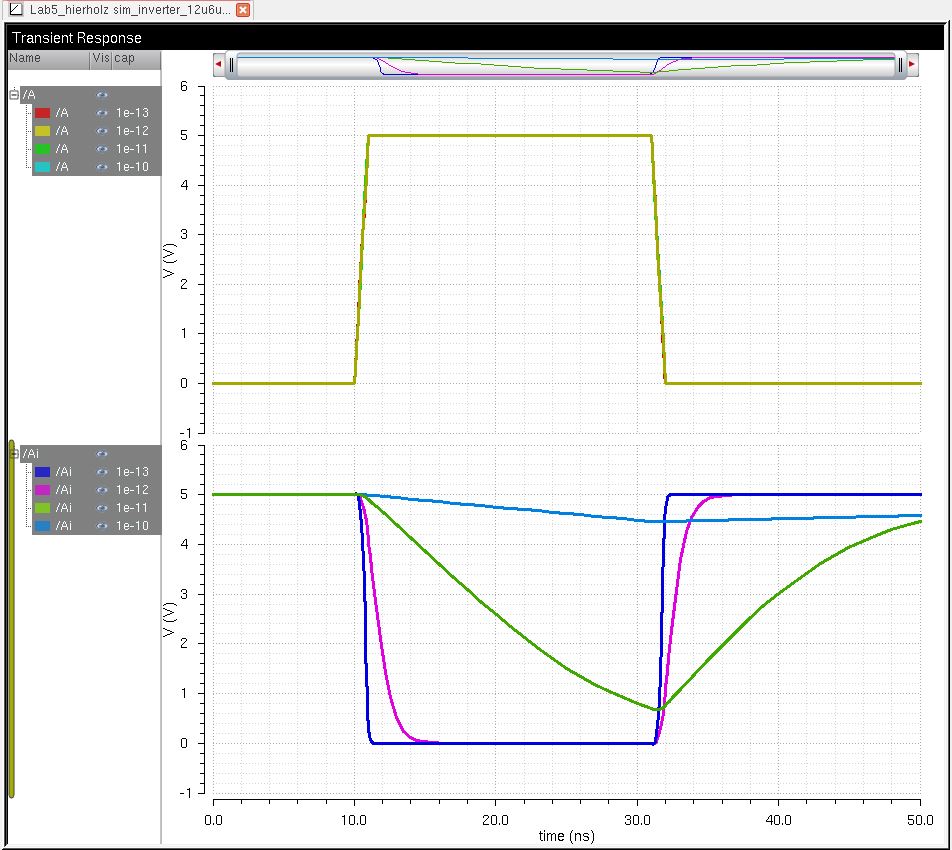

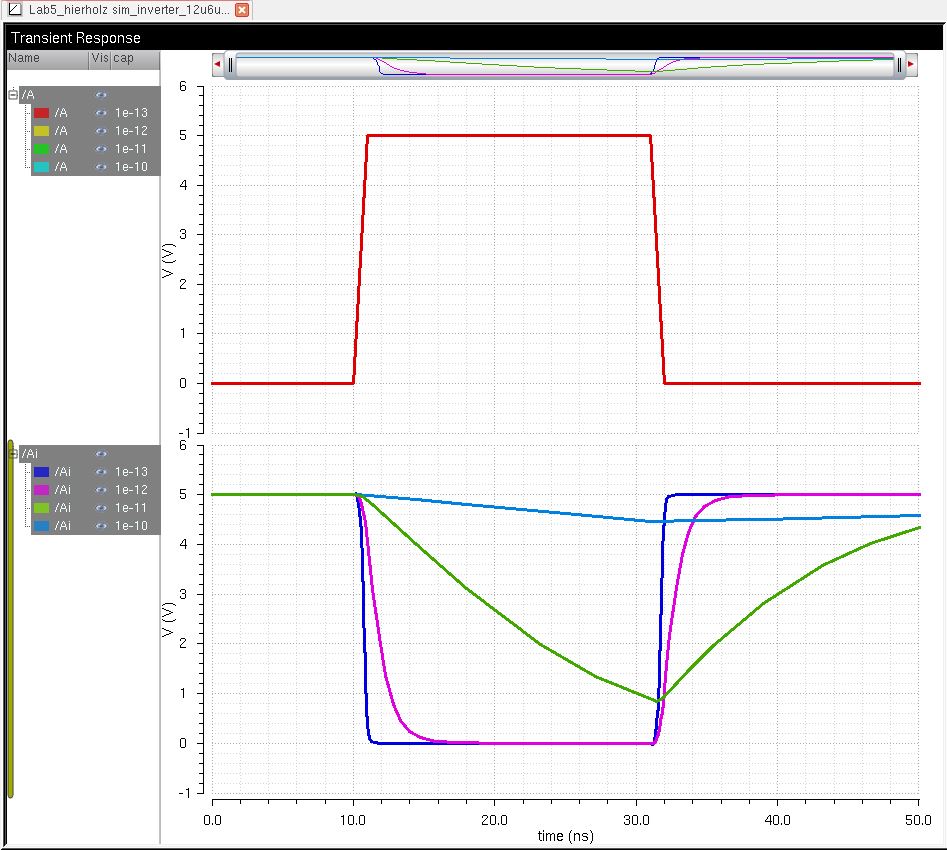

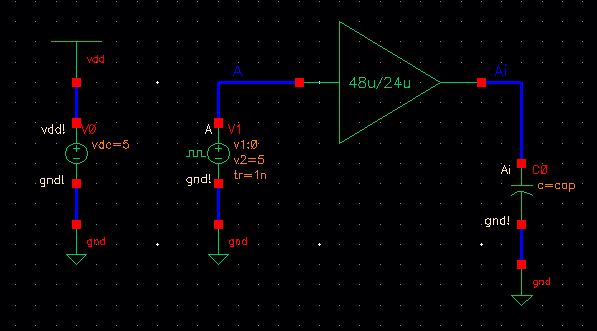

- Schematic to simulate the inverter with time delay of 10ns and transient time of 50ns

SPECTRE

ULTRASIM

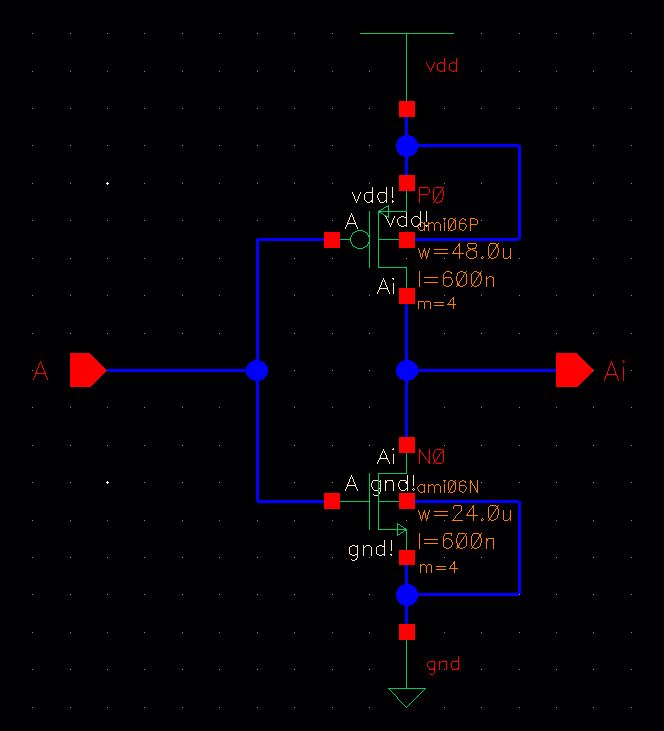

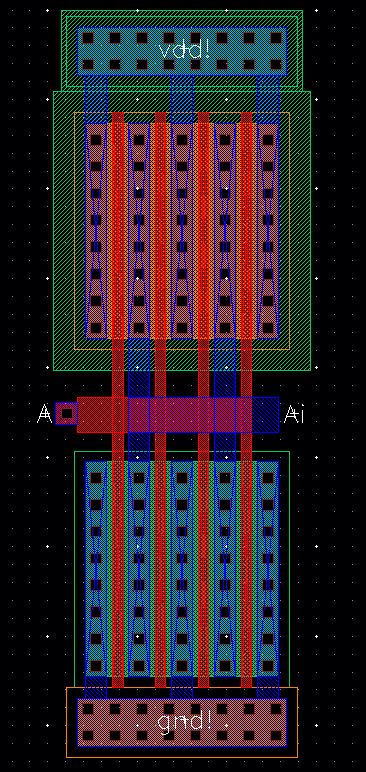

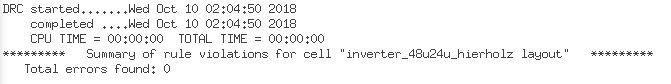

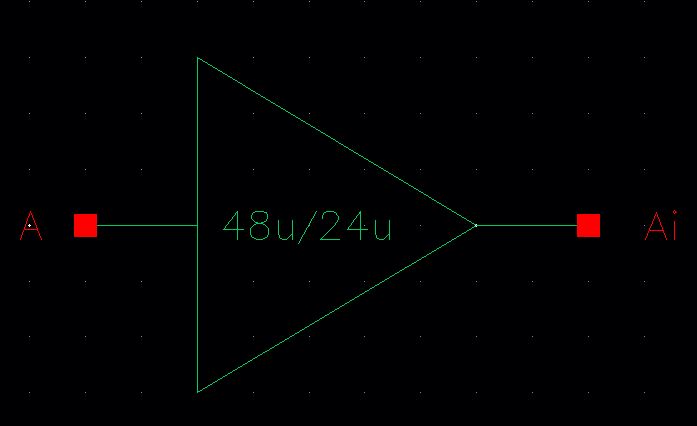

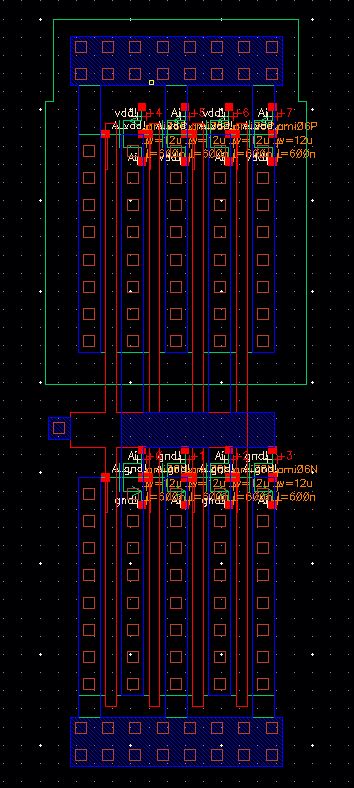

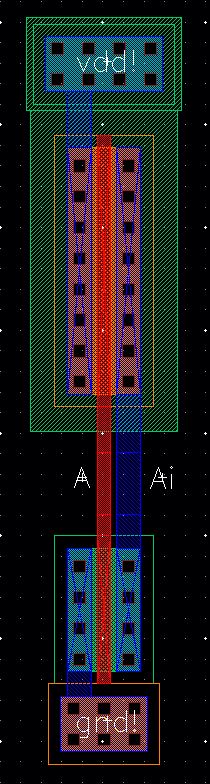

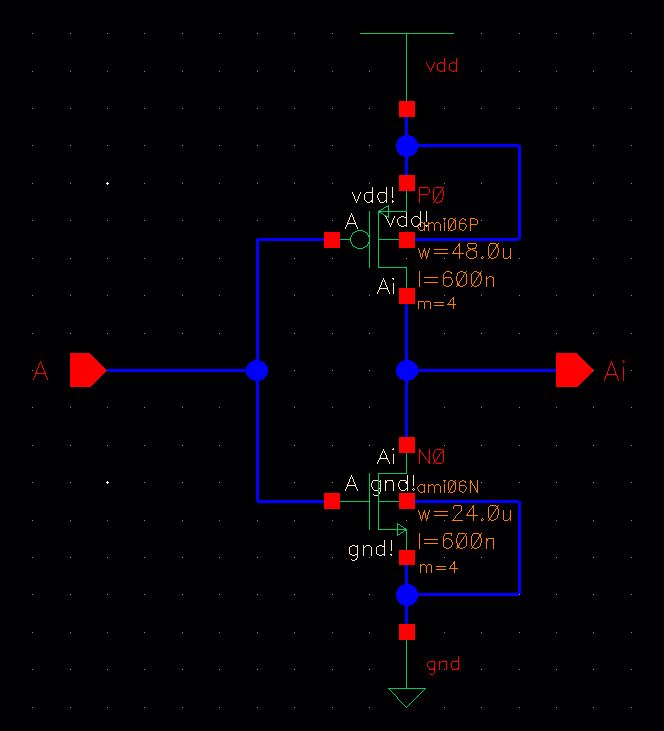

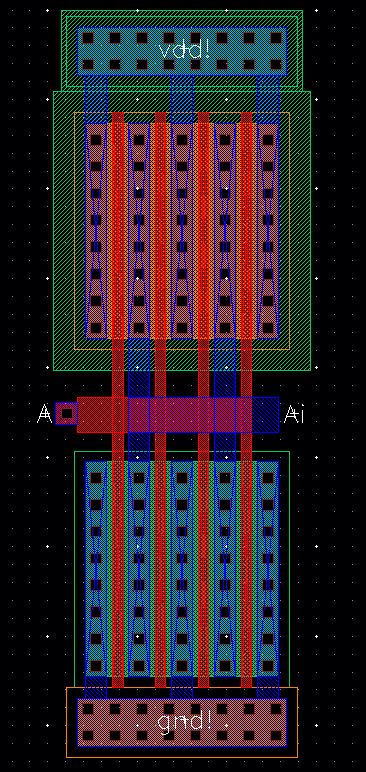

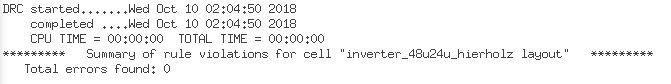

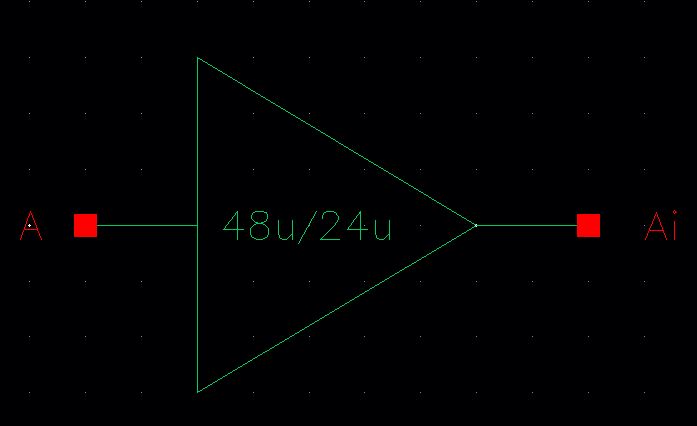

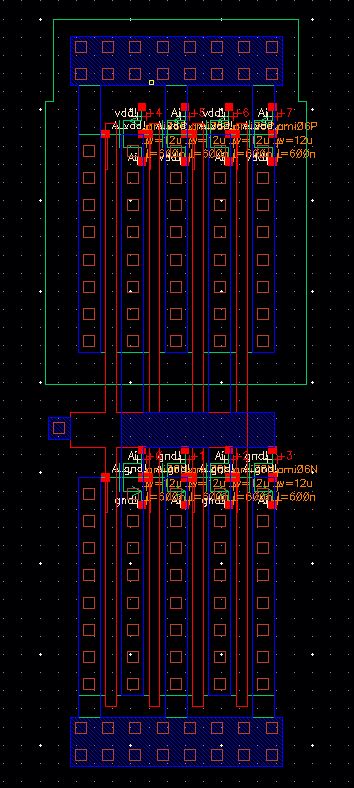

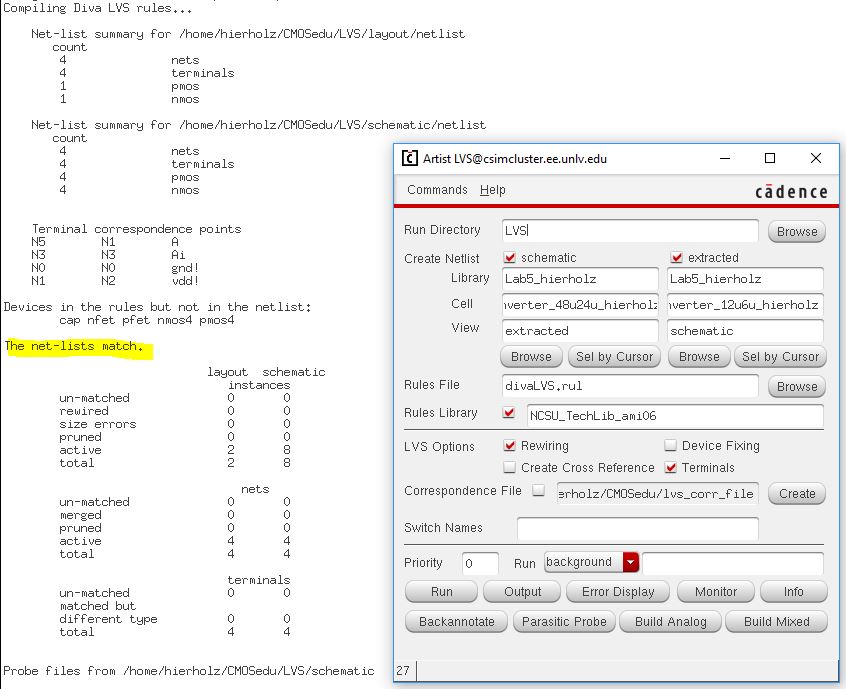

- Create an inverter with size 48u/24u where the

devices use a multiplier, M = 4 (set along with the width and length of

the MOSFET)

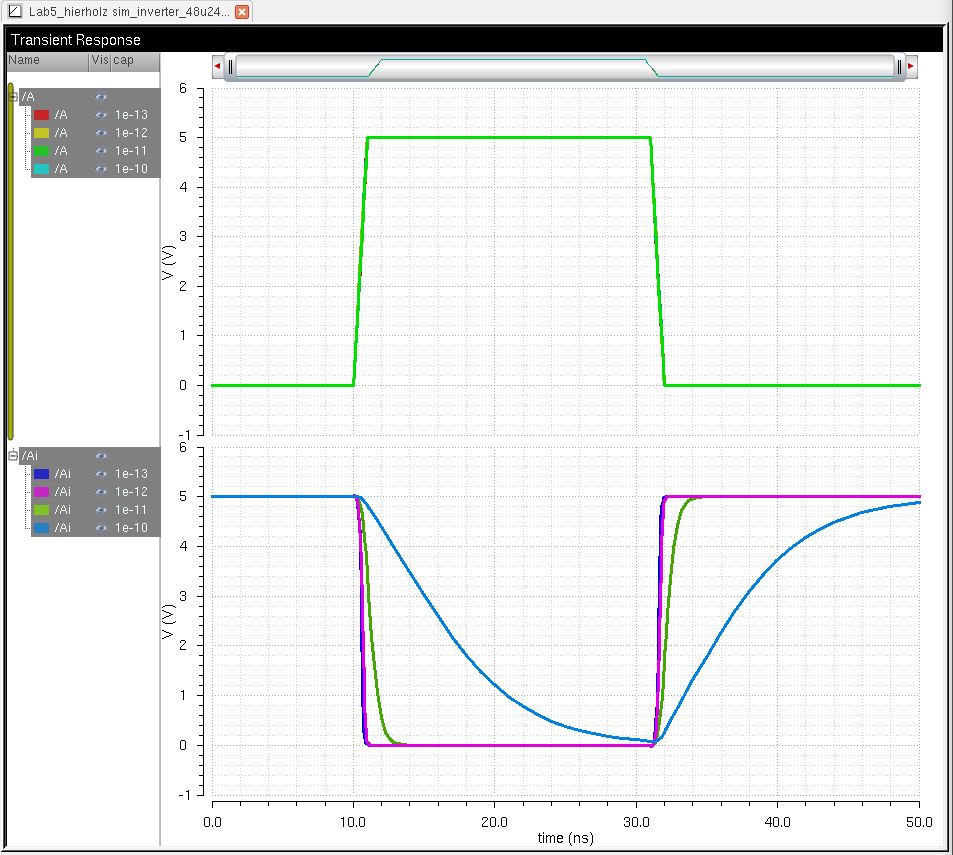

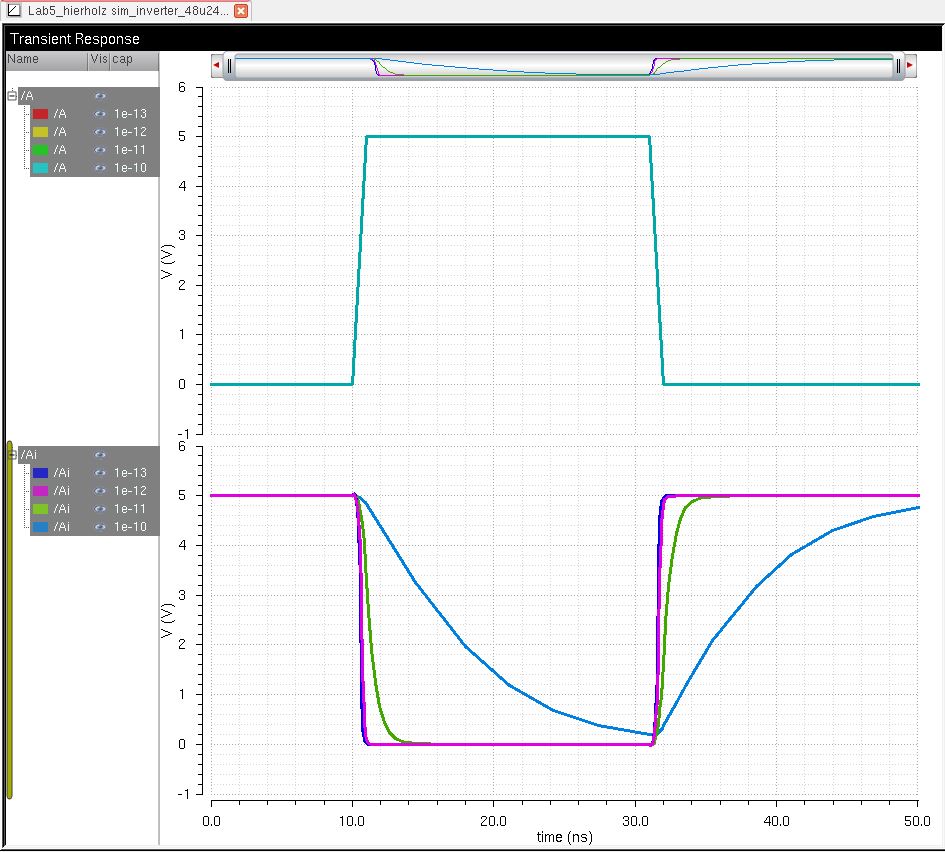

- Schematic to simulate the inverter with time delay of 10ns and transient time of 50ns

SPECTRE

ULTRASIM

The cells used to generate the images used on this webpage can be downloaded in Lab5_hie

Return to EE 421 Lab

Return to Student Lab Reports