EE 421L

Lab 1

Authored

by Jeremy Morgan

Due: 9/6/2017

Lab

description:

Understanding and following directions outlined within Tutorial 1: Layout and Simulation of a Resistive Voltage Divider.

Prelab:

Creating a account within CMOSedu for use with KompoZer.

Reviewing guide to tutorial 1.

Lab:

Phase 1: Constructing workspace and opening cadence.

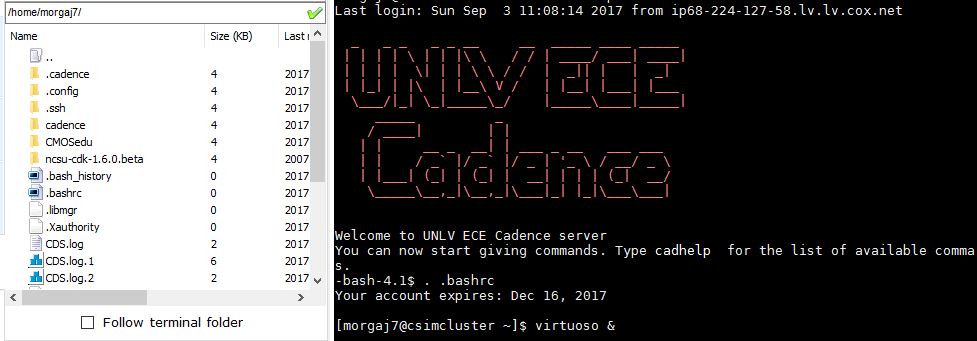

The first step in creating our Resistive Voltage Divider was to setup our Cadence workspace by

downloading the zip file and installing the proper ON's C5 software along with setting up our mobaX terminal workspace.

We run Cadence by typing 'virtuoso &' in our Cd CMOSedu workspace.

Phase 2: Constructing a simulation of a resistive voltage divider.

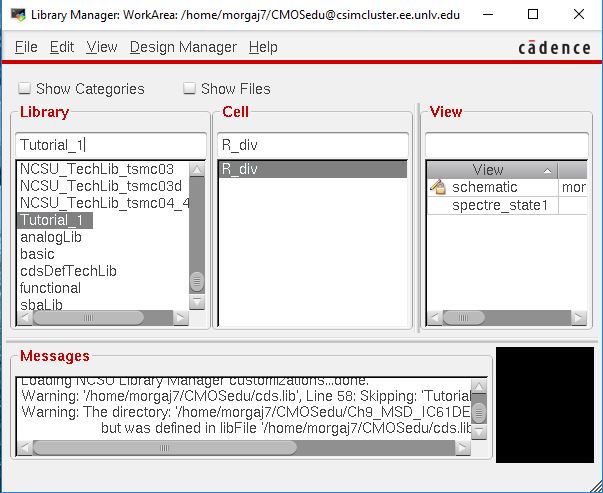

After constructing a workspace, we then created a location for our schematic.

We created a library titled 'tutorial 1' along with a cell view:

Following the design instructions, I constructed a resistive voltage divider within the cell view of 'tutorial 1'.

We then were able to construct a simulation of its voltage 'In' and 'Out' Components:

Schematic.

Voltage simulation.

Phase 3: Backing up lab data.

I will be backing up my data using a combination of using my student drive:

And uploading the lab files to a google drive:

Return to EE 421L Labs