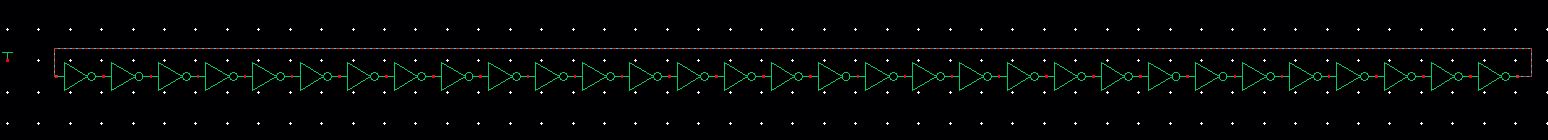

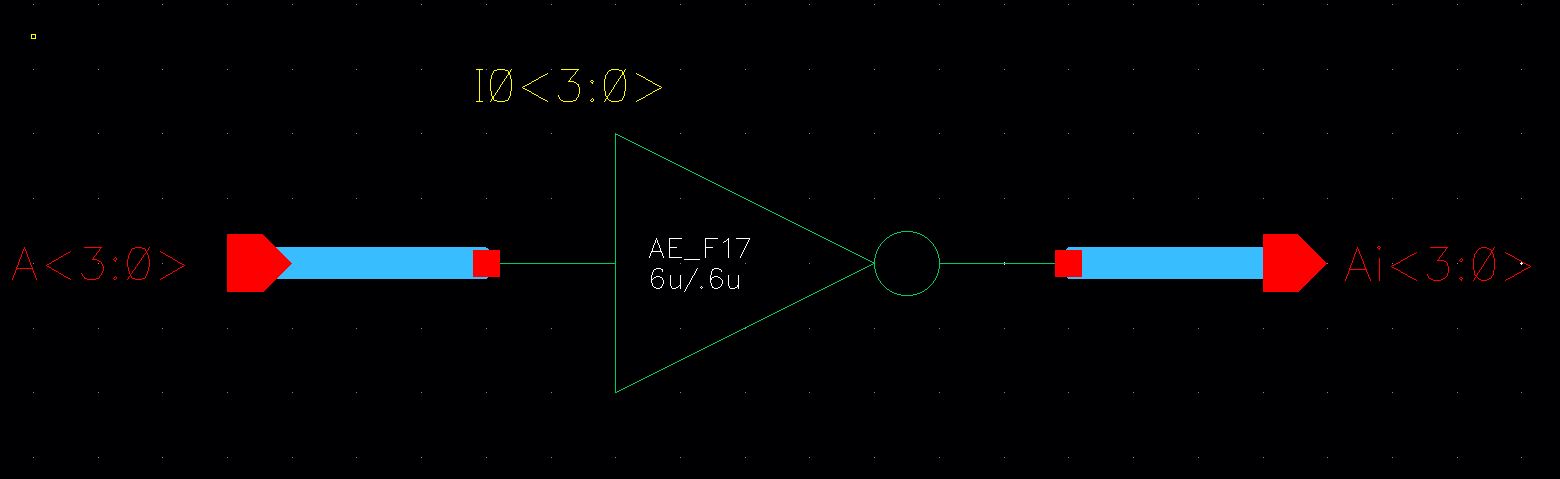

Since this can be inconvient to have within the circuit, we can simplify it by creating a bus of wires such as show below.

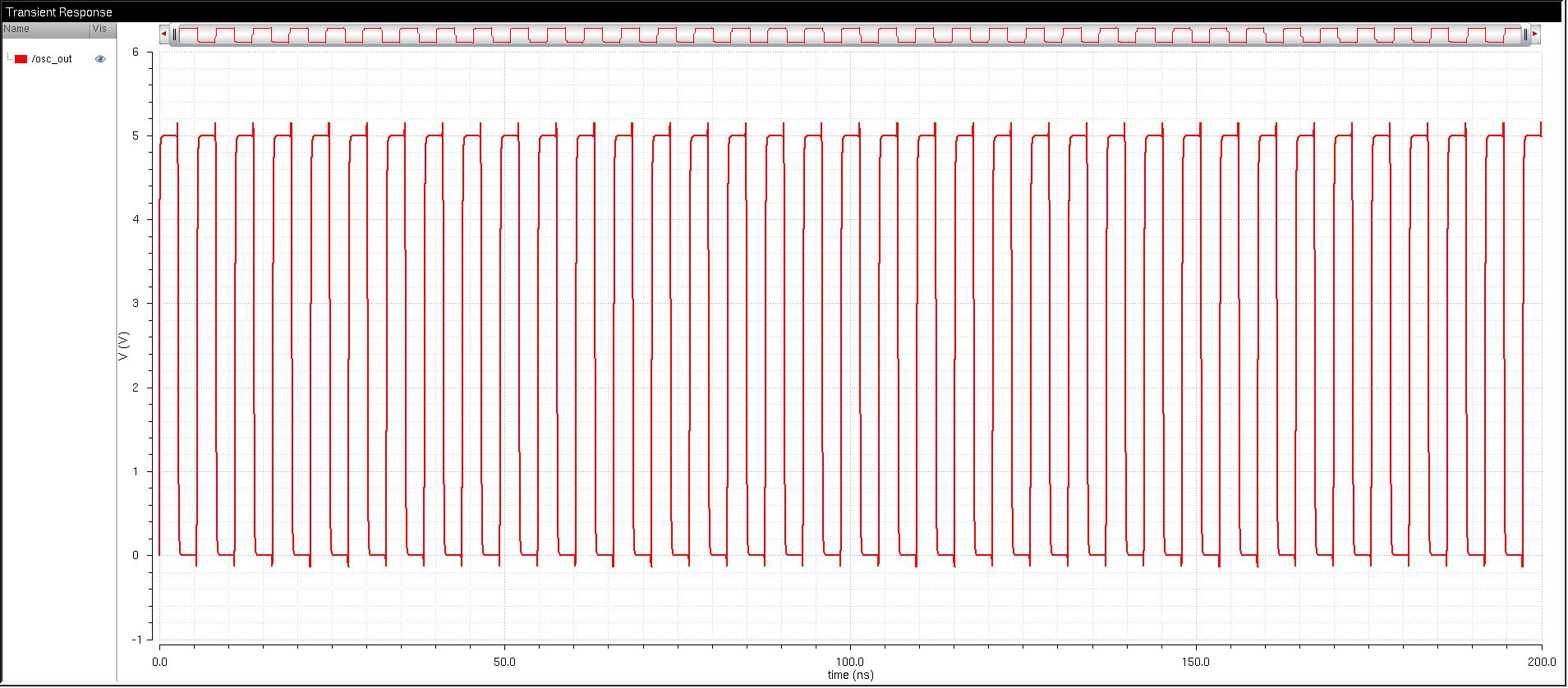

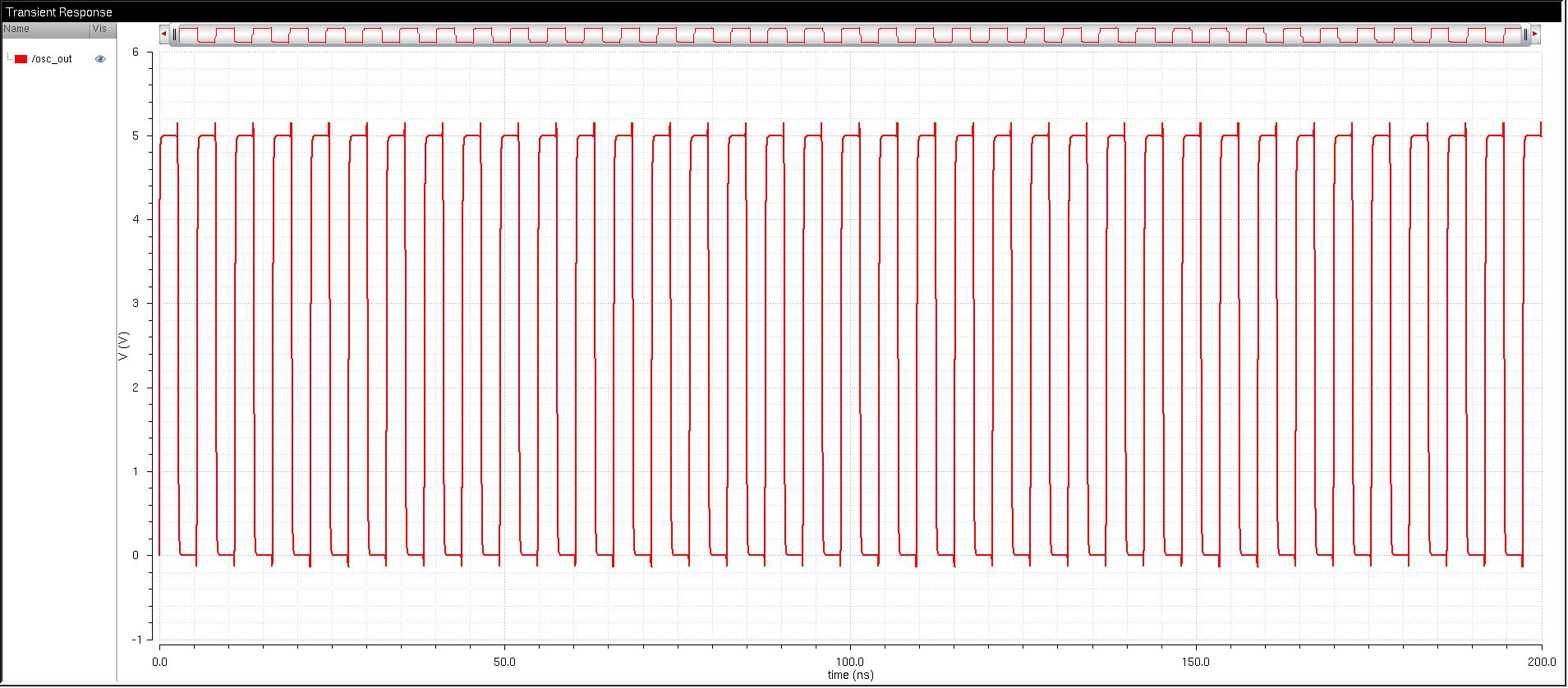

Initial ring oscillator schematic |  2nd circuit with simplified ring oscillator |

Lab 07 - EE 421L

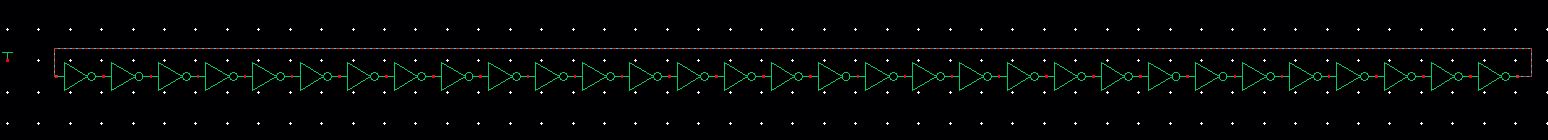

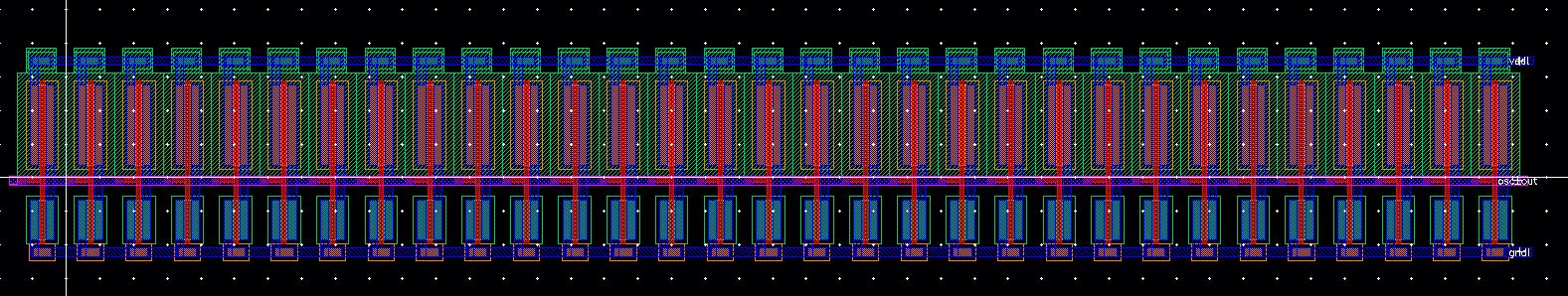

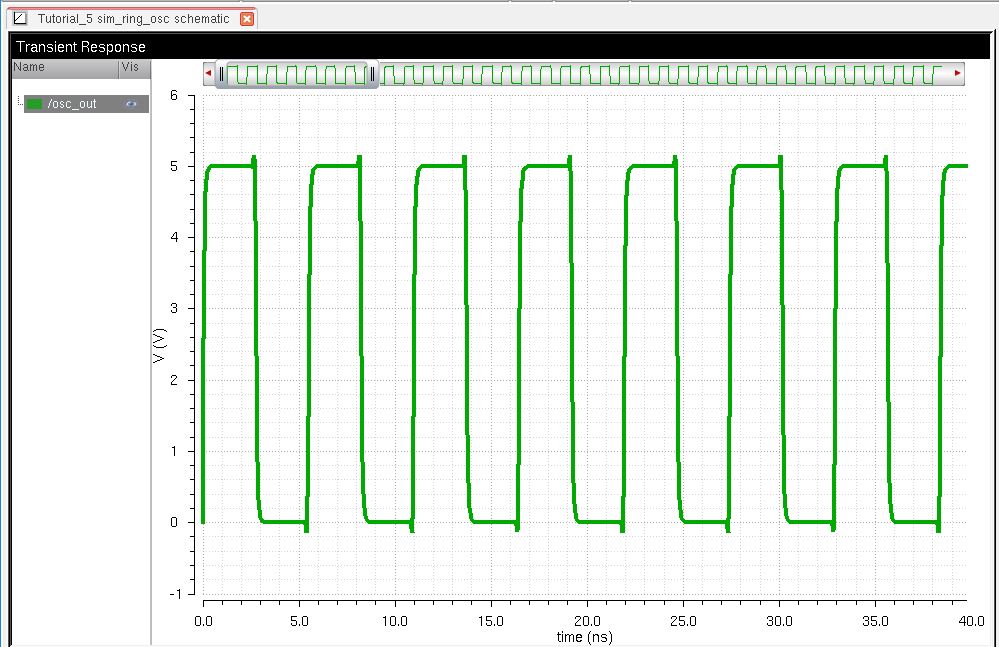

Initially, we want to place 31 inverters in series to create a ring oscillator

Initial ring oscillator schematic |  2nd circuit with simplified ring oscillator |

We can clearly see, they produce the same results, however, one is much easier to place in a large circuit.

From here, we should try to create a layout for these circuits - which can lead us to learn a few new tricks.

|  |

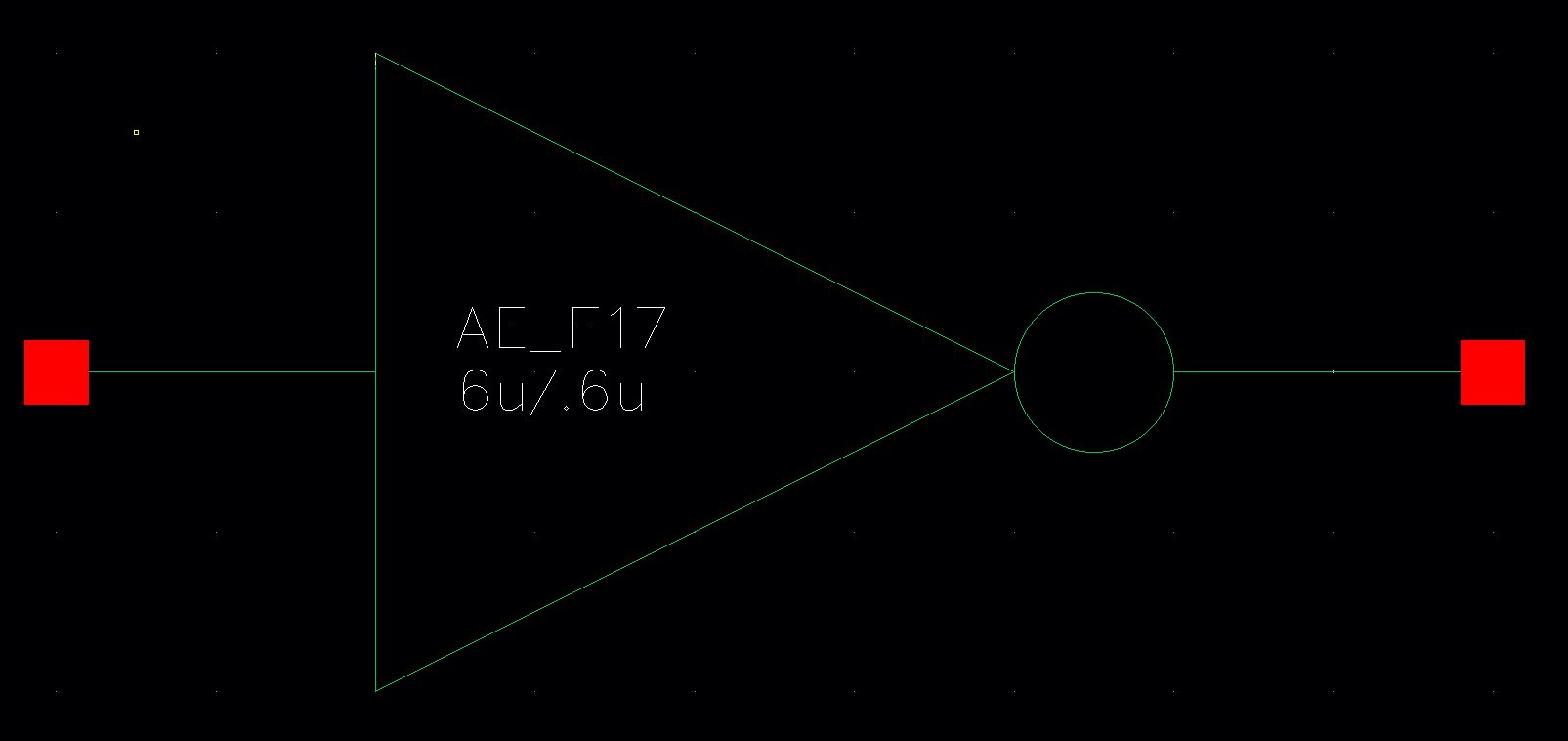

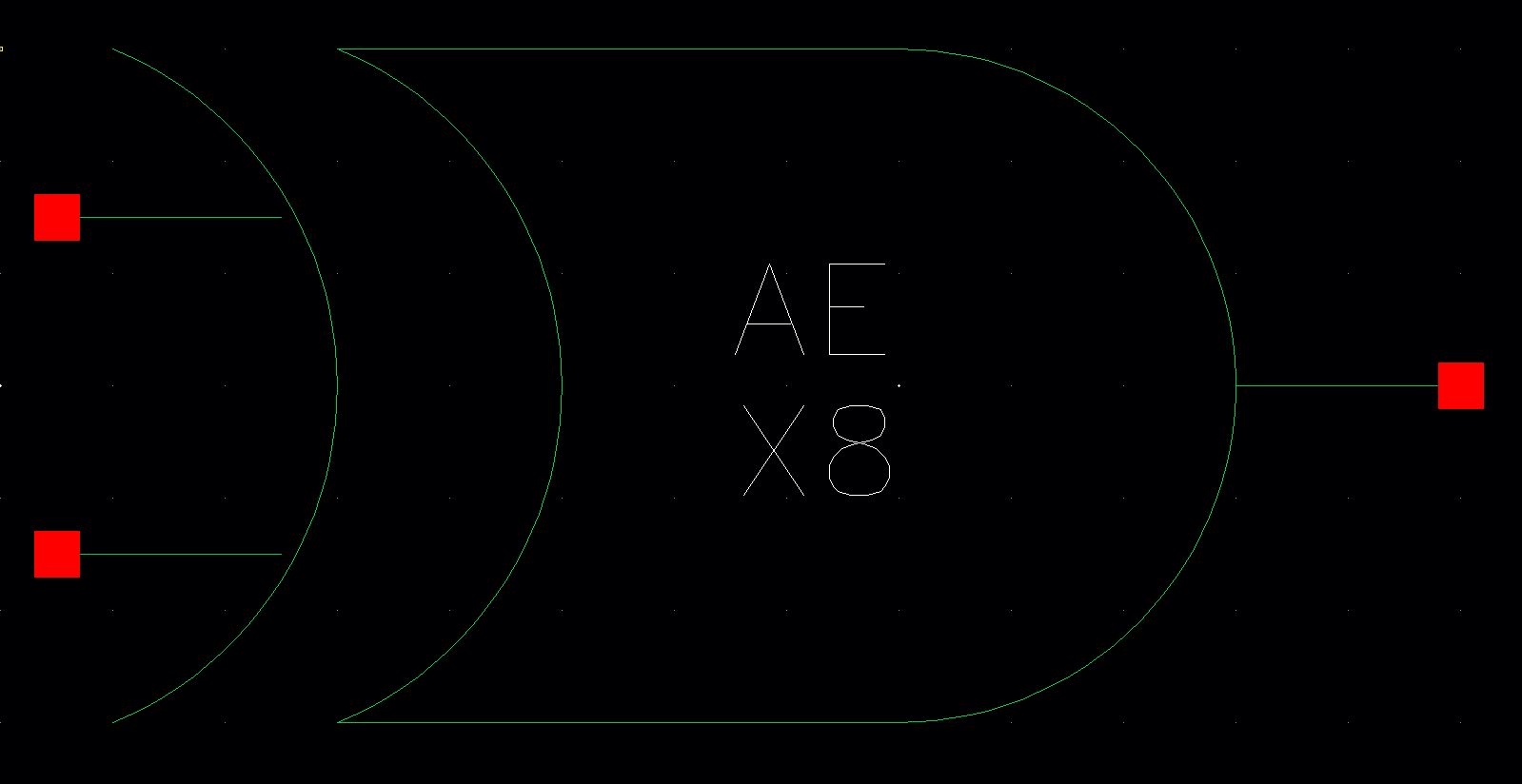

Initial schematic |  Created symbol |

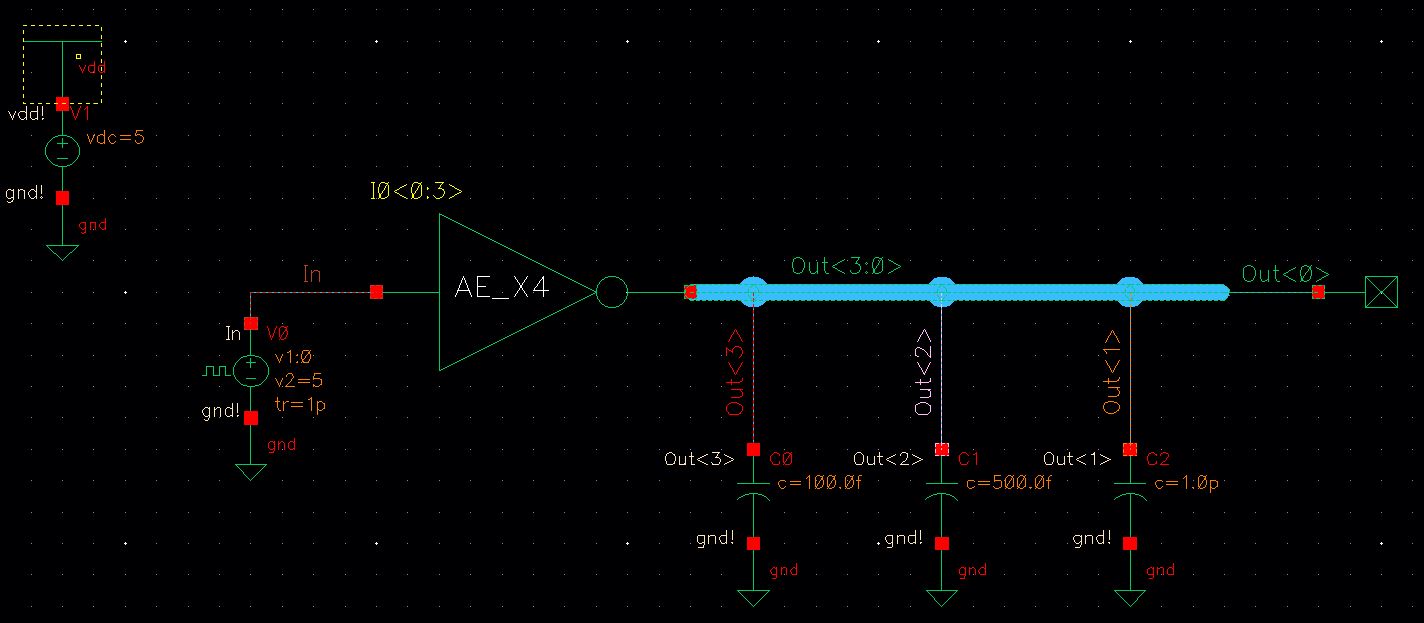

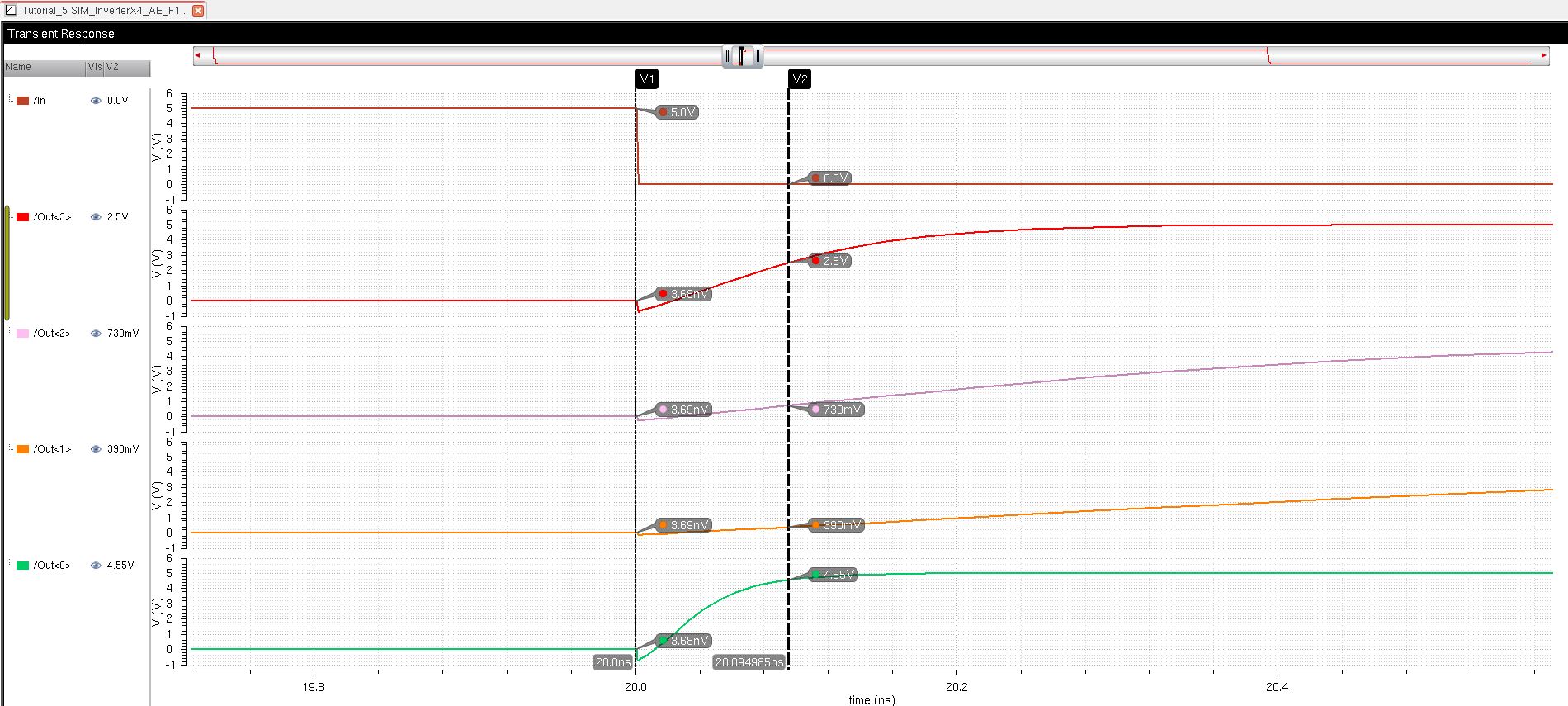

Simulation schematic |  Results |

6/0.6 Inverter Schematic |  Associated Symbol |

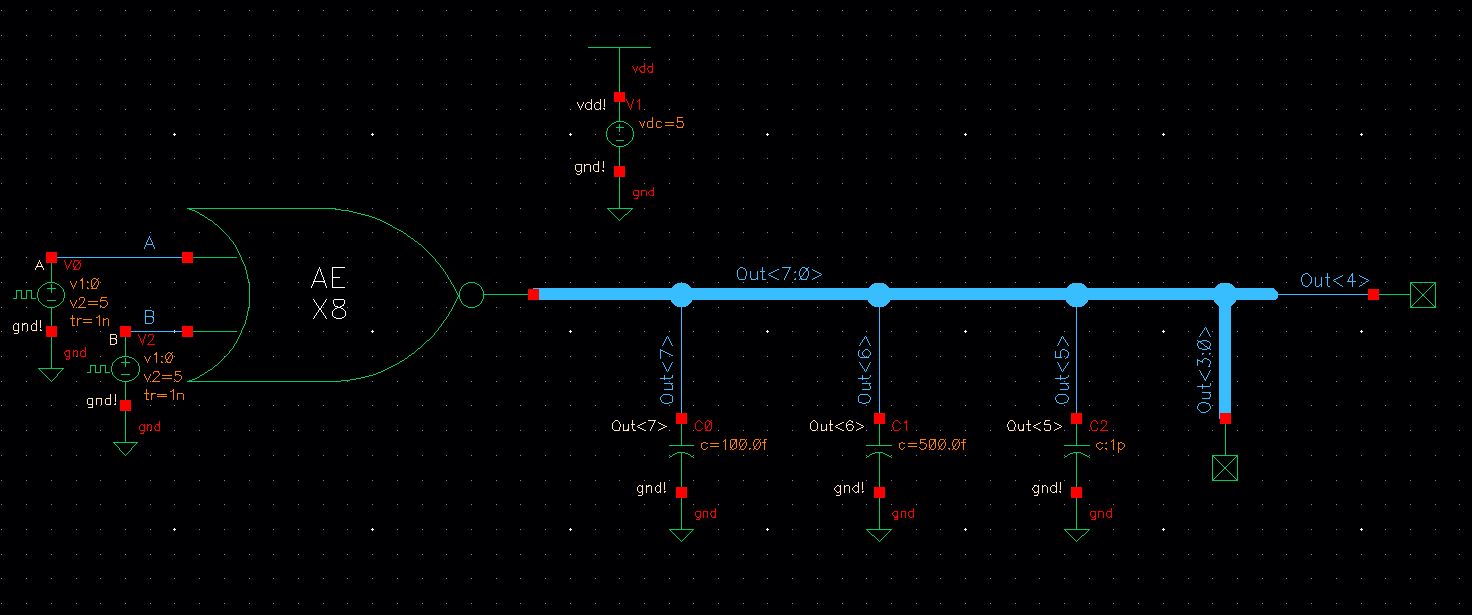

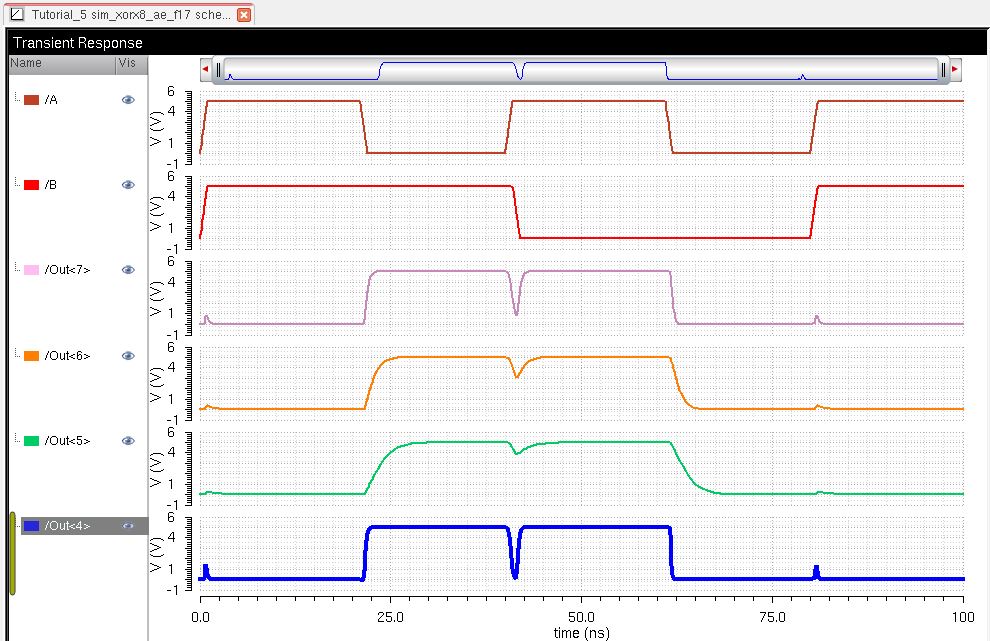

General outputs - we can see the delay difference between each node due to capacitors |  Zoomed in - we can see at Out<3>, it reached 1 time constants, while Out<2> and Out<1> are much slower |

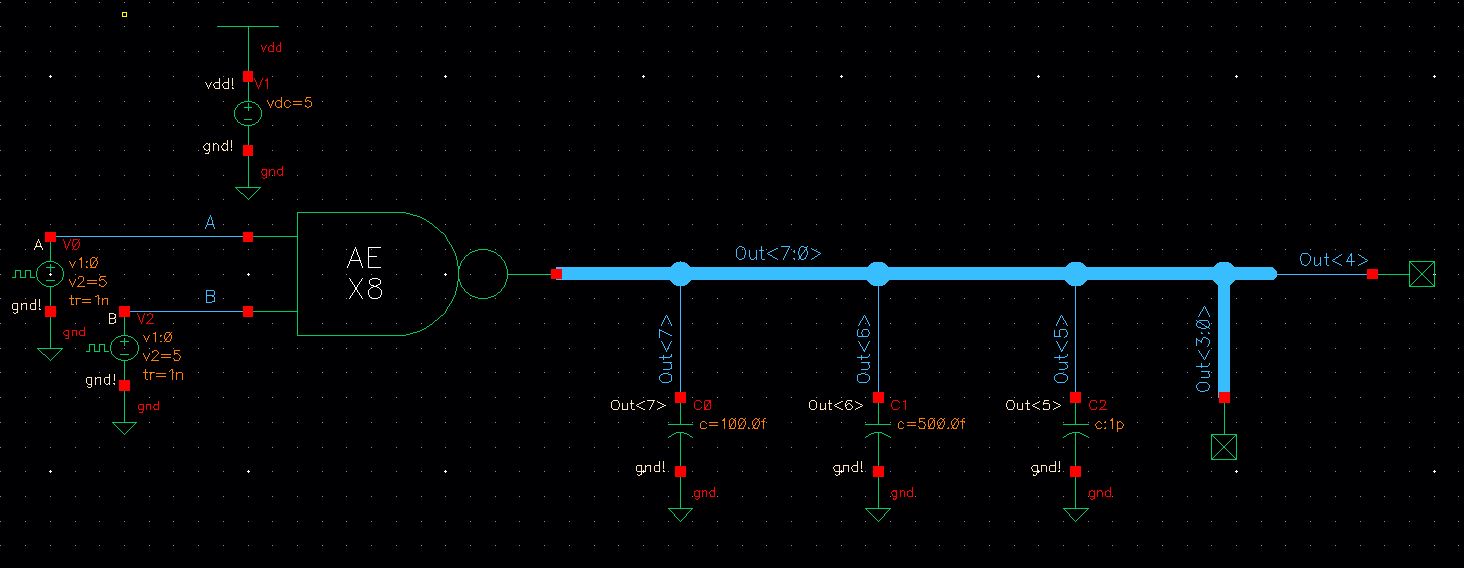

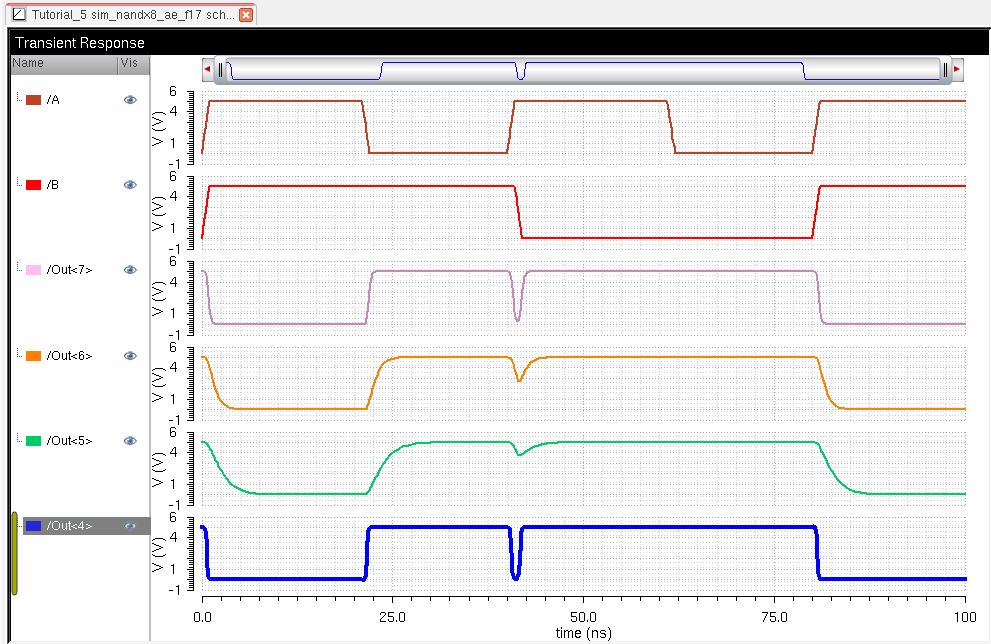

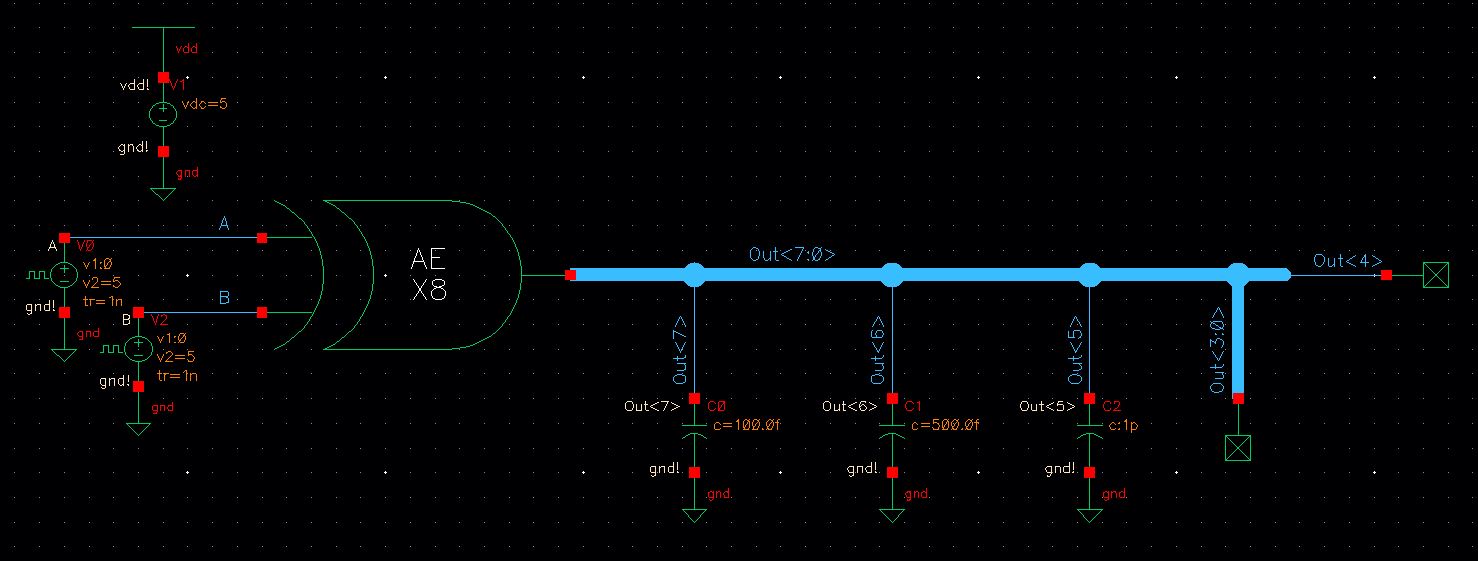

Now that we are familar with this process, we can do something similar to create an 8-bit version for an Inverter, NAND, AND, OR, XOR and NOR logic gates

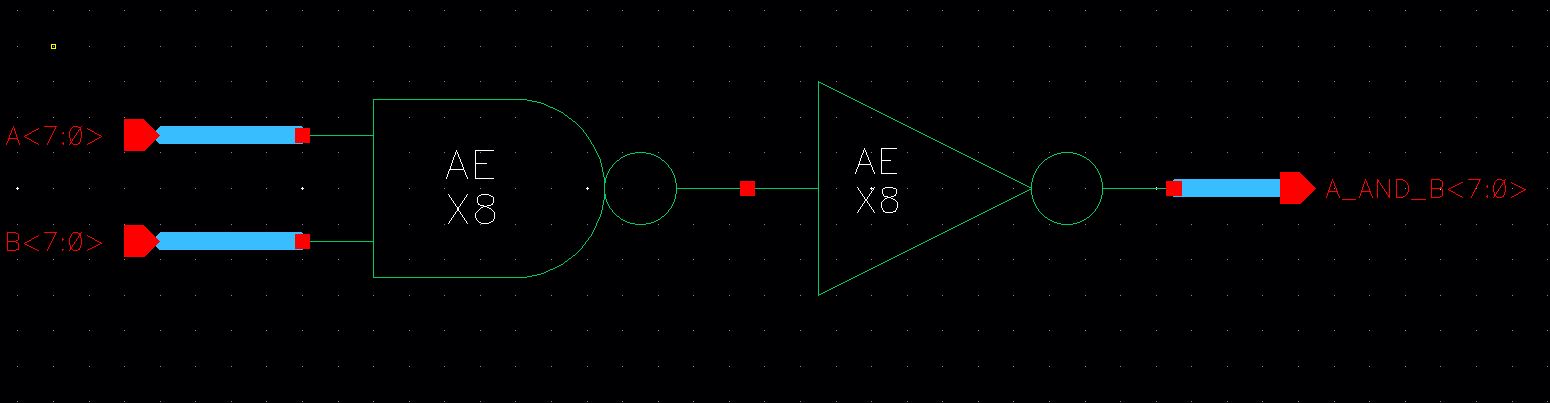

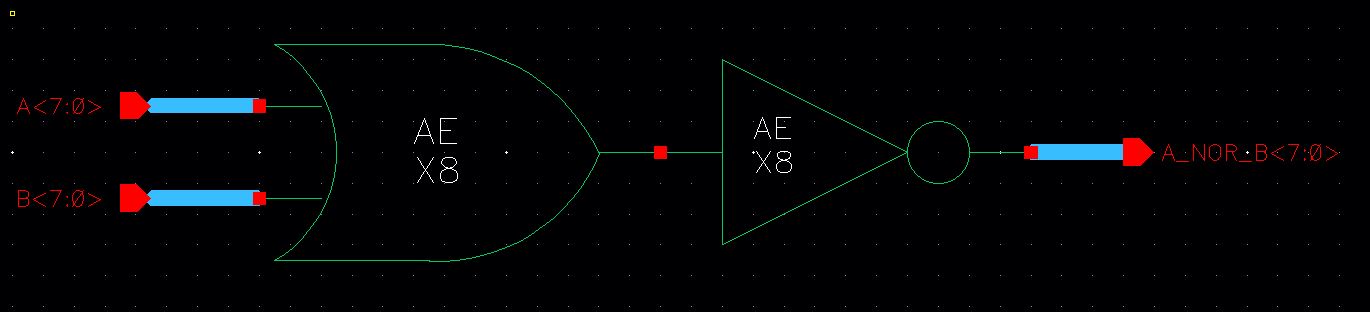

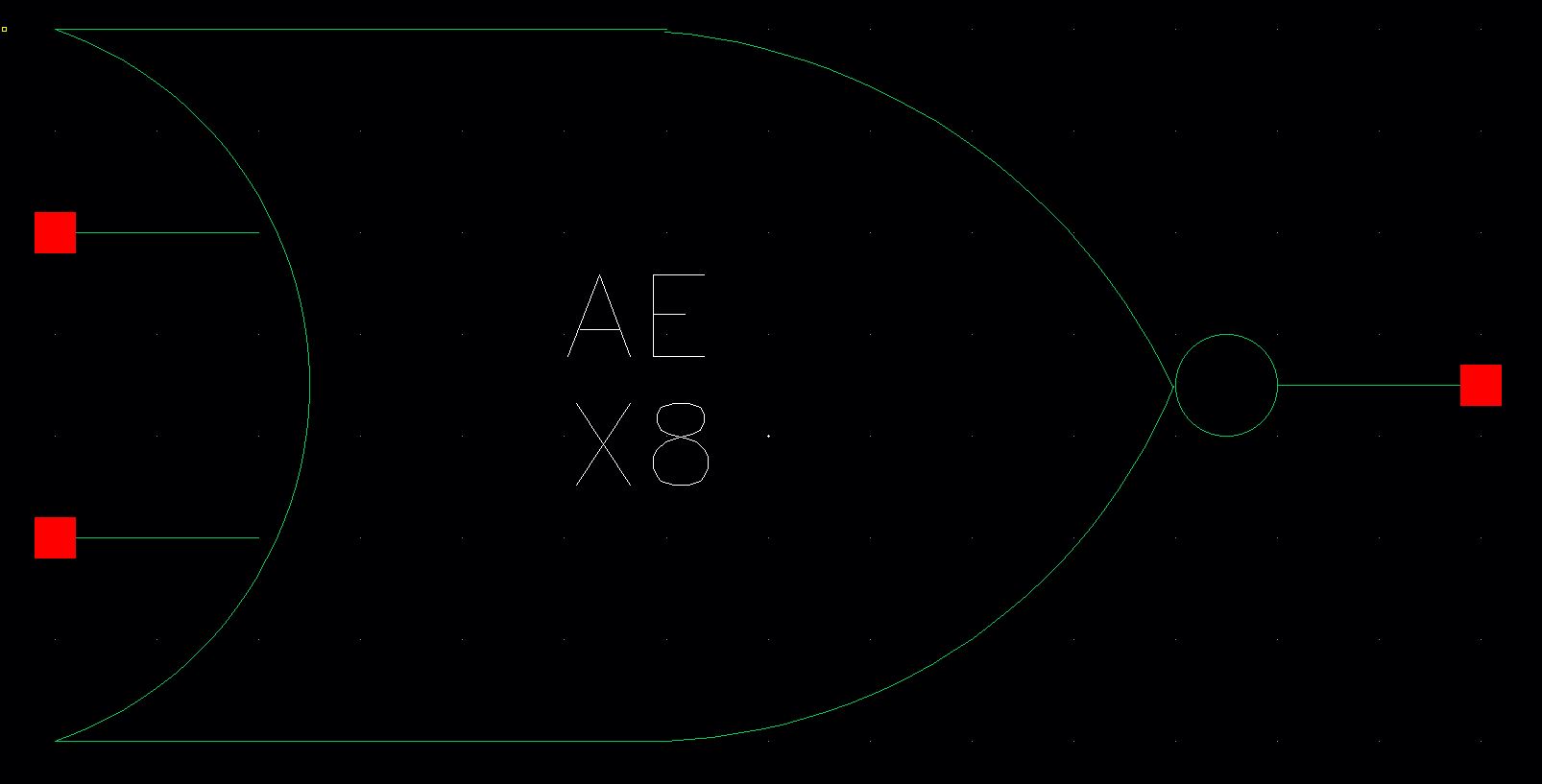

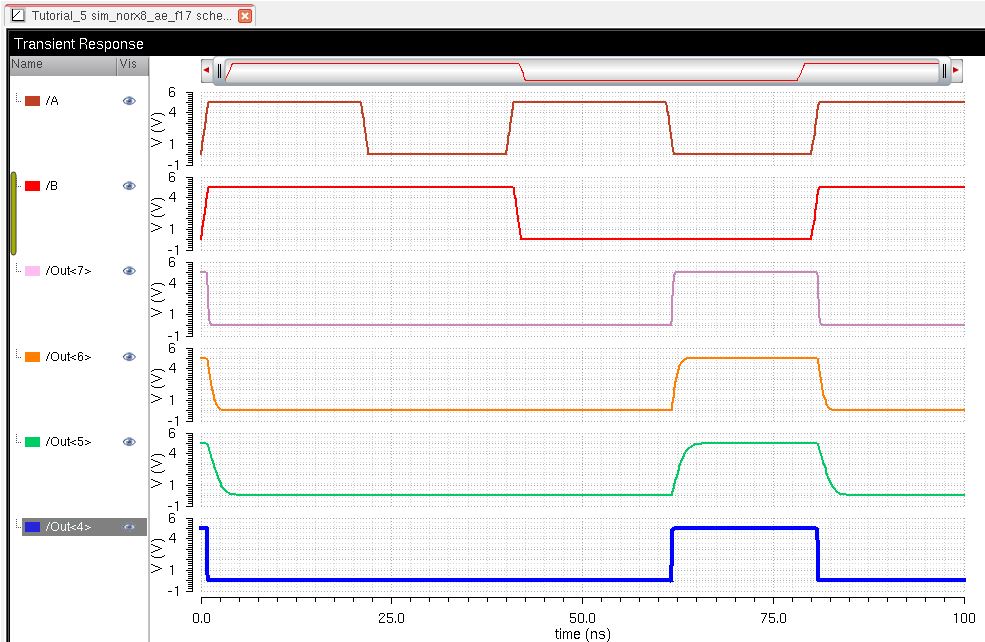

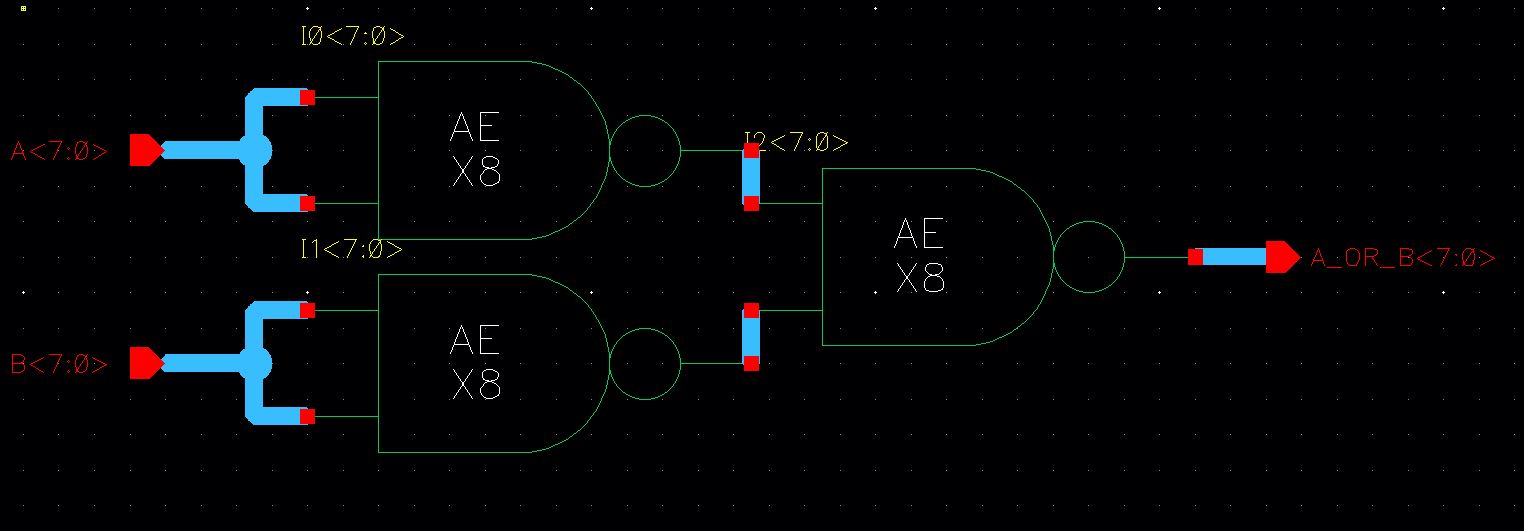

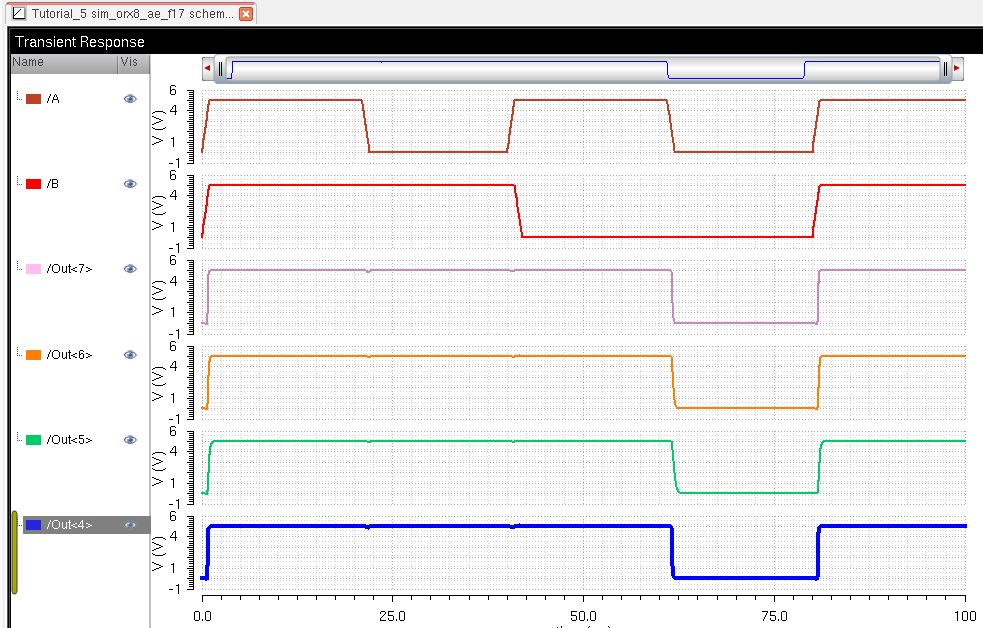

| Logic | Initial Schematic | Symbol | Simulation schematic | Results |

| 8 bit NAND |  |  |  |  |

| 8 bit AND |  |  |  |  |

| 8 bit NOR |  |  |  |  |

| 8 bit OR |  |  |  |  |

| 8 bit XOR |  |  |  |  |

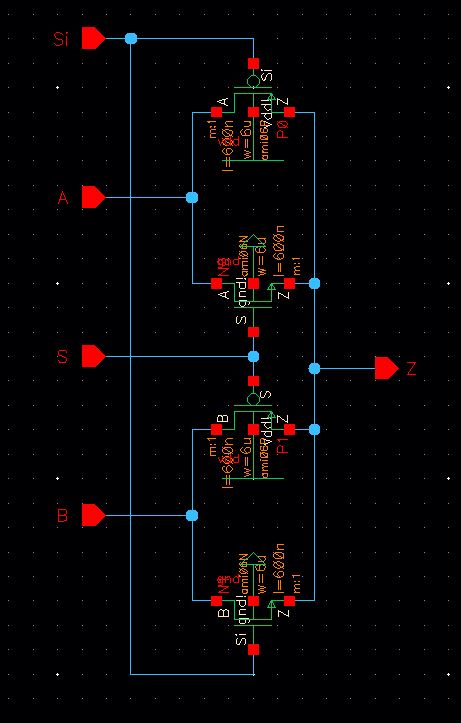

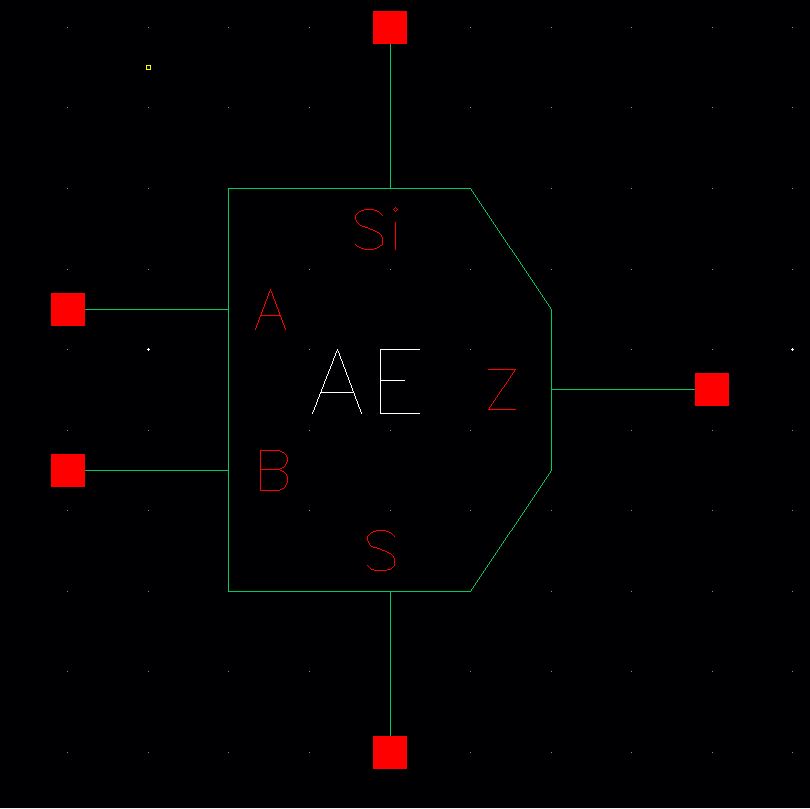

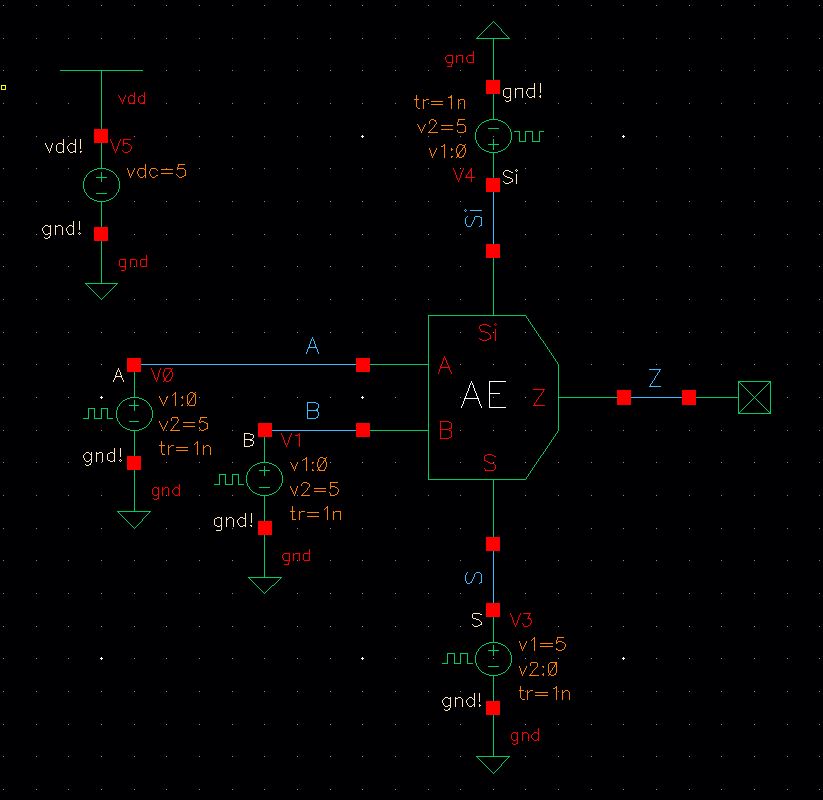

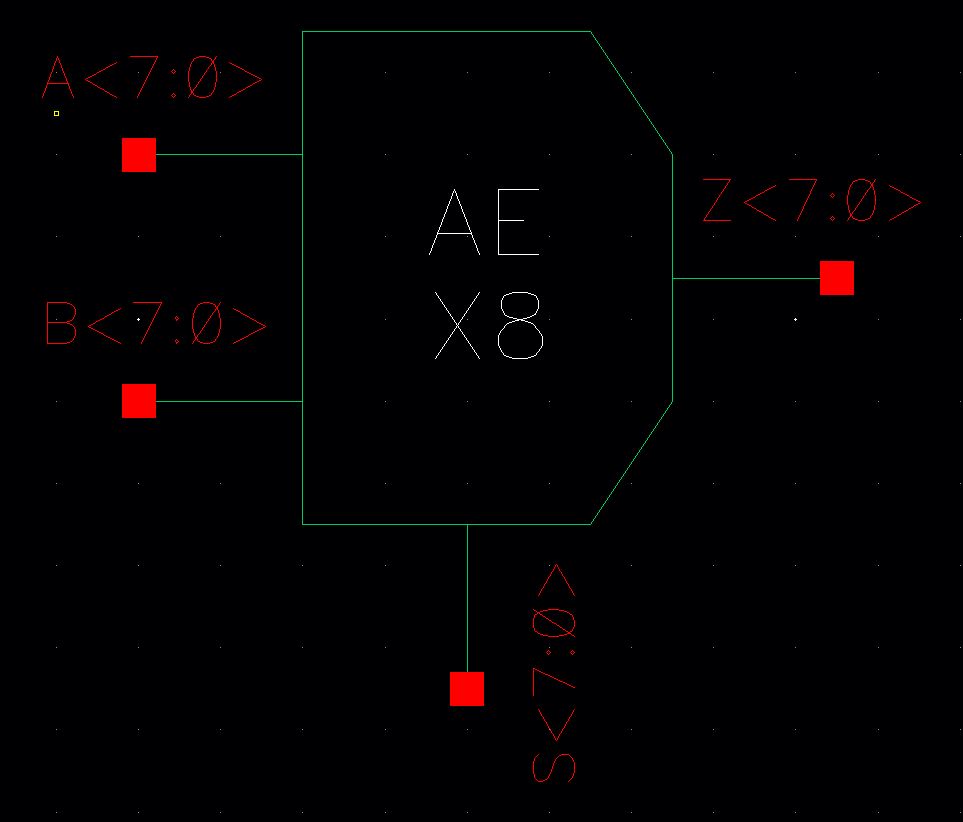

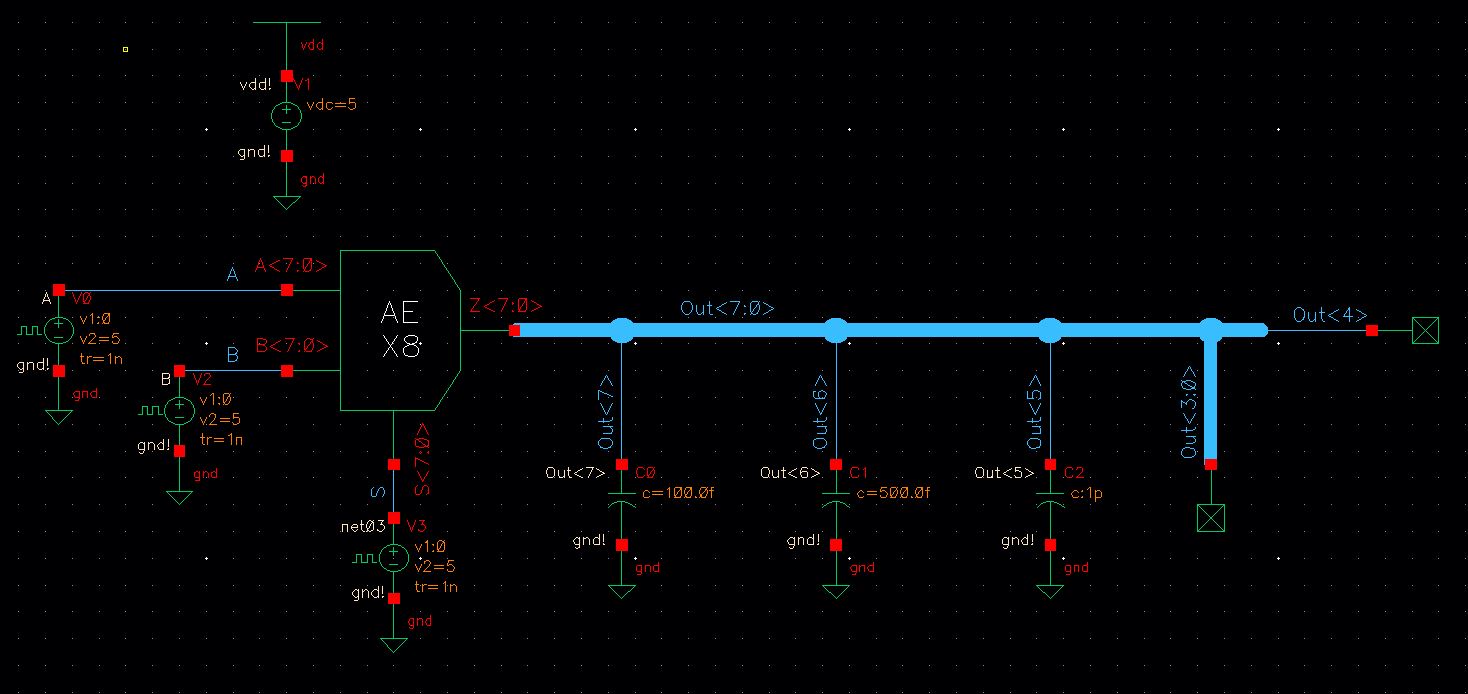

From here, we are next asked to create a 2-to-1 demux/mux as well as an 8-bit version of the same schematic; here are the results of that

| Logic | Initial Schematic | Symbol | Simulation schematic | Results |

| 2-to-1 MUX |  |  |  |  |

| 8 bit 2-to-1 MUX |  |  |  |  |

We can sere by looking at the schematic the functions of this circuit. We receive two inputs, A and B. but only 1 output. Which output is selected is determined by the logic of the S or Si input. If S is high, than the output is A, if Si is high (S is low) then the output is B. This defines a 2-to-1 MUX.

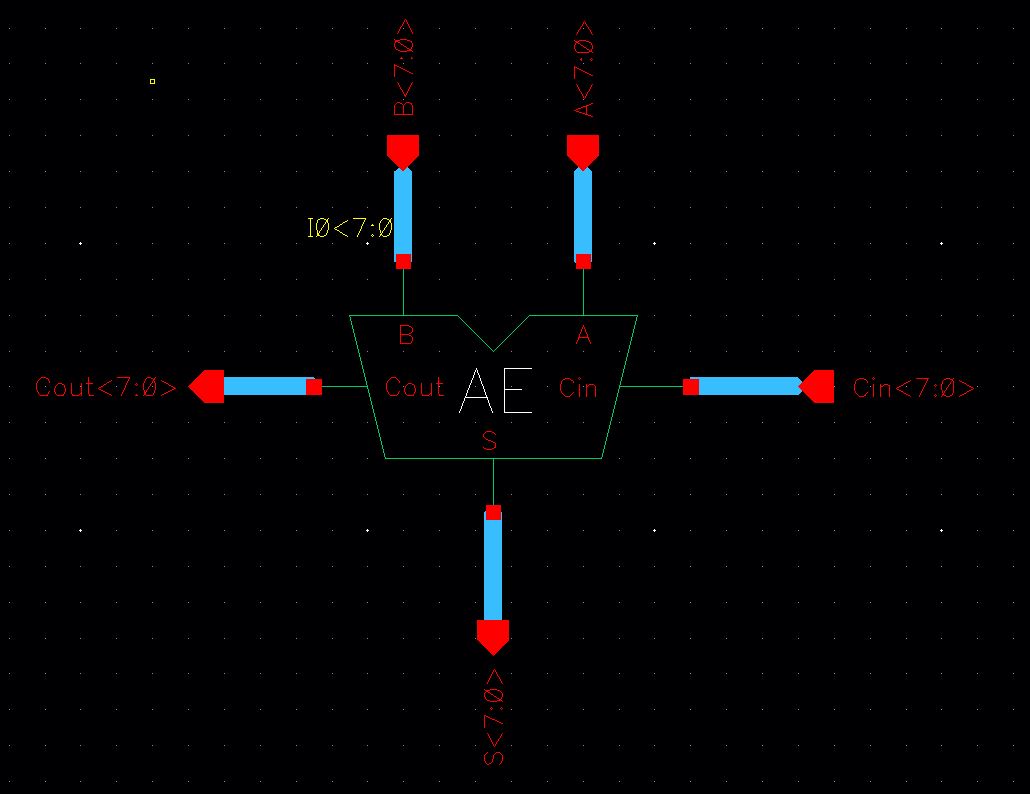

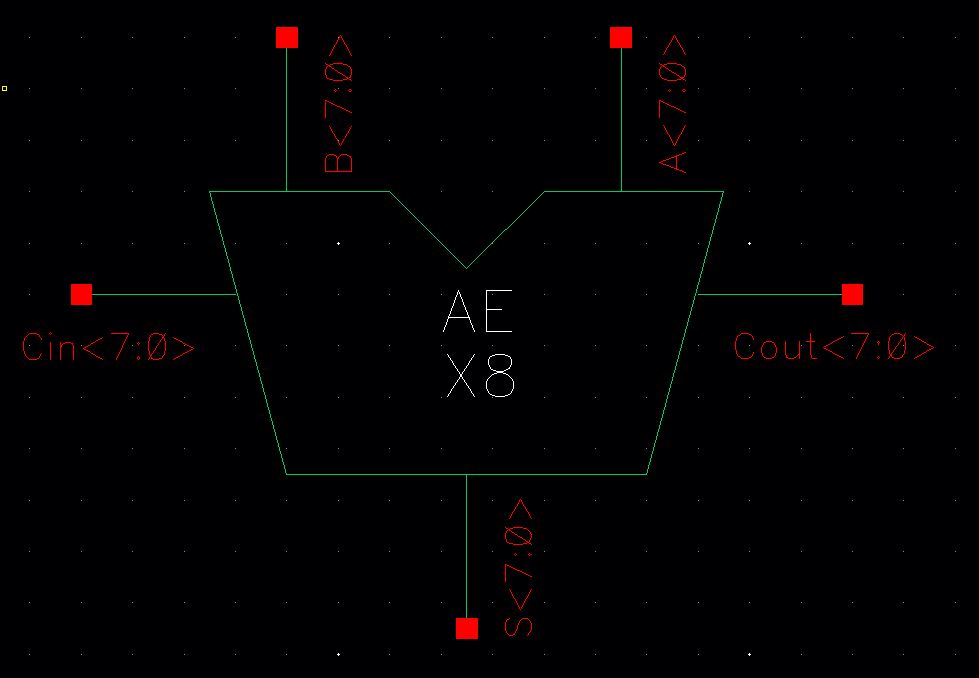

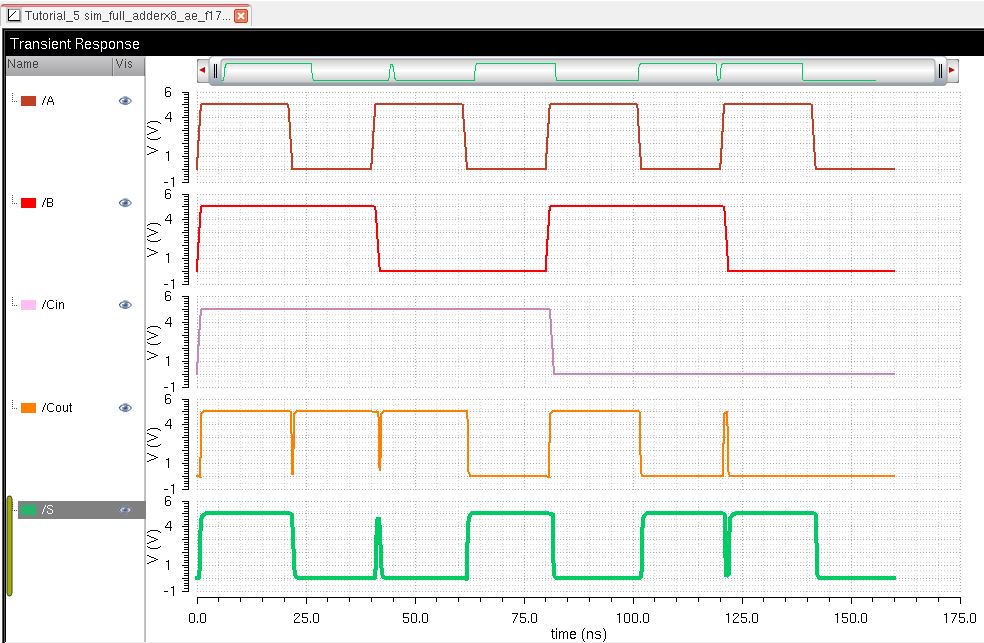

Finally, we were asked to create a full adder and an 8-bit version of a full adder - this is now shown below.

| Logic | Initial Schematic | Symbol | Simulation schematic | Results |

| full adder |  |  |  |  |

Here is my work backed up with a link to download and simulate all of these files