Lab 6 -

EE 421L

Authored

by Reiner Dizon,

Email: dizonr1@unlv.nevada.edu

Today's

date is October 18, 2017

Lab

description: This

lab is about designing and laying out CMOS NAND and XOR gates which will be used to create a full adder circuit.

PRELAB

- Back-up all of my work from the lab and the course

Lab Backup:

| Course Backup:

|

Schematic:

| Symbol:

|

After creating the NAND gate symbol,

I laid out the logic gate design and DRCed it. Since the

schematic and layout were already created, I performed LVS afterwards to

confirm if the netlists matched.

Finally,

I ran the

simulation on both the schematic and the layout, and the simulations

were identical. For the simulating the NAND gate schematic, I created a

simulation schematic with power and ground.

Simulation Schematic:

| Simulation Results:

|

- Read through the lab before starting

LAB

REPORT

1) Create schematic, symbol, and layout for 2-input NAND gate using 6u/0.6u (W/L ratio) MOSFETs

The

schematic and symbol for the 2-input NAND gate use those from Tutorial 4

(prelab). Since my design uses the ones from the prelab, I made a copy of that cell

view in order to make changes to them according to the lab

instruction. I added my initials "RD" in the center of the NAND gate to differentiate mine. Here are my schematic and symbol for the NAND gate.

Schematic:

| Symbol:

|

Before laying out this schematic, I made a standard cell frame for

all the gates in this lab. This cell allows me to easily wire power and

ground in the same places for all the gates, which helps make my

designs consistent. Since the MOSFETs in this lab have the W/L ratio of

6u/0.6u, I made frame size a bit larger than these dimensions to allow

for more space while wiring up multiple gates.

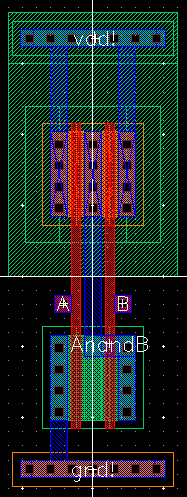

Since

the prelab used 12u/0.6u PMOS for the NAND gate, this does not match

the schematic given above. Therefore, I modified the layout to match

the ratio of 6u/0.6u for the PMOS transistor. Instead of simply

modifying the layout, I inserted my standard frame cell and moved

everything over to that cell. Since it had more space than the one from

the tutorial, I spread out the components within the frame. Afterwards,

I performed the DRC for the design. Here are my layout and DRC results:

Layout:

| DRC Results:

|

After

checking the layout for errors, I extracted the layout for the LVS tool

which will check it against the NAND gate schematic. Here are the extracted layout and the corresponding LVS results:

Extracted:

| LVS Results:

|

2) Create schematic, symbol, and layout for 2-input XOR gate using 6u/0.6u (W/L ratio) MOSFETs

For

the 2-input XOR gate, I had to make the schematic almost from scratch.

However, I copied some of my previous circuit onto this schematic (i.e.

inverter and NAND) and modified them according to the schematic given

in the lab instruction. The symbol, on the other hand, was created from

scratch. Just like the NAND gate symbol, I added my initials on it. Here are my schematic and symbol for the XOR gate.

Schematic:

| Symbol:

|

As done with the NAND gate layout, I used the standard cell frame as

the foundation of my layout. According to the schematic above, there

are four sets of NMOS/PMOS pairs (some with multipliers) that needs to

be laid out for the XOR gate, so I instantiated four standard frames.

As with these frames, I immediately connected all powers and grounds

accordingly. Moreover, since the are many metal1 connections in the

layout, I had to use metal2 to avoid crossing metal1 connections with other metal1's which would alter the design. Here are my layout and its DRC results:

Layout:

DRC Results:

After

checking the layout for errors, I extracted the layout for the LVS tool

which will check it against the XOR gate schematic. Here are the extracted layout and the corresponding LVS results:

Extracted:

LVS Results:

3) Logic gates simulation

Before simulation, I created a simple simulation schematic that contains all of the logic gates that I have created so far. Using

the Spectre tool in ADE, I simulated the logic gate (i.e. 12u/6u

inverter, NAND, XOR) operations for all possible 2-bit inputs on both

the schematics and the layouts. Here are my simulation schematic and results:

Schematic:

| Schematic Simulation:

|

Layout Simulation:

| Netlist Display (Proof):

|

Comment about glitching:

From

the above simulations, the transition between the input "01" and "10"

causes a glitch at the XOR output. Because both inputs are changing

voltage levels simultaneously, the rise and fall time (or transition

time) when these voltages are changing affects the output at the XOR

gate for that moment until it produces the proper output. Shrinking

this time will reduce or even eliminate this glitch.

4) Draft a full adder schematic and symbol

For

the full adder schematic, I used the NAND and XOR gates symbols from

previous parts of this lab to create my full adder schematic. It has

three inputs: a, b, & cin. Also, it has two outputs: sum &

cout. I also made the corresponding symbol. Here are my schematic and symbol for the full adder.

Schematic:

| Symbol:

|

5) Full adder layout

As

done with the full adder schematic, I imported the layouts for each

gate (3 NAND and 2 XOR) and placed them side-by-side, so I can connect

all power and ground connections. I used metal1 pins for inputs and

outputs of the full adder. I mostly used metal2 to connect between gate

pins, along with m2_m1 layouts. Here are my layout and its DRC results:

Layout:

DRC Results:

After DRCing, I extracted the layout and performed LVS

which will check it against the full adder schematic. Here are the extracted layout and the corresponding LVS results:

Extracted:

LVS Results:

6) Full adder simulation

Before simulating the full adder schematic and layouts, I created a simulation schematic. Using

the Spectre tool in ADE, I simulated the full adder operation for all

possible 3-bit inputs on both the schematics and the layouts. Here are

my simulation schematic and results:

Schematic:

Schematic Simulation:

Layout Simulation:

Netlist Display (Proof):

After finishing the lab, I backed up my lab 6 web directory from CMOSedu and library from the cluster:

Return

to Reiner's Labs

Return

to EE 421L Labs