Lab 07 - EE 421L

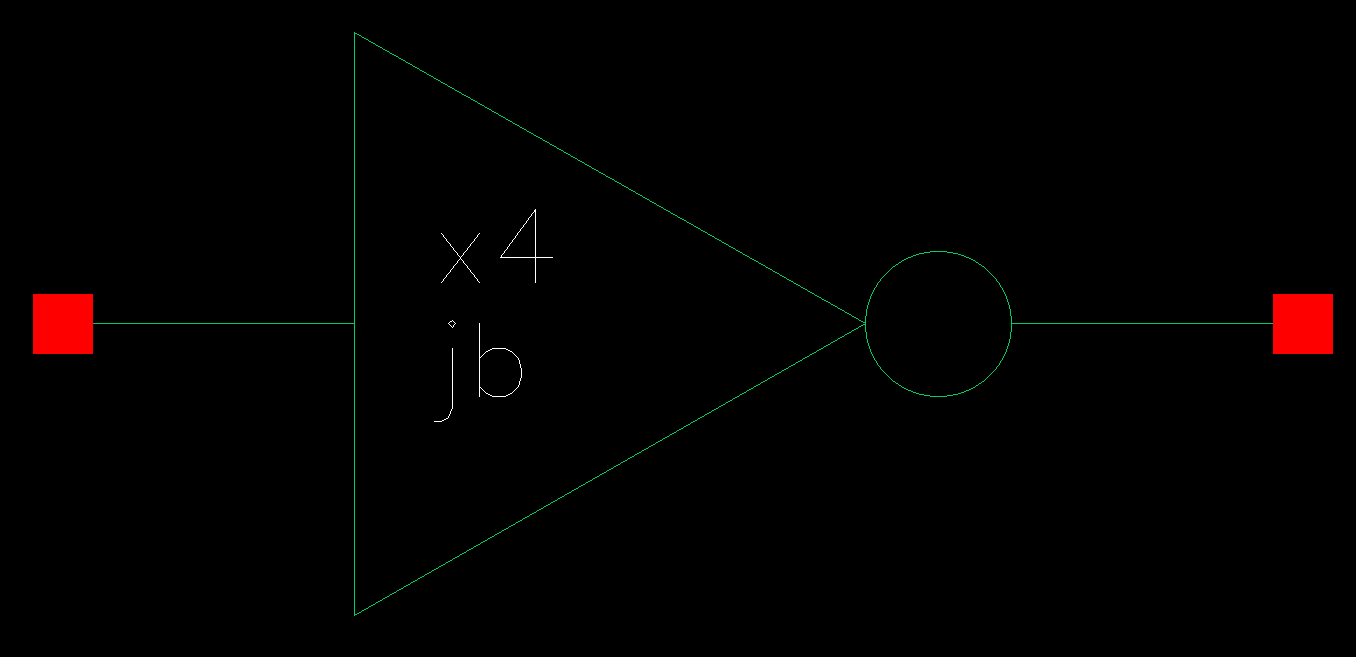

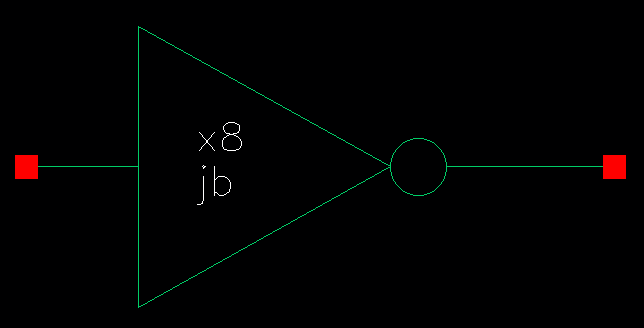

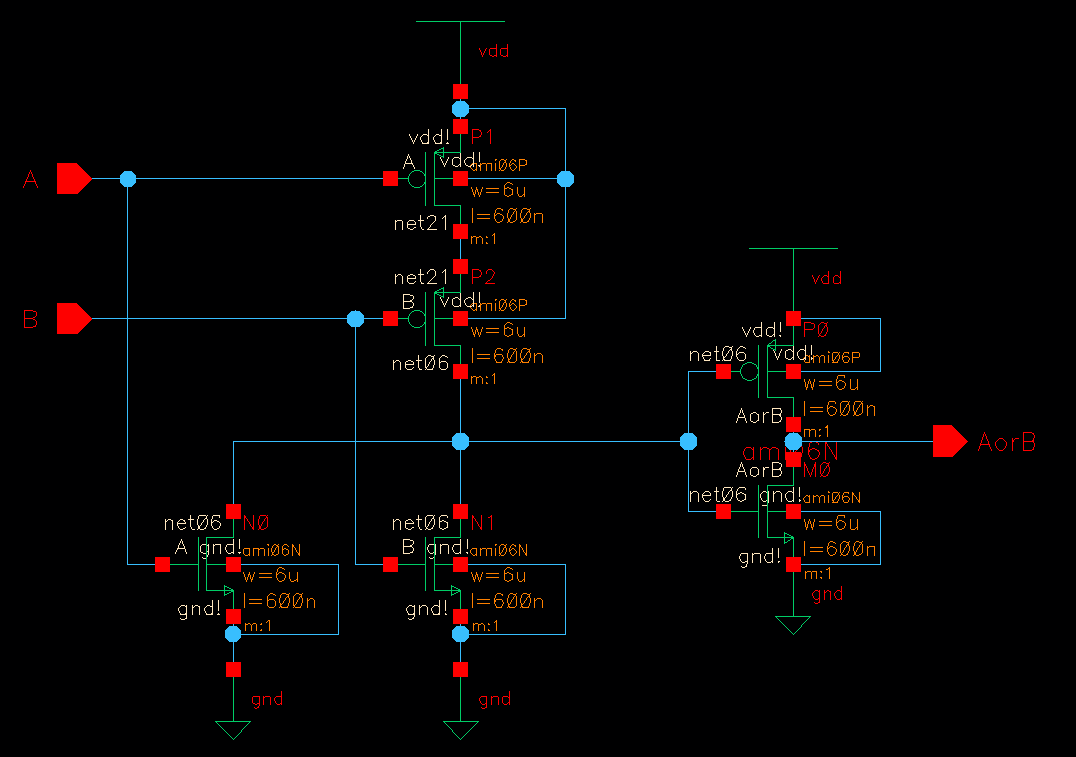

| Transistor-level Schematic | Concise Schematic | Symbol |

|  |  |

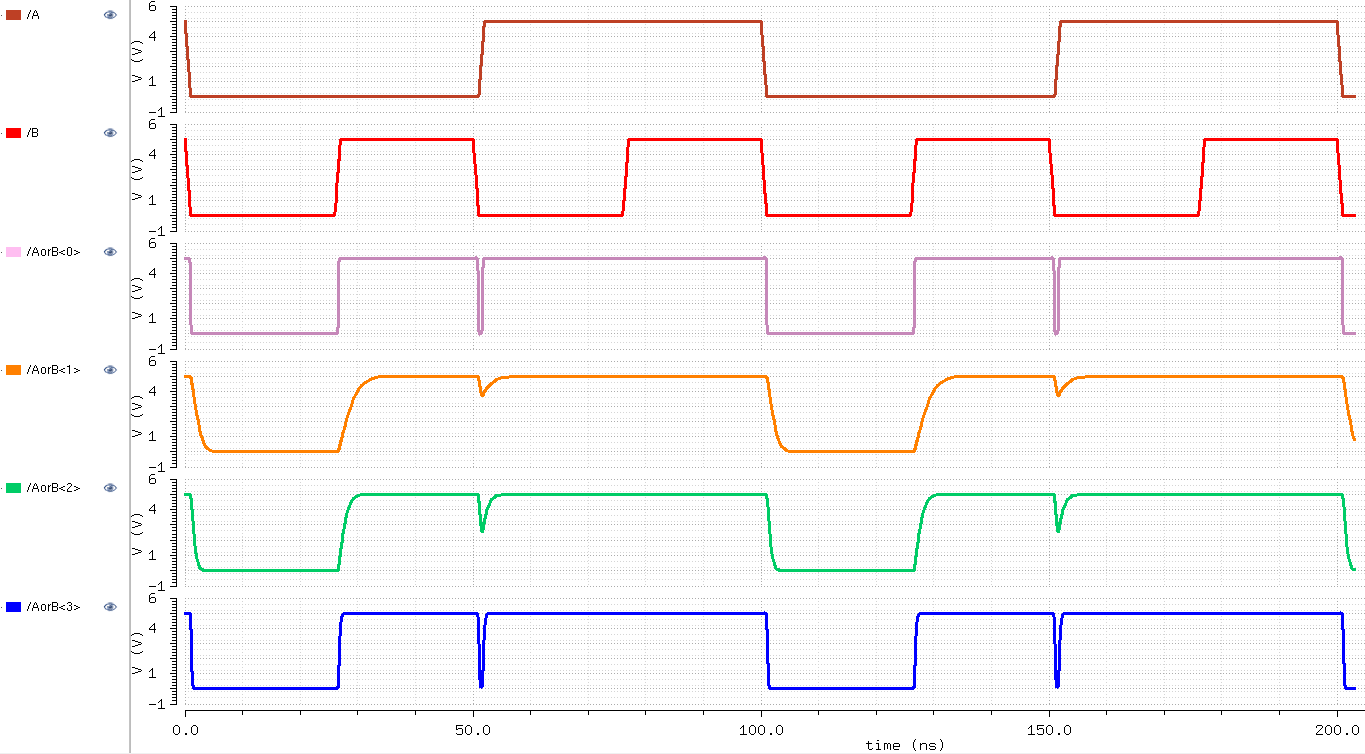

| Schematic of Simulation | Simulation Result |

|  |

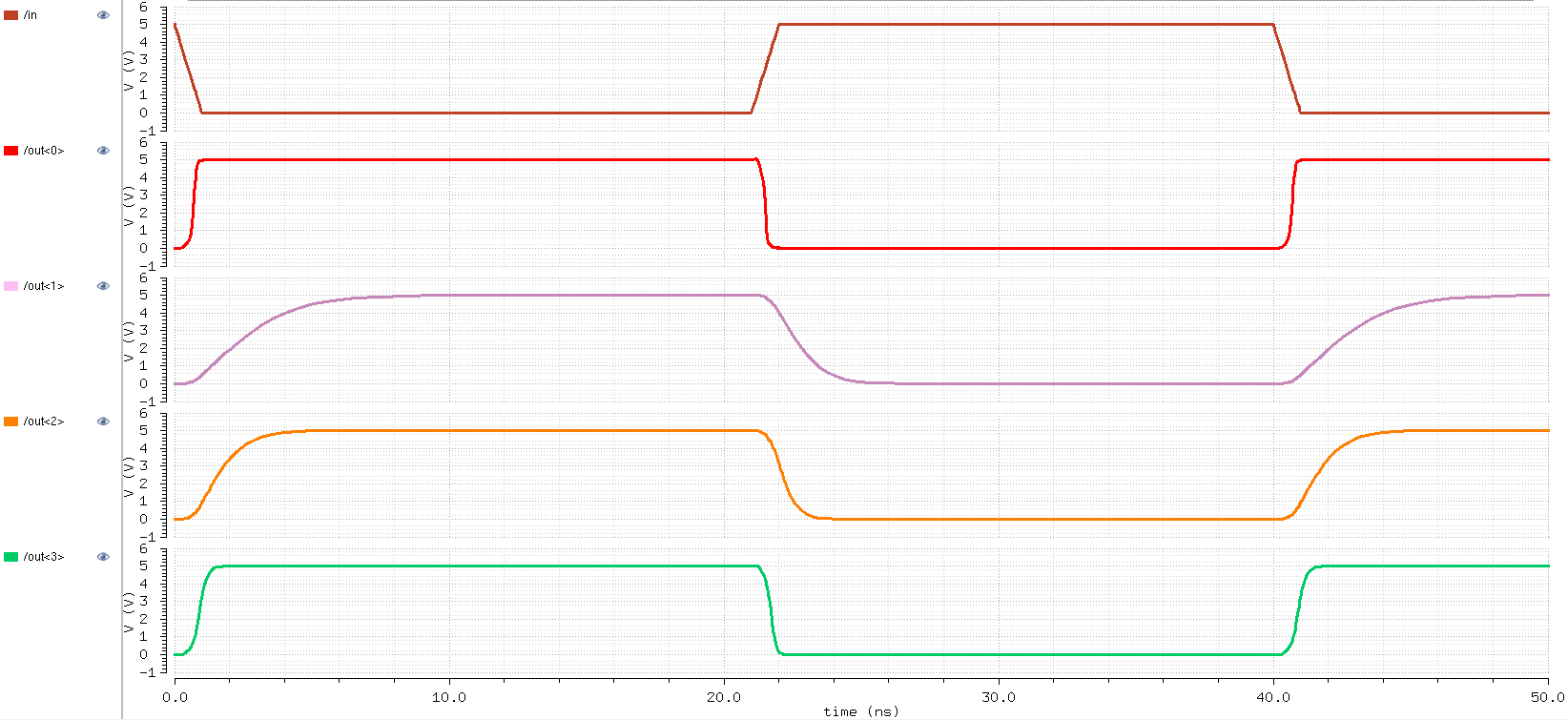

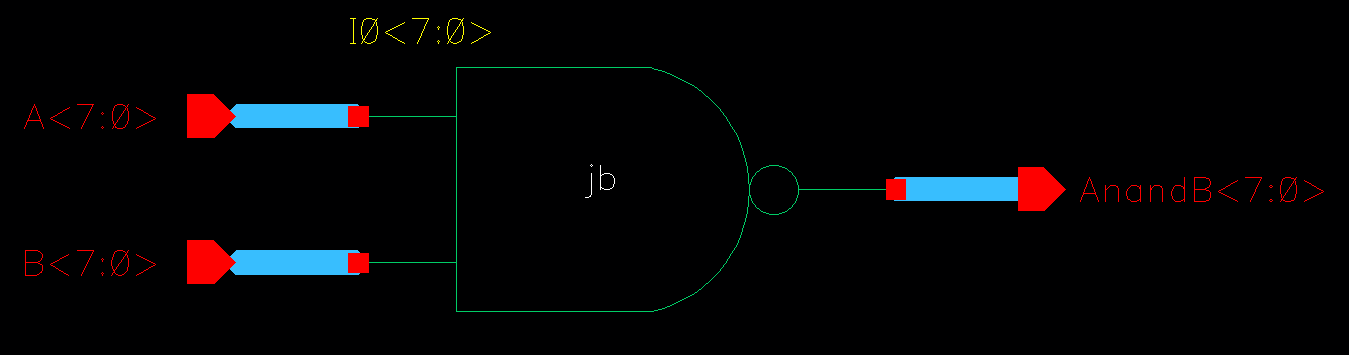

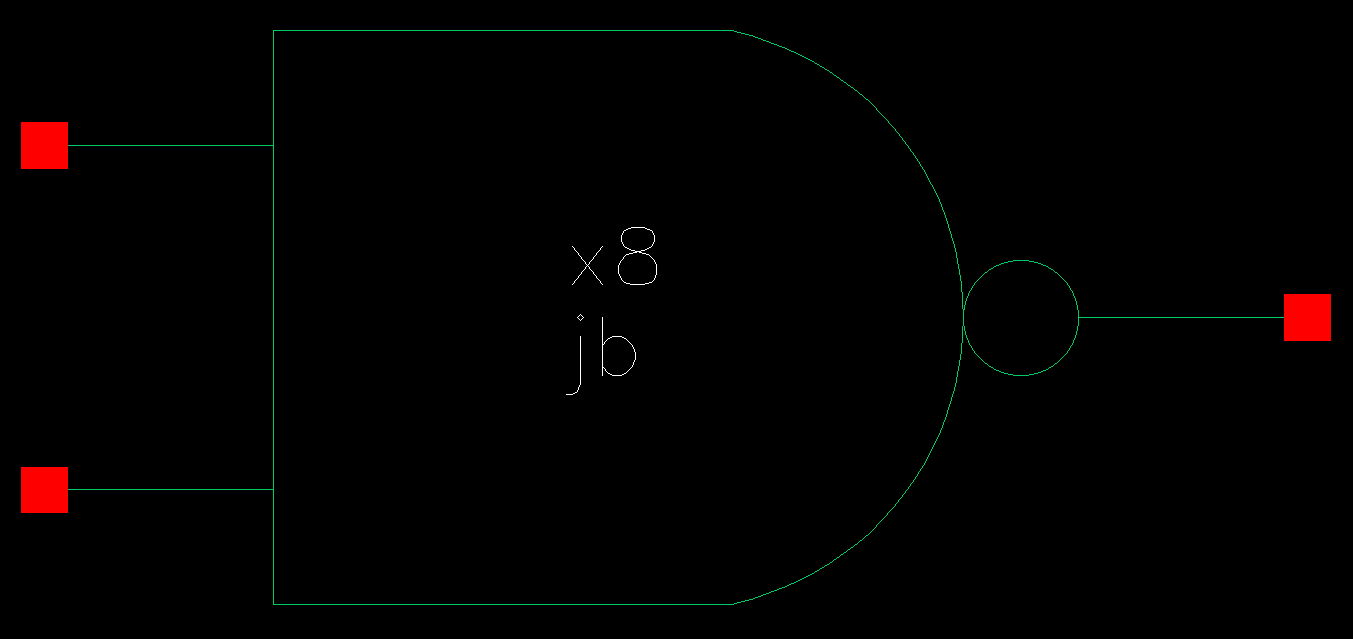

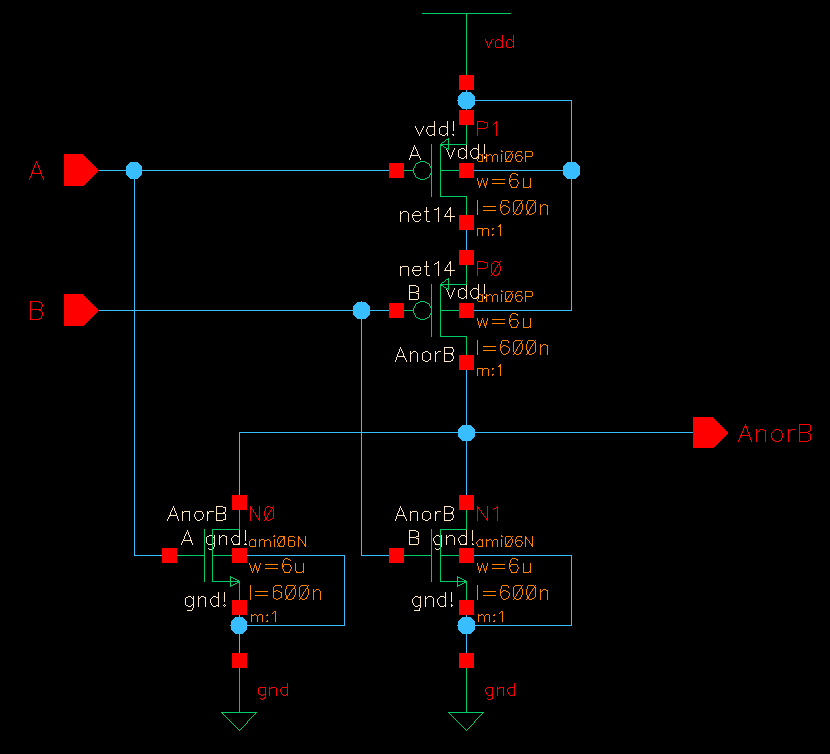

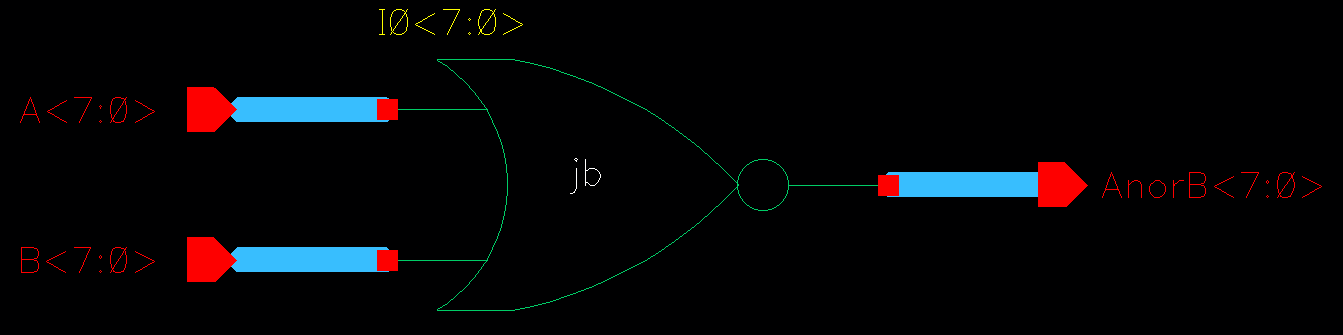

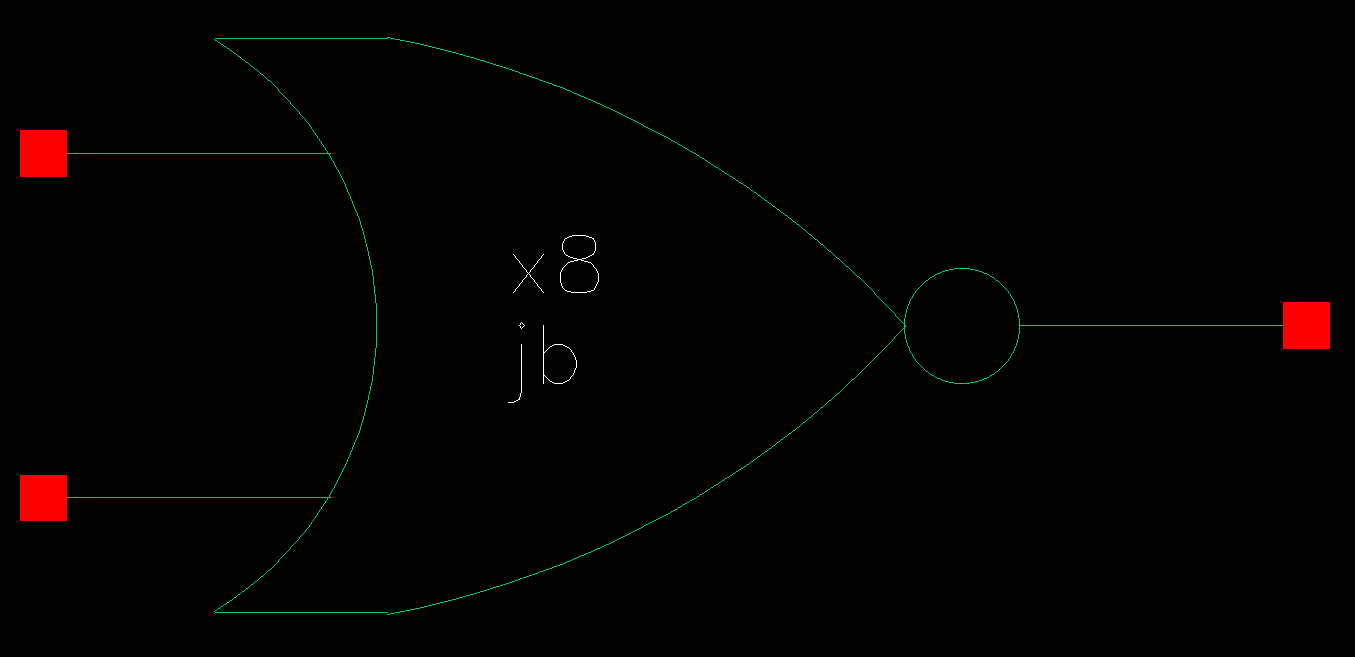

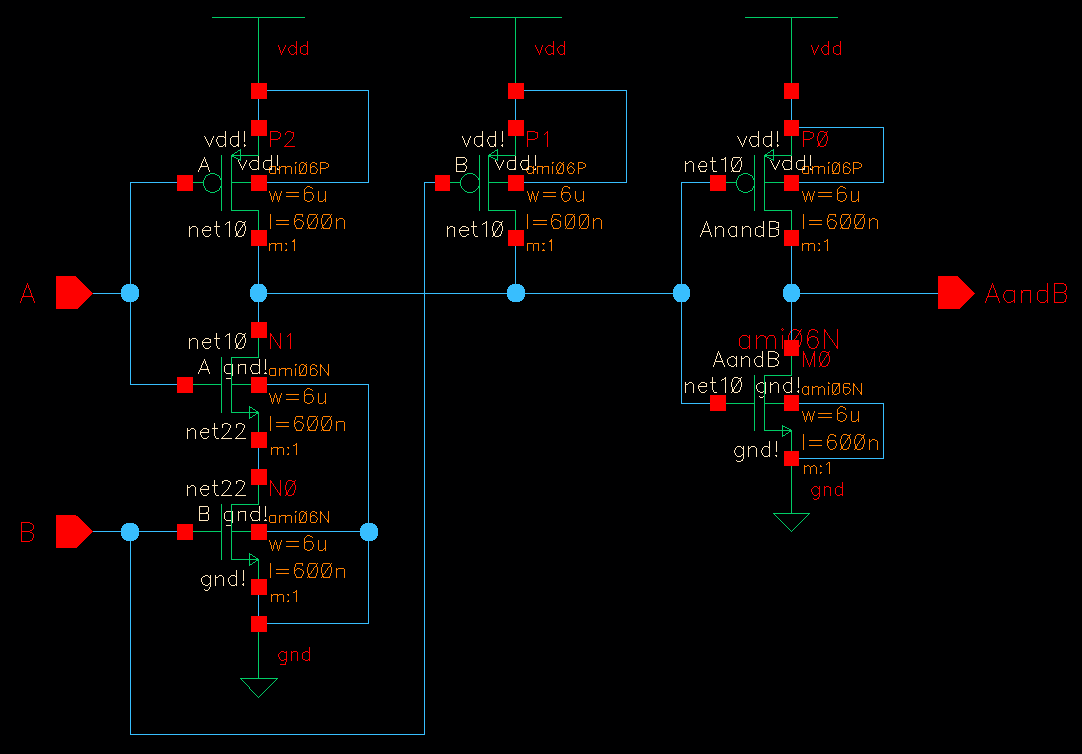

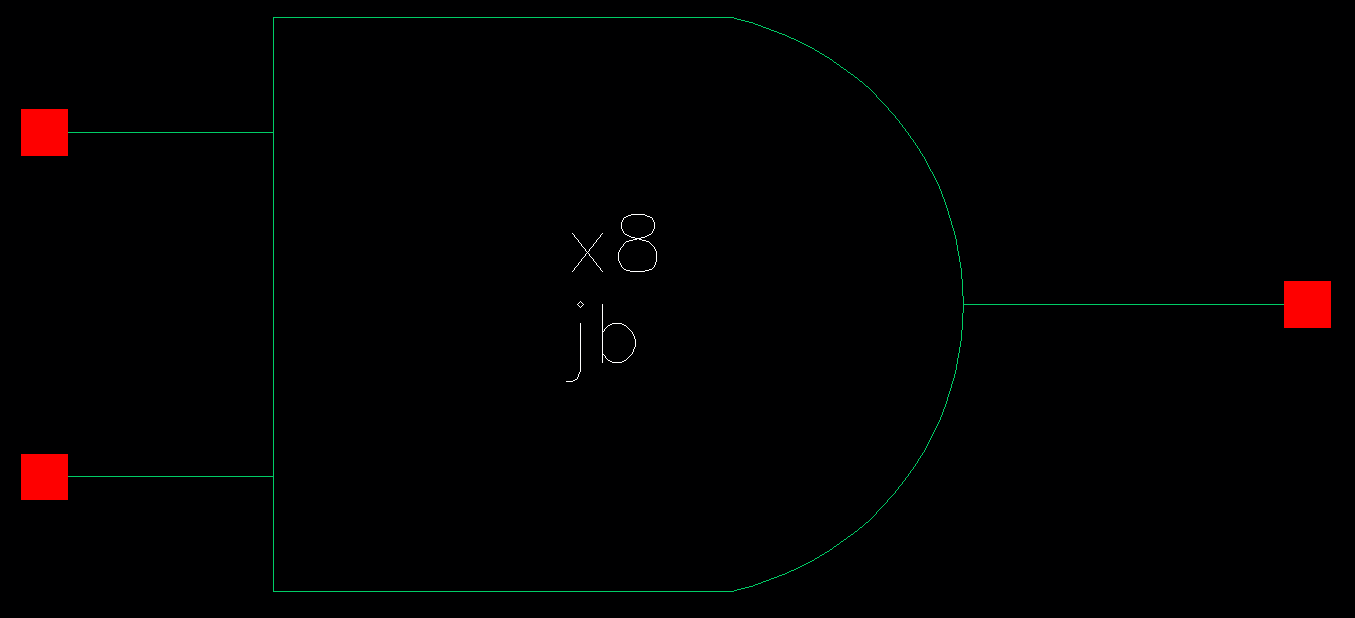

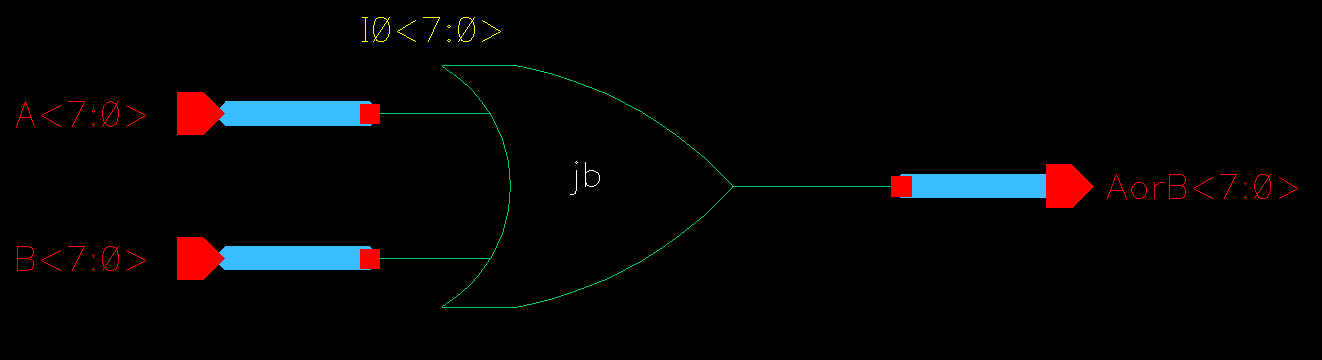

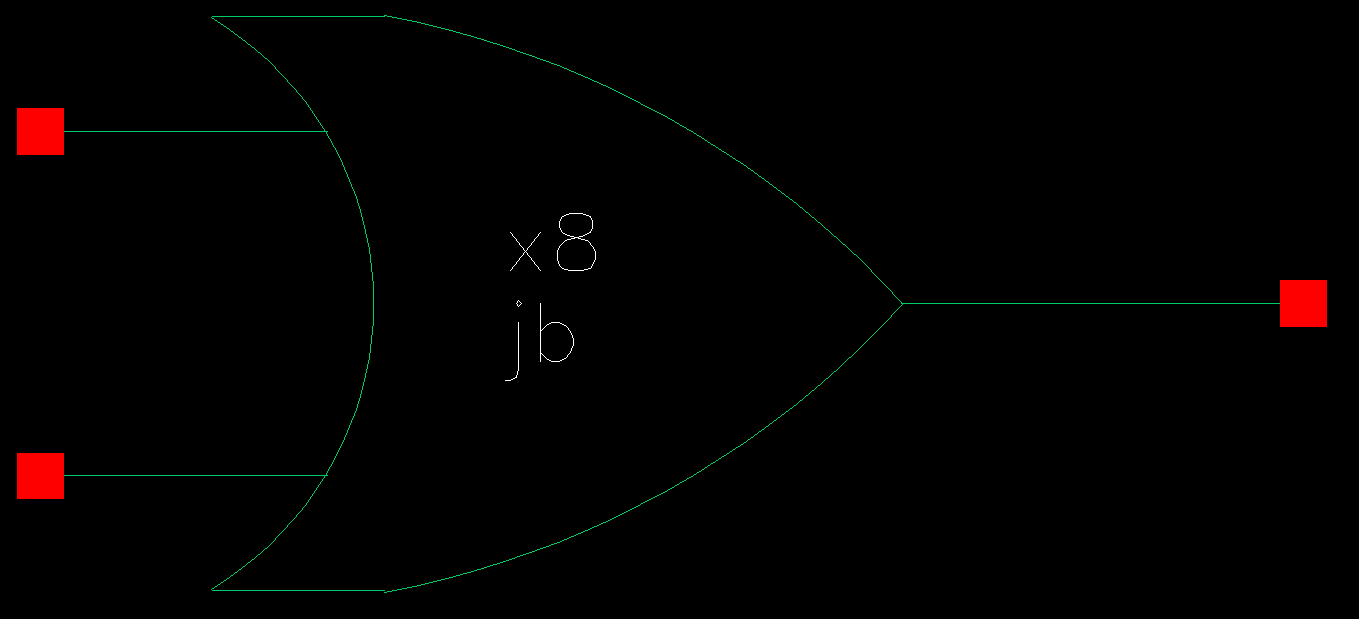

| Logic Gate | Transistor-level Schematic | Concise Schematic | Symbol |

| NAND |  |  |  |

| NOR |  |  |  |

| AND |  |  |  |

| inverter |  |  |  |

| OR |  |  |  |

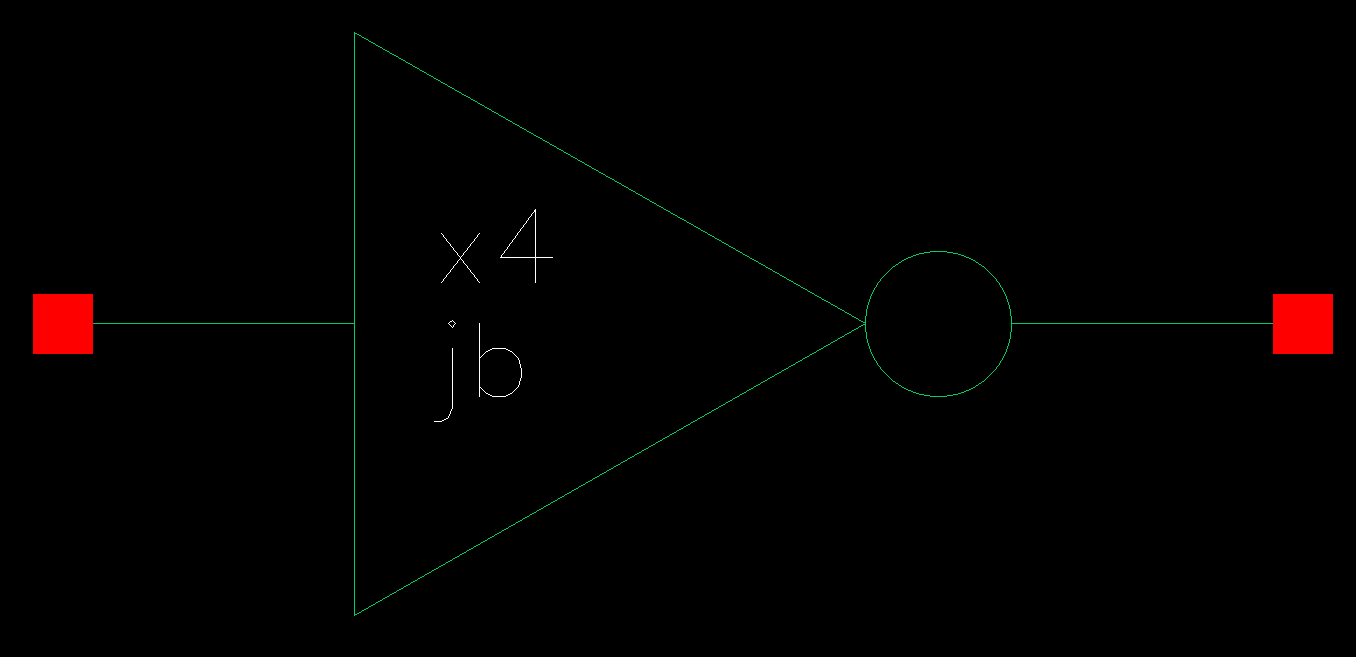

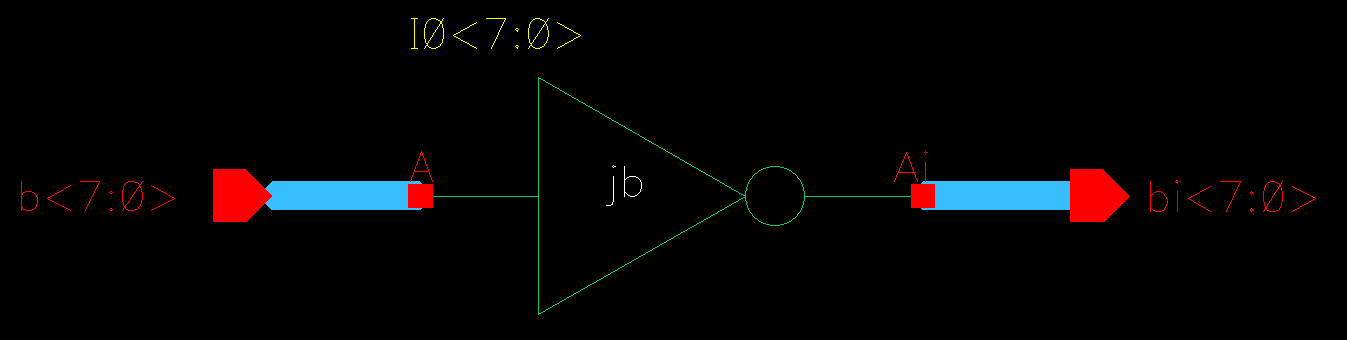

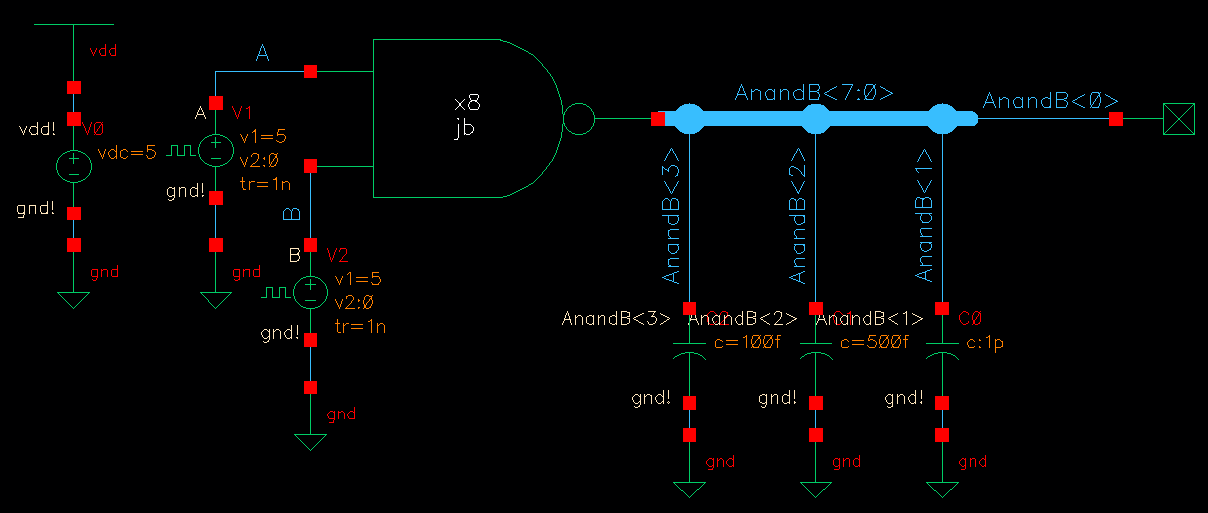

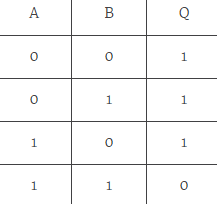

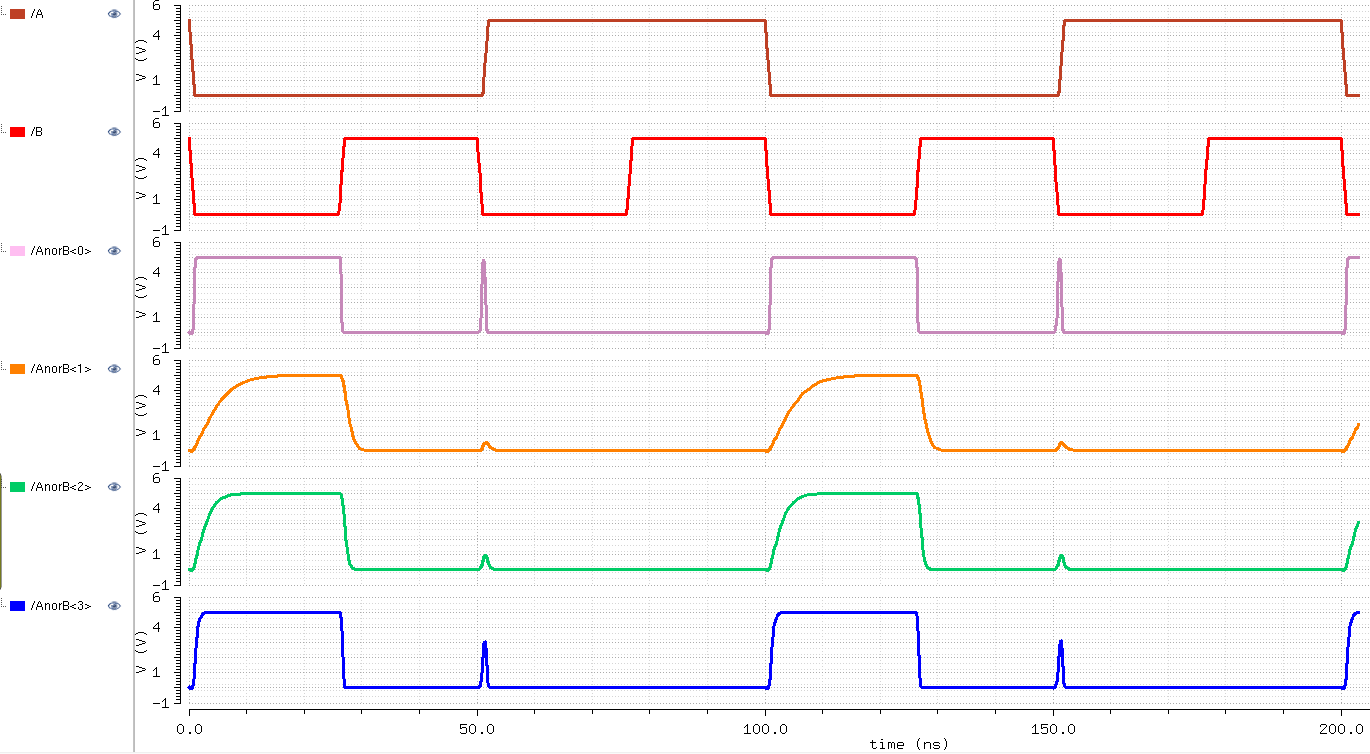

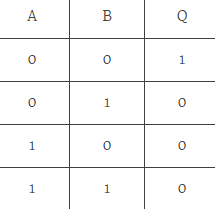

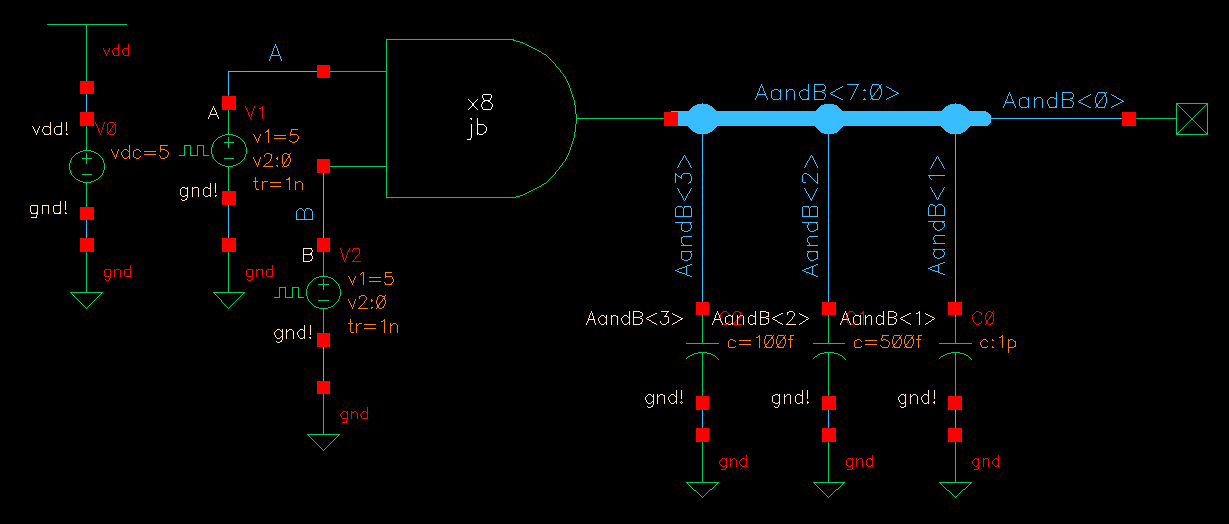

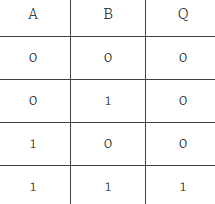

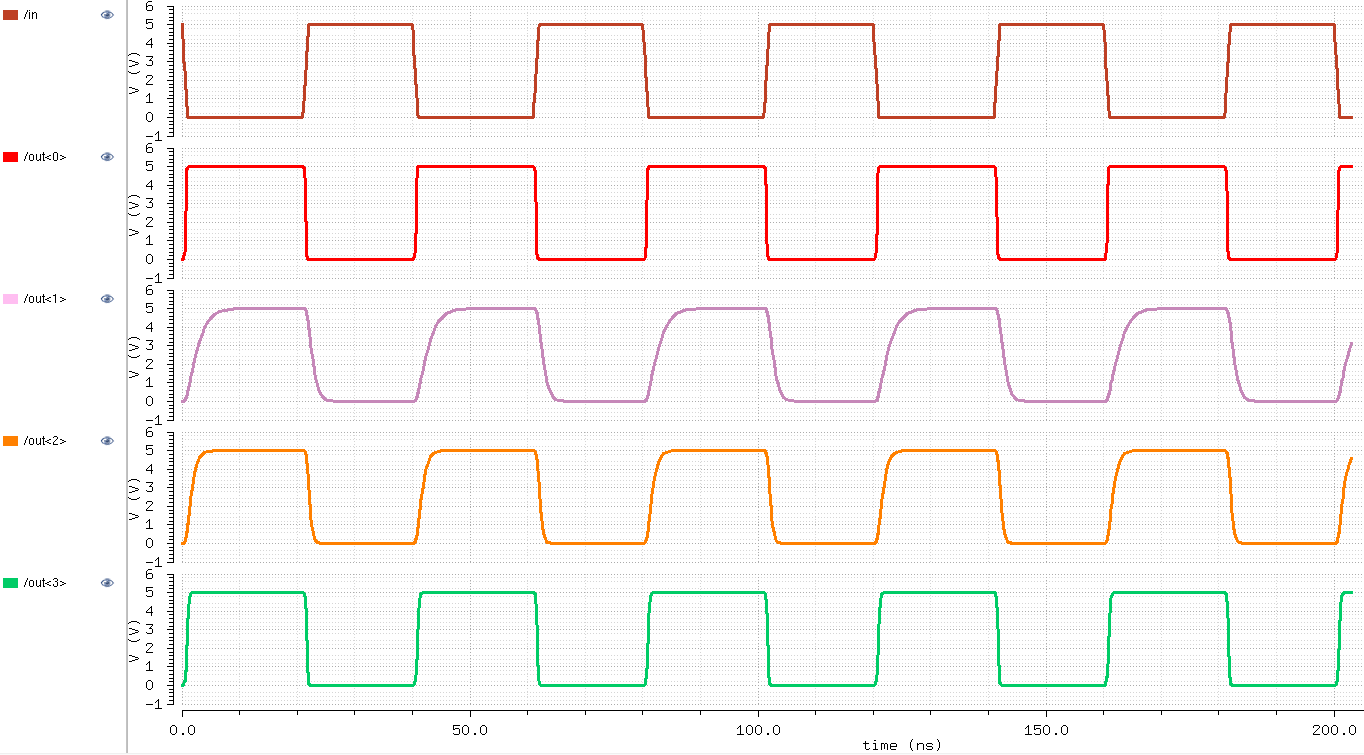

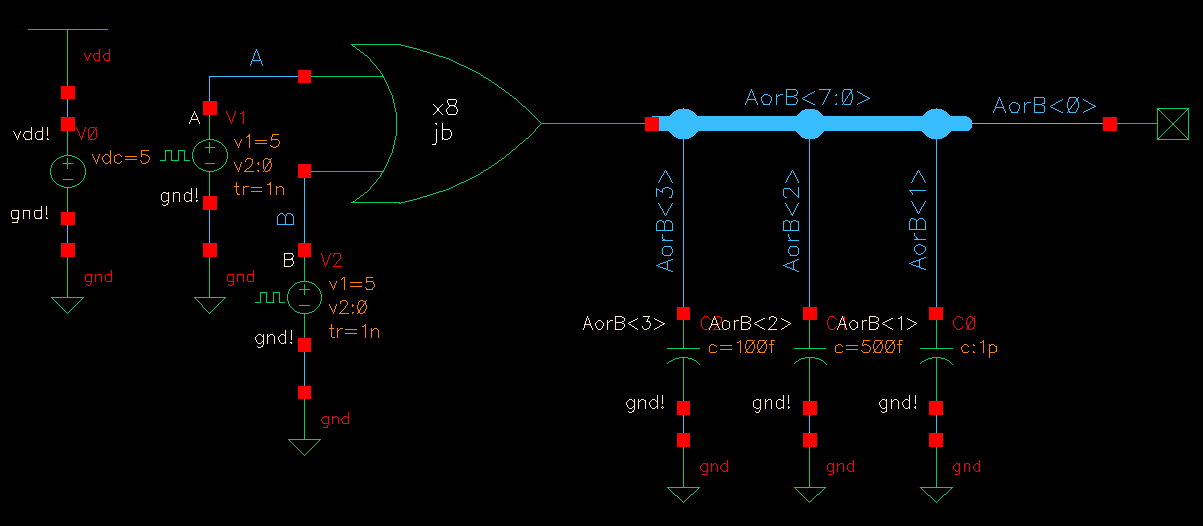

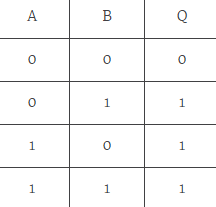

| Logic Gate | Schematic of Simulation | Simulation Result | Truth Table |

| NAND |  |  |  |

| NOR |  |  |  |

| AND |  |  |  |

| inverter |  |  |  |

| OR |  |  |  |

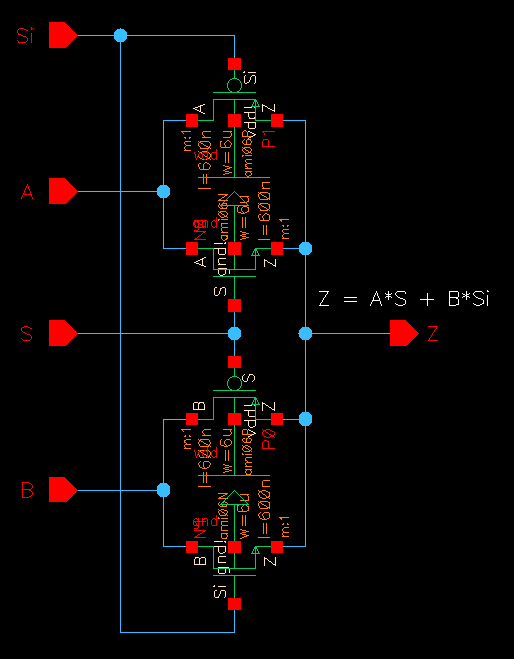

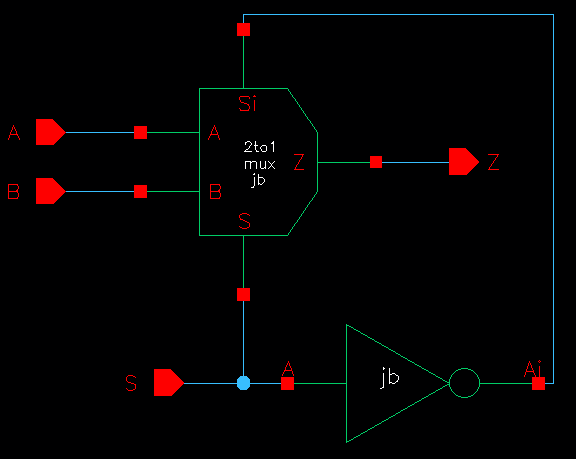

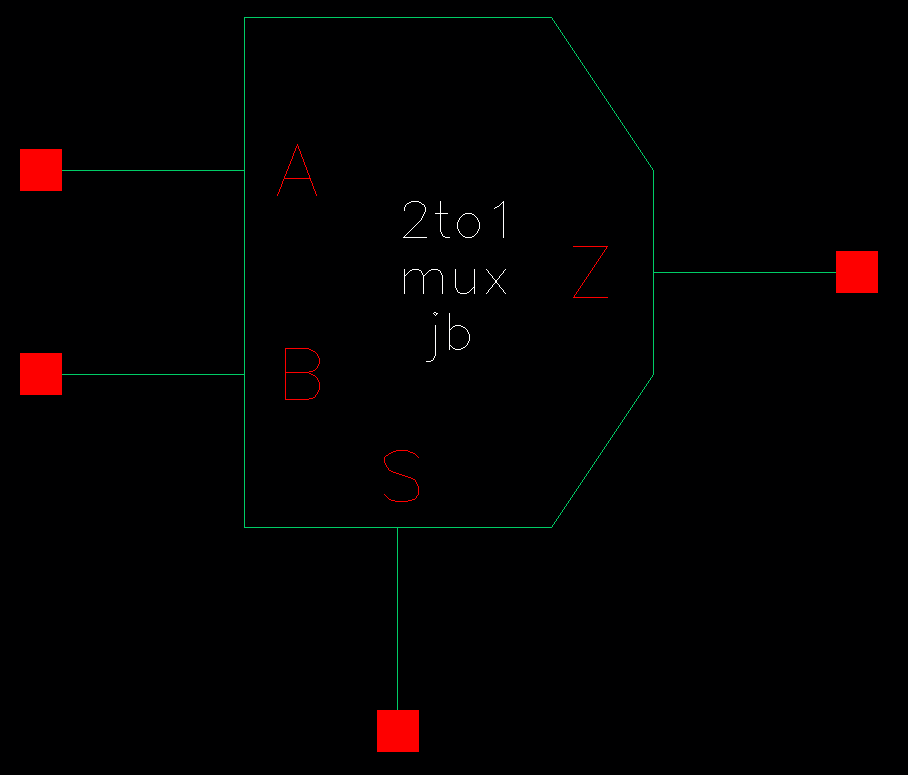

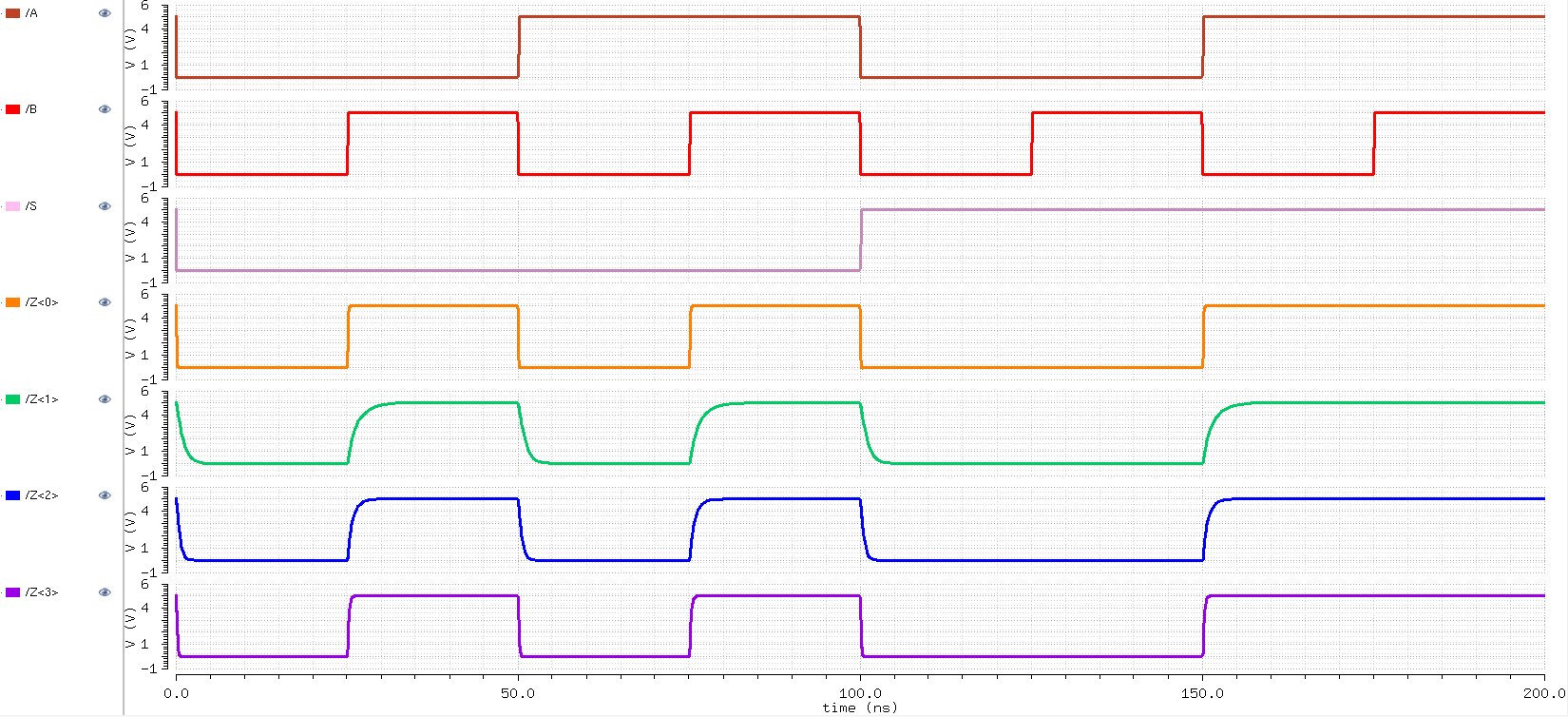

| Transistor-level Schematic | Symbol | 2-to-1 MUX Simulation Schematic | Simulation Result |

|

|  |  |

| Schematic | Symbol | 2-to-1 MUX Simulation Schematic | Simulation Result |

|  |  |  |

| Schematic | Symbol |

|

|

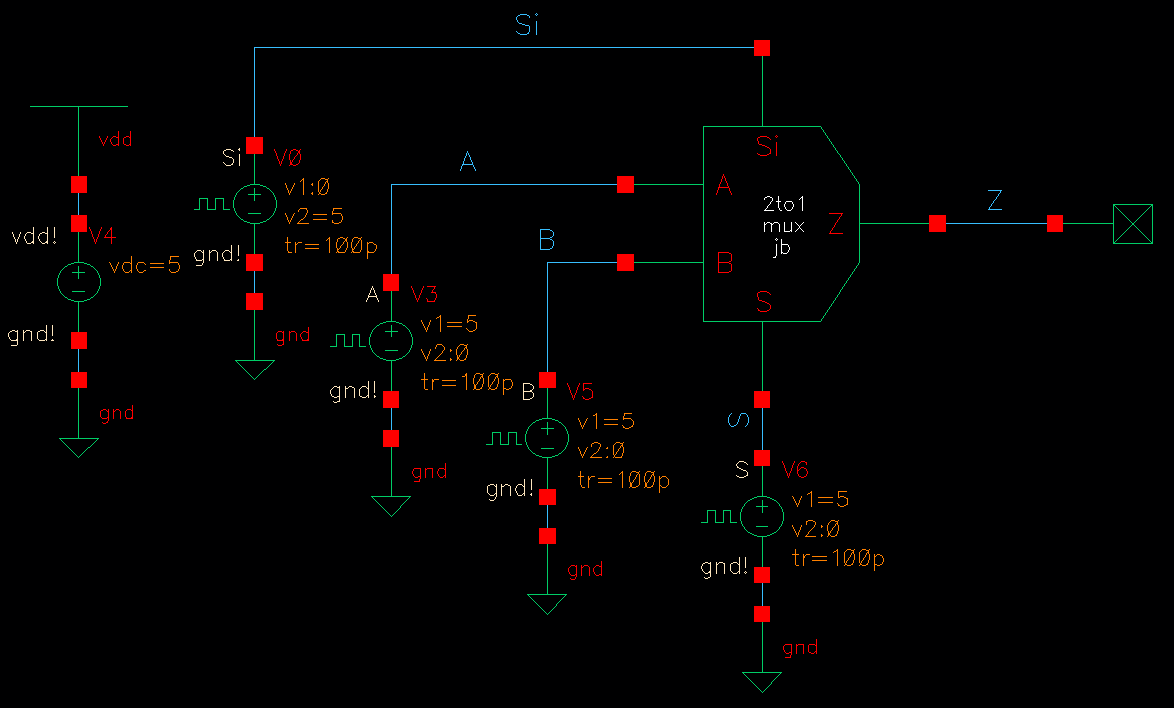

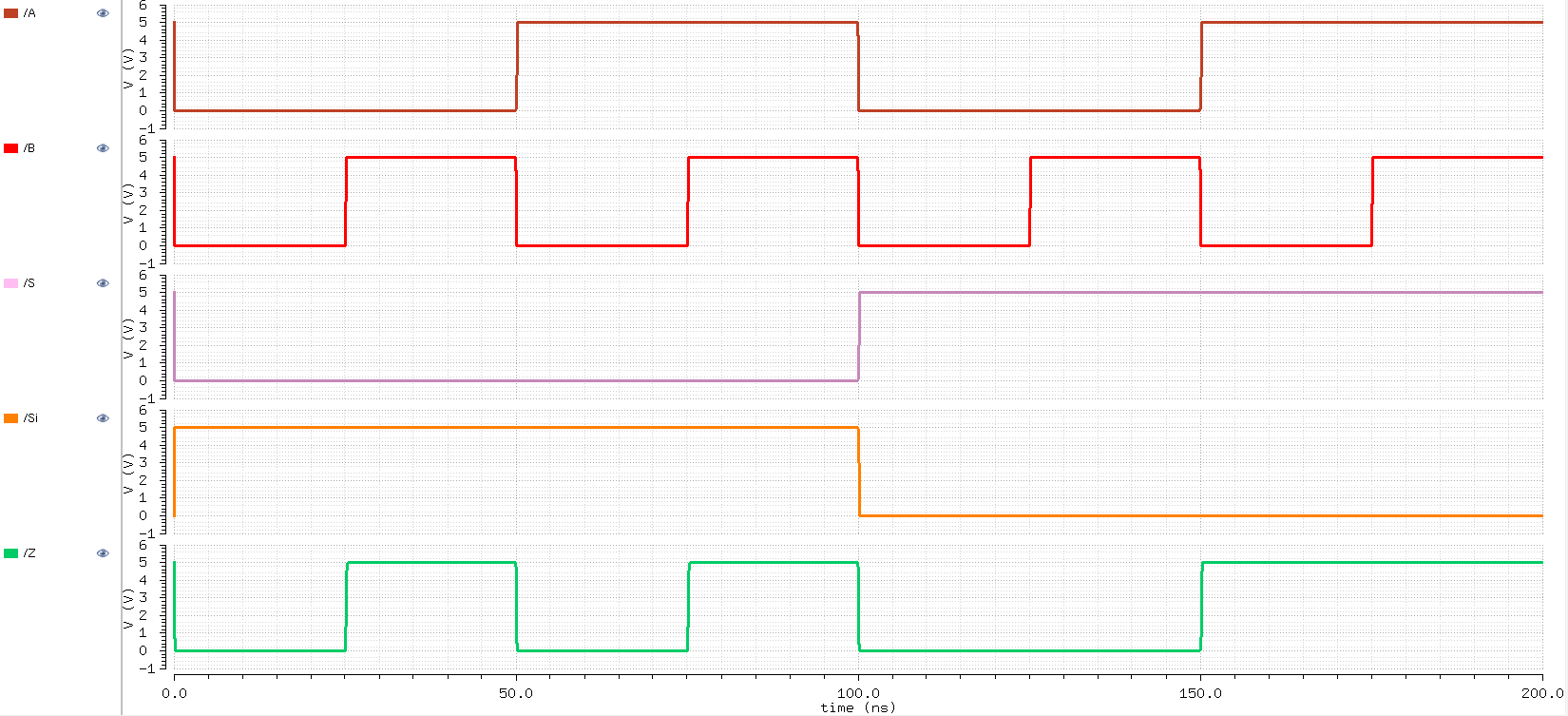

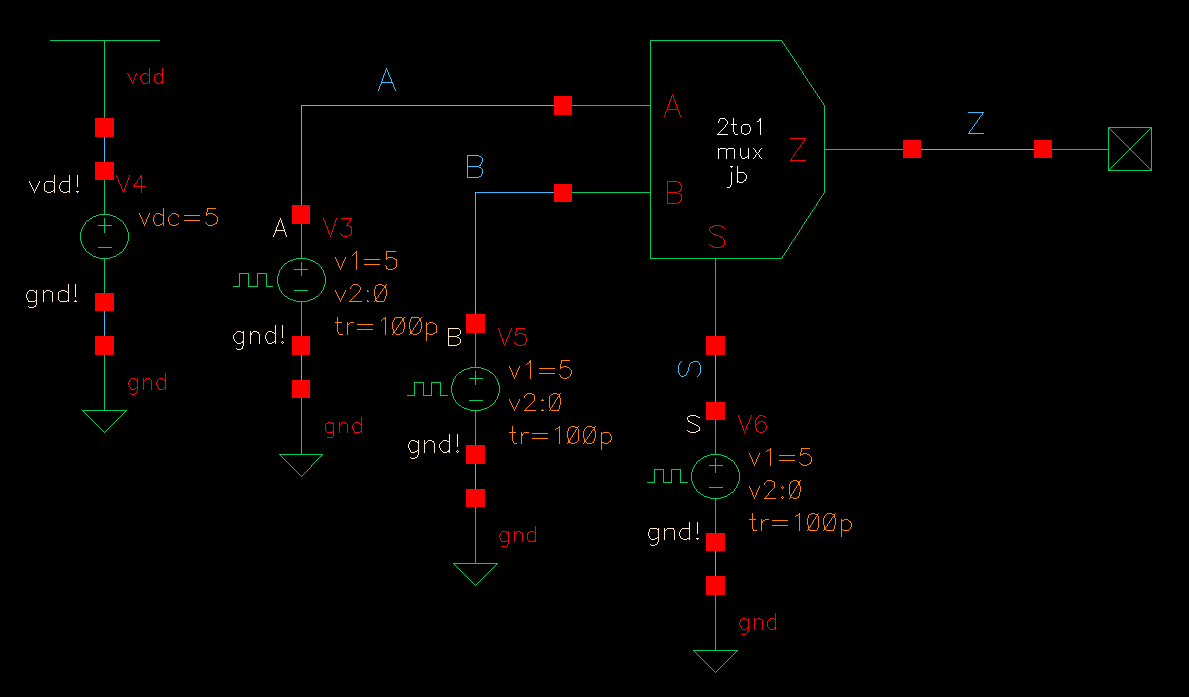

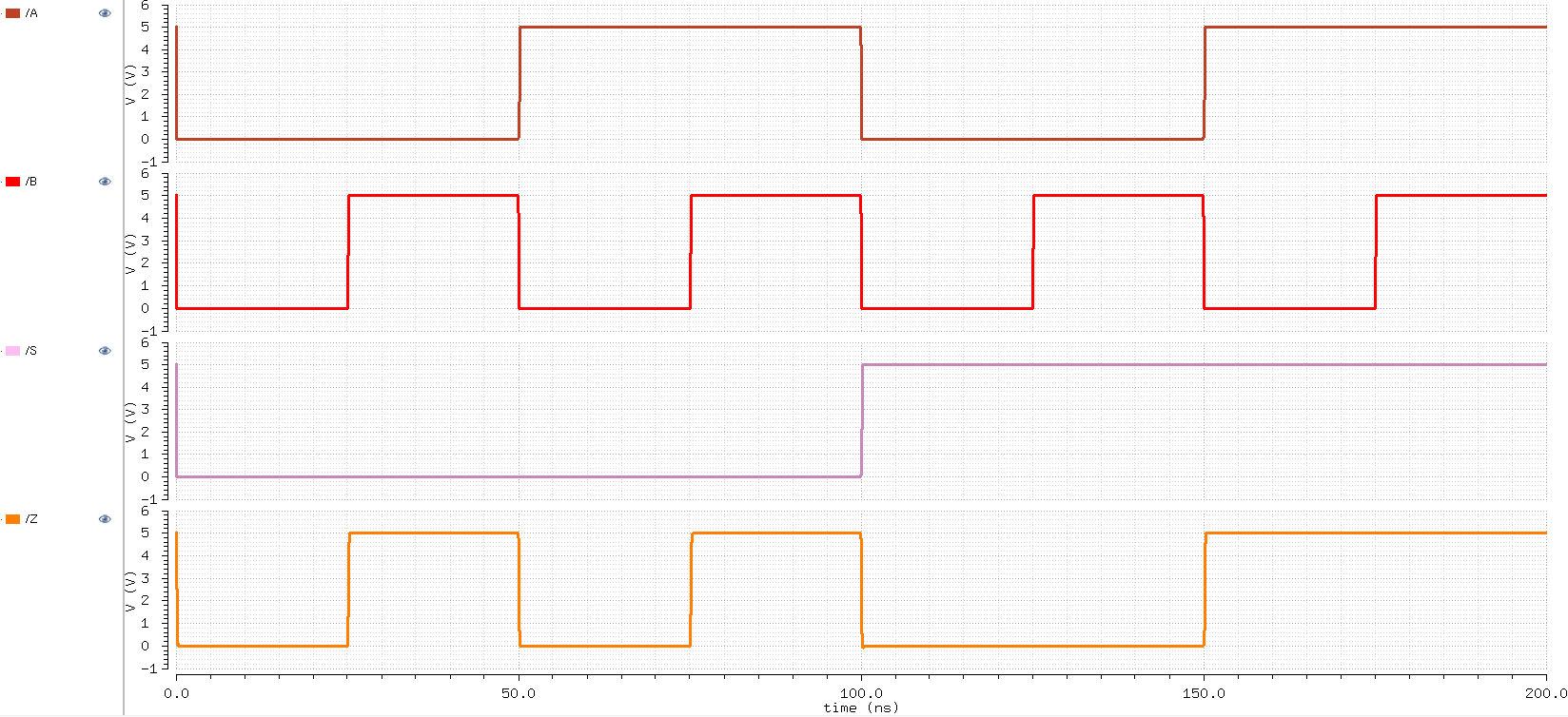

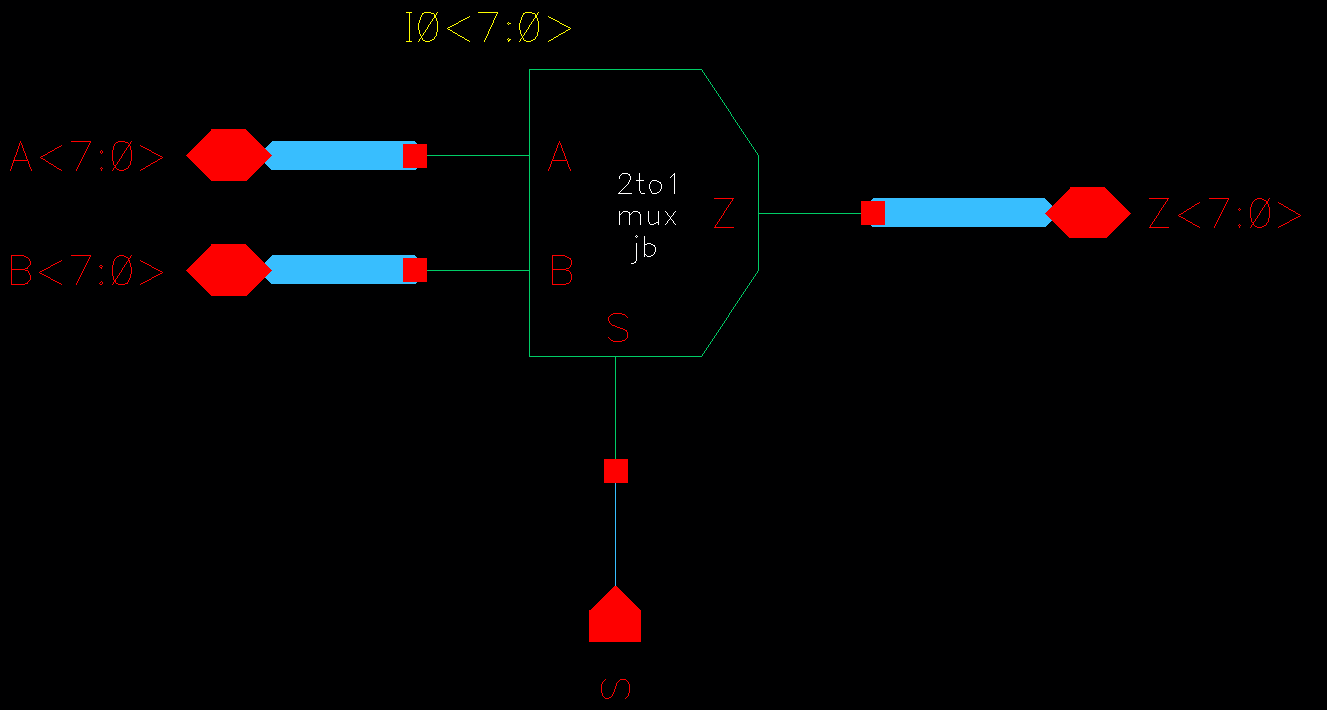

| 2-to-1 MUX Simulation Schematic | Simulation Result |

|  |

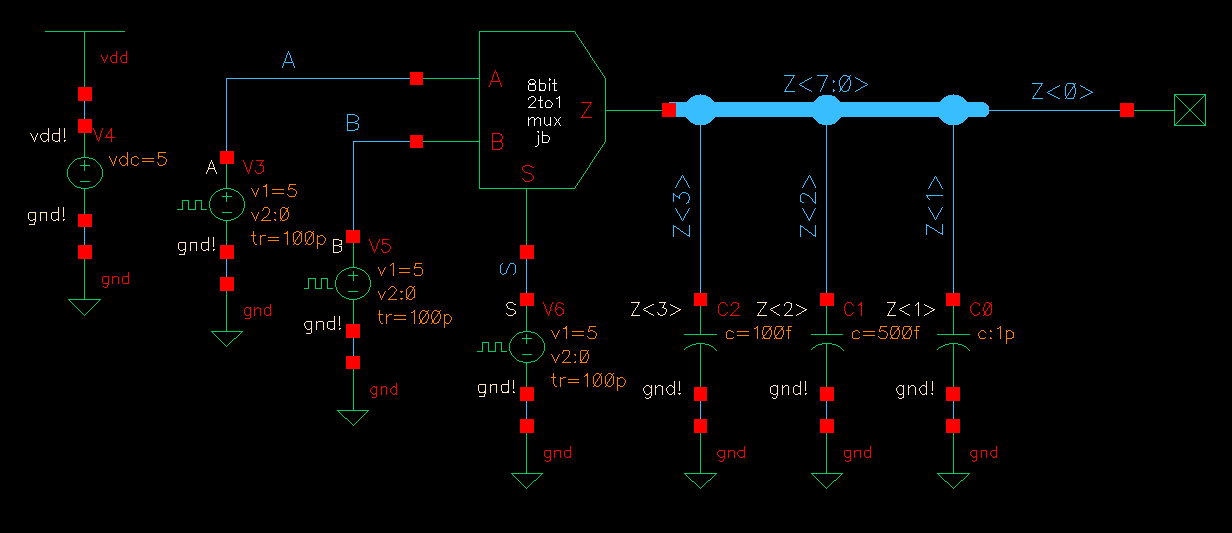

| 2-to-1 DEMUX Simulation Schematic | Simulation Result |

|  |

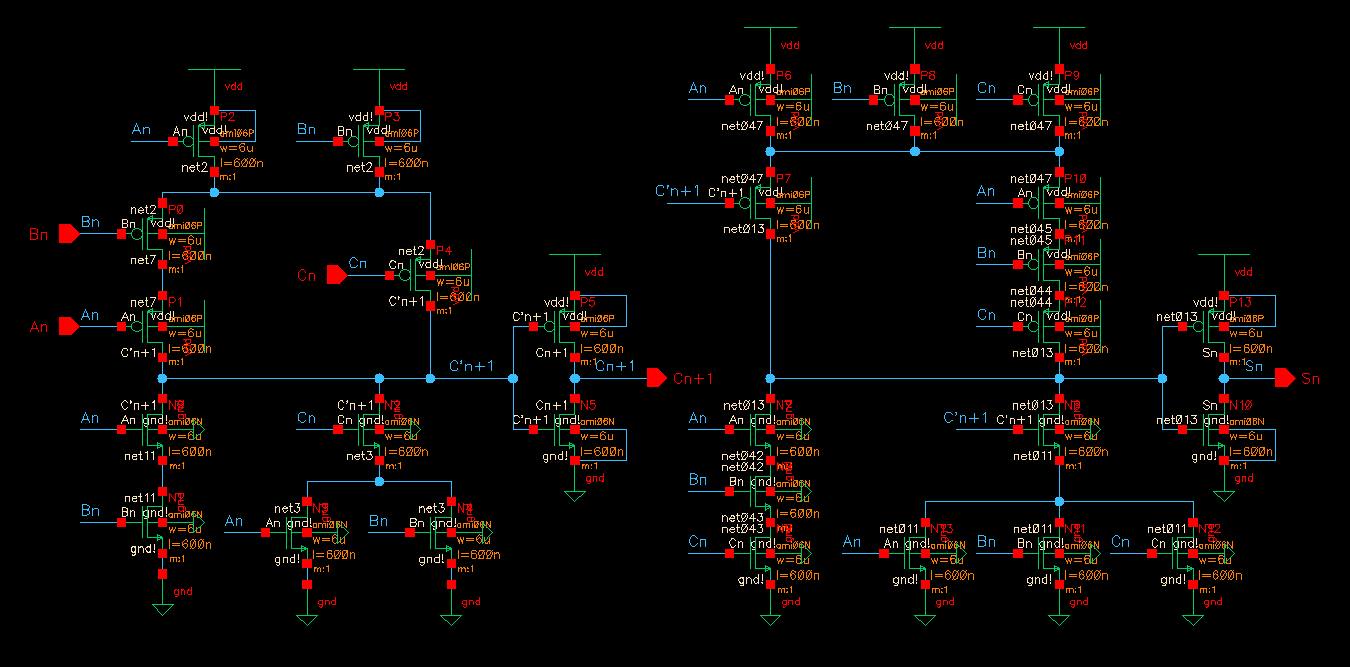

| Transistor-level Schematic | Symbol |

|

|

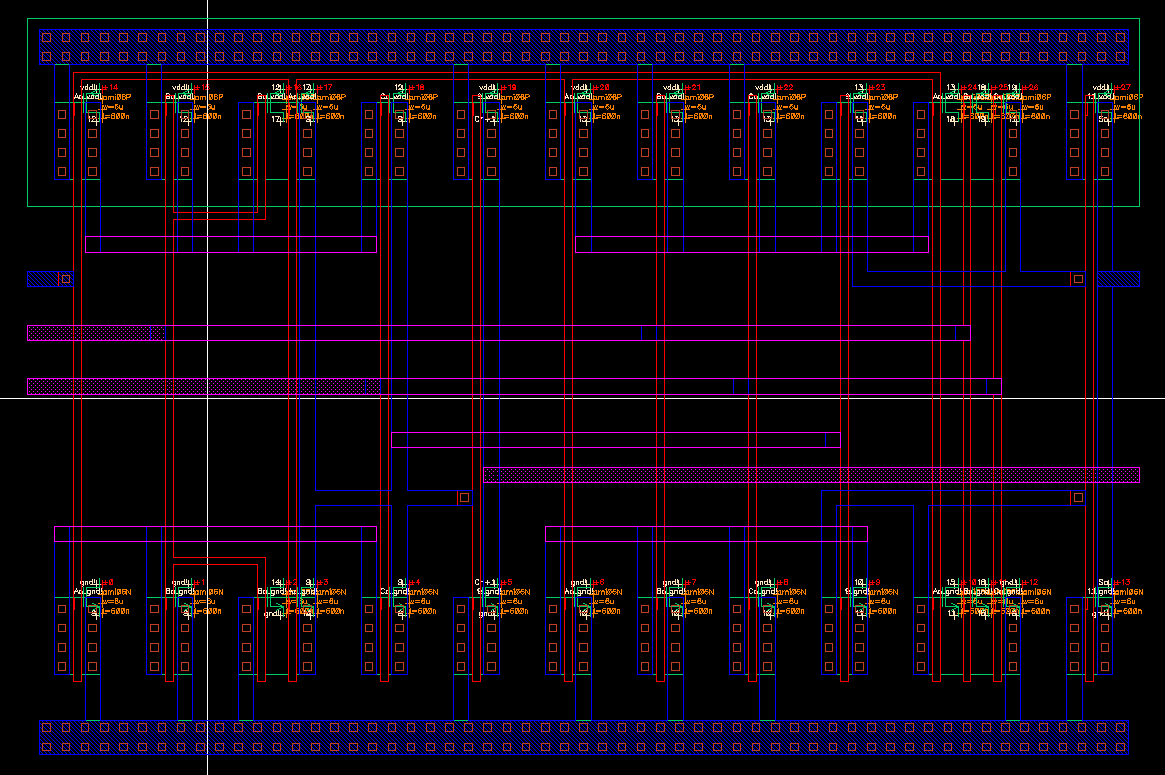

| Layout | Extracted |

|  |

|

|

| Simulation Schematic |

|

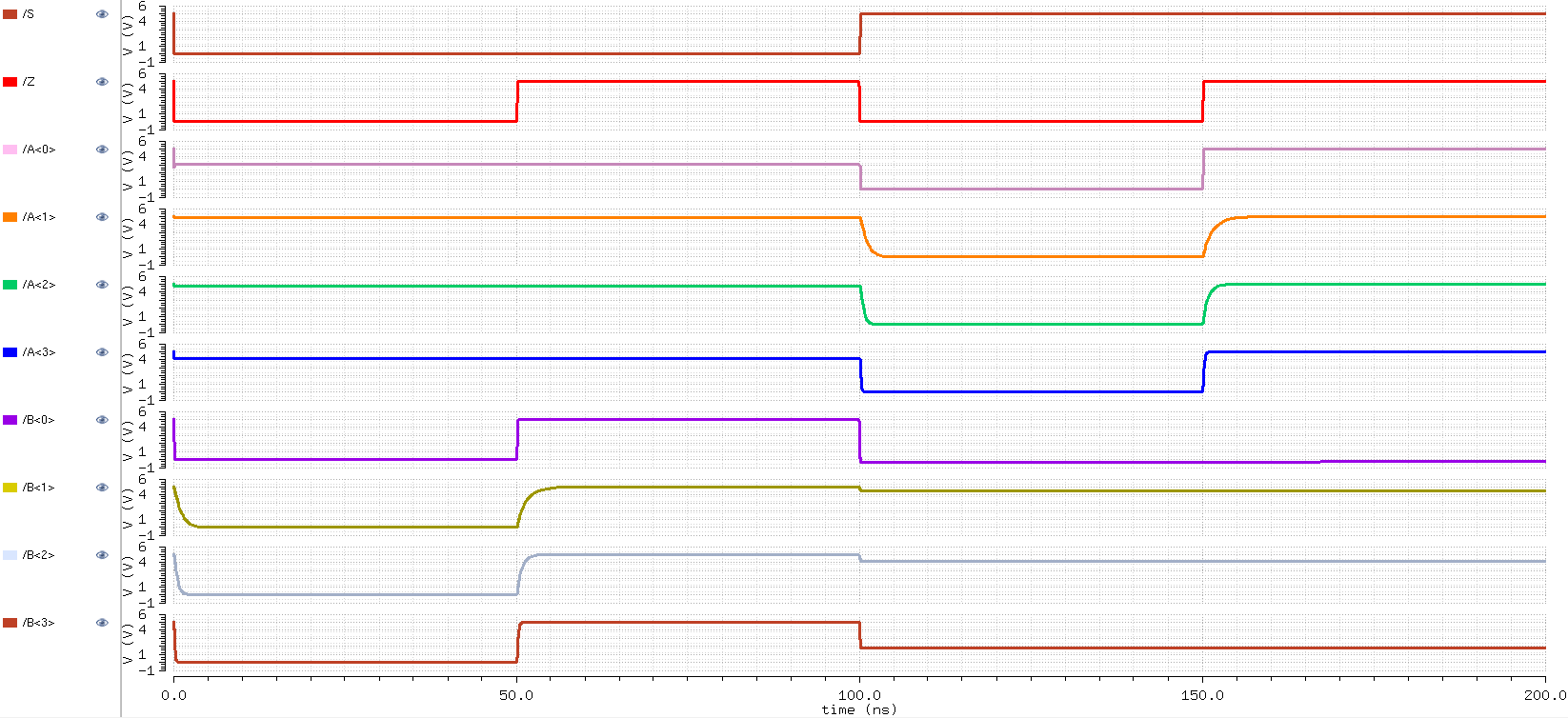

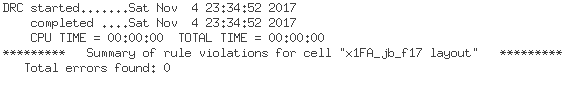

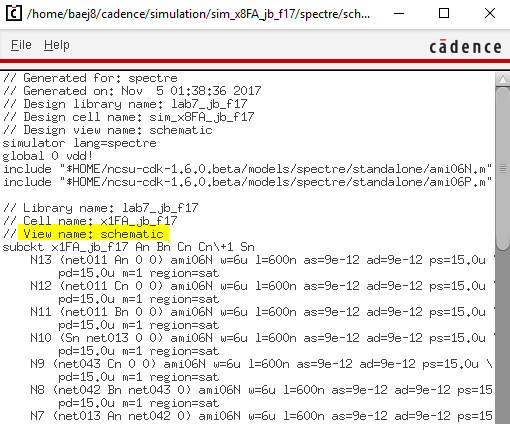

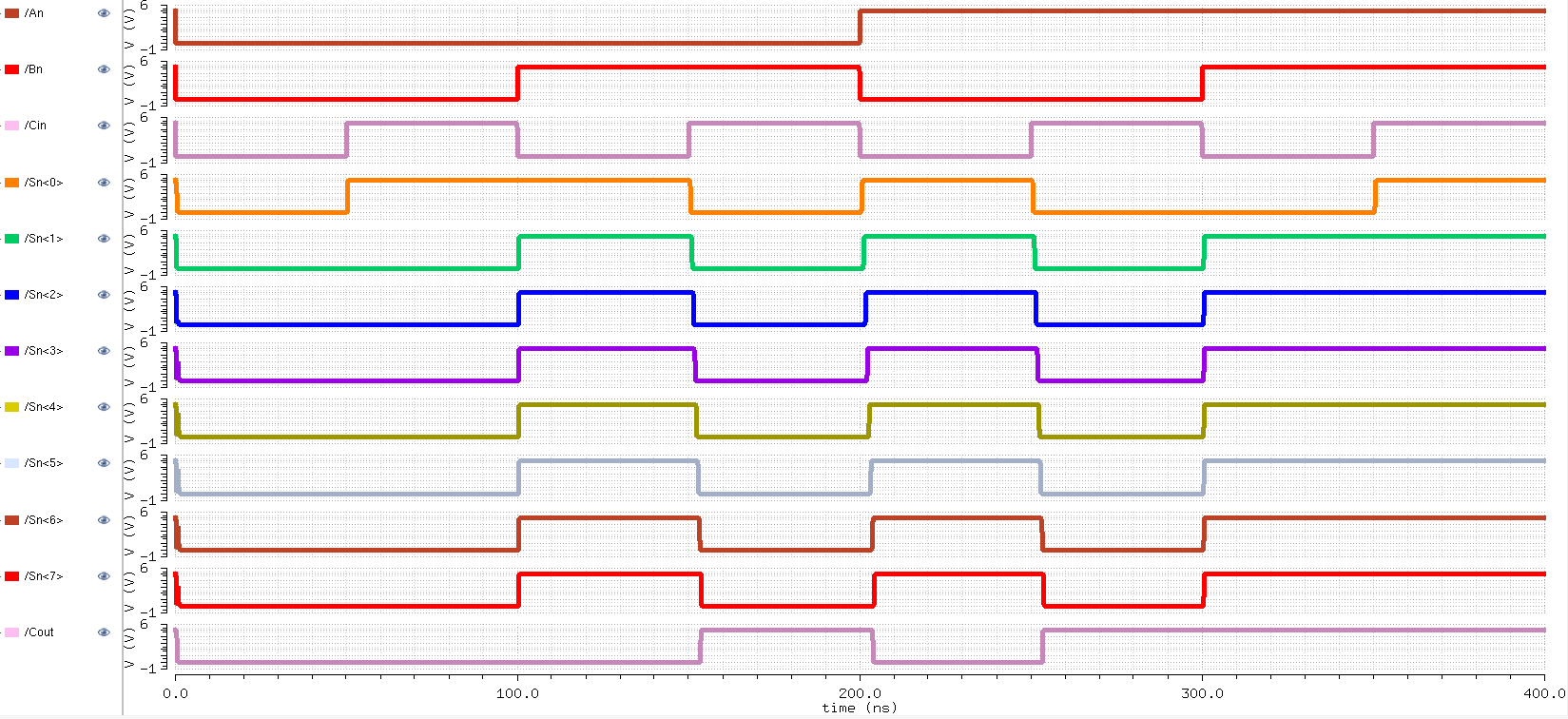

| Simulation Netlist | Simulation Result |

|

|

|

|

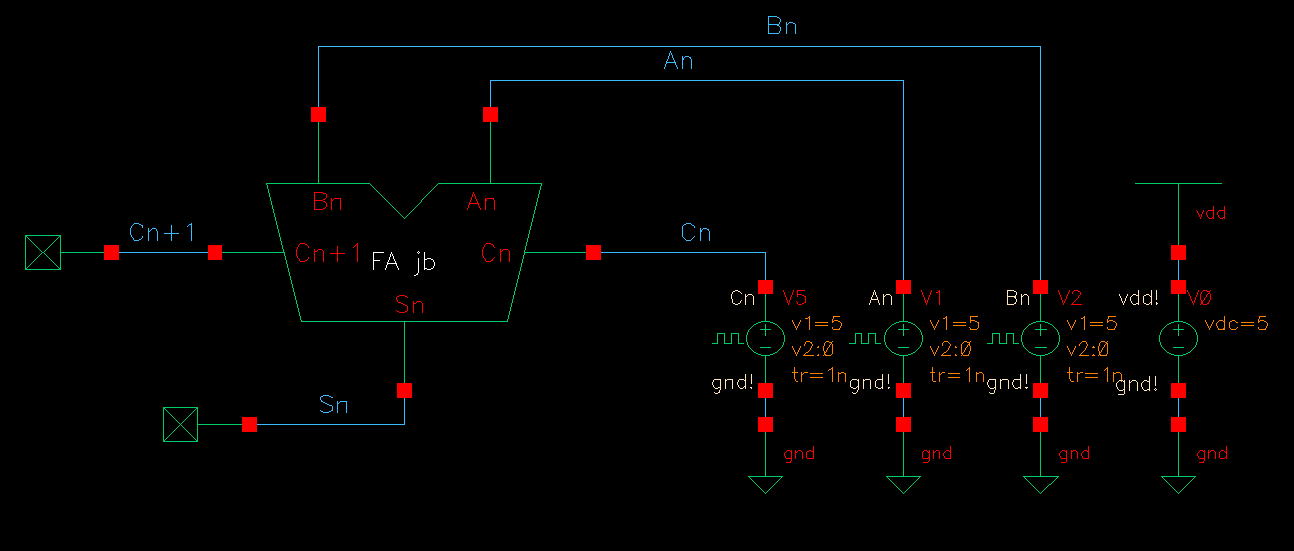

| a | b | cin | s | cout | |

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 1 | 0 | |

| 0 | 1 | 0 | 1 | 0 | |

| 0 | 1 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 |

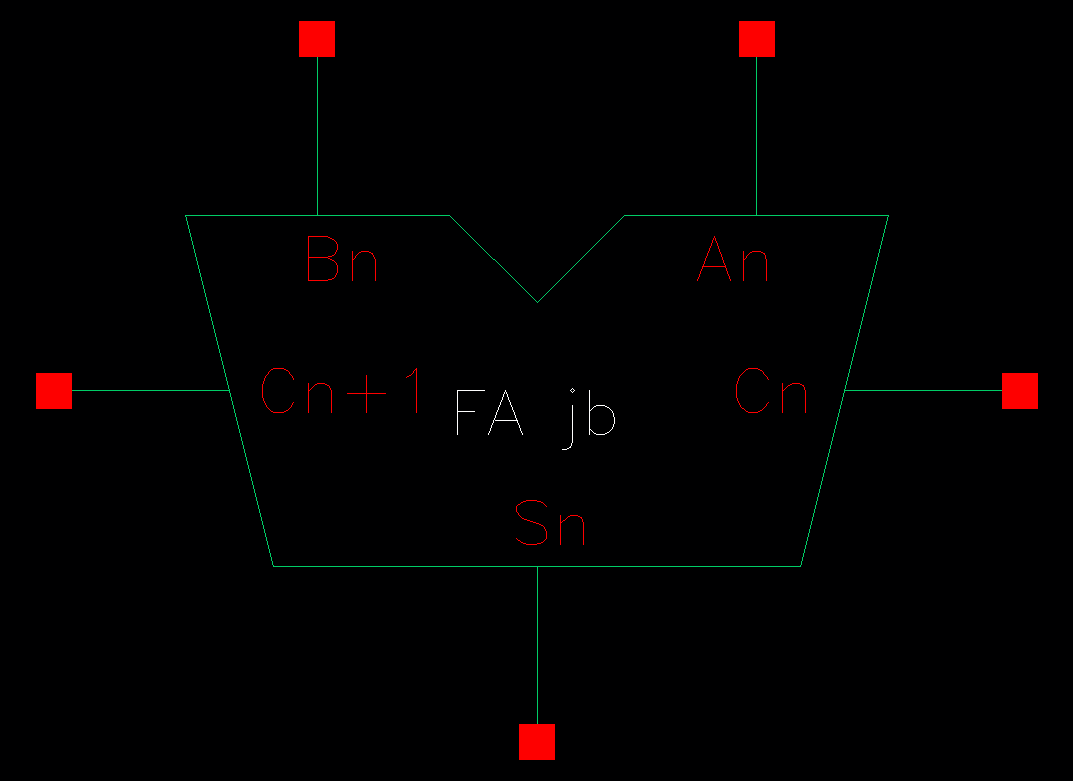

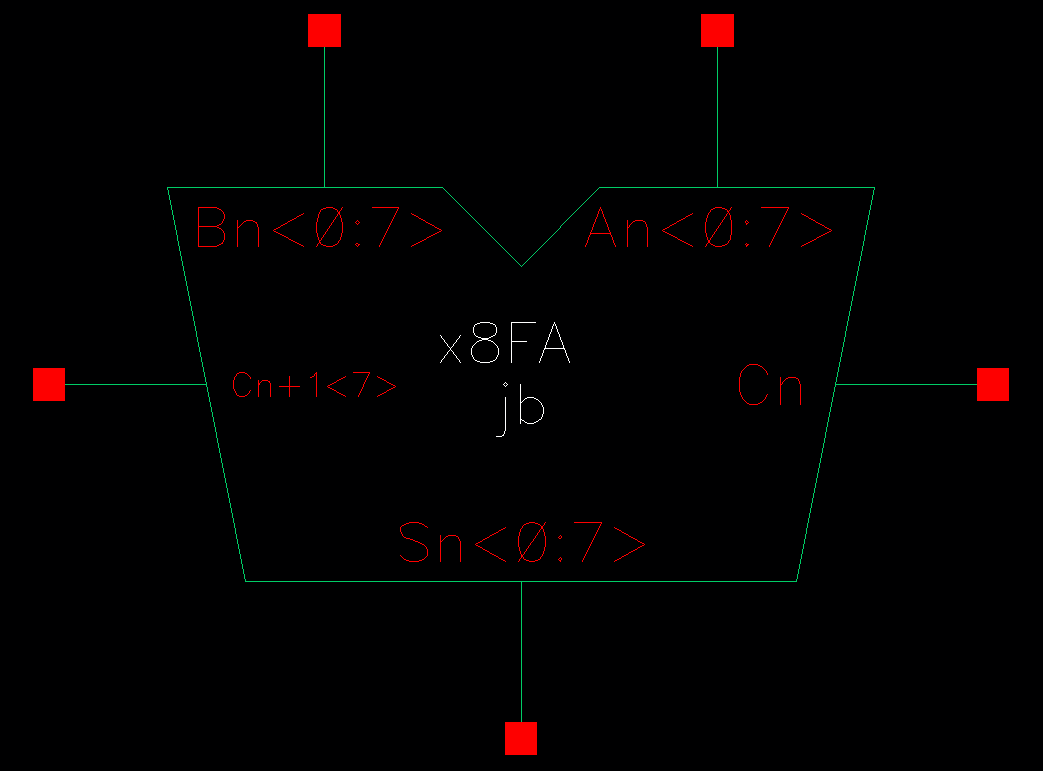

| Schematic | Symbol |

|

|

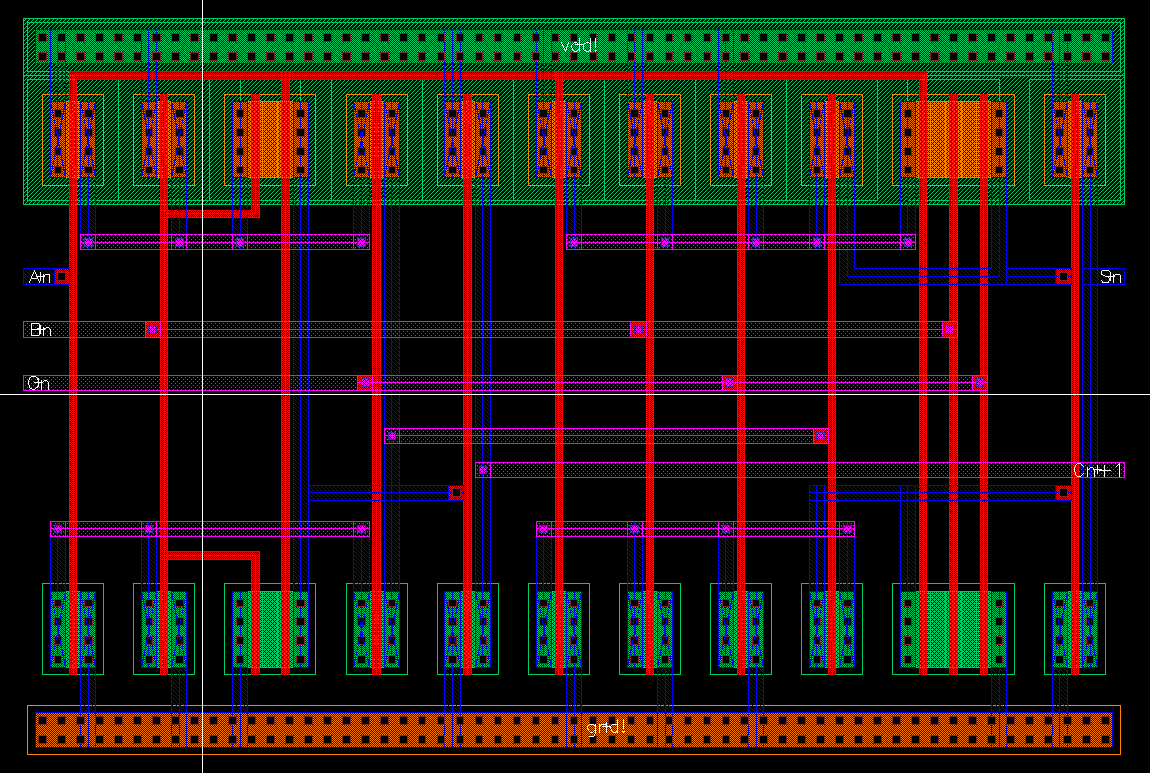

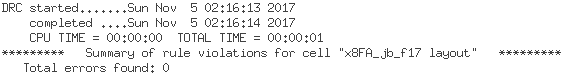

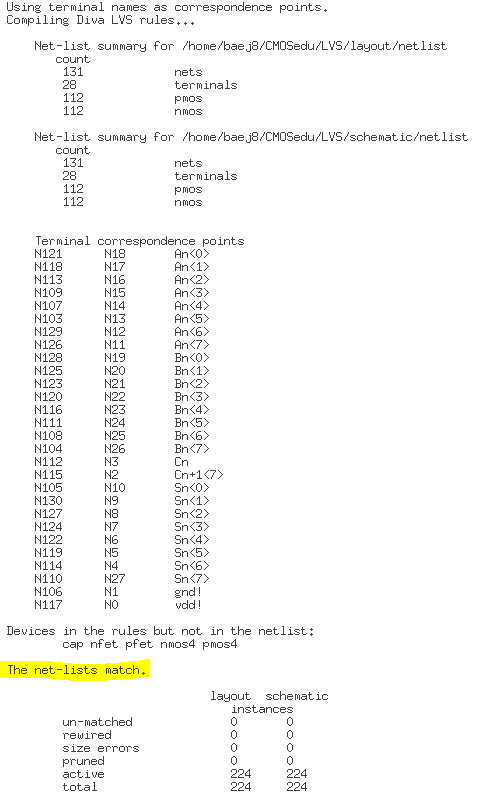

| Layout |  |

| Extracted |  |

|

|

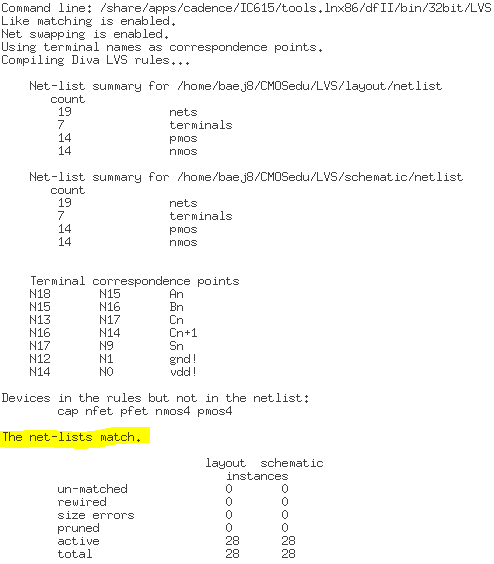

| Simulation Schematic |

|

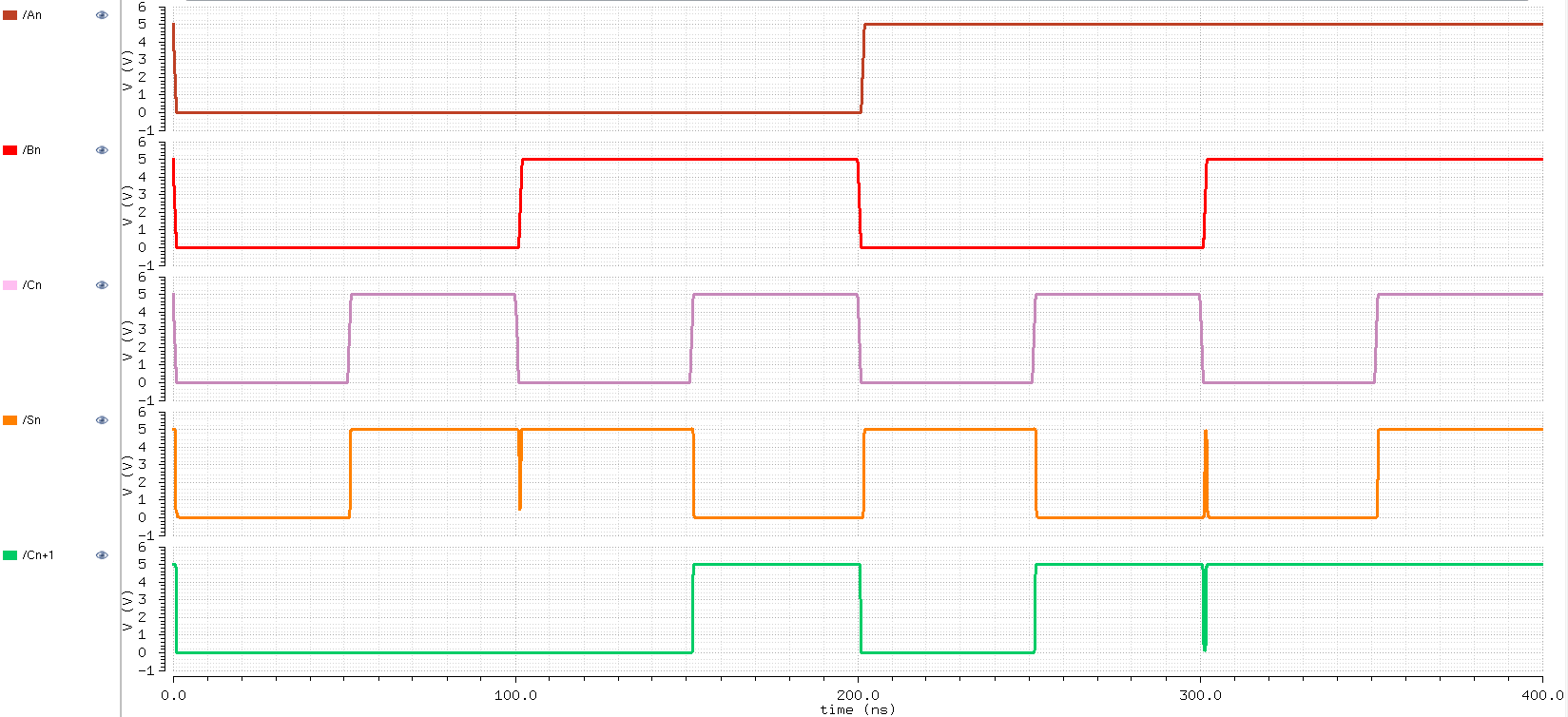

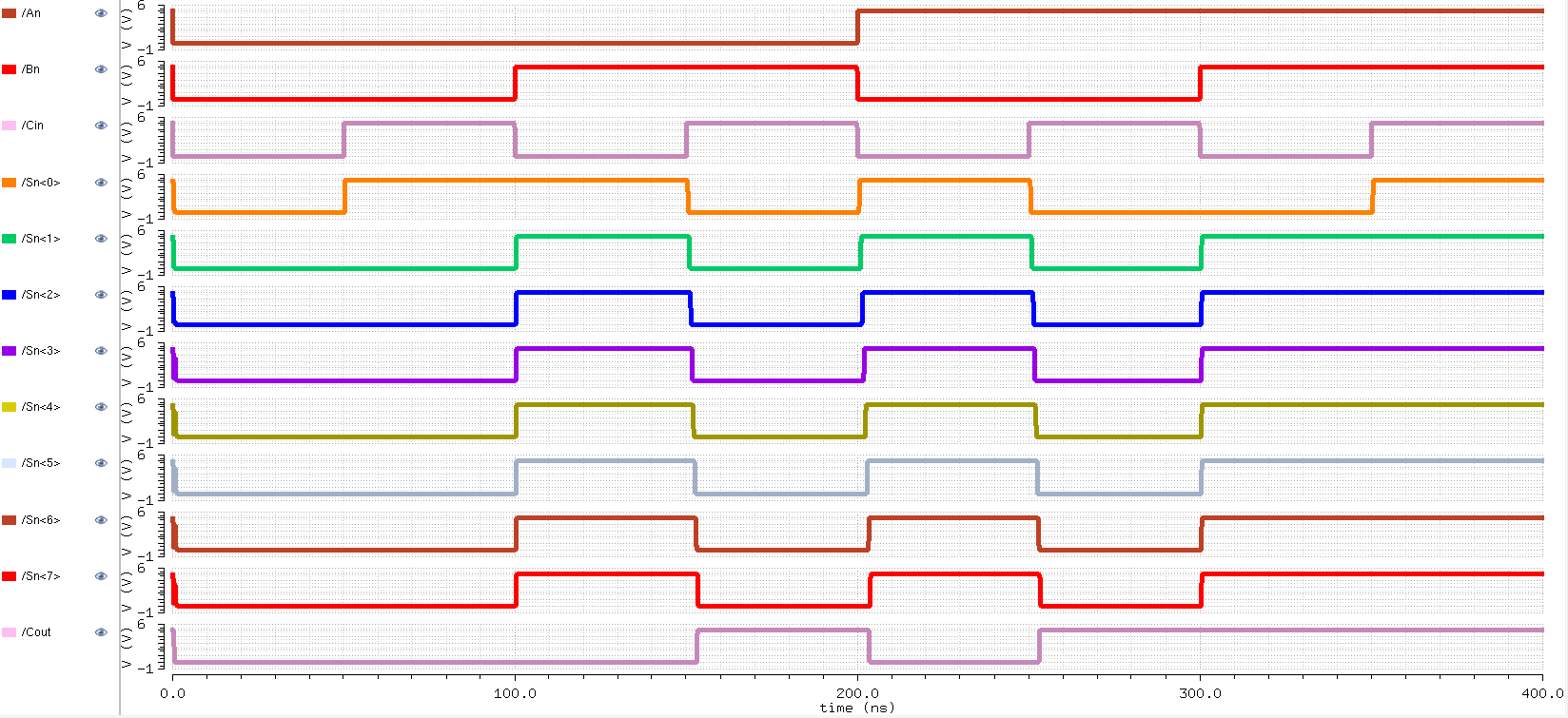

| Simulation Netlist | Simulation Result |

|

|

|

|