Lab 05 -

EE 421L

Authored

by Junho Bae

baej8@unlv.nevada.edu

October

11, 2017

Pre-lab

work

Back-up all my work from

this lab and the course.

Complete Tutorial

3.

An inverter which was used in the lab below was drafted.

Lab

Work

Drafting CMOS inverters

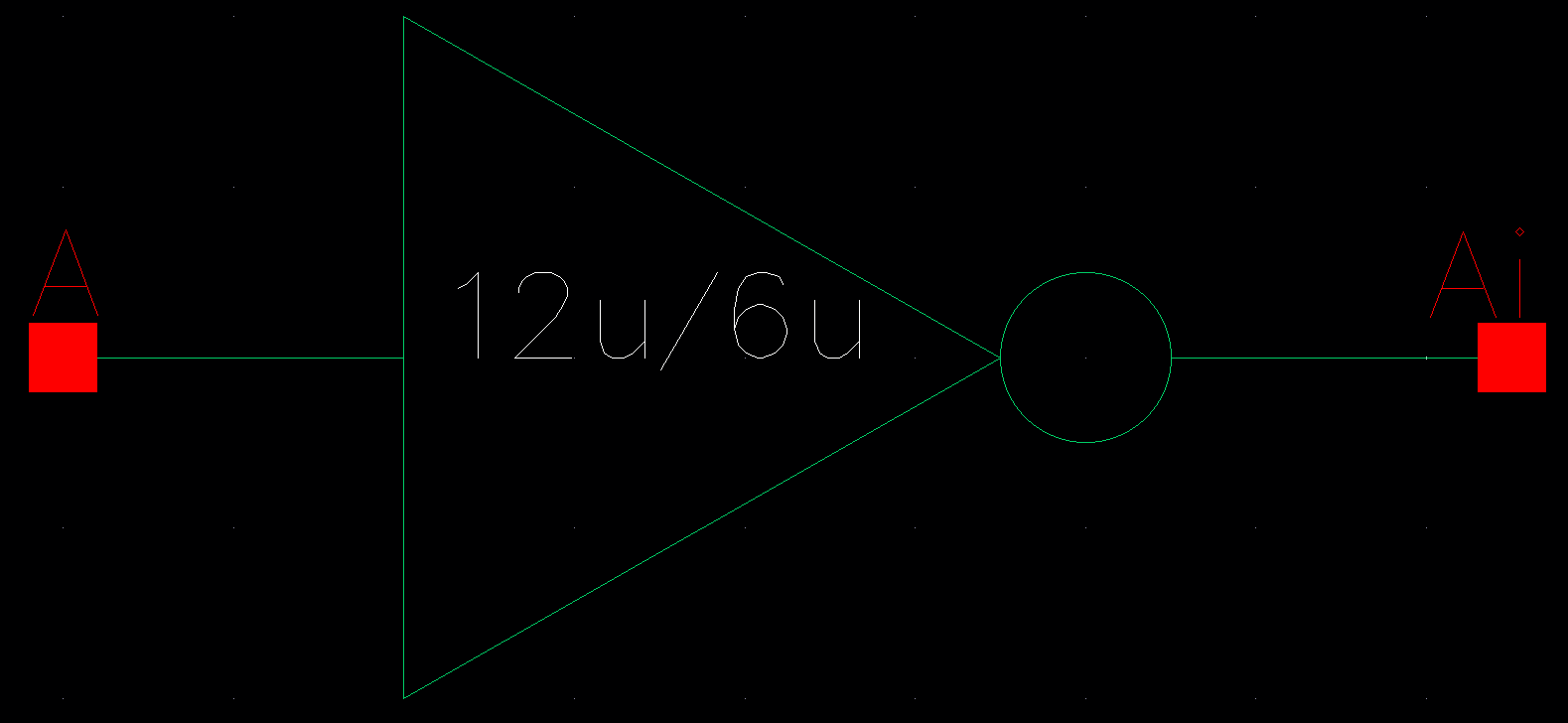

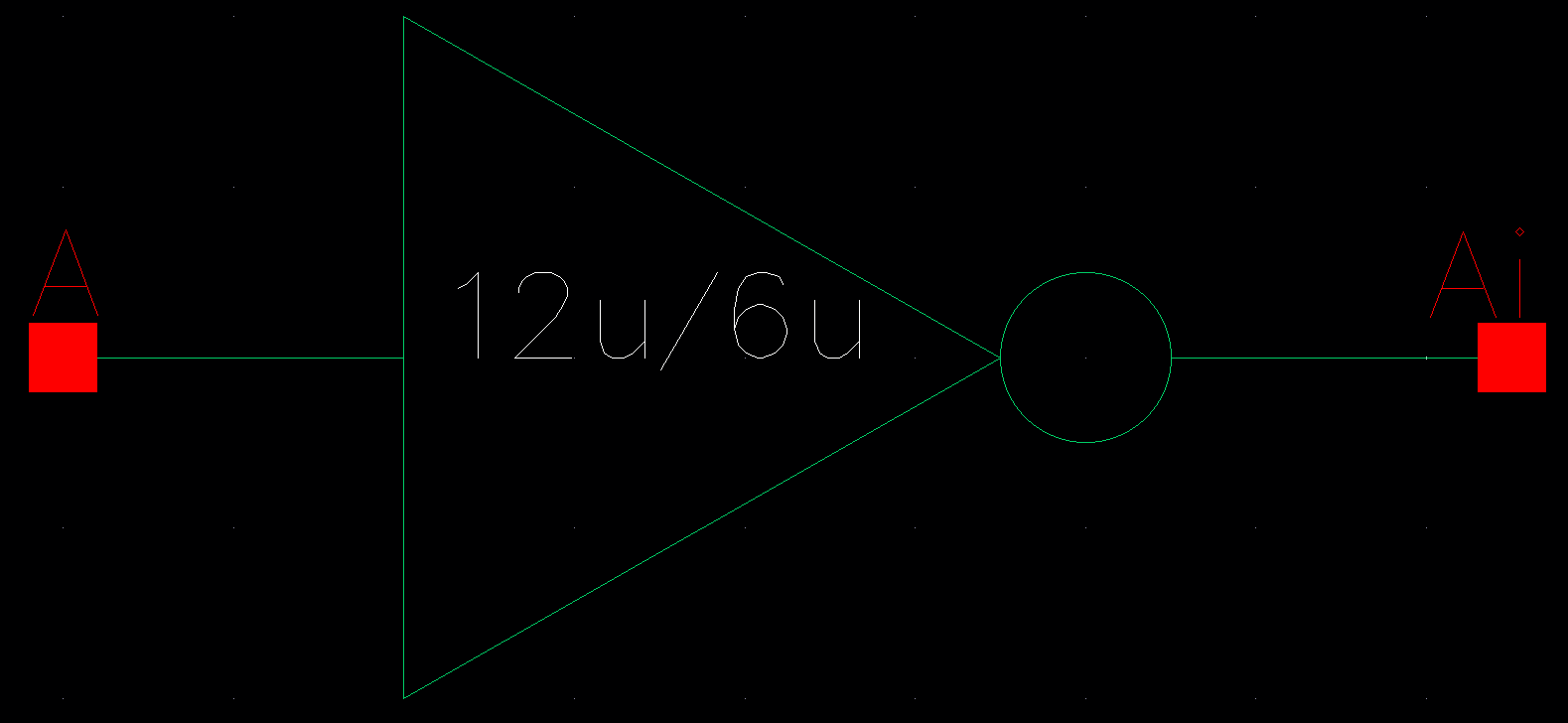

12u/6u Inverter

I first drafted the schematic of the inverter using a PMOS

(w=12u l=600n) and an NMOS (w=6u l=600n).

The

schematic had two pins in comparision to the layout which had four pins

to cover the global power and ground. The bodies of the PMOS and NMOS

were connected to their respective source terminals, their gate

terminals were tied together to create an input pin, and their drain

termials were connected together to create an output pin.

This process was covered in the prelab; therefore, moved on to draft

the second inverter.

| Schematic |

Symbol |

|

|

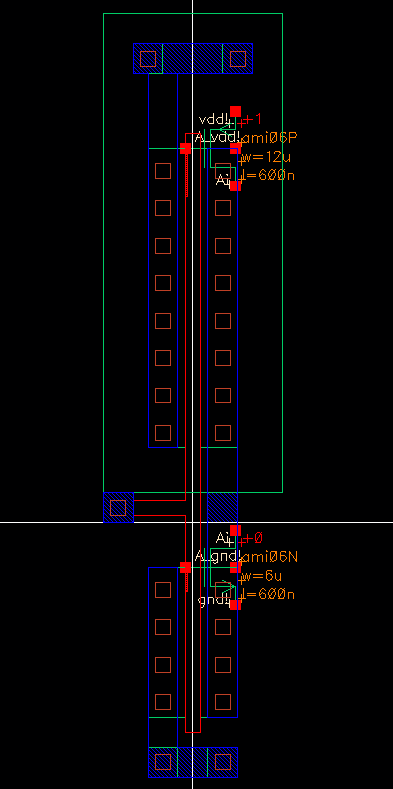

To

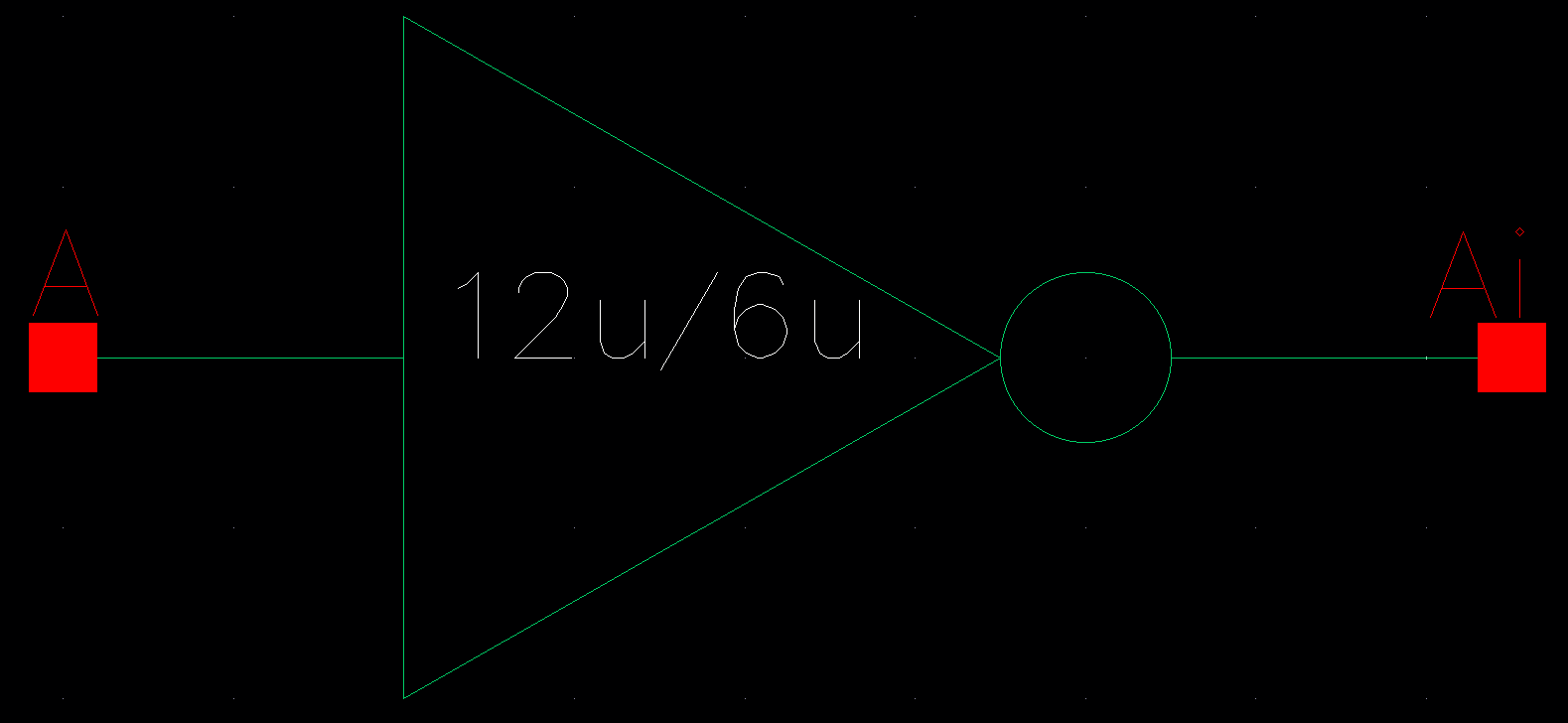

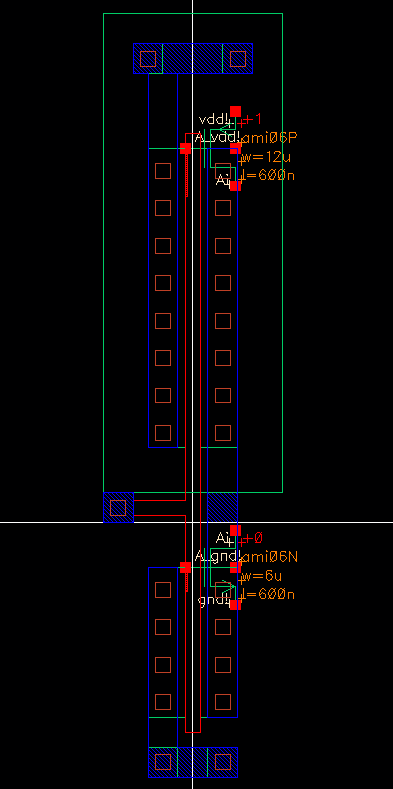

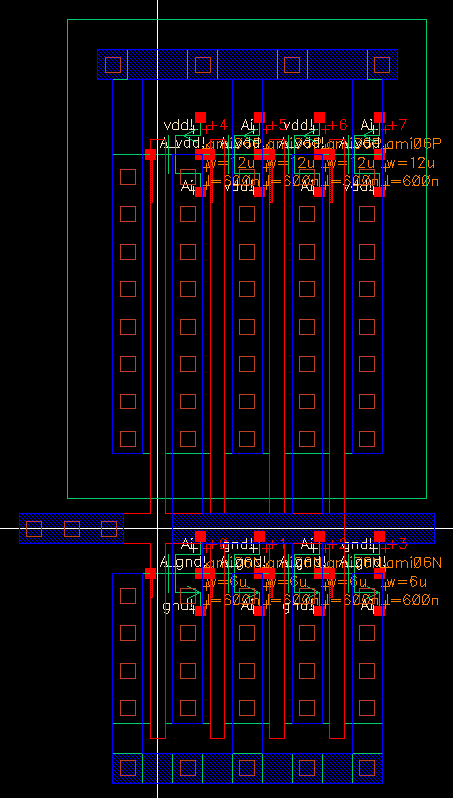

draft the layout of the inverter, I used pre-existing cells (ntap,

ptap, m1_poly, pmos, and nmos) with a few addtional connections to

connect the 4 terminals to match the schematic.

| Layout |

Extracted |

|

|

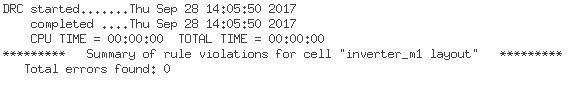

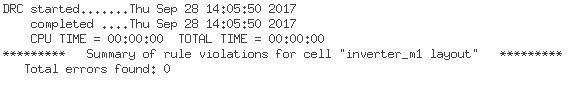

DRC successful

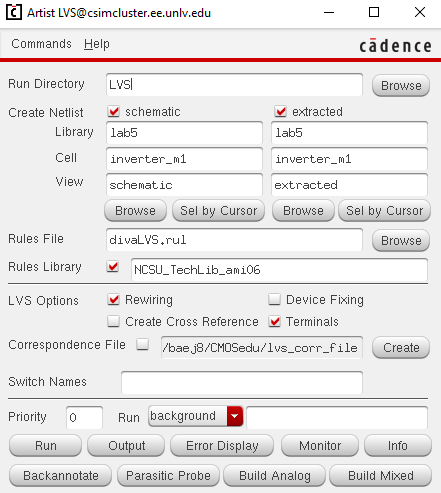

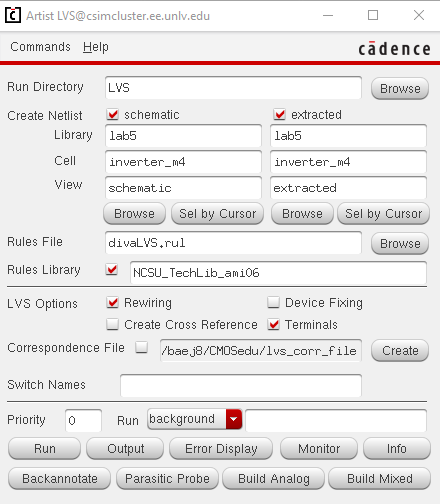

LVS

successful

Drafting CMOS inverters

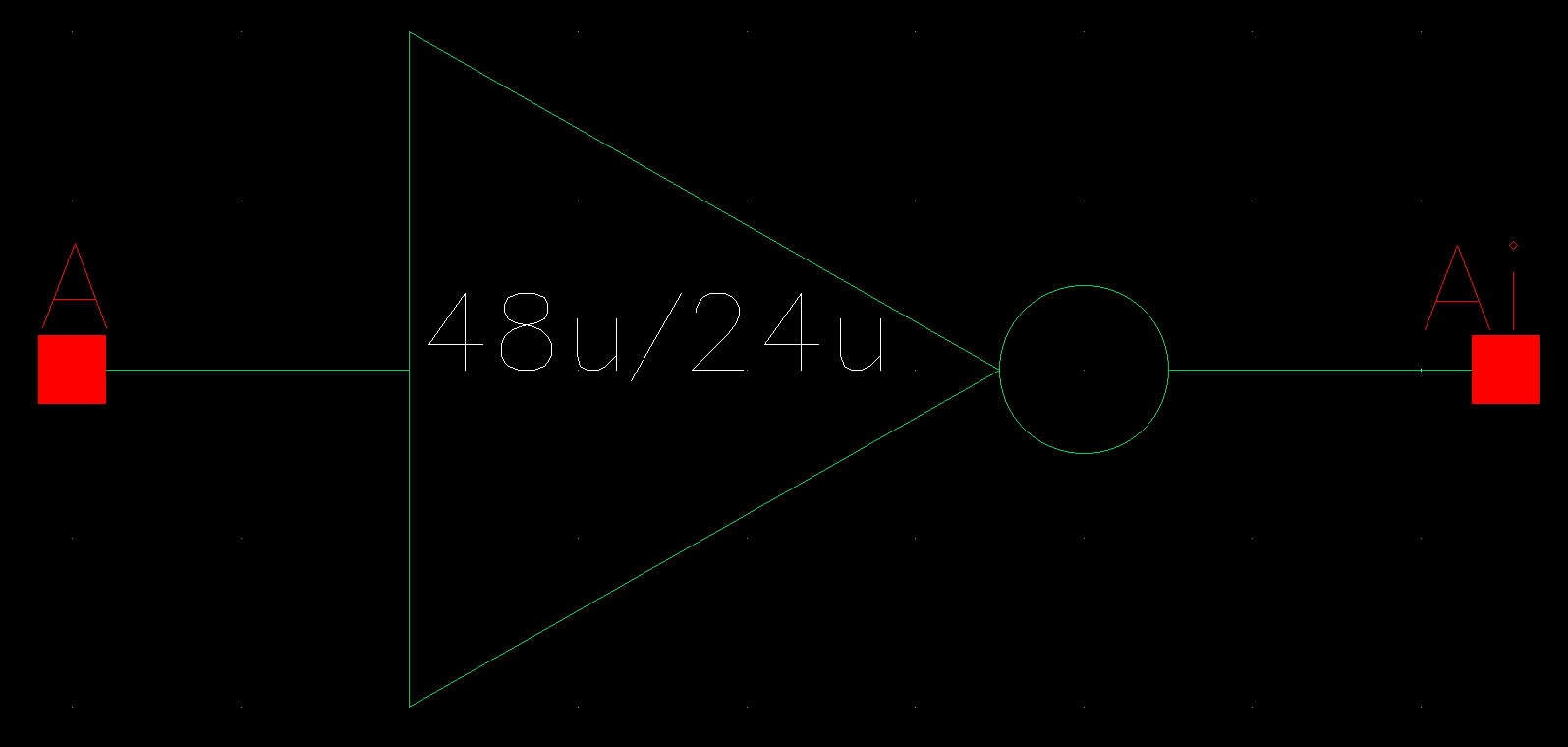

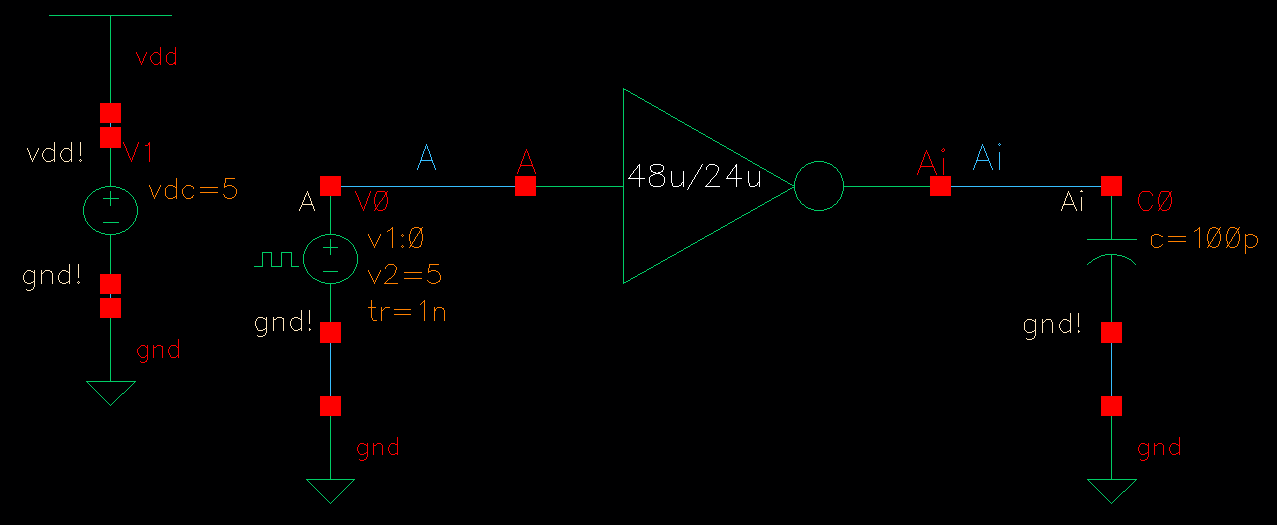

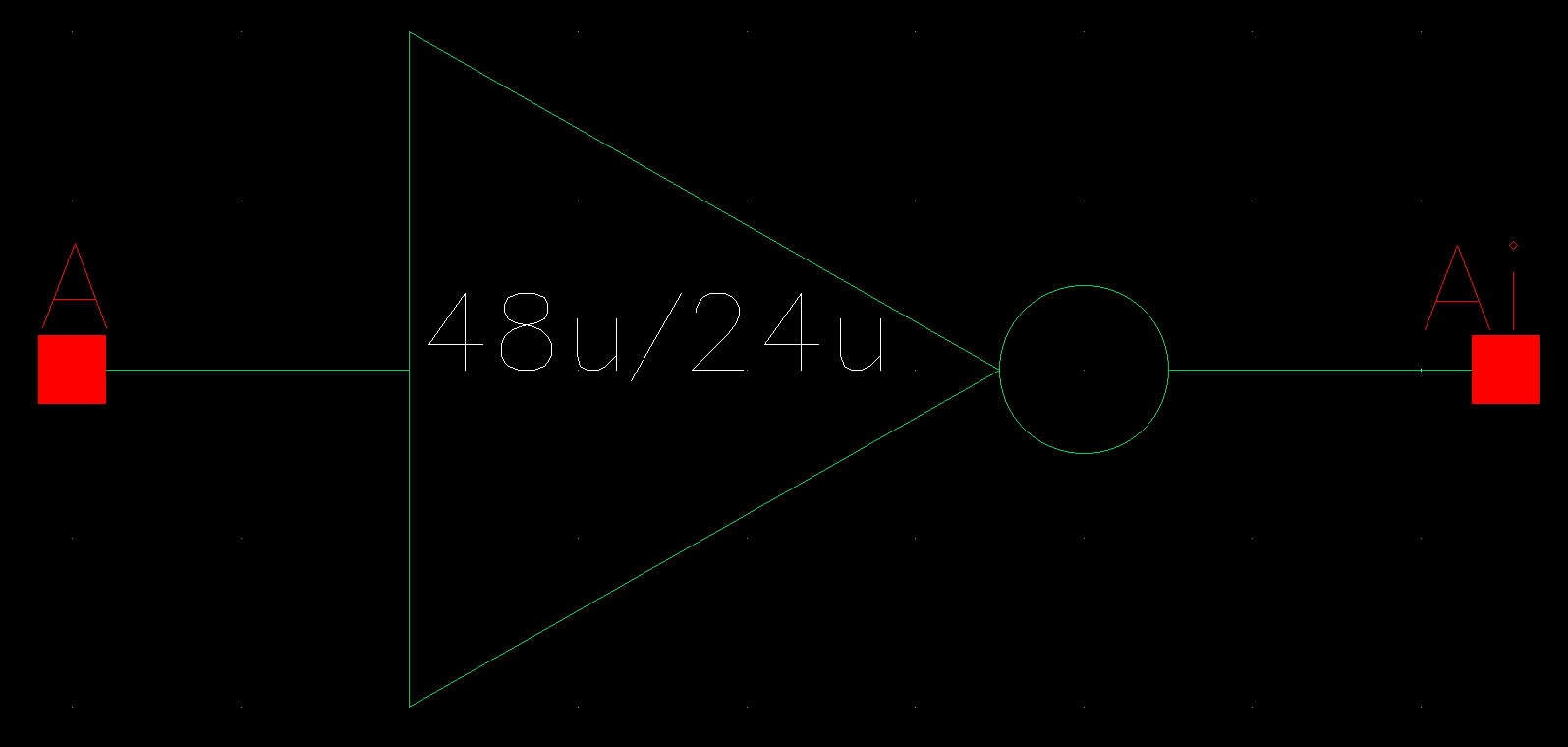

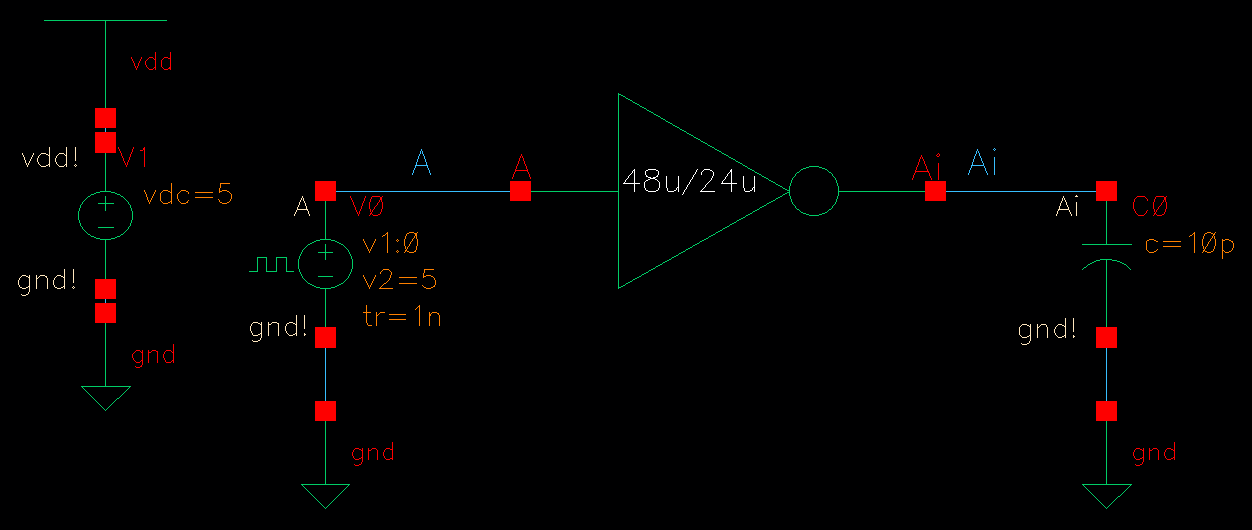

48u/24u inverter

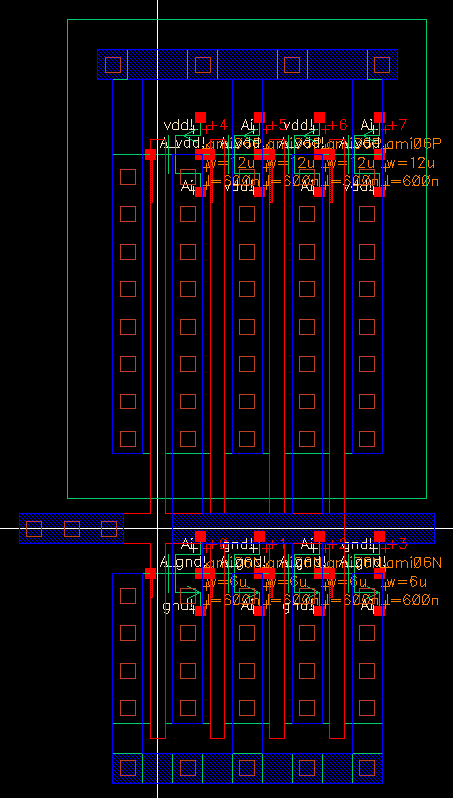

Similarly, the schematic of the second inverter was drafted using the

same methods as above.

This time around, the 'multiplier' parameter of the MOSFETS were

adjusted.

| Schematic |

Symbol |

|

|

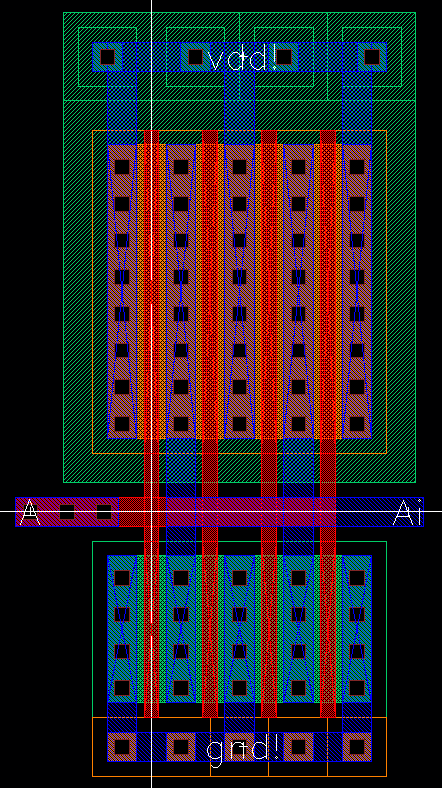

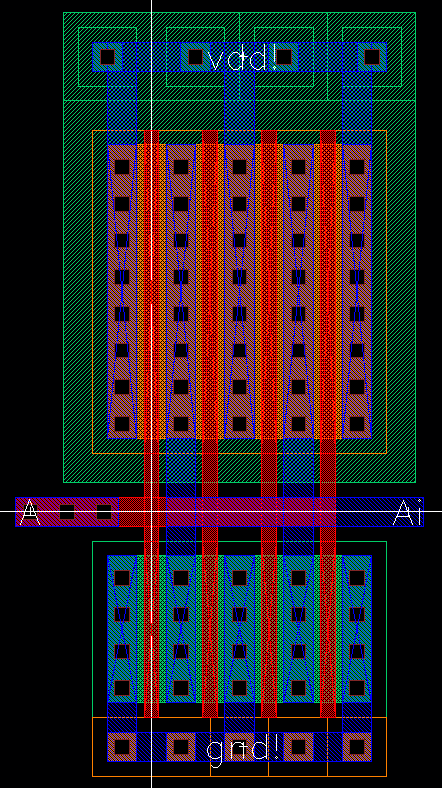

Just like the layout for the first inverter, I connected the terminals

of the MOSFET accordingly.

The deciding factor of which terminals were the source and drain

terminals was decided on the greater area.

| Layout |

Extracted |

|

|

DRC

successful

LVS

successful

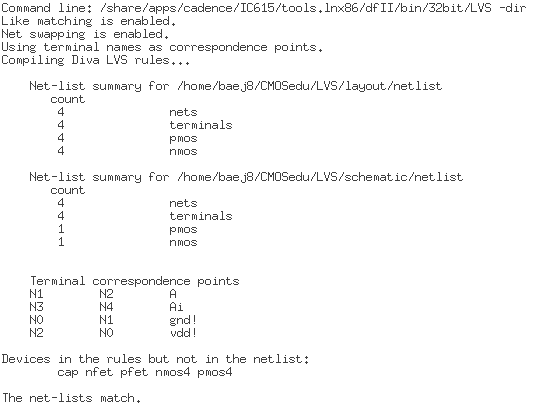

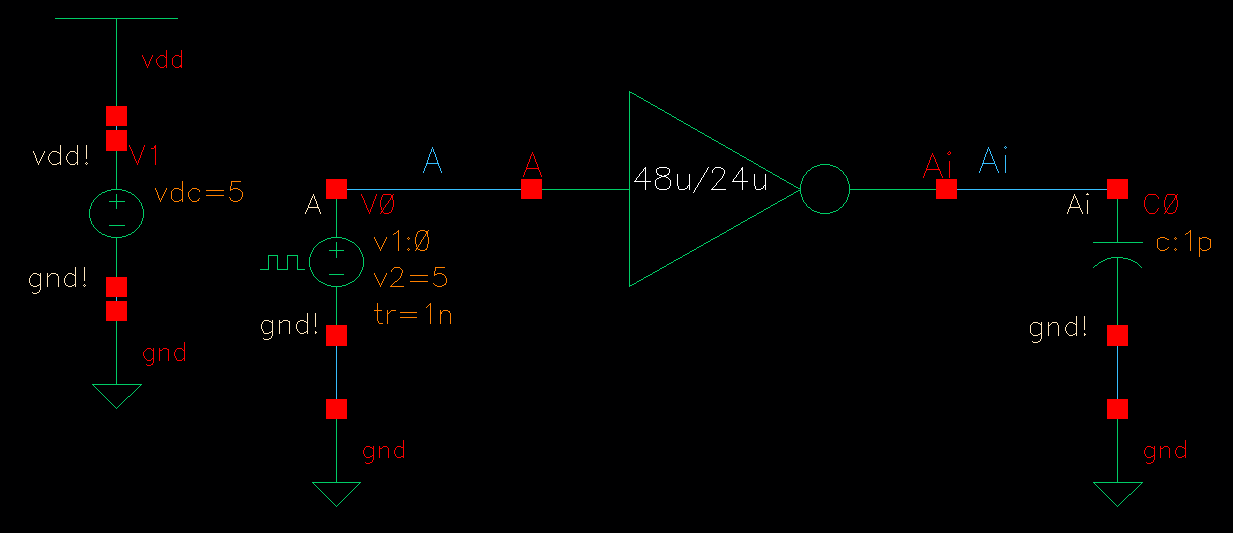

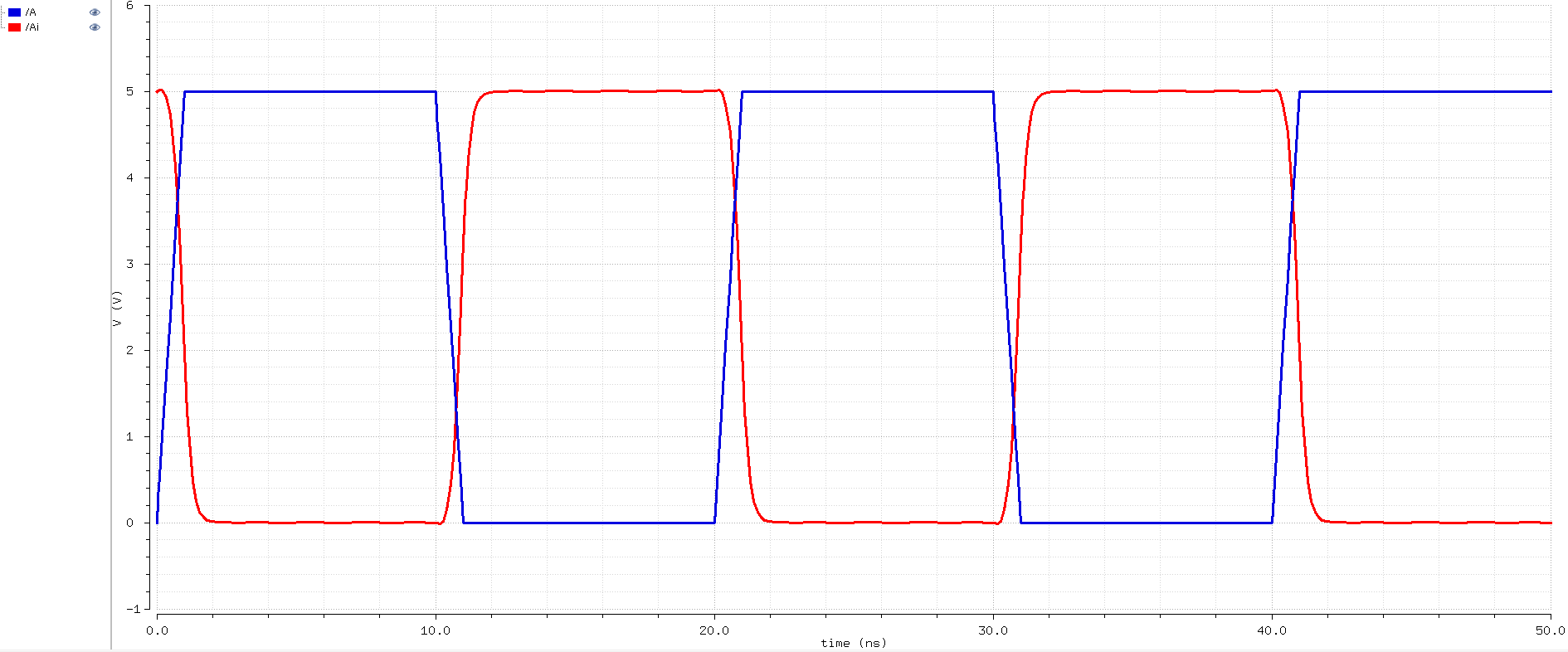

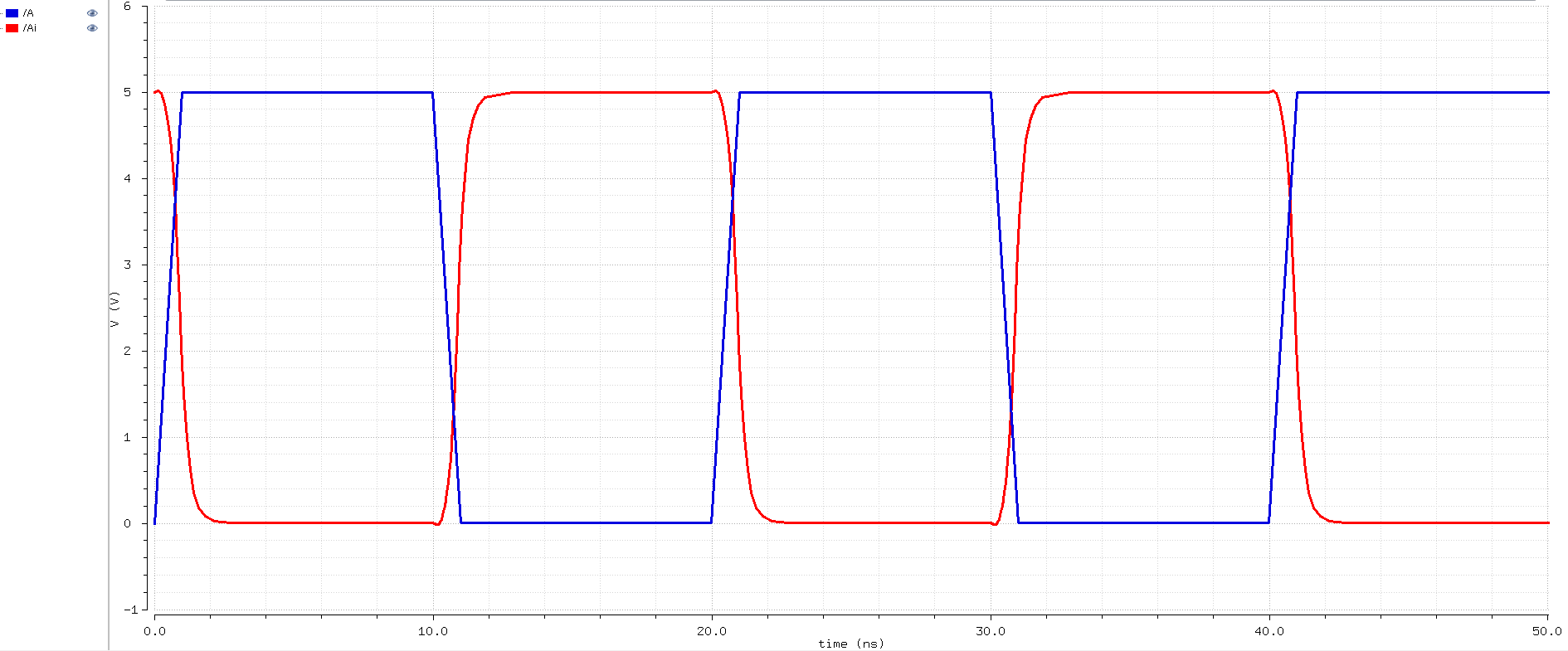

SPICE

simulations

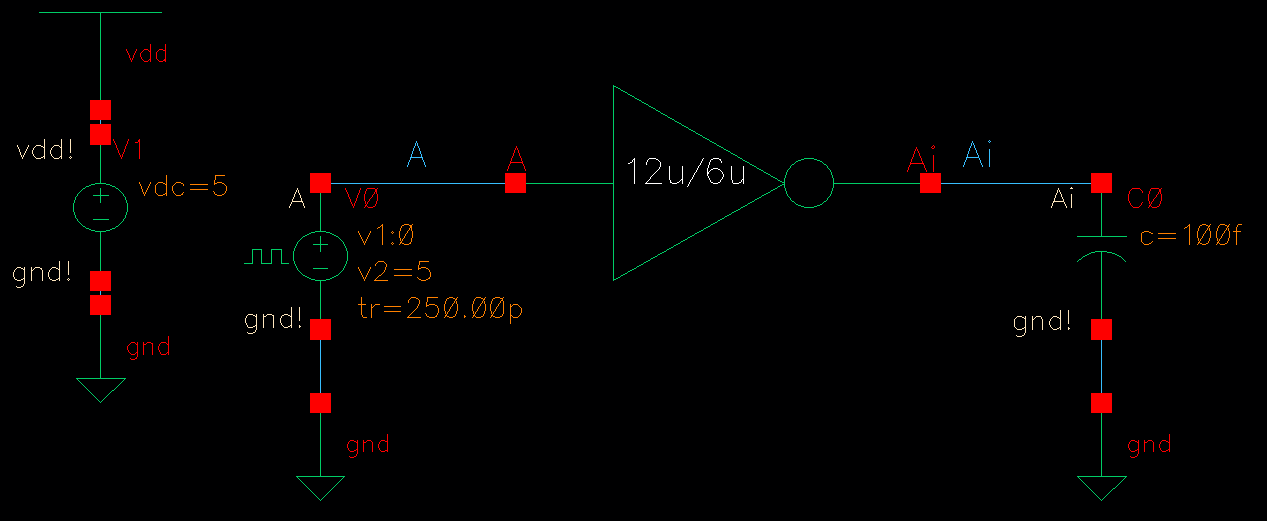

12u/6u Inverter

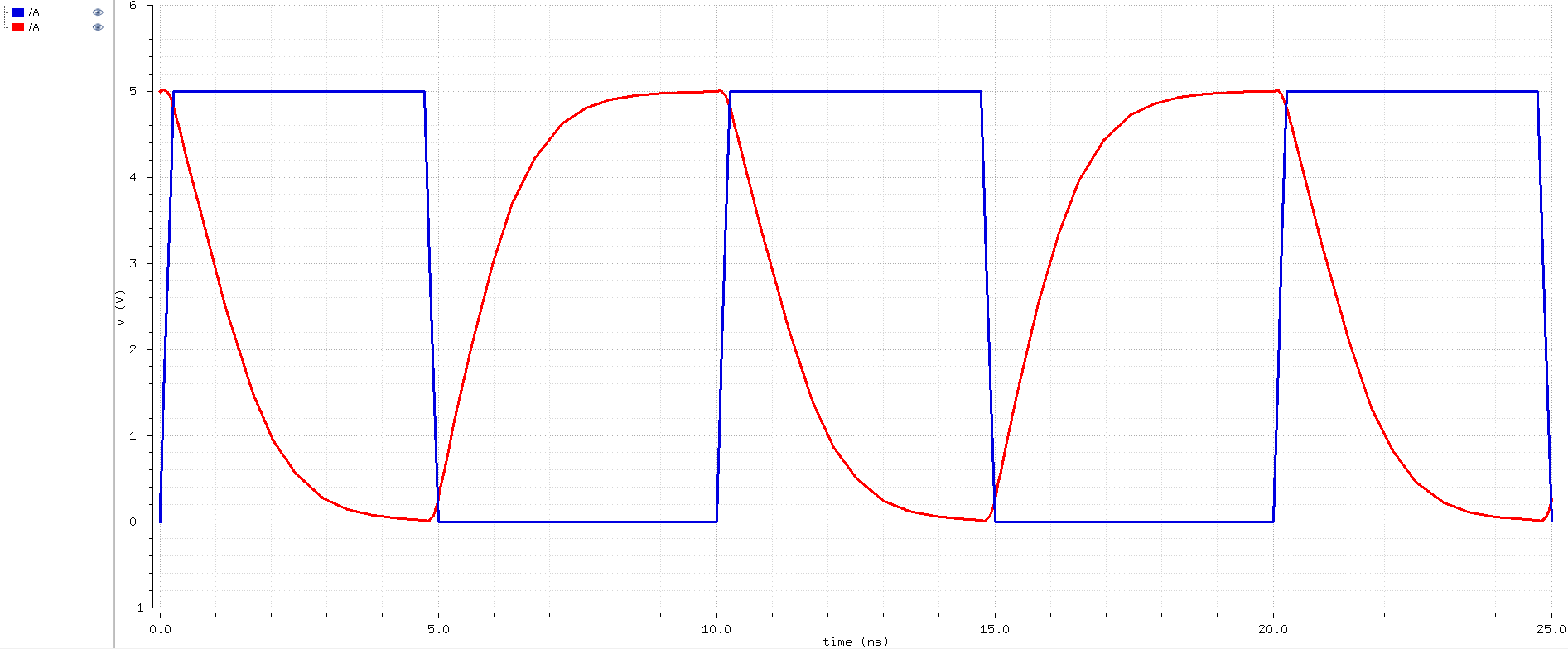

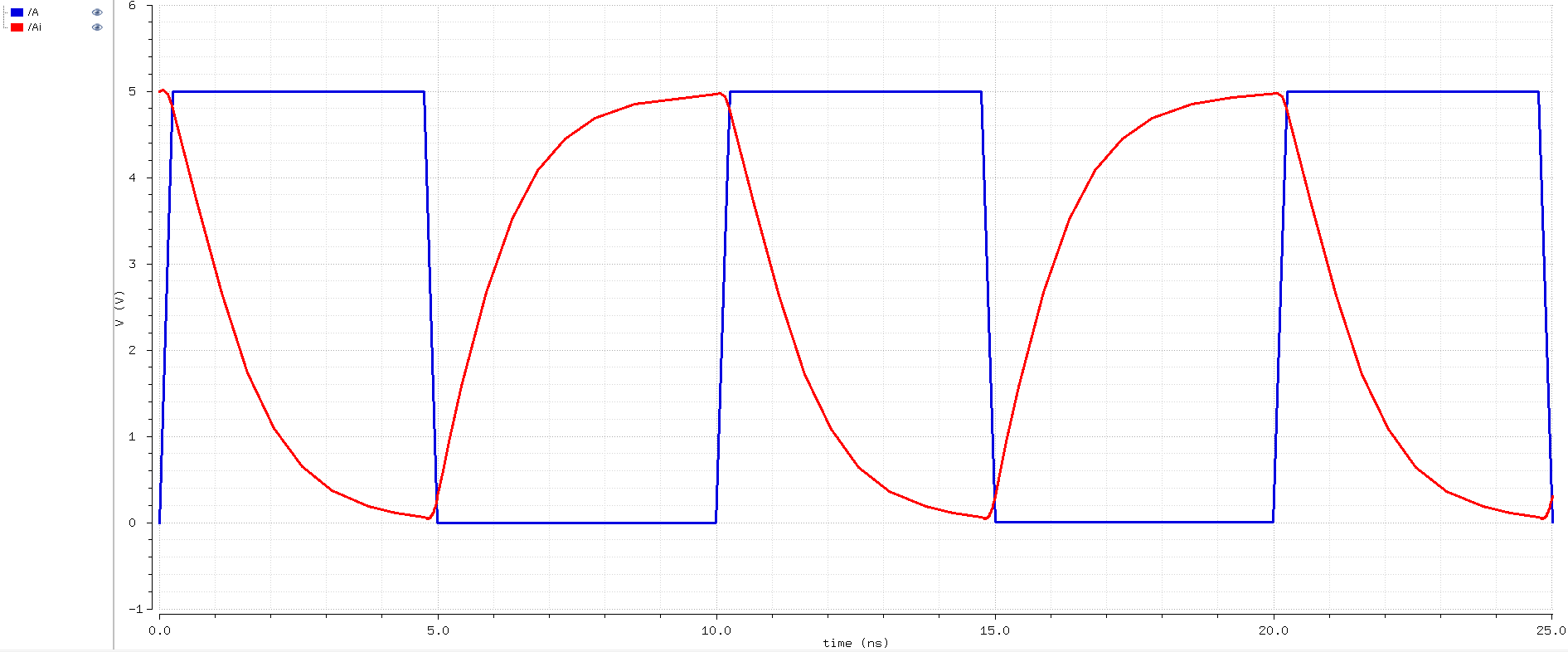

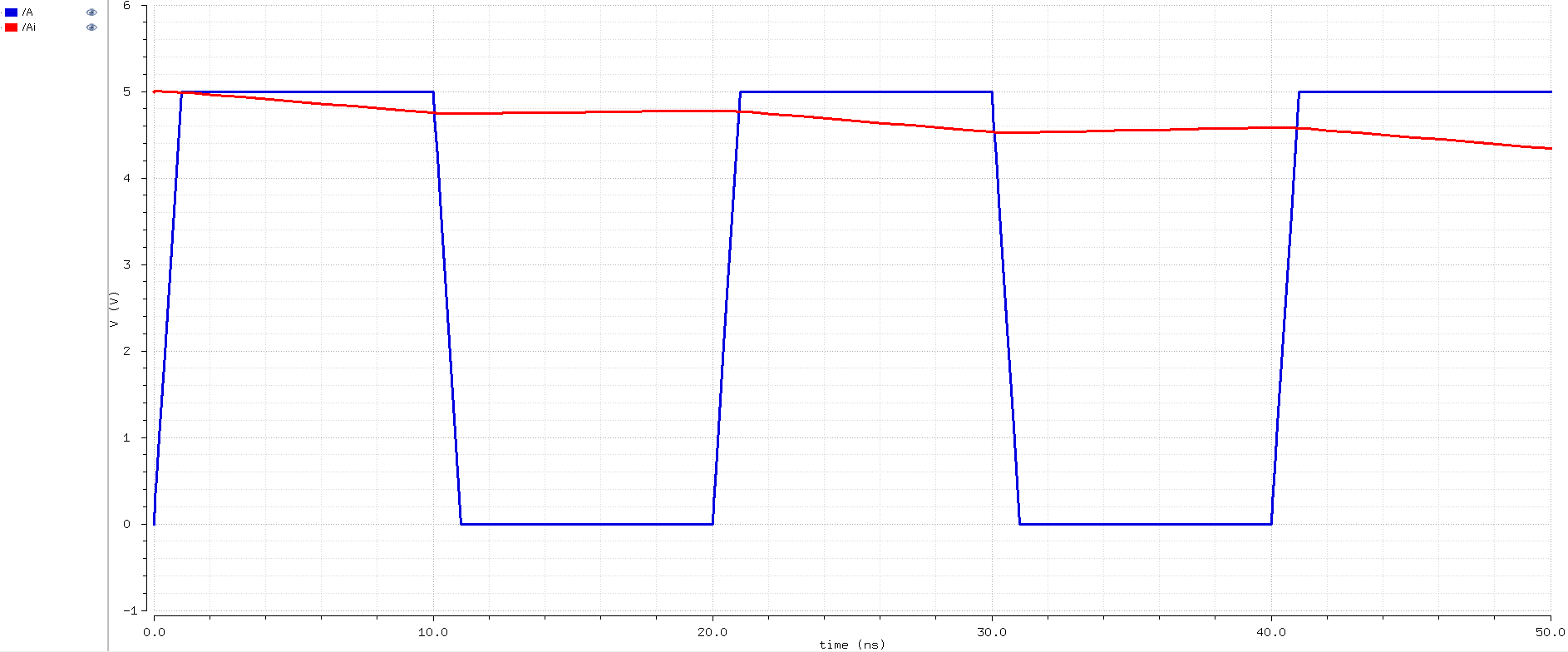

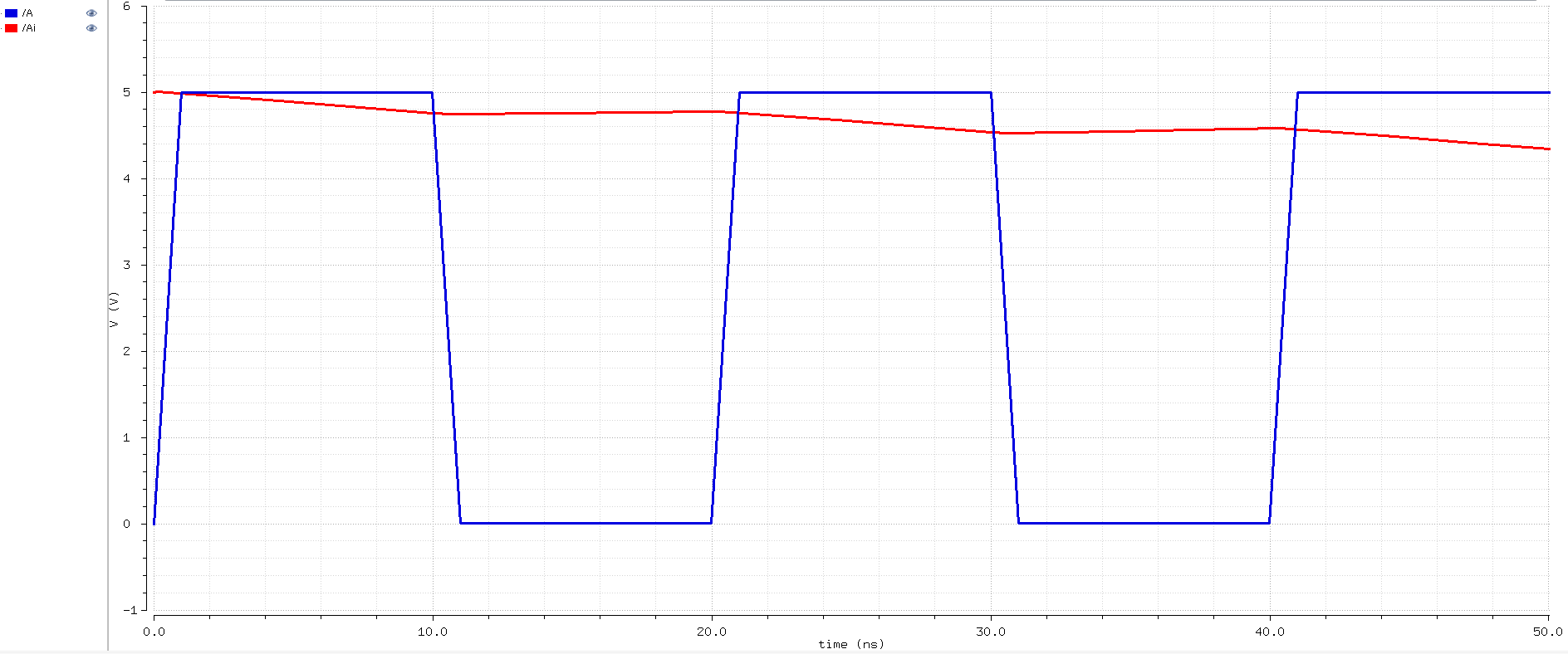

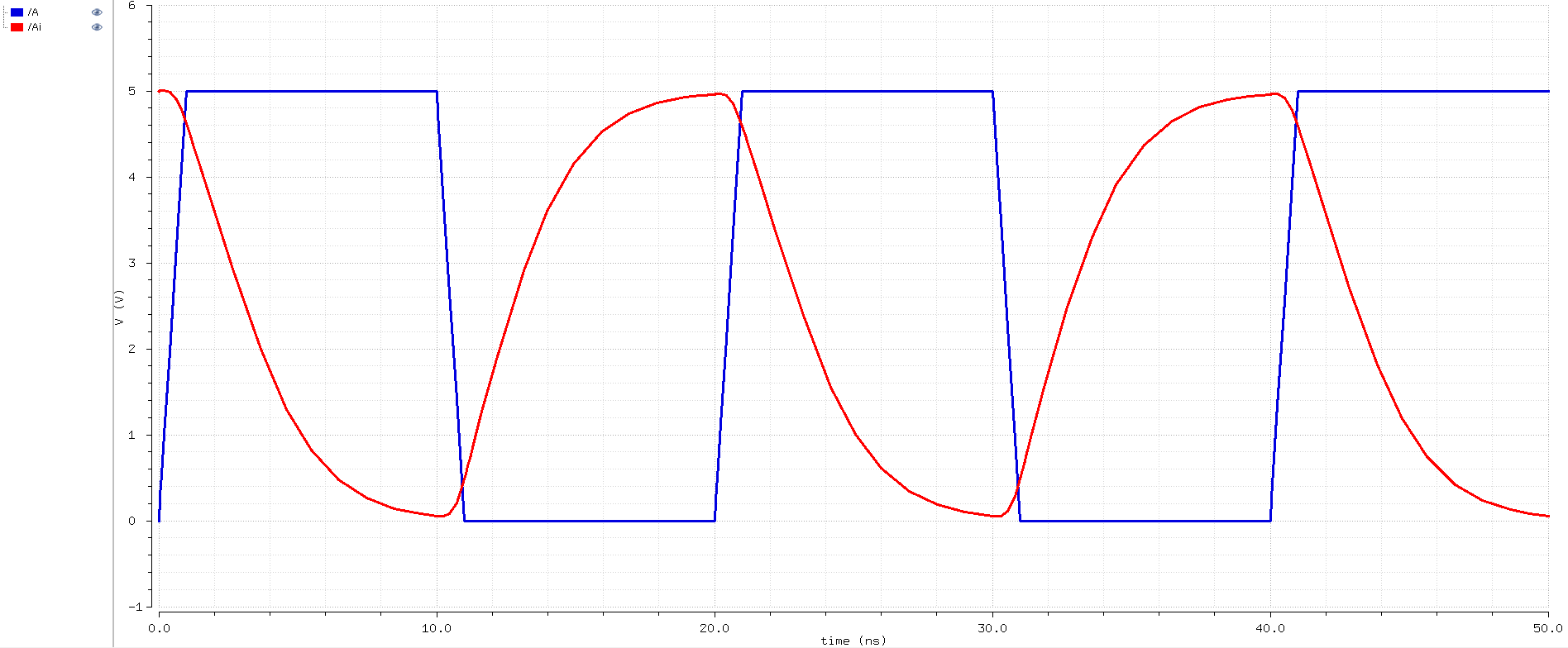

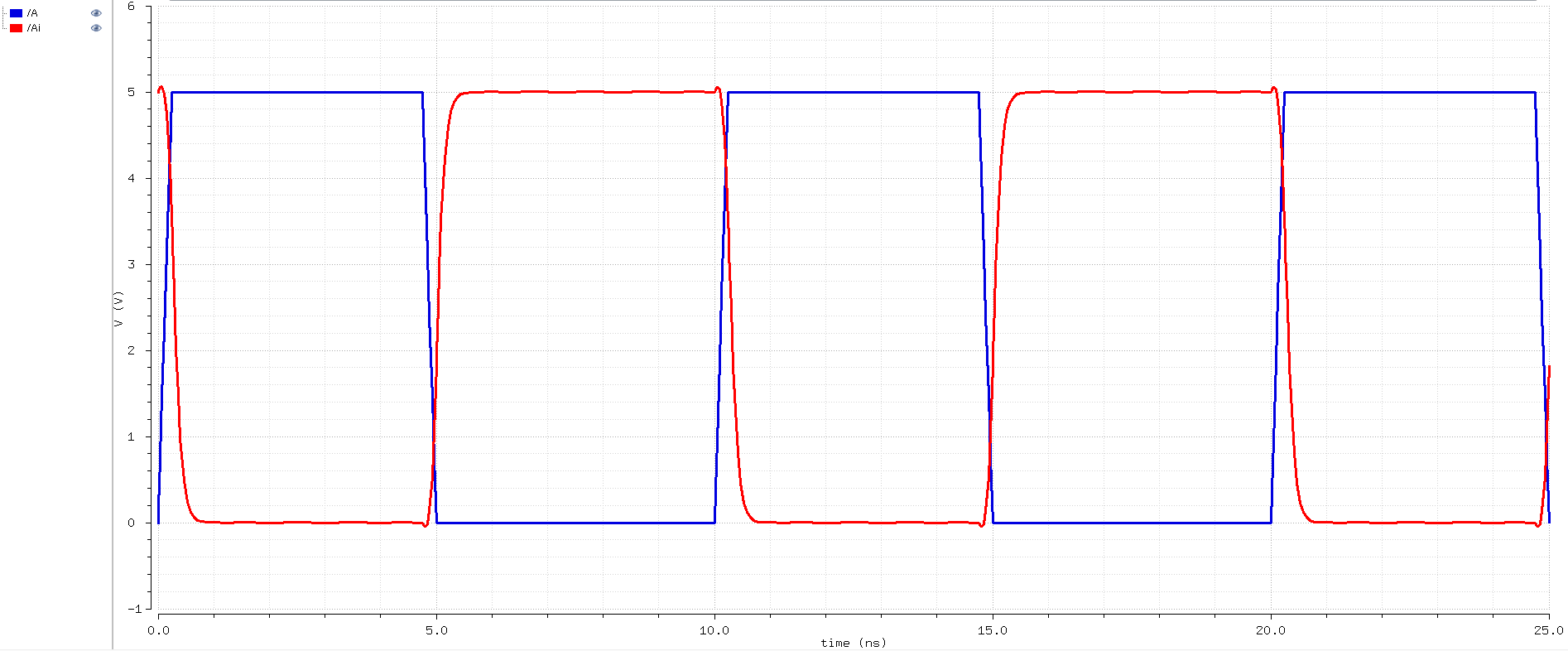

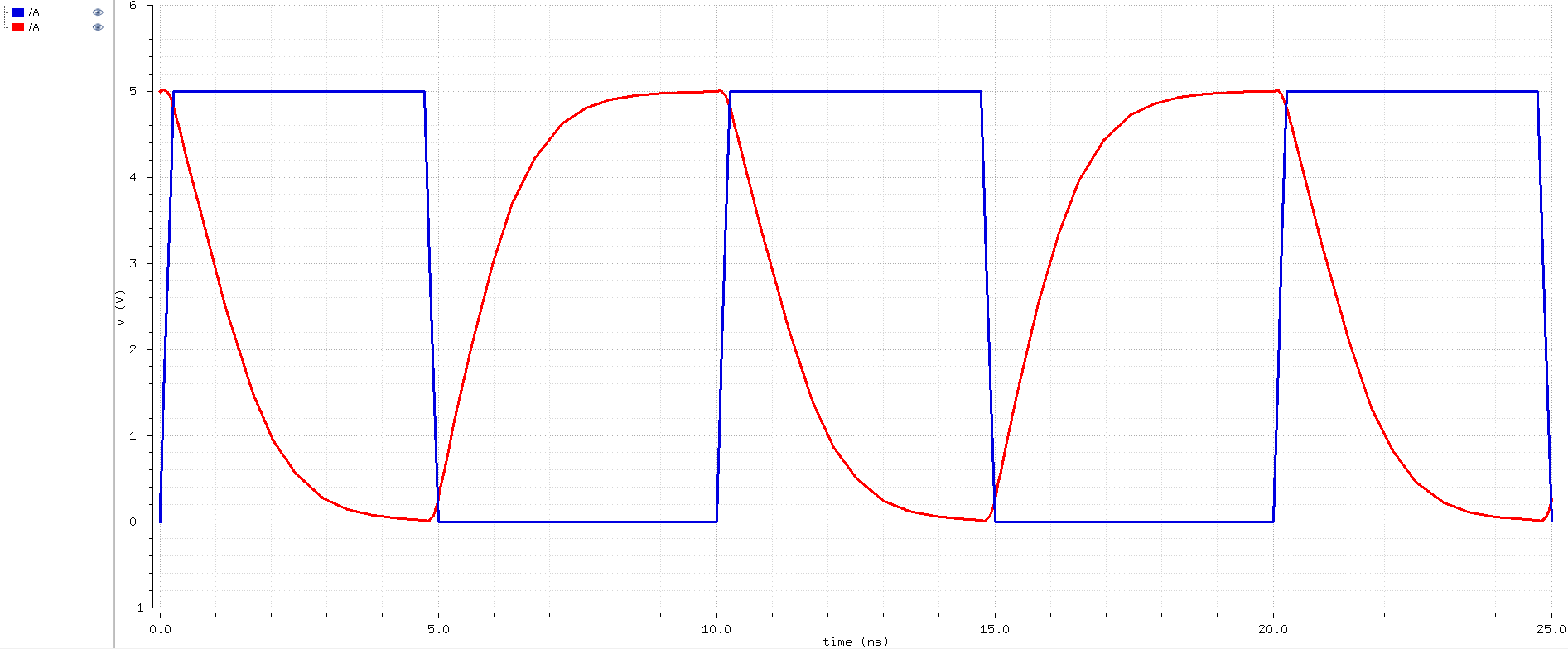

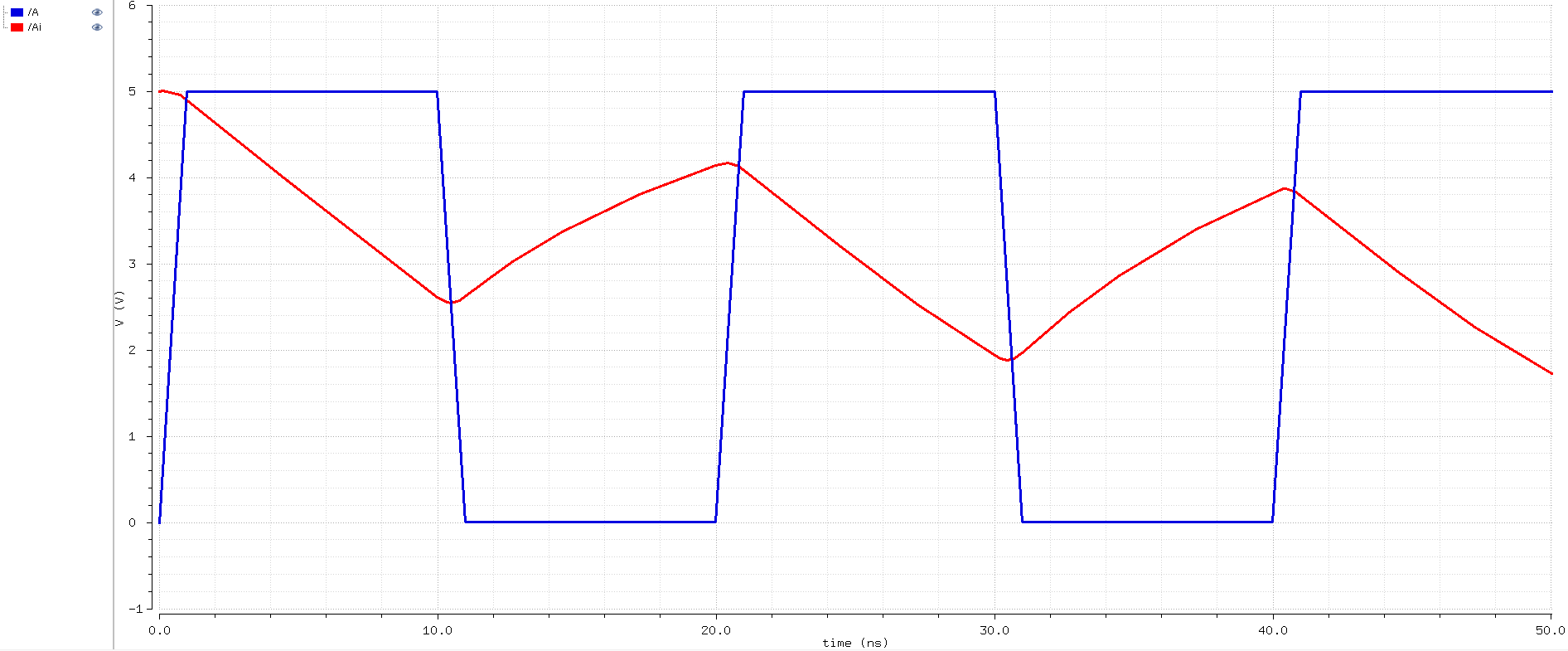

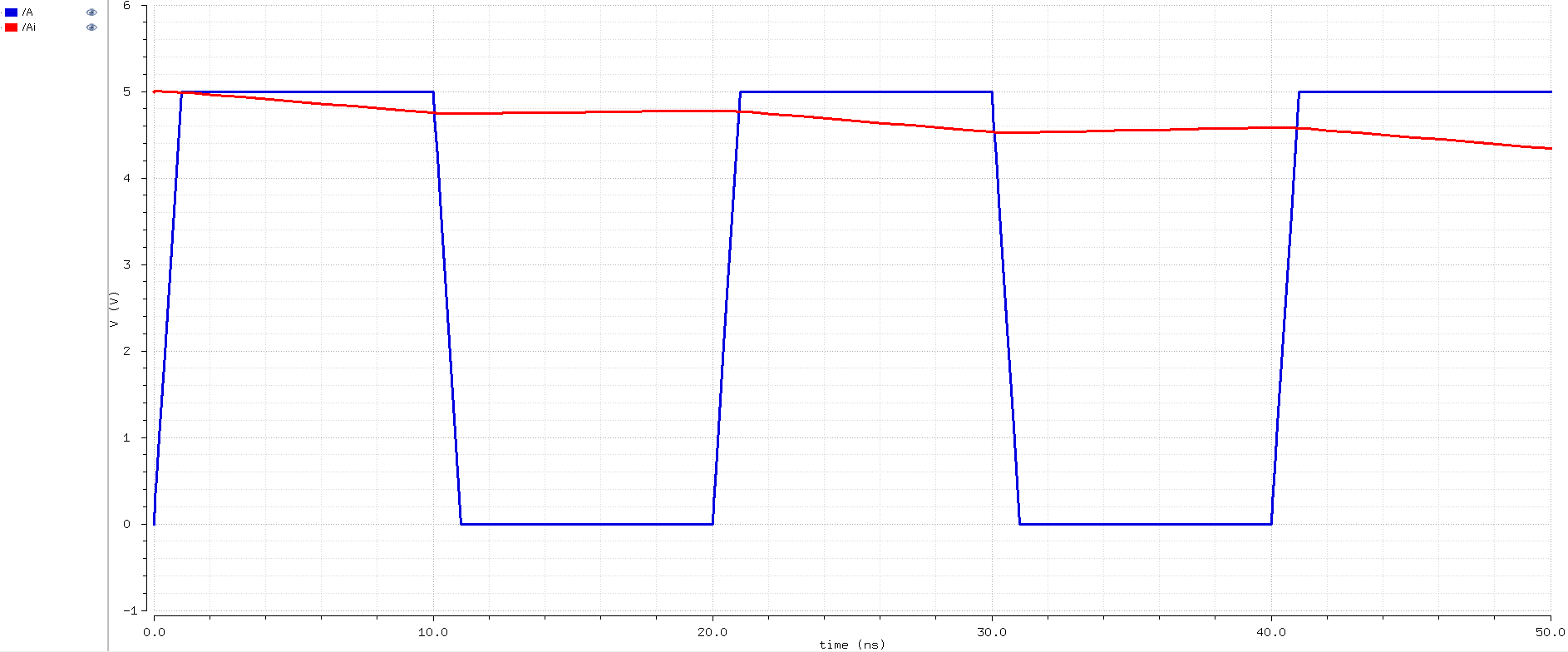

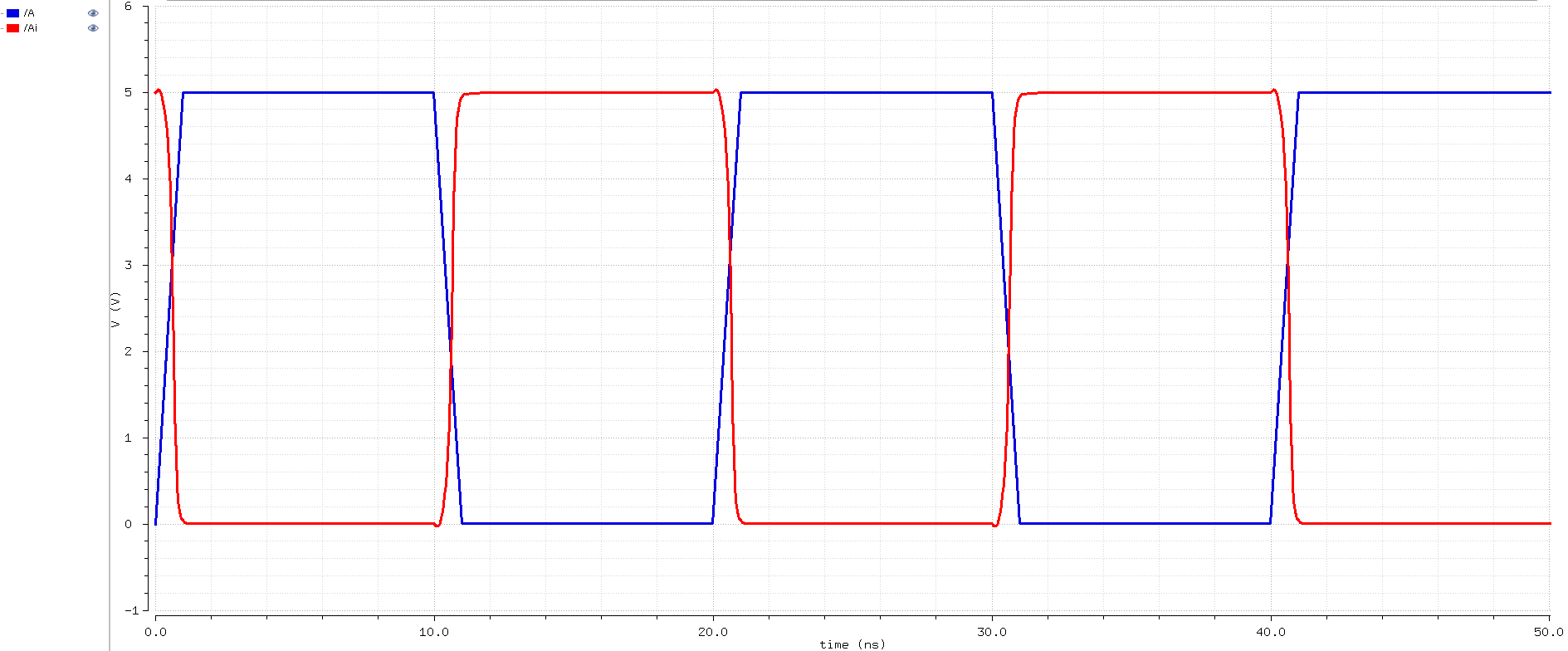

| Capacitive

Load |

Schematic |

Spectre |

UltraSim |

| 100 fF |

|

|

|

| 1

pF |

|

|

|

| 10

pF |

|

|

|

| 100

pF |

|

|

|

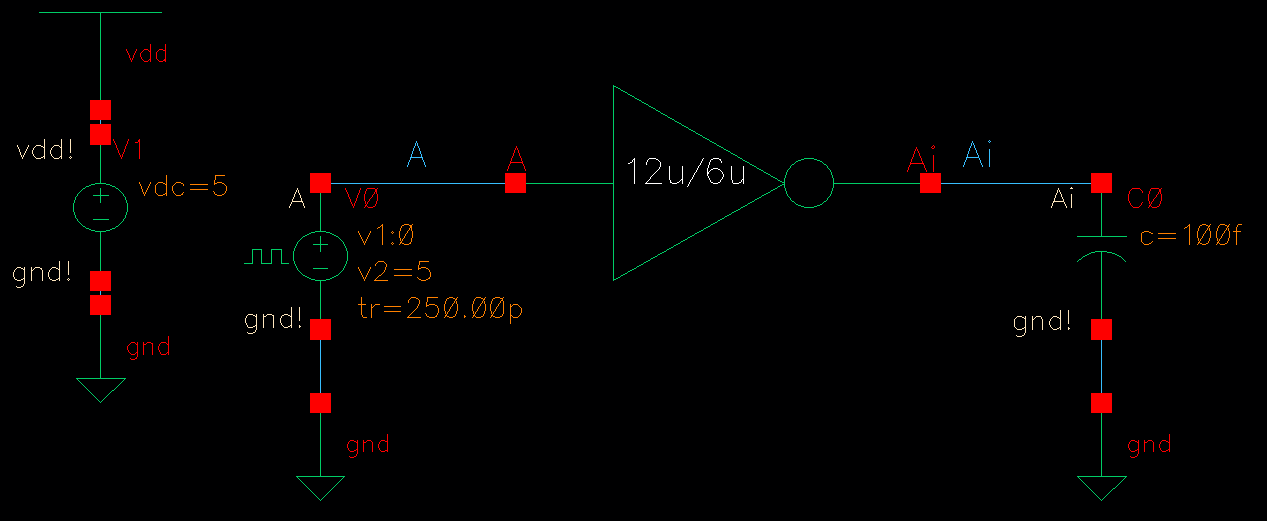

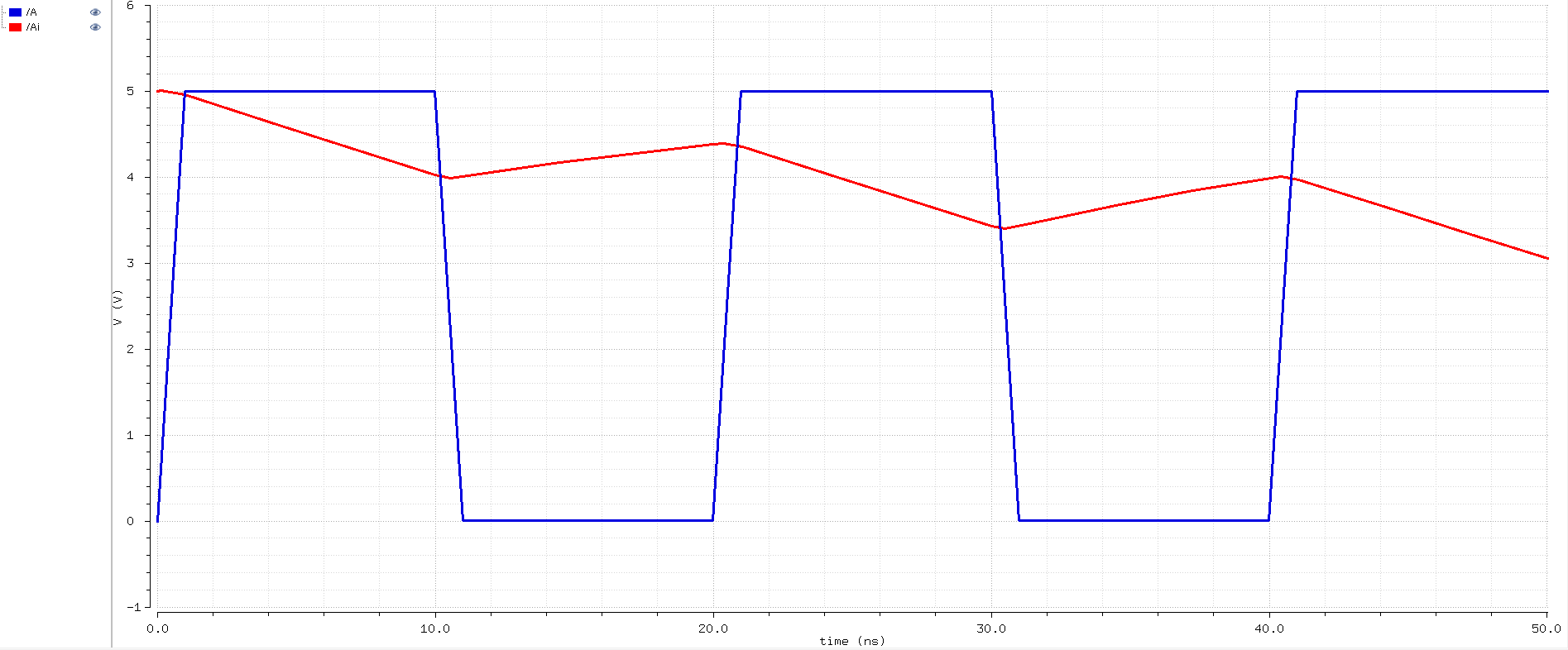

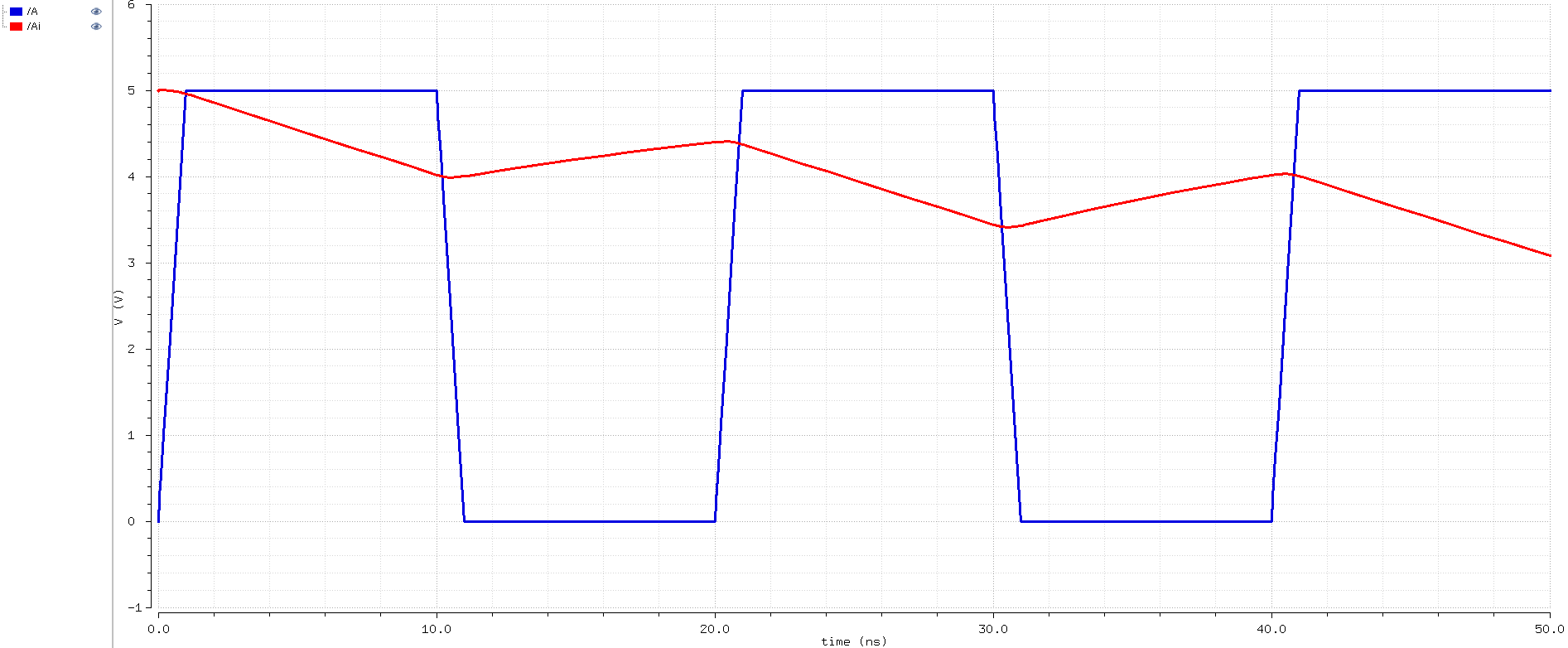

As

the capacitor values increased, the inverted signal was affected more

and more. Because it takes longer to charge and discharge the

capacitors due to an increase in time delay, the capacitors could not

be charged fast enough which resulted in poor output signals. This

could be resolved by decreasing the frequency of the input signal, or

keeping the capacitive load to a minimum.

In addition, there were

minimum differences between the normal simulation tool that Cadence

uses (Spectre) and Cadence's fast SPICE simulator (UltraSim).

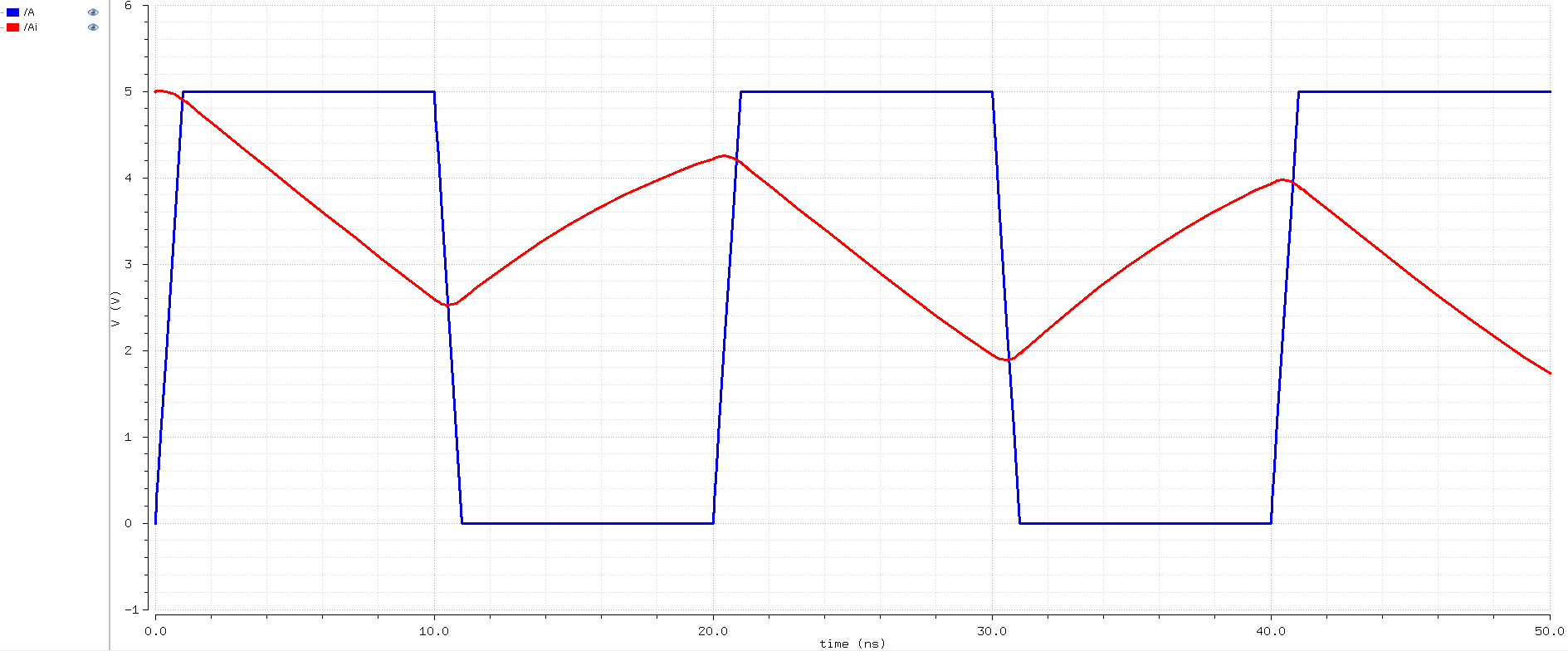

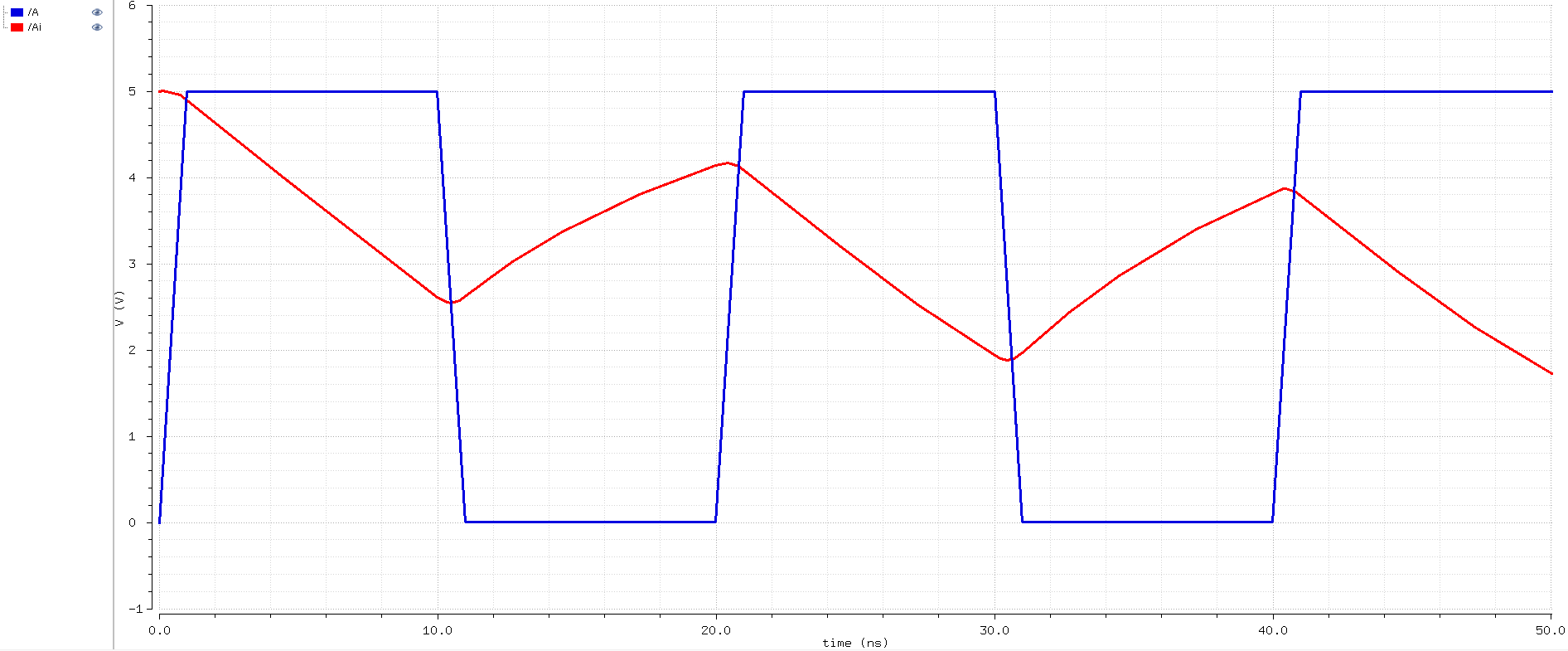

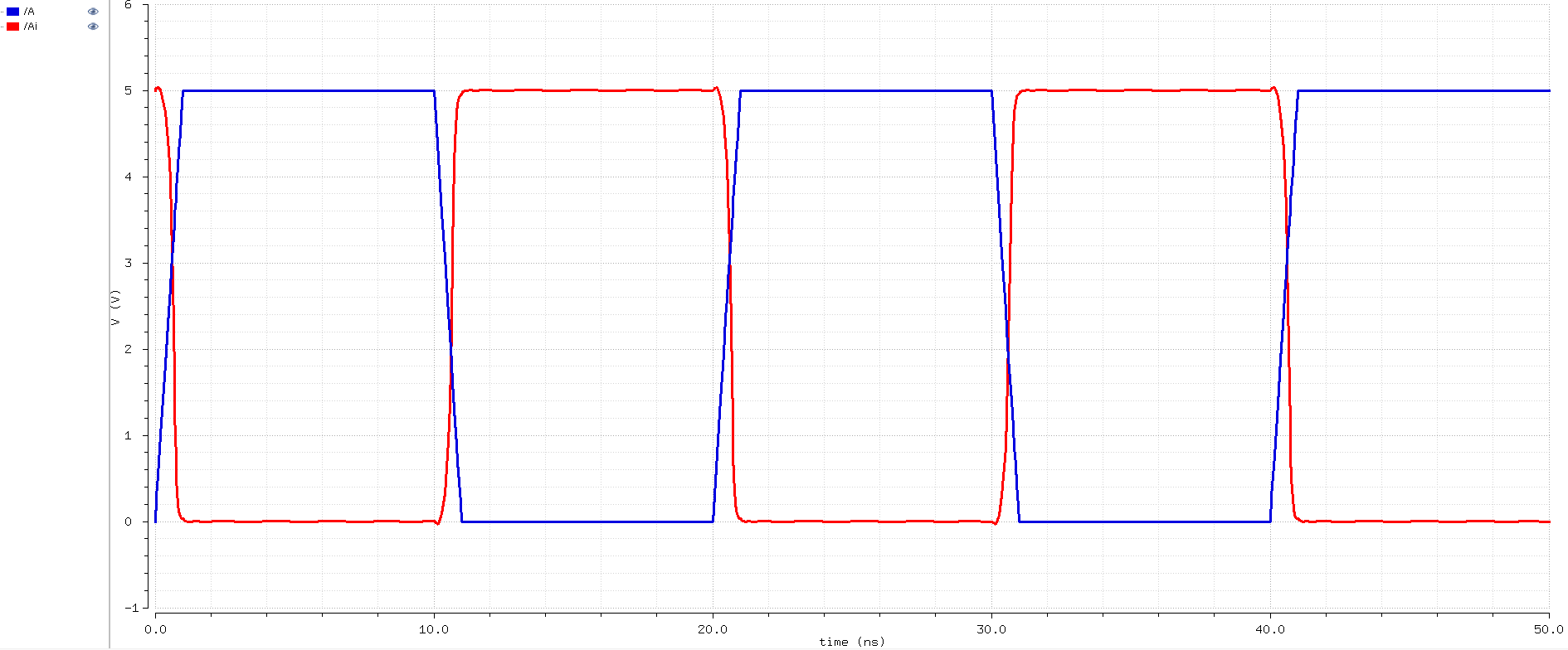

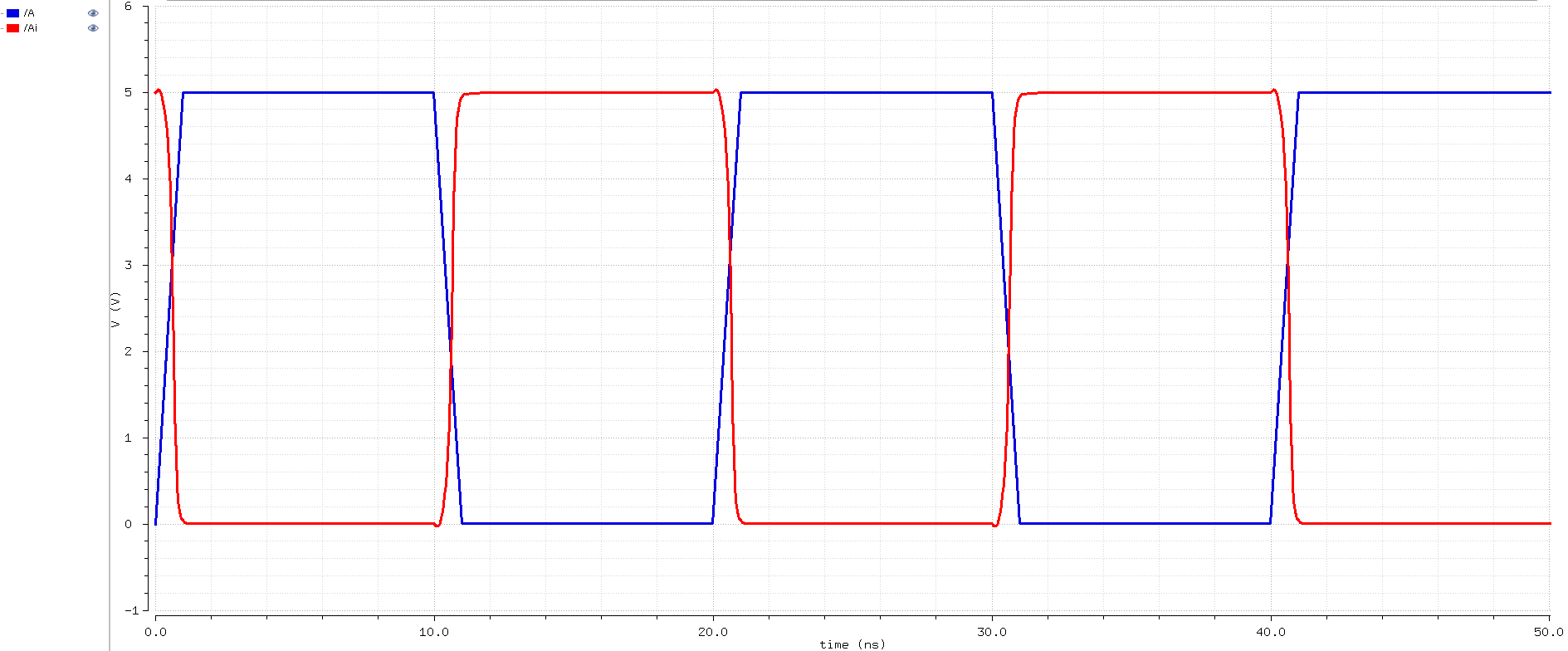

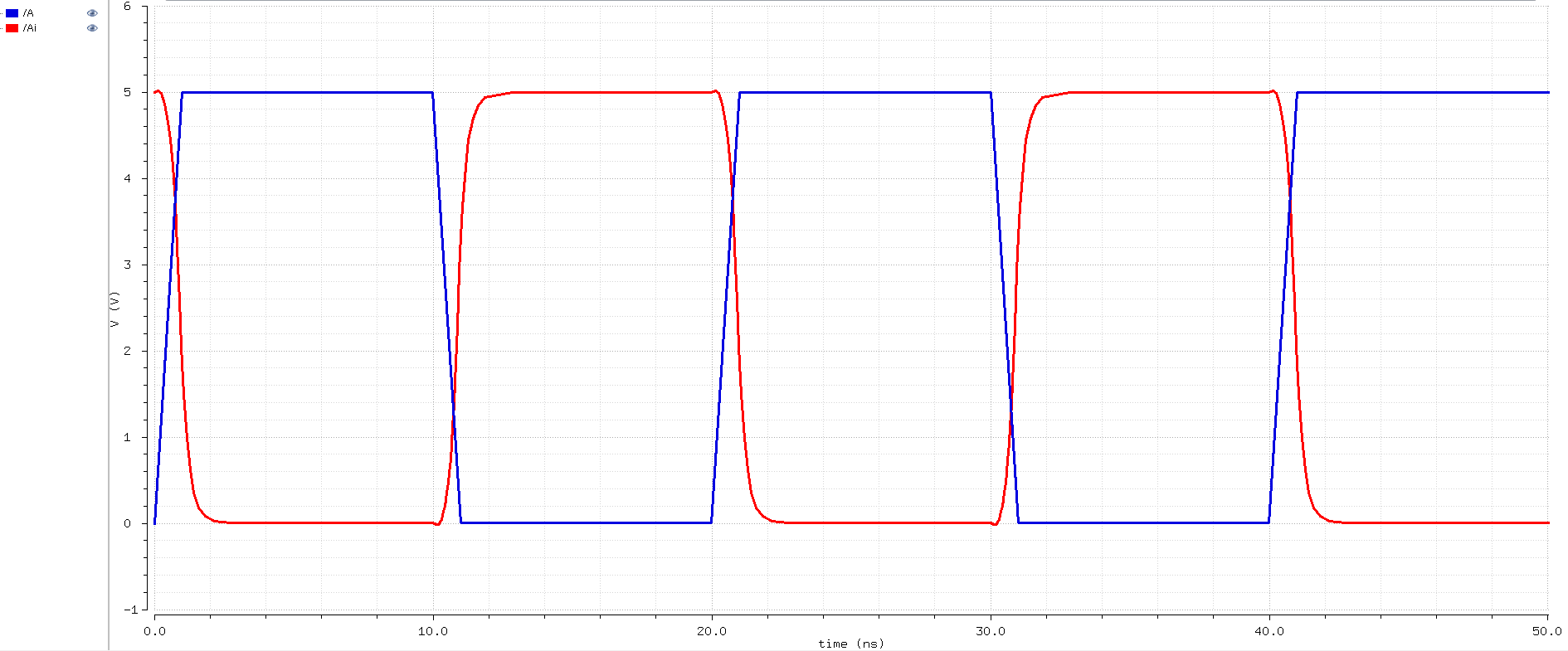

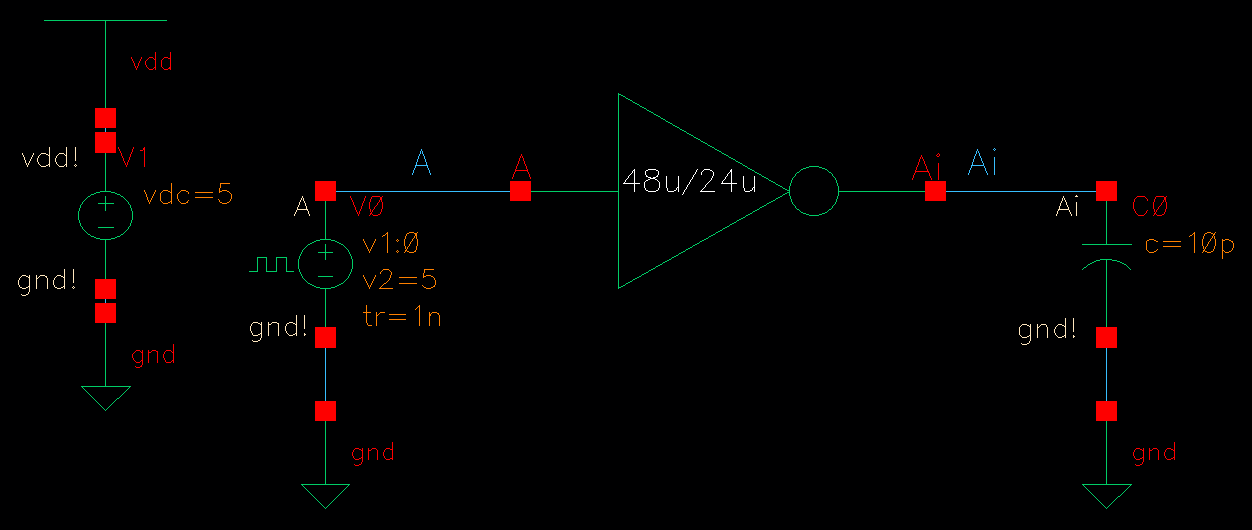

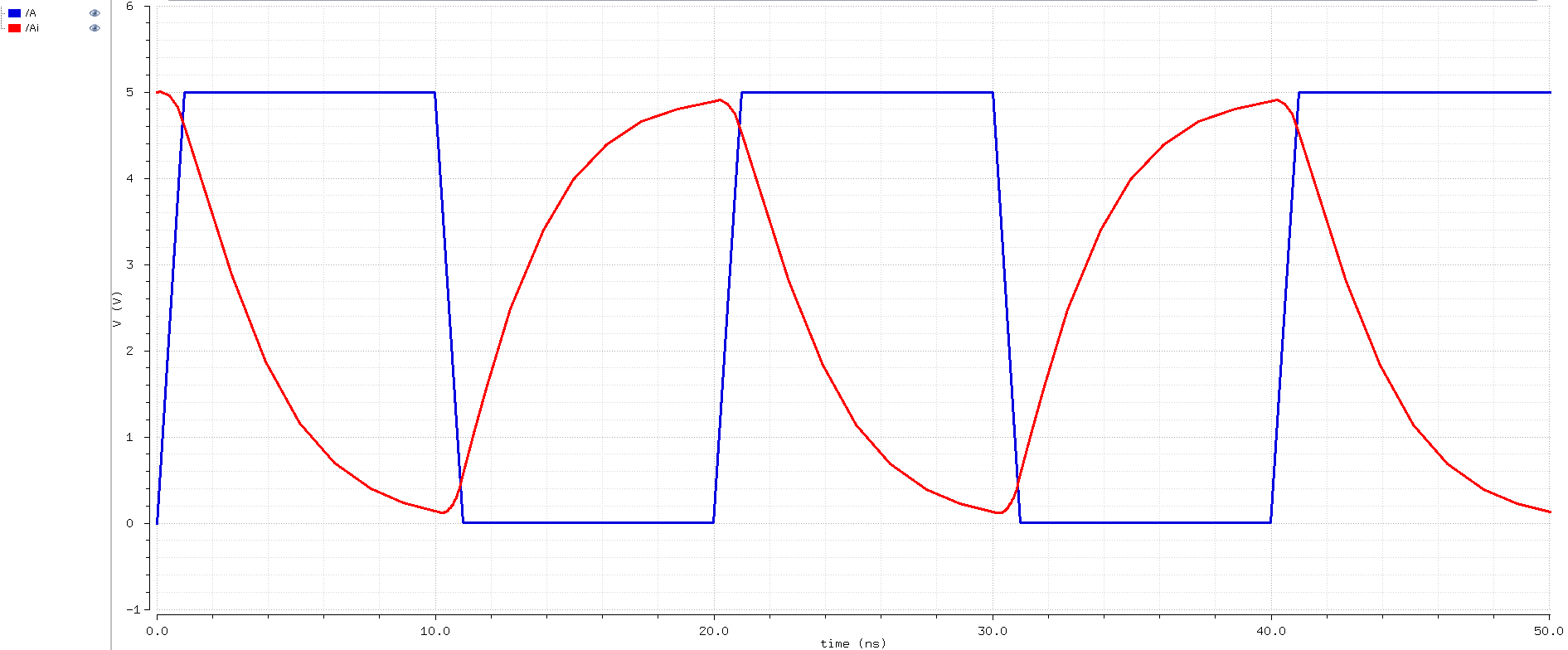

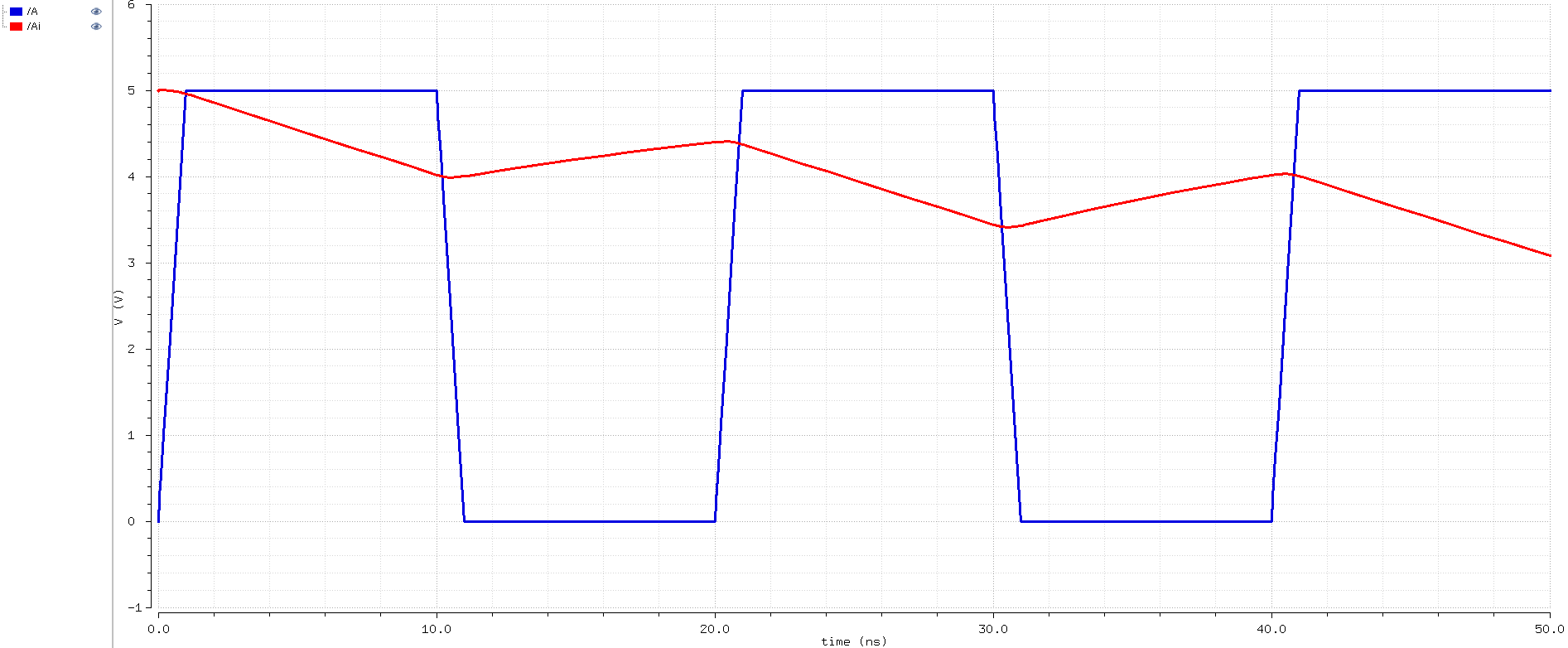

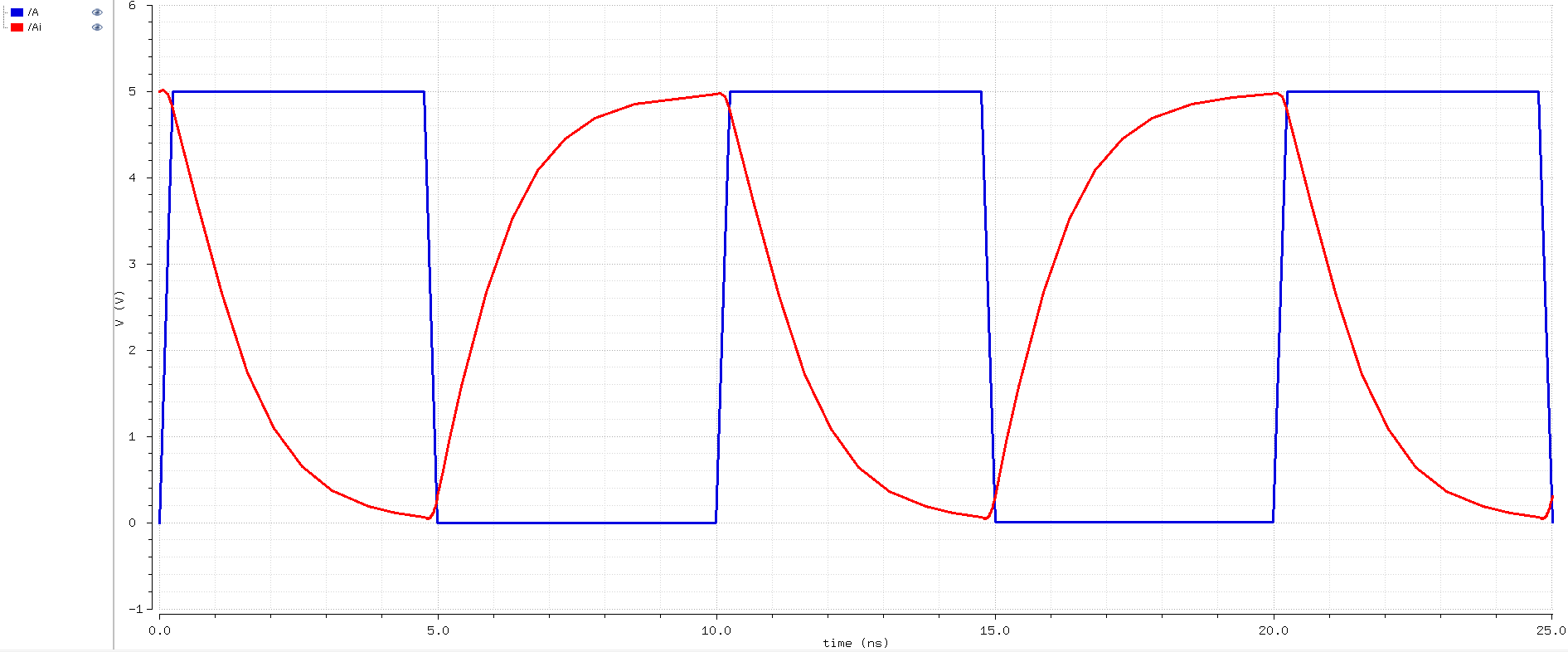

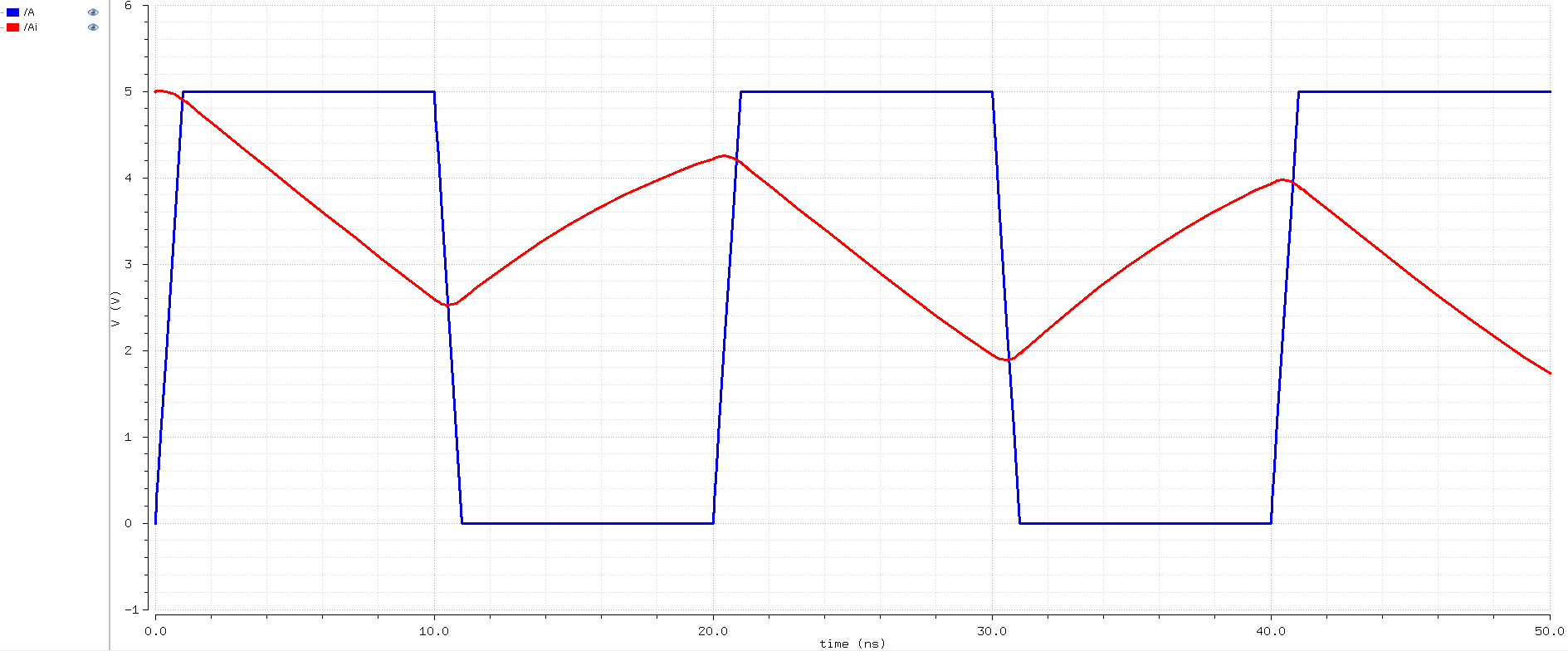

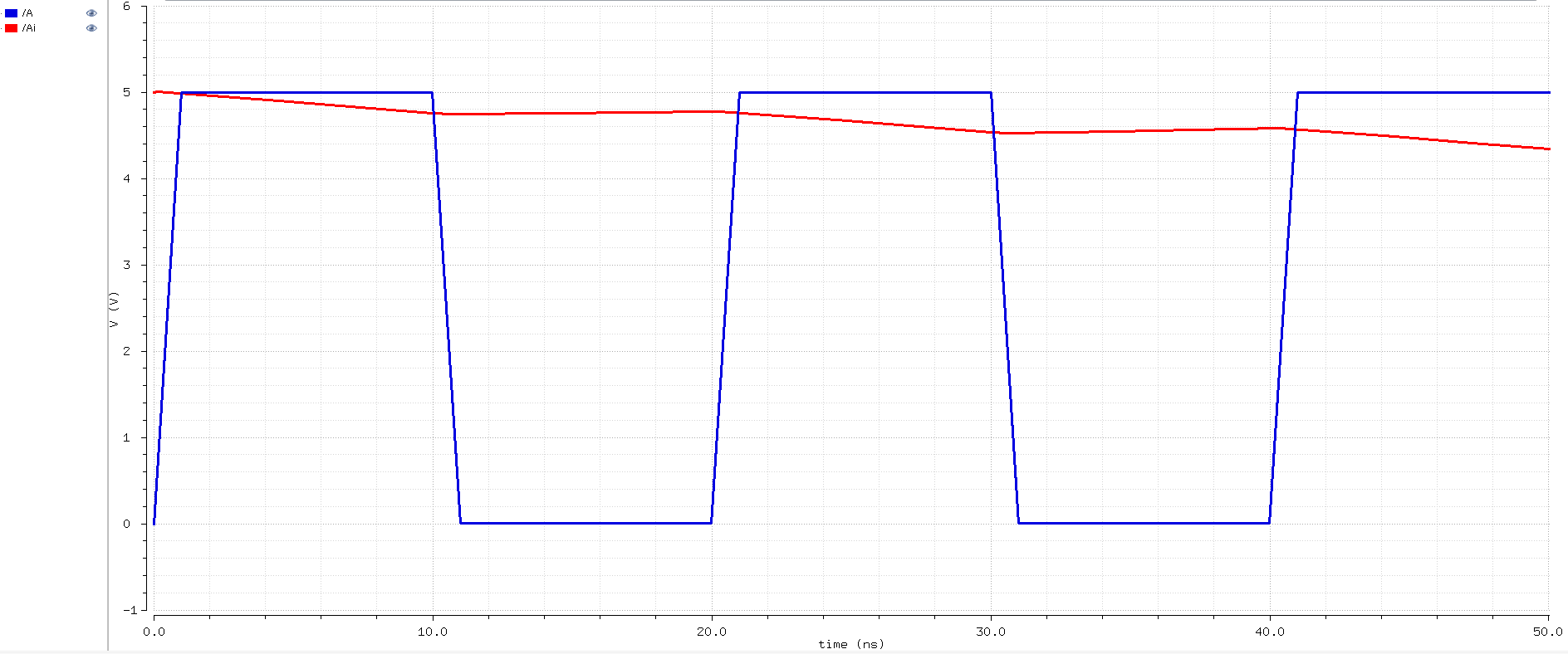

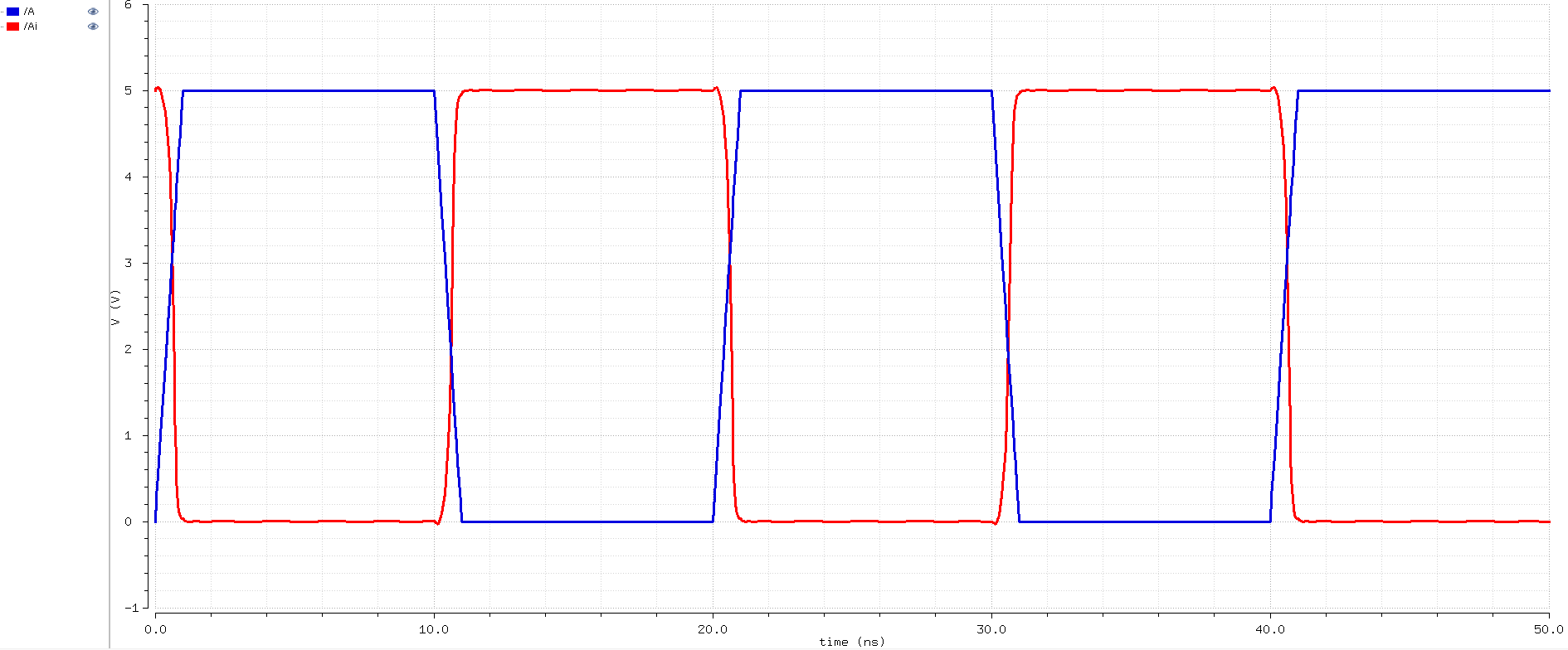

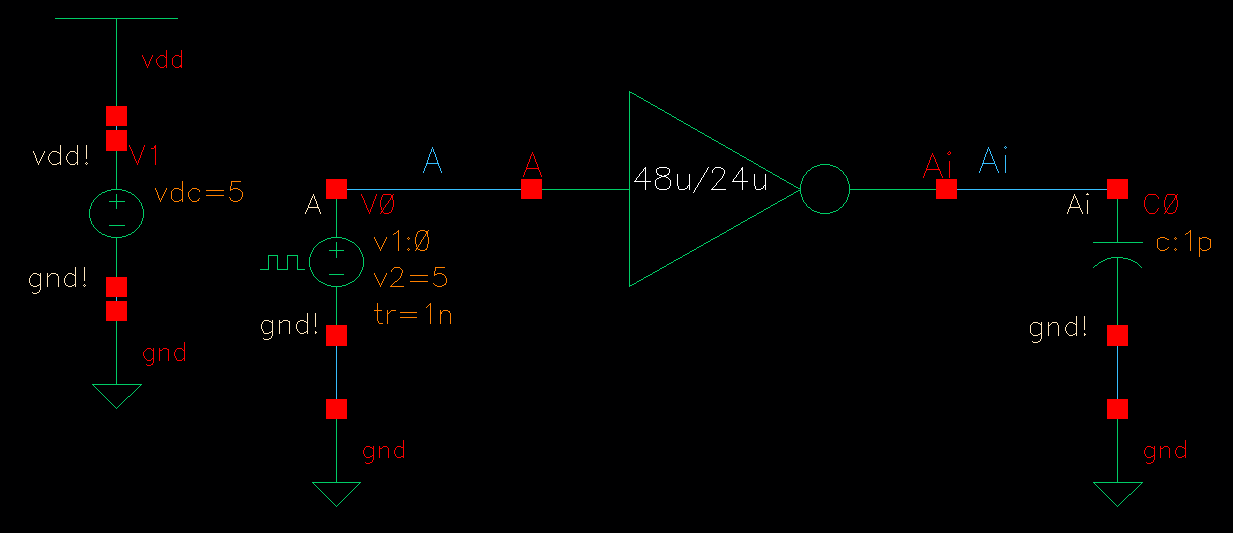

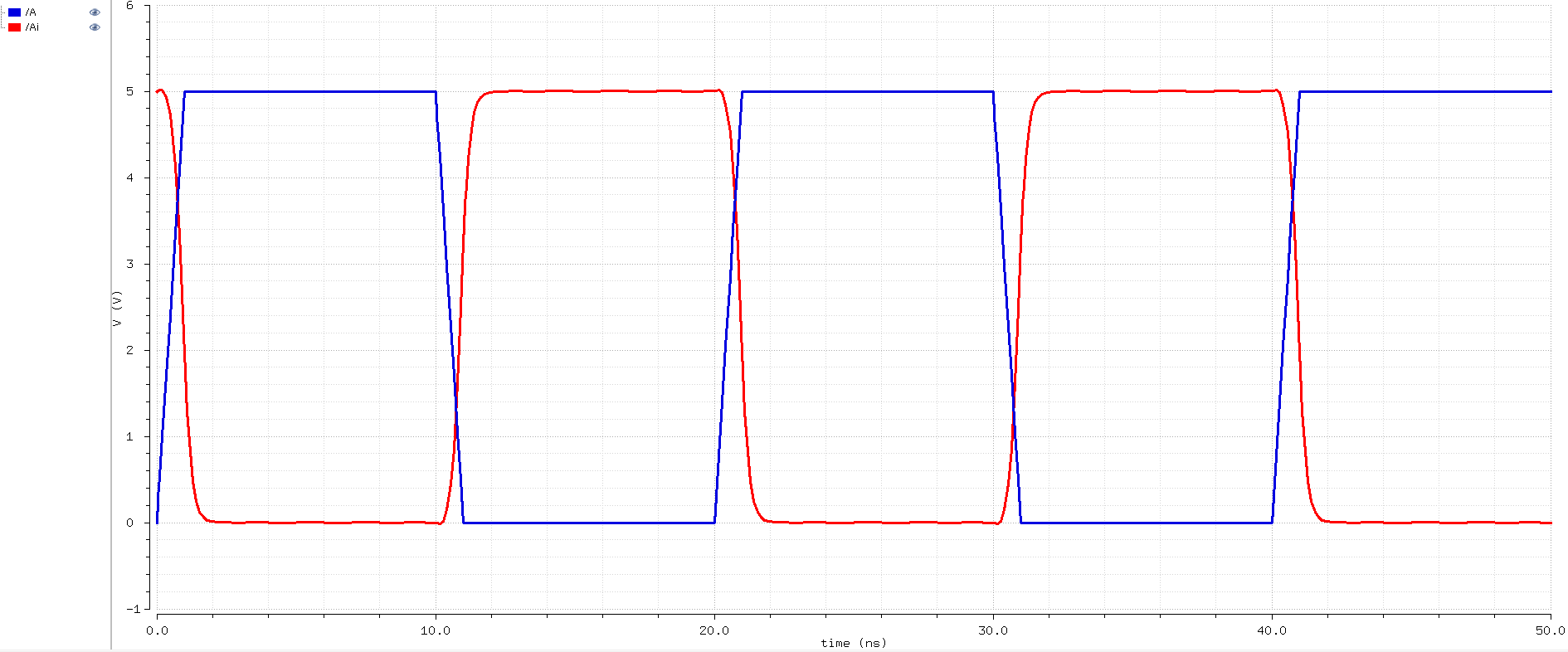

SPICE

simulations

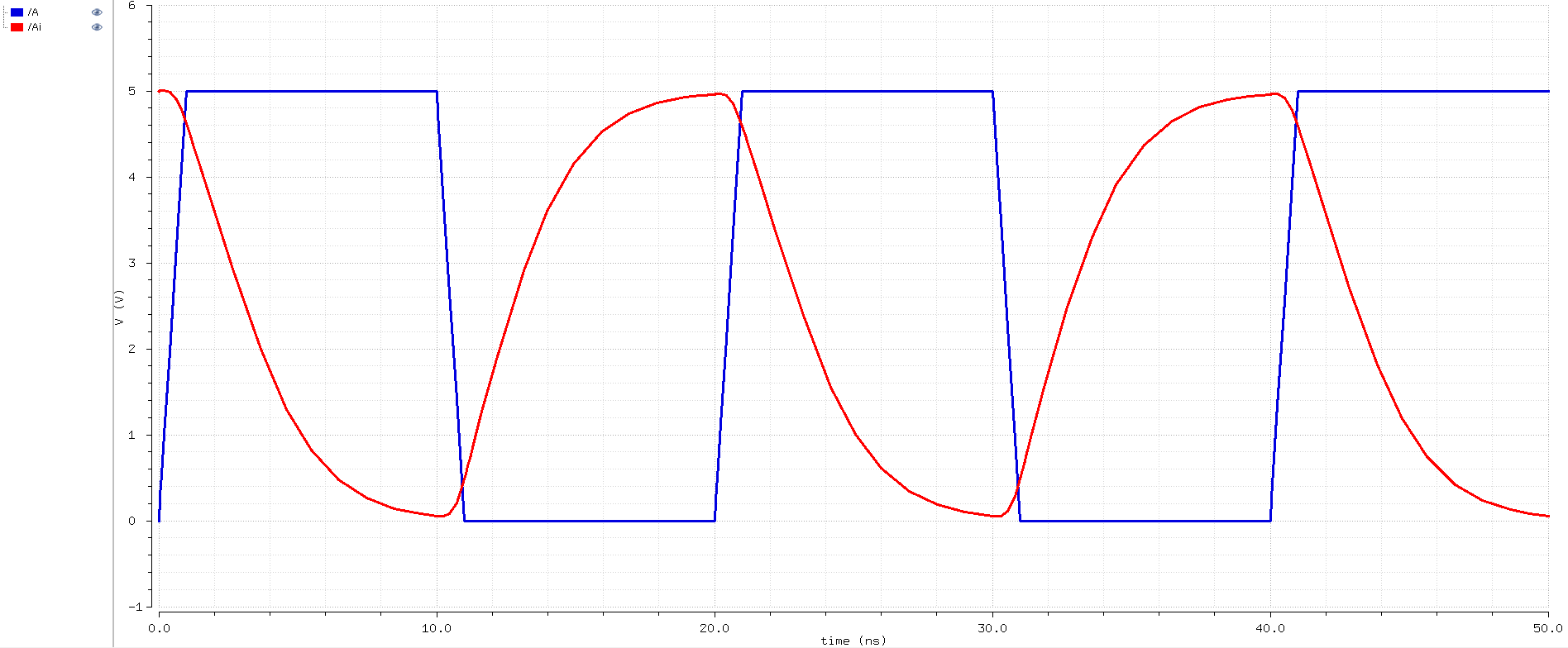

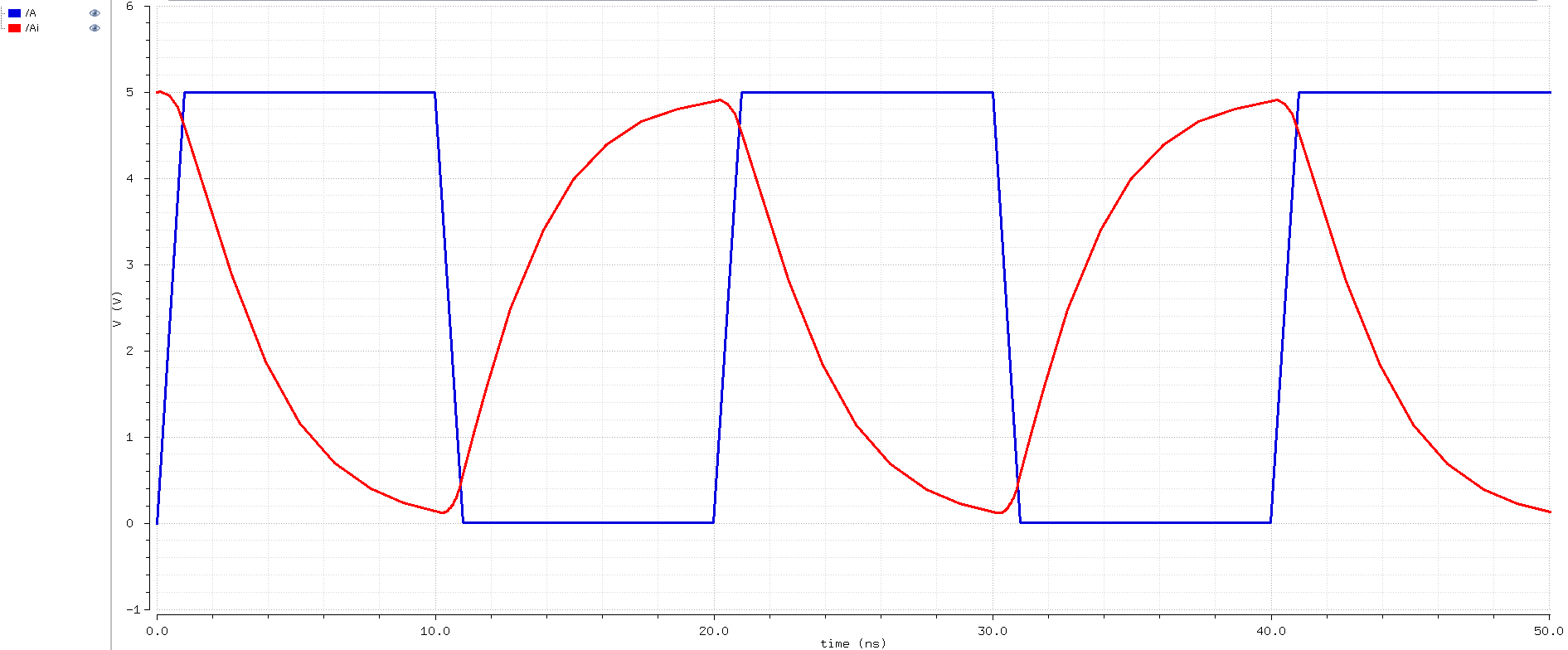

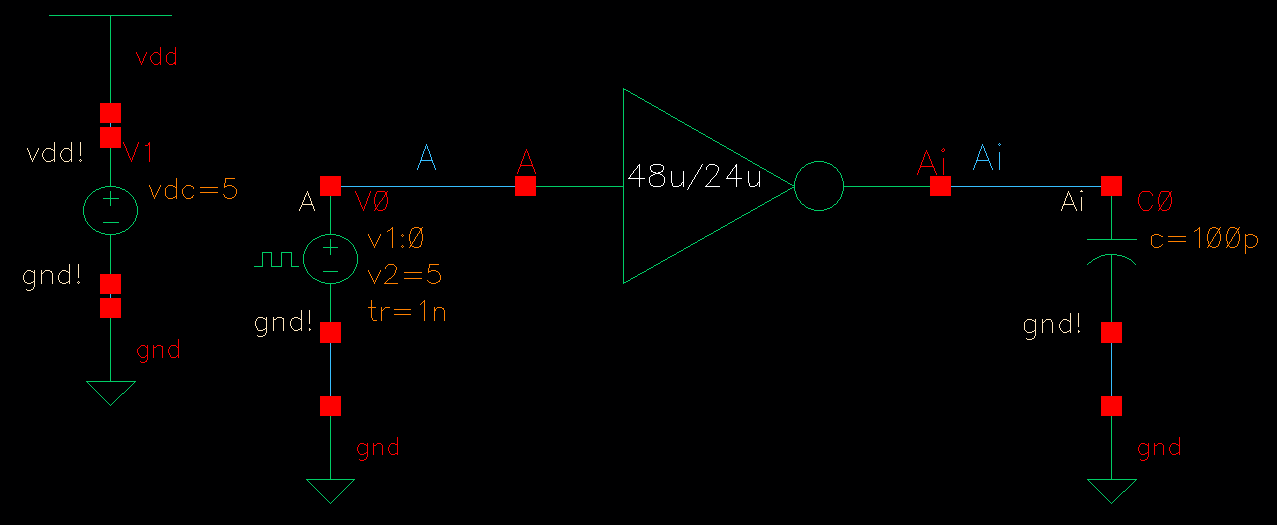

48u/24u inverter

| Capacitive

Load |

Schematic |

Spectre |

UltraSim |

| 100 fF |

|

|

|

| 1

pF |

|

|

|

| 10

pF |

|

|

|

| 100

pF |

|

|

|

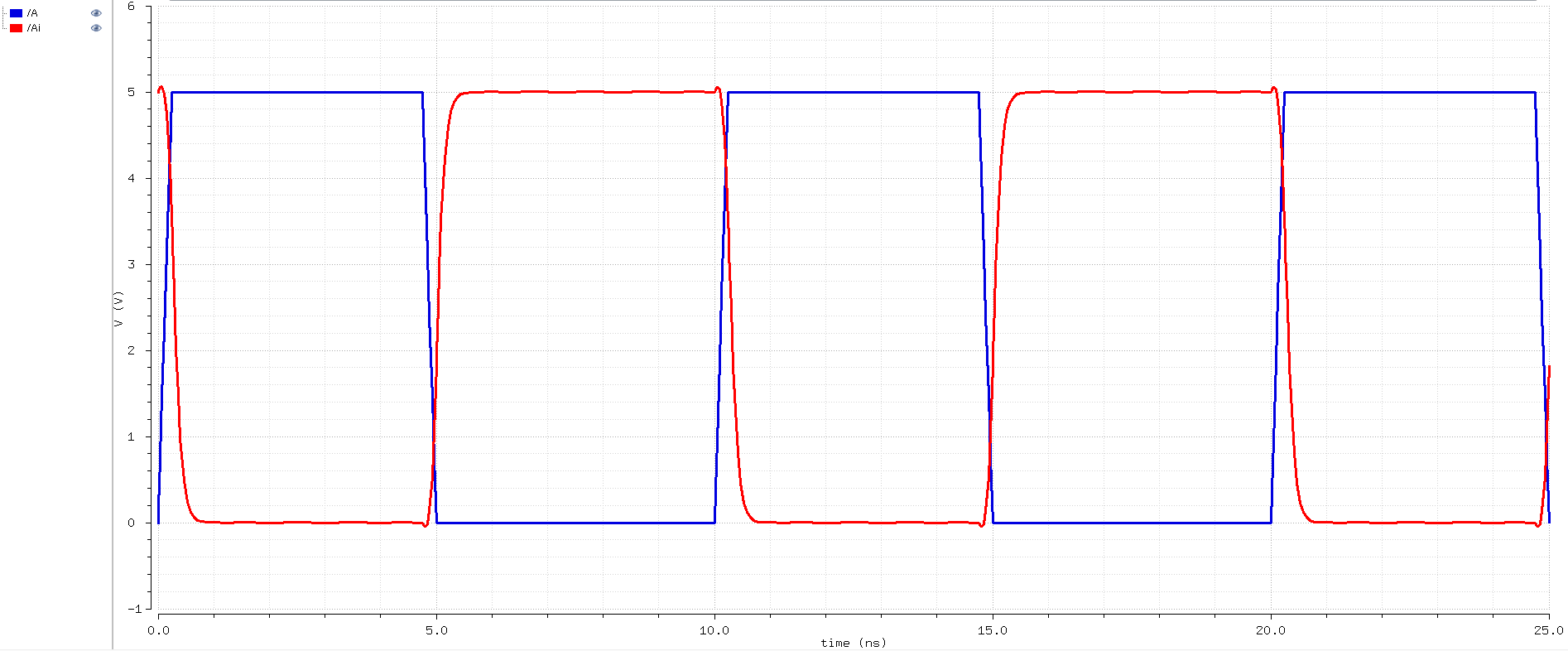

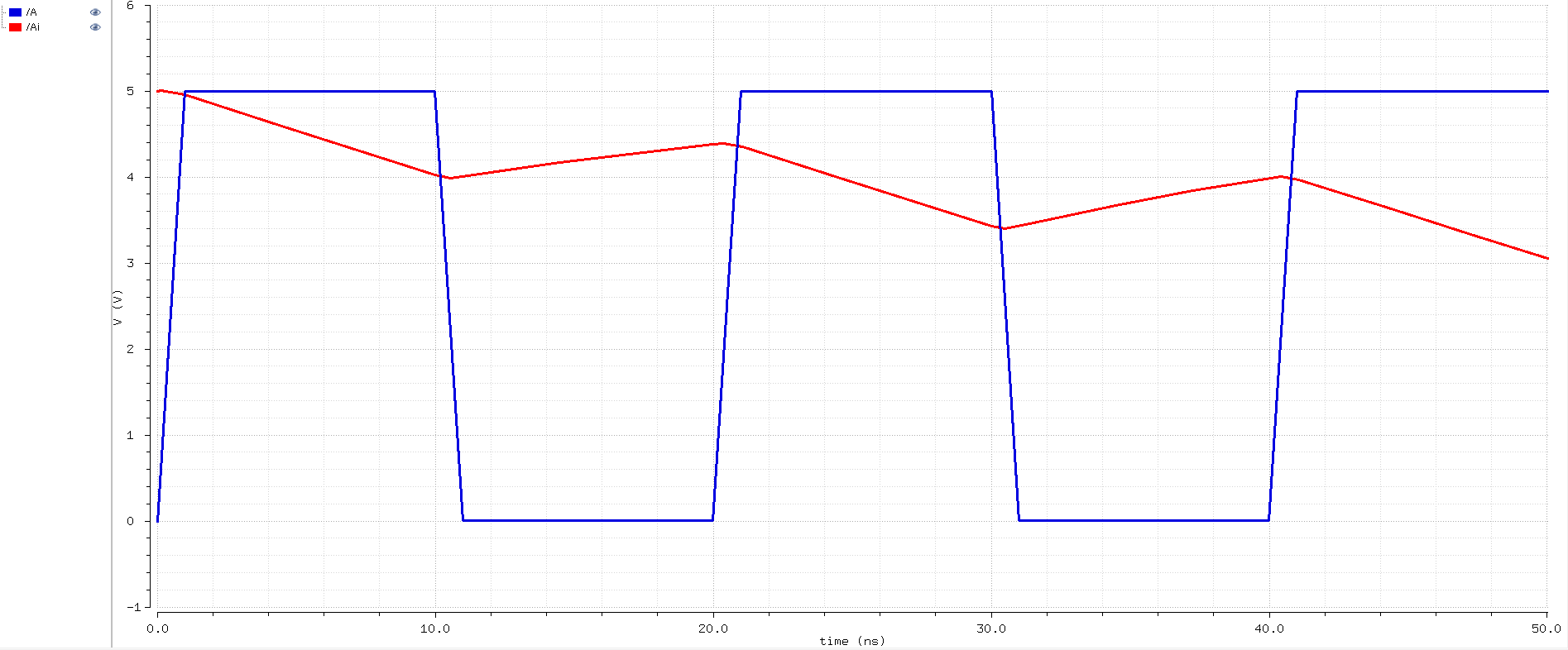

The

pattern from the first inverter still persisted; however, the inverter

was able to handle greater capacitive loads due to more current flowing

through the inverter. The time delay of the simulations were shorter

than the inverter with a 'multiplier' parameter of 1, but became

irrelevant as the capacitive load increased past a certain extent.

Although the simulations were faster, there wasn't much of a loss in

accuracy when using the UltraSim tool.

Final

design directory: lab5_jb.zip

Return

to Junho's Labs

Return

to EE421L Labs