Lab 04 - EE 421L

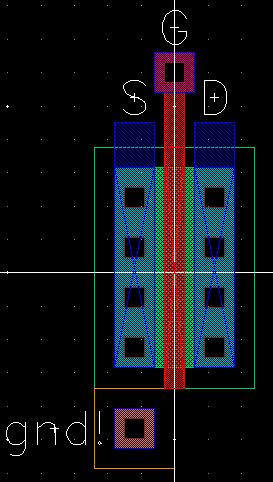

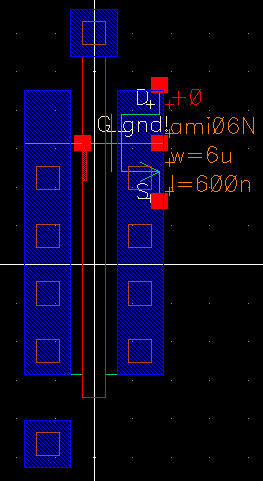

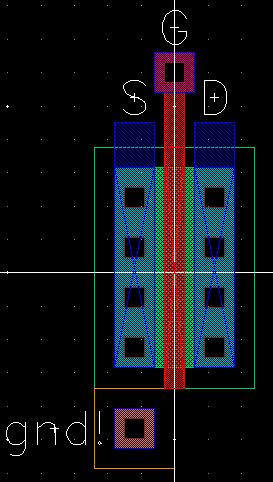

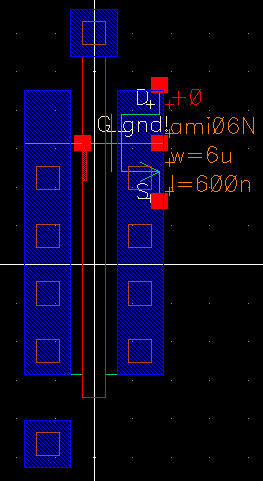

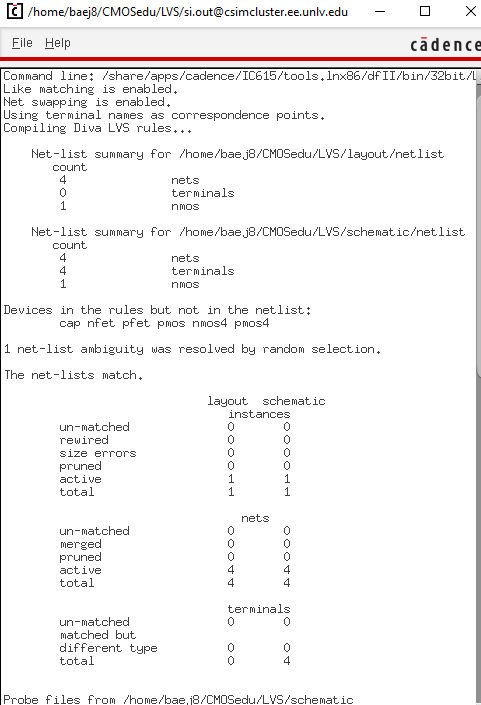

| Schematic | Symbol | Layout | Extracted |

|

|

|

|

| Schematic | Symbol | Layout | Extracted |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

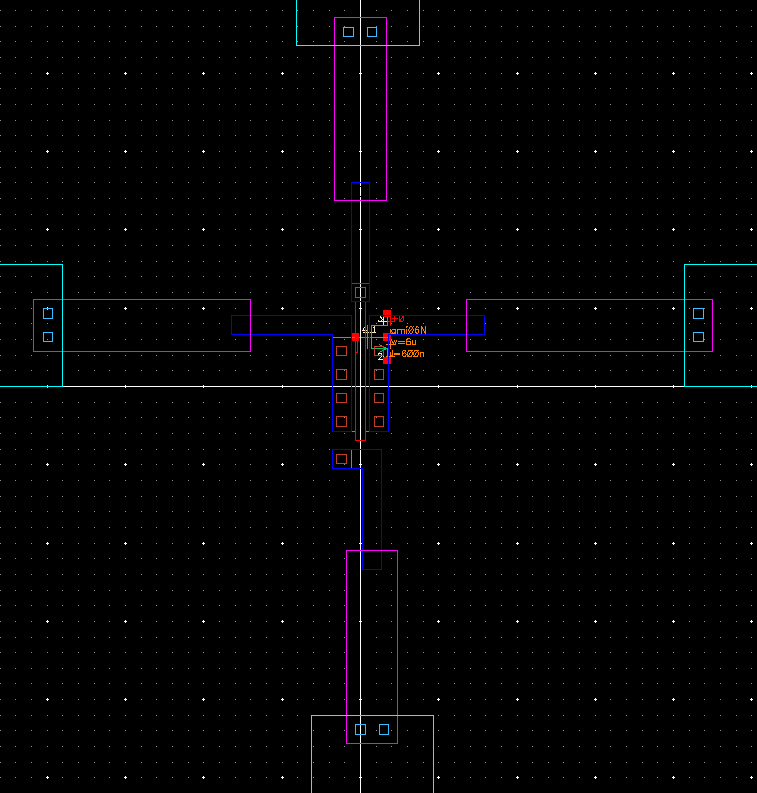

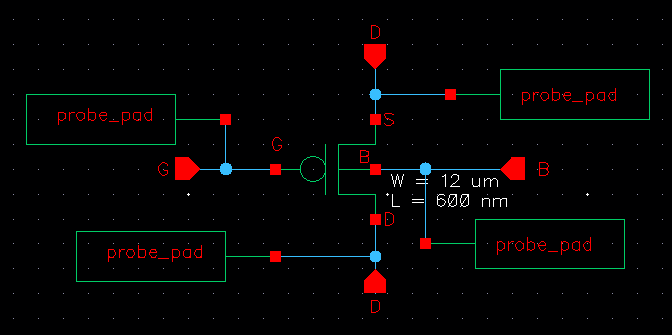

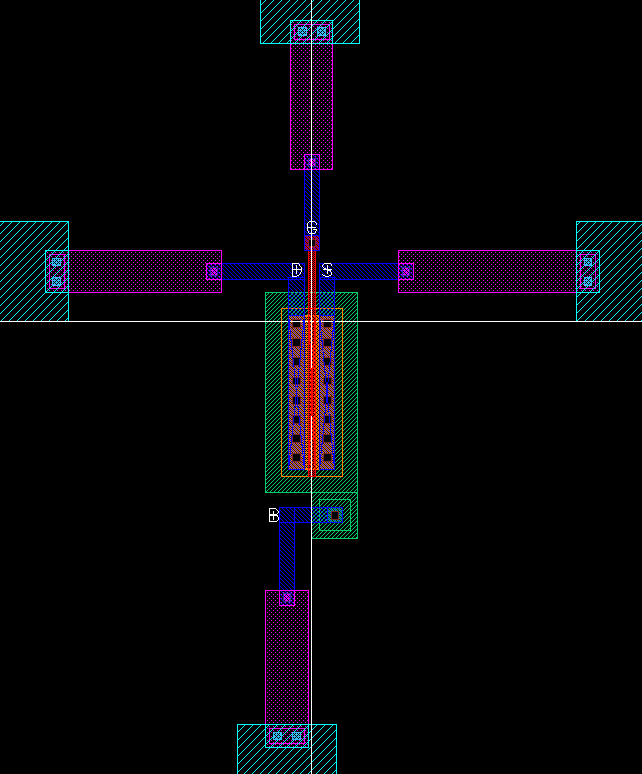

| Schematic | Layout focusing on NMOS | Full Layout view |

|

|

|

| Extracted view focusing on NMOS | Full Extracted view |

|

|

|

|

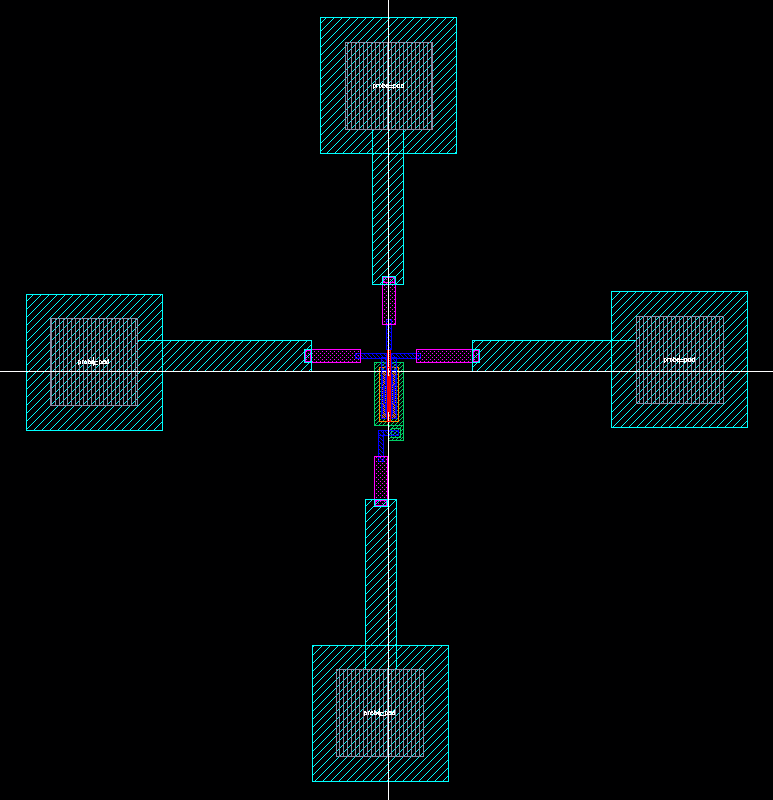

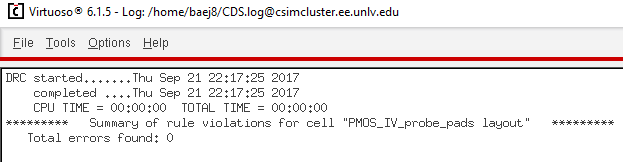

| Schematic | Layout focusing on PMOS | Full Layout view |

|

|

|

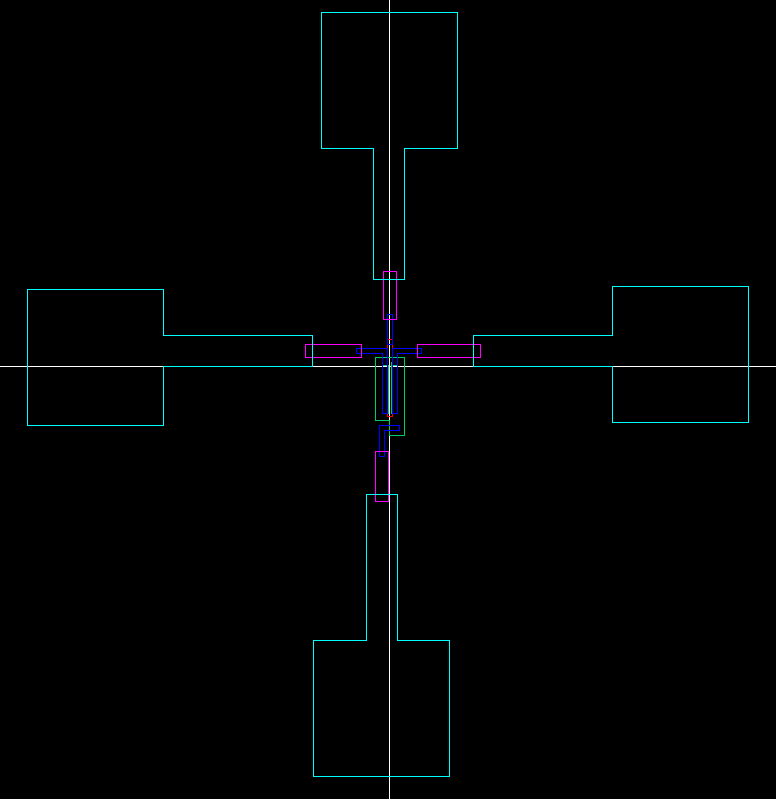

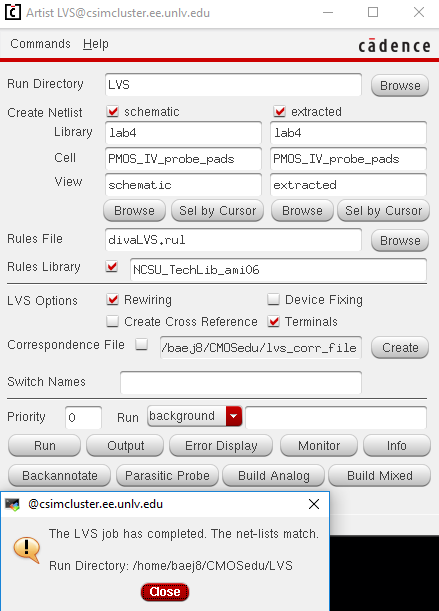

| Extracted view focusing on PMOS | Full Extracted view |

|

|

|

|