Project - EE 421: Digital Integrated Circuit

Design

Project:

Detector Circuit: This

circuit uses 6 DFF’s which receives values sequentially determined by the clock

cycle, specifically the rising edge of the clock cycle. When the designated sequence of input’s is received

the output goes high.

For this

project I will need an inverter, 6 DFF’s, and a 6 input NAND gate.

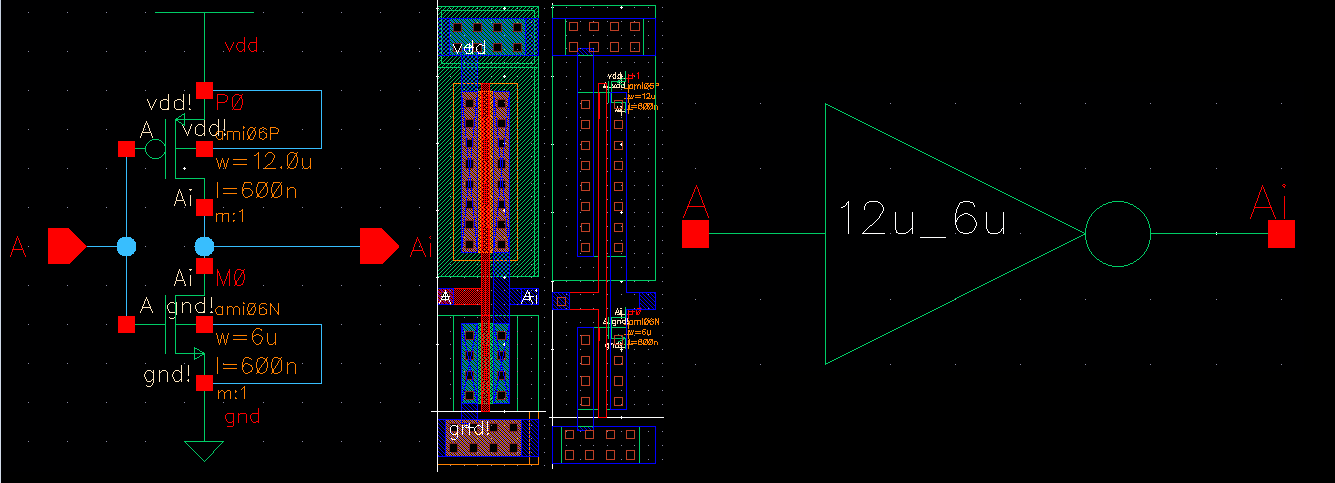

Below in figure

1 is the schematic, layout, symbol, and extracted views of the inverter.

Figure 1

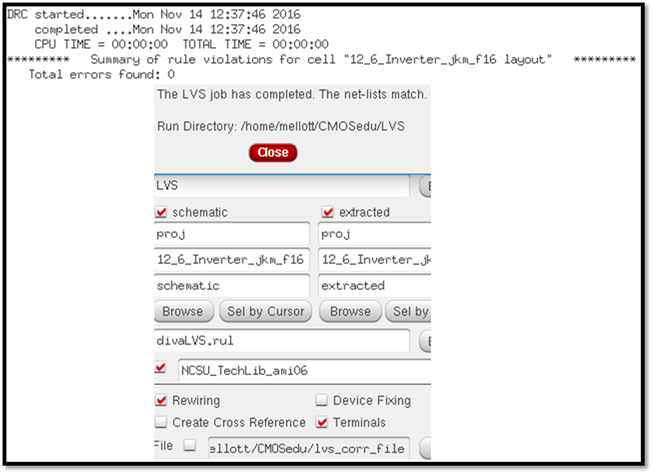

Below in

figure 2 is the successful LVS and DRC of the inverter.

Figure 2

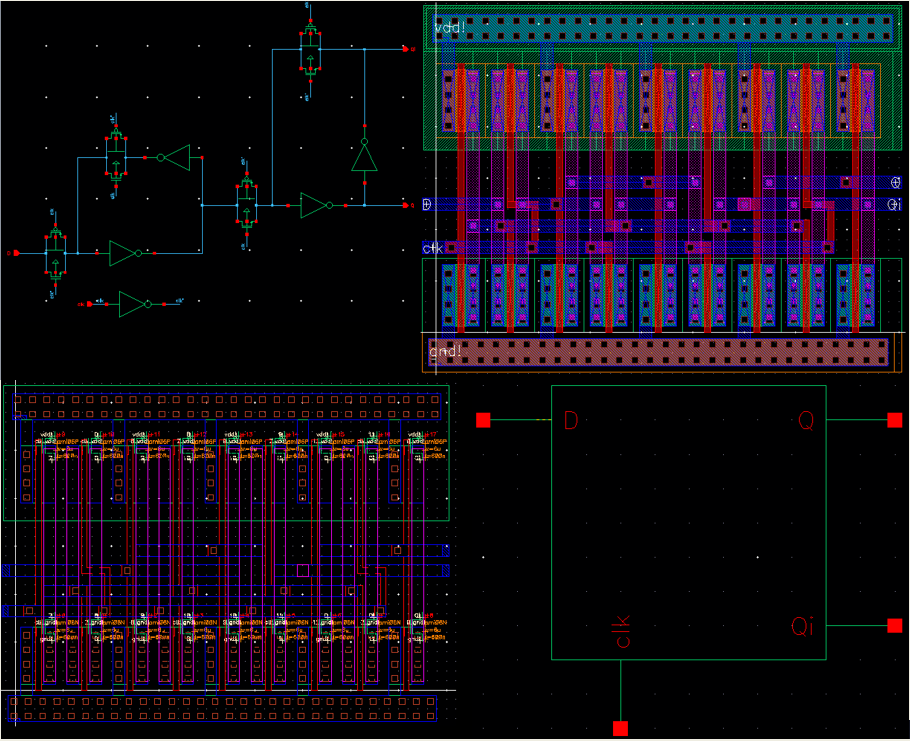

Below in

figure 3 is the schematic, layout, symbol, and extracted views of the DFF.

Figure 3

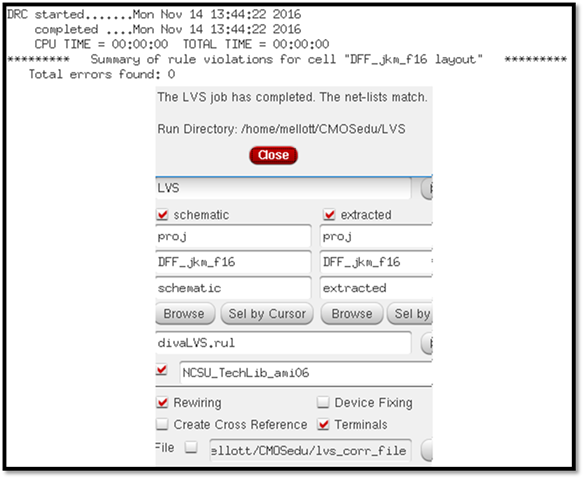

Below in

figure 4 is the successful LVS and DRC of the DFF.

Figure 4

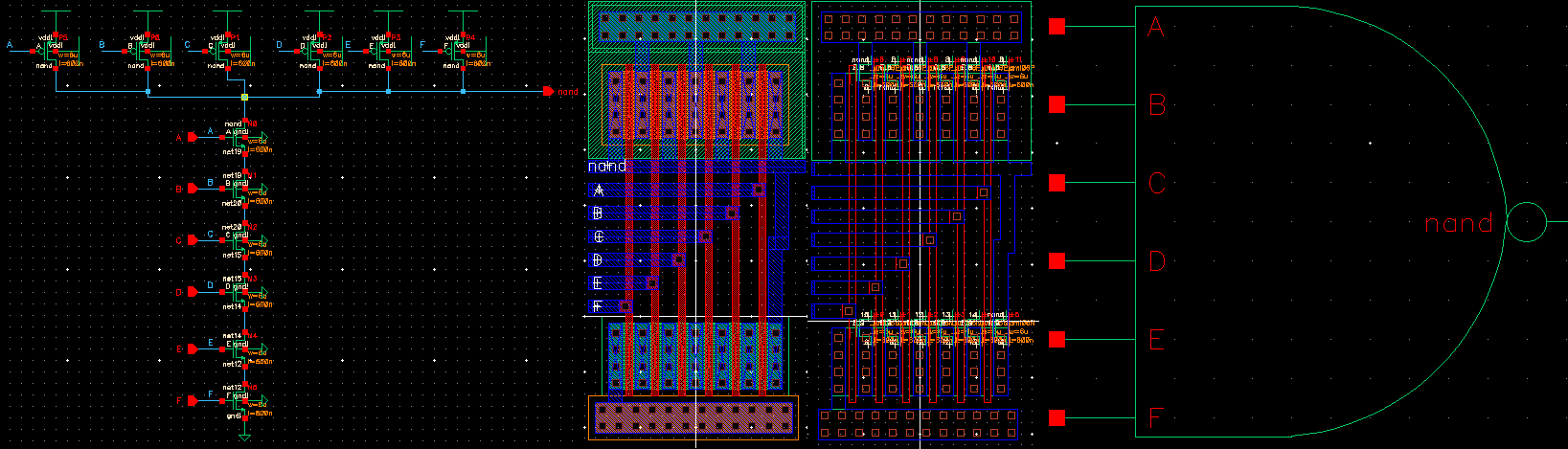

Below in

figure 5 is the schematic, layout, symbol, and extracted views of the 6 input

NAND gate.

Figure 5

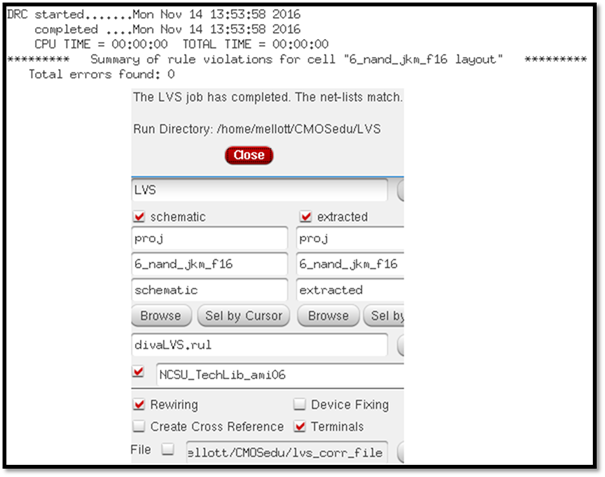

Below in

figure 6 is the successful LVS and DRC of the 6 input NAND gate.

Figure 6

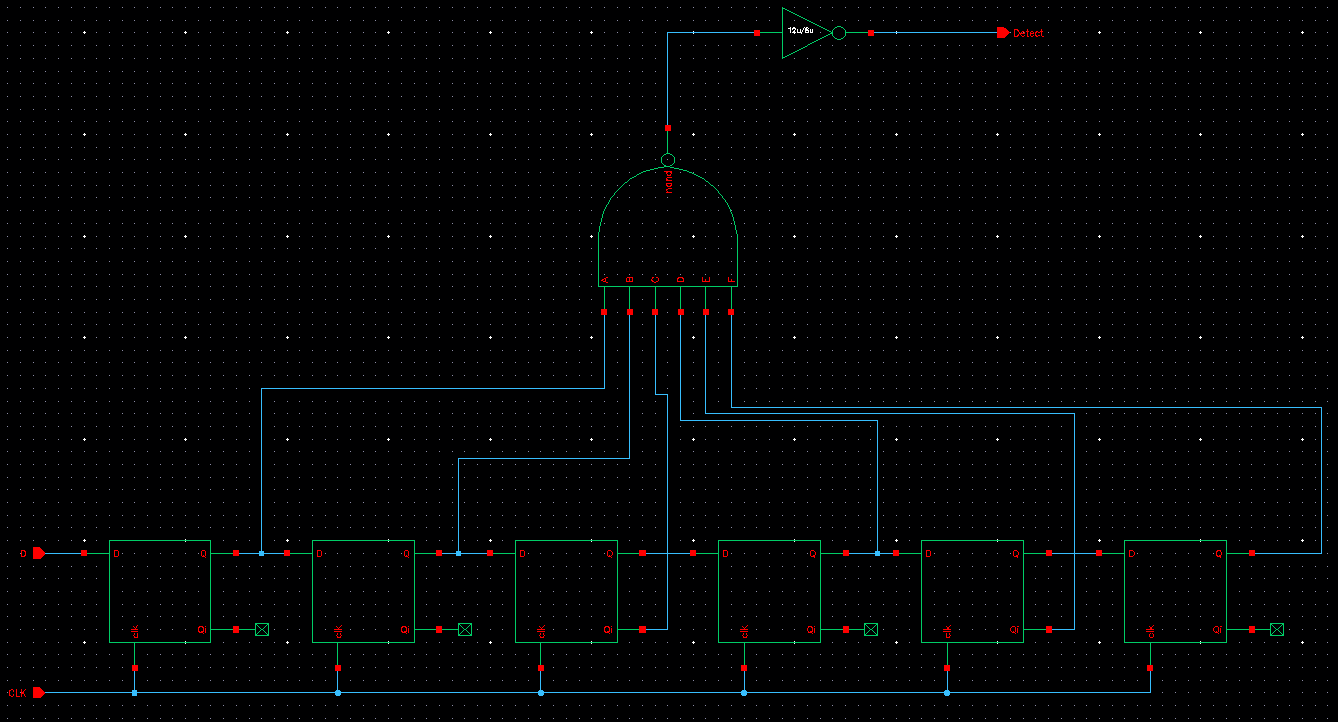

Below in

figure 7 is the schematic for the detector circuit. The sequential DFF’s take the value of the

previous DFF every clock cycle on the rising edge. Our detector circuit is set to detect a

specific signal “101011”.

Figure 7

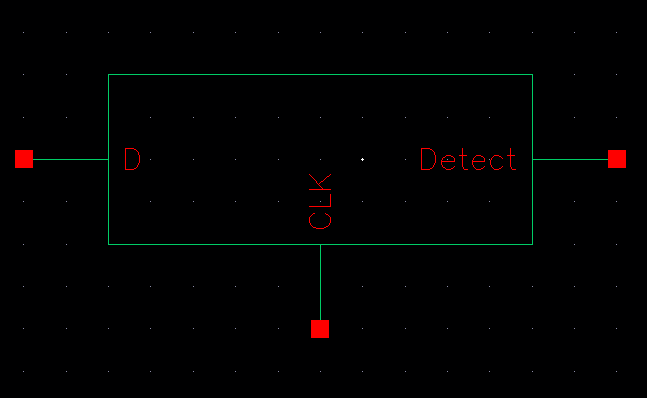

Below in figure

8 is the symbol for the detector circuit which will be used in simulations.

Figure 8

Below in

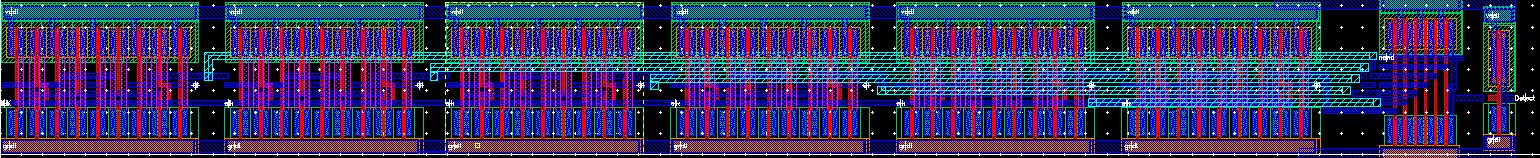

figure 9 is the layout of the detector circuit.

Figure 9

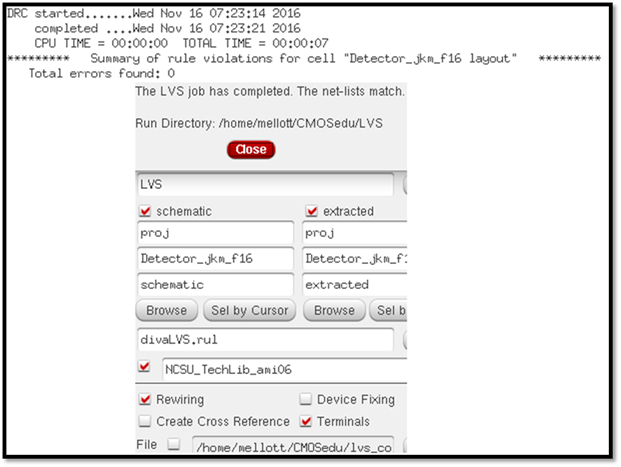

Below in

figure 10 is the successful LVS and DRC of the detector circuit

Figure 10

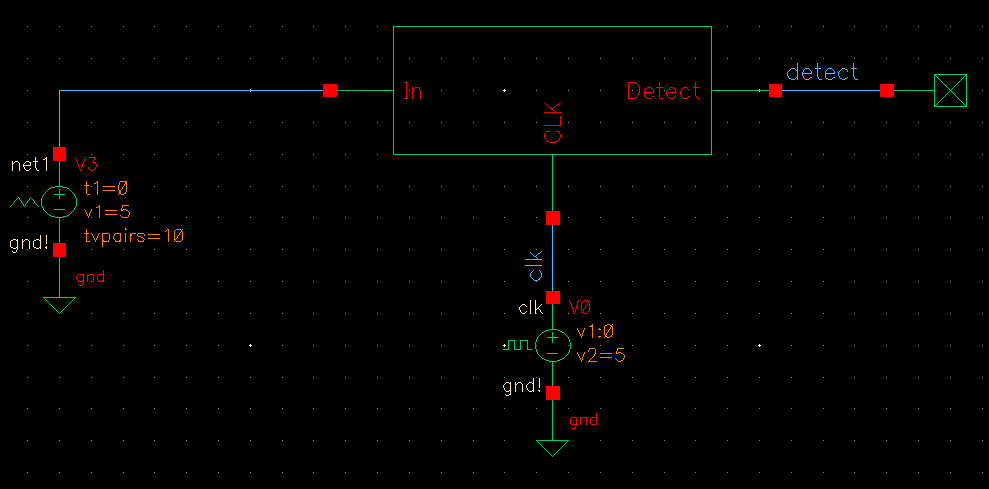

Below in

figure 11 is the schematic used to simulate the detector circuit. I used a PWL to generate the sequence

required with a 23ns period

Figure 11

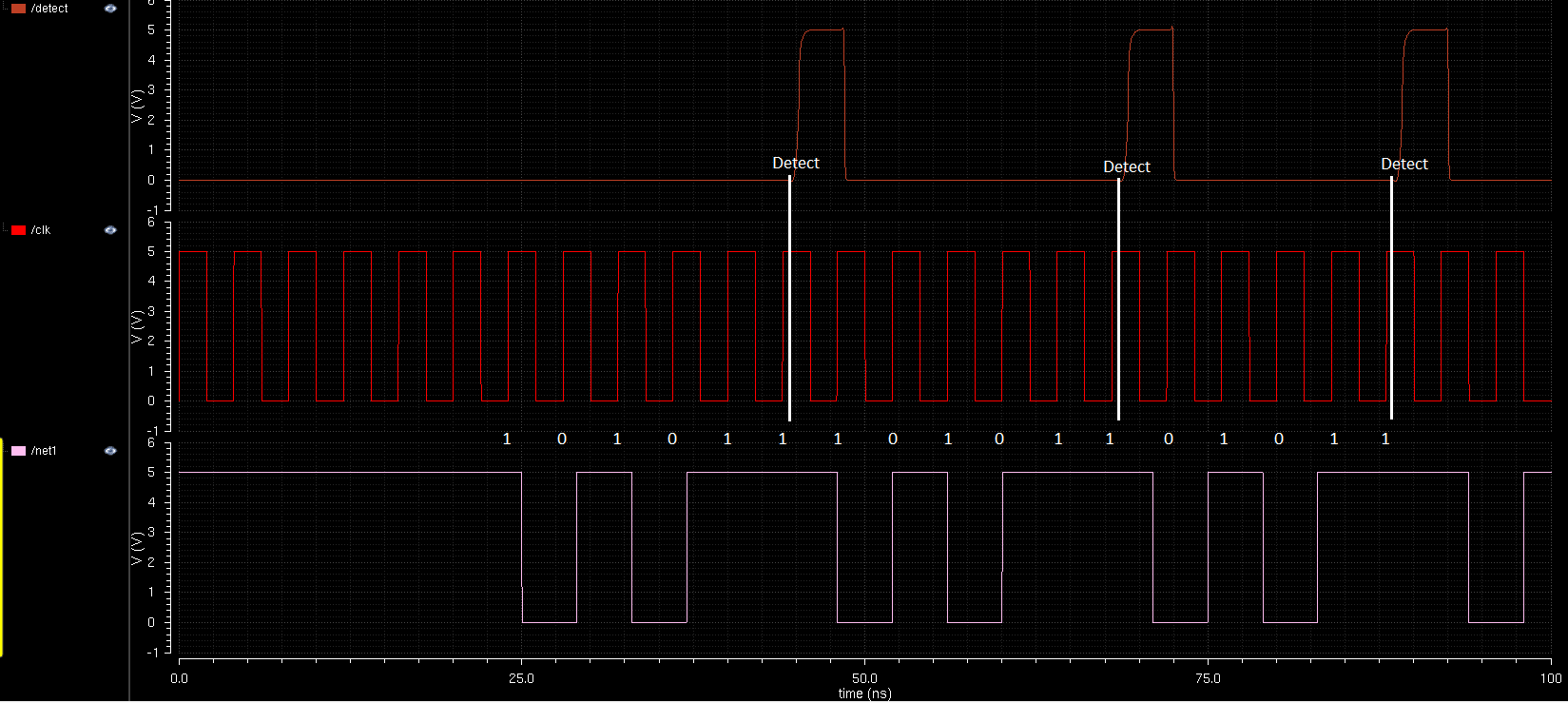

Below in figure

12 is the simulation results which shows the input is the desired detected

signal of 101011 and on the rising clock edge of the last digit Detect goes

high for one clock cycle. Once the

correct value is in each DFF the NAND gate receives all “1’s” and outputs a “0”

which is then inverted to a “1”.

Signaling that the circuit has detected the designated signal.

Figure 12

Return to Dr.

Baker’s Course Listings