Lab 2 - ECE 421L

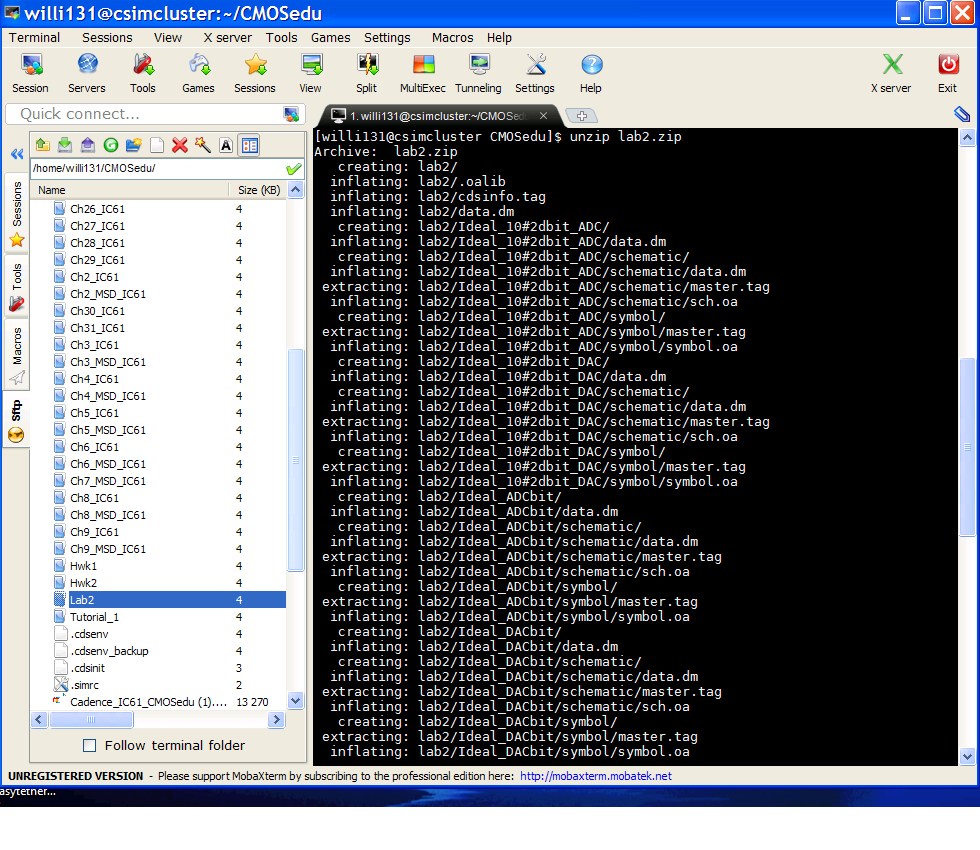

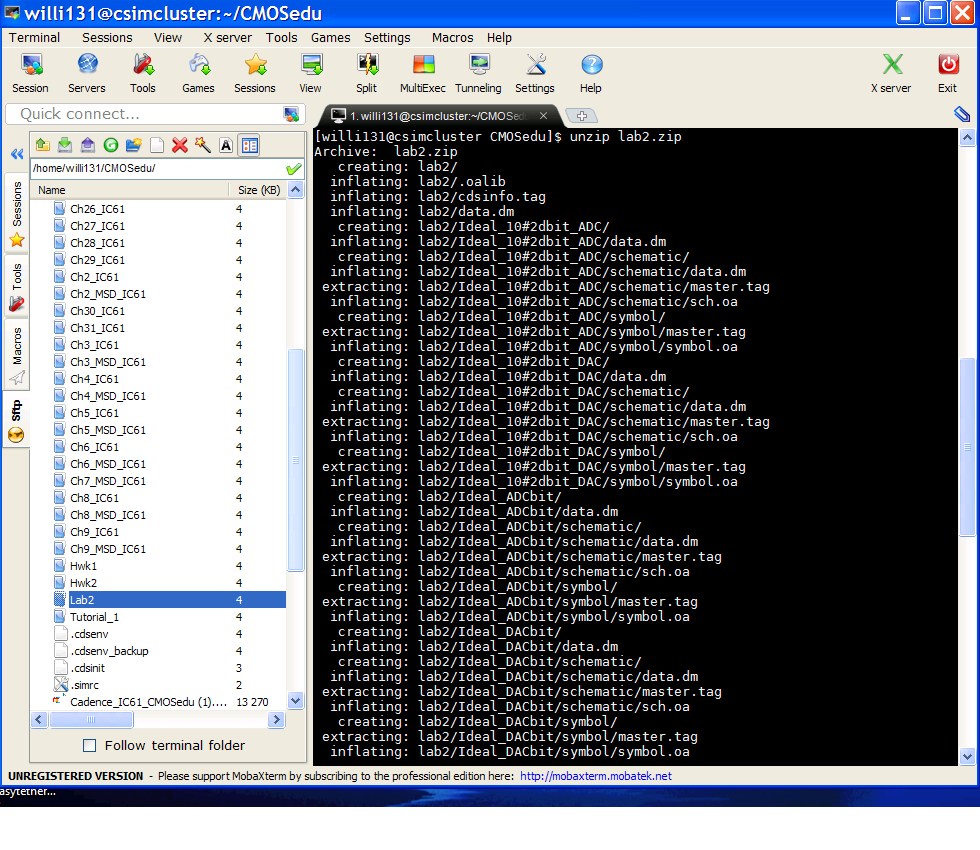

I. First the lab2.zip was downloaded to my computer, then uploaded into my CMOSedu directory through MobaXterm. Here I unzipped the file and adjusted my cdslib to accomodate the new directory Lab2. Below are images showing these steps...

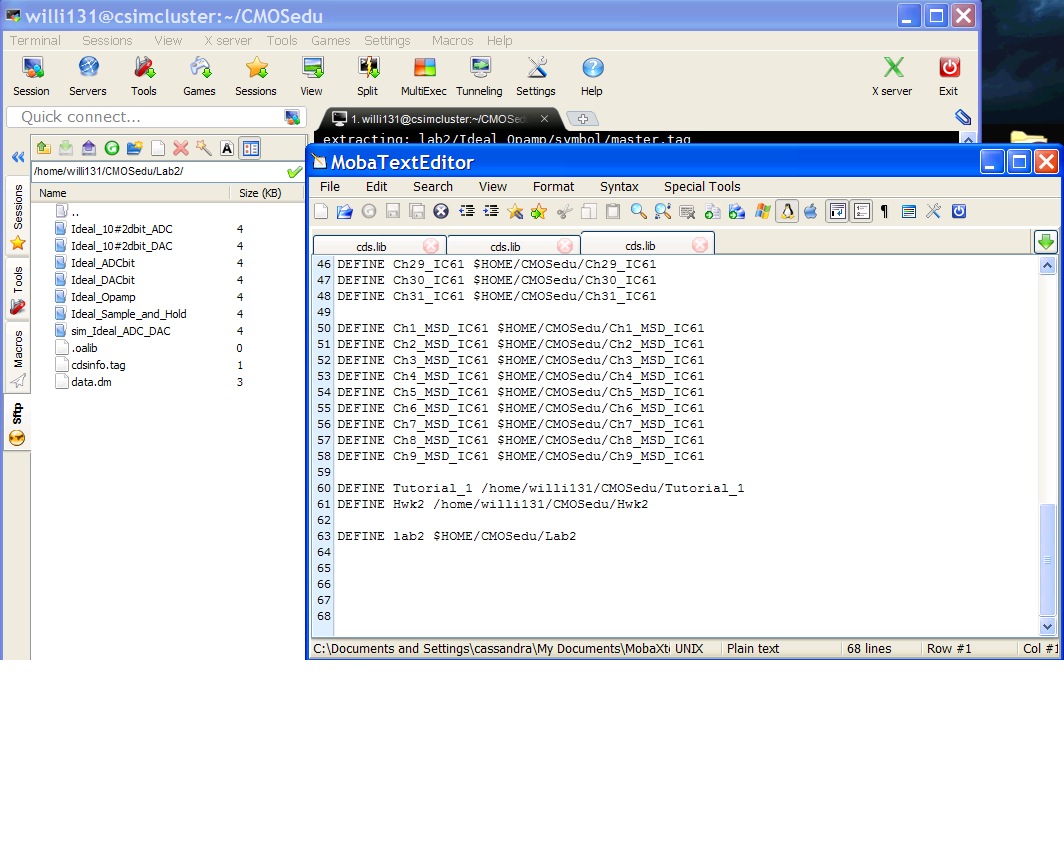

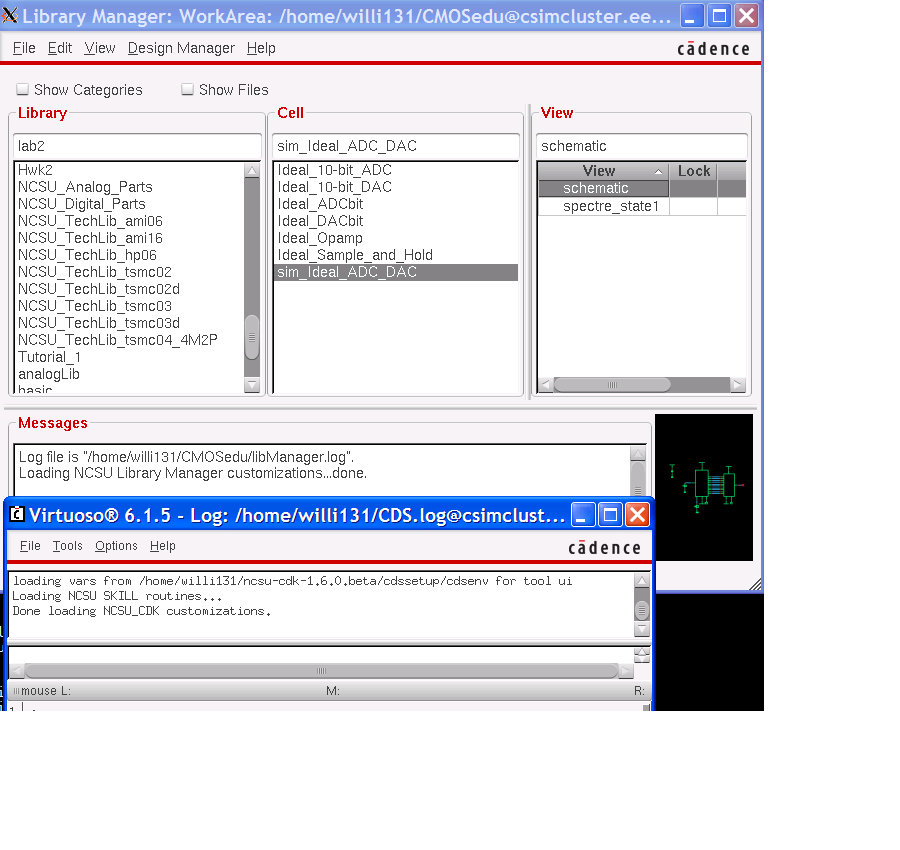

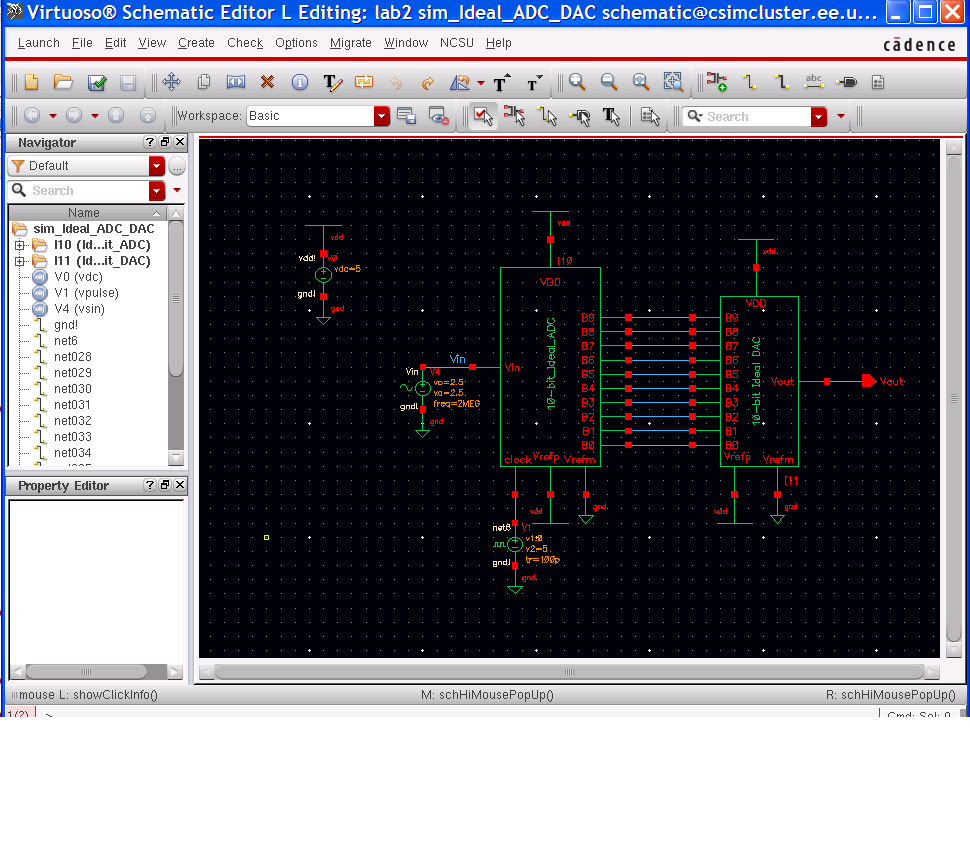

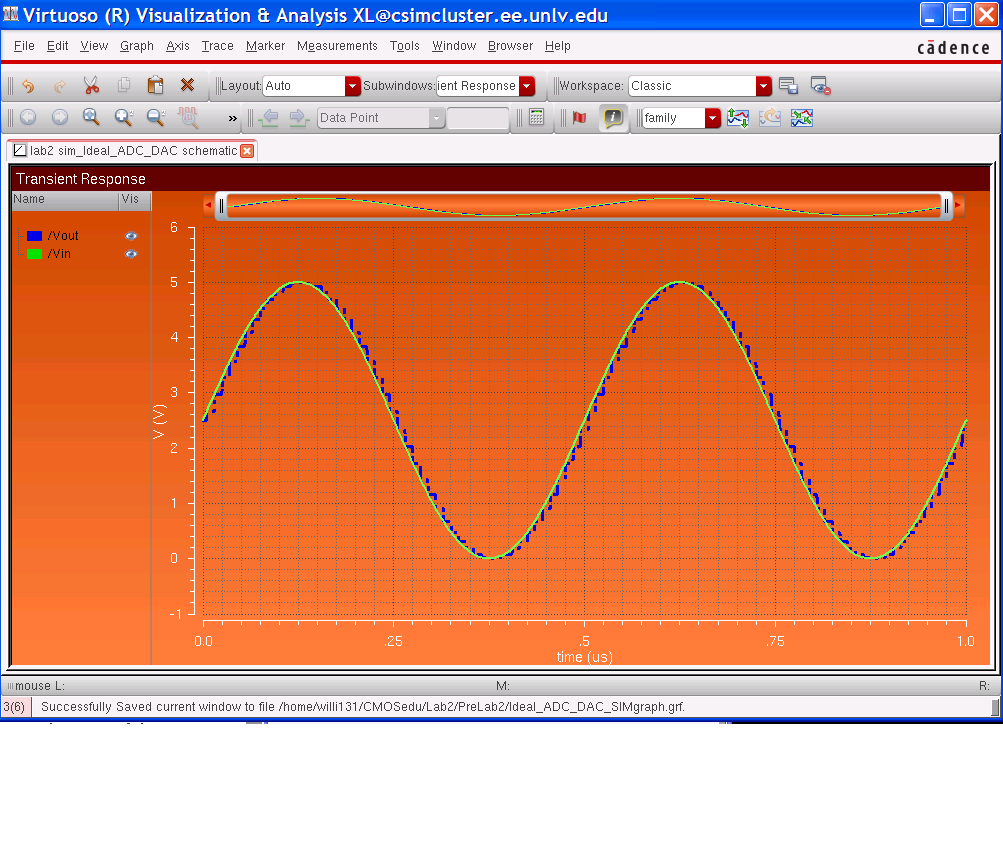

II. Next, Cadence is started and sim_ideal_ADC_DAC is found under the Lab2 library. The schematic is opened and simulated using the spectre_state1, which was created and preset previously...

III. ADC-DAC explained:

1. Analog to Digital Converter

a. Analog input which is any signal that contains continuous values.

b. Digital output which is a discrete signal (made up of 1's and 0's).

Below shows a simple relationship between our (10-bit) Analog input (Vin) and corresponding Digital output B(0:9). Also, the last column shows the decimal value which corresponds to the number of levels the output signal has.

| INPUT | OUTPUT | DECIMAL VALUE = LEVELS |

| 0 V | B0: 0000 0000 00 | 0 |

|

. . . |

. . . |

. . . |

| 5V | B9: 1111 1111 11 | *2^10 = 1024 |

c. Because in the lab we are using a 10-bit ADC we take 2 to the power of 10 in order to calculate the maximum levels of our output signal. Levels of our digital signal is called the resolution.

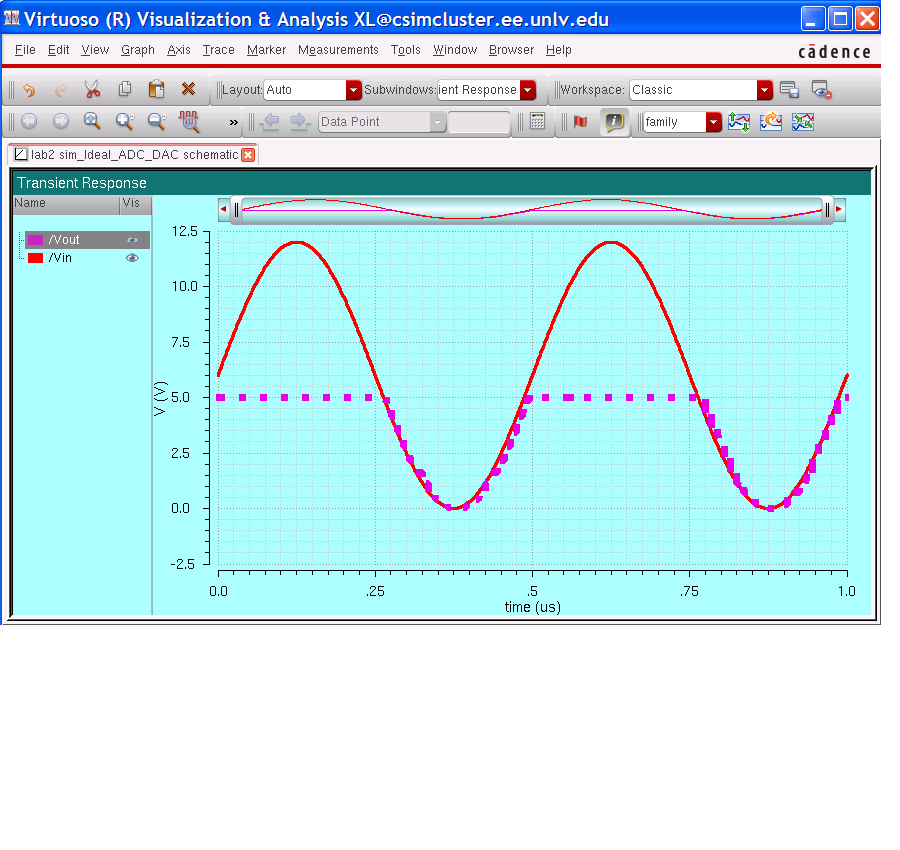

d. Below are a few examples of how varying the input can have an effect on the output. Because the control voltage VDD is 5V, changing our input voltage from 2.5V as originally shown to 6V as shown below, we see that our output signal is capped at 5V.

2. Digital to Analog Converter

a. Digital input

b. Analog output

As one would expect, a DAC works in the inverse way as the ADC taking a discrete digital signal and outputting a continuous analog signal.

c. various ways to accomplish this conversion

1. One method which we'll use in the lab is a resistive ladder. This will be shown and explained in much further detail in the post lab.

III. LSB- Least Significant Bit

1. LSB is the minimum possible input voltage change required to have an effect and change our digital code output (B(0:9)).

a. To calculate the LSB we use the following formula:

Vin/(Output levels-1) = LSB value

b. In our case of using the 10-bit ADC, with a voltage range of 0V to 5V, and 1024 levels (2^10) we have the following:

5000 mV/ (1024-1) = 4.8876 mV

- This shows that any value below 4.8876 mV for an input will not have any effect on the output.

d. The above schematic follows the original example of the resistor ladder. We have B0-B9 inputs and a single Vout output. Below is the DAC symbol created:

f. So at this point I wanted to make sure my symbol is just like the ideal DAC used in the original ADC-DAC schematic from the prelab. So I copied the original schematic and replaced the DAC in it with my own designed one. As you can see, the results are the same showingthat the DAC I created is comparable to the original. :)

II. Delay and Driving a Load

a. 10pF Cap Load:

First we were to ground all pins except B9 which was connected to a PULSE Voltage source going from 0V to 5V, and connect a 10pF Capacitor to the output of our DAC.. According to my calculations using the equation for delay of td = .7RC , the delay of our circuit should be about 70ns. Below is the circuit constructed and the simulation output.

Next, modifying the schematic, in addition to the 10pF capacitor a single 10K Resistor was added in parallel. This demands the circuit act similar to a voltage divider causing our output to just about drop to half of the first simulation with solely a capacitive load. (Still using the same delay equation, (.7*10p*5K) *** 5K is the result of our load 10K resistor and our DAC (10K n-well resistor) in parallel with each other**

Below you can see that the output voltage has dropped and the delay was shortened as well.

c. Driving a 10K Resistive Load:

Finally, I modified the circuit one more time by removing the capacitor. Now we have a very simple voltage divider. This should merely cut the voltage value in half.

And below is my resulted simulation showing my predictions were mostly correct. The output voltage is indeed much less that the input voltage. This result, not being exactly half of the input voltage as expected could very possibly be due to parameters/errors within my design.