Project, Part 2 - ECE 421L

Authored

by Stephanie Silic

silics@unlv.nevada.edu

November 23rd, 2015

Project, Part 2 Description:

This report will detail the layout of the up/down counter

Report:

8-bit resettble (with clear) up/down counter

The layout is as follows:

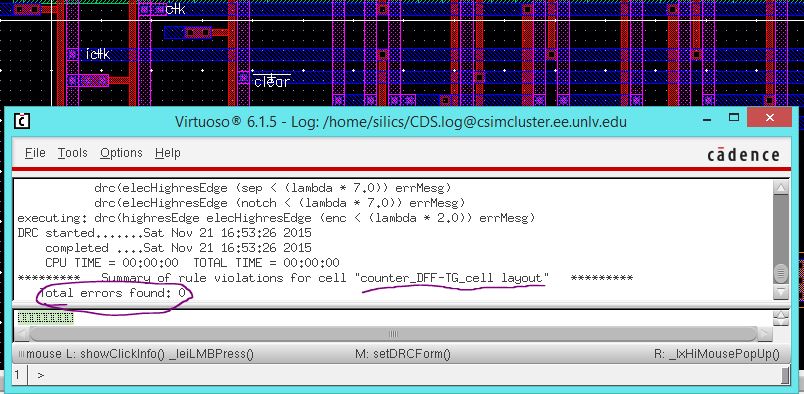

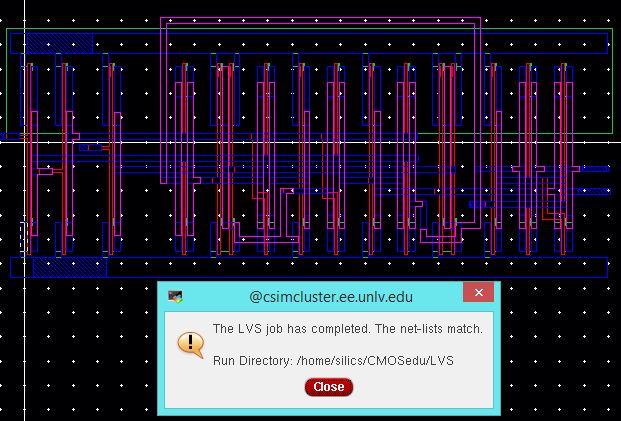

The following images show that this layout DRCs and LVSs properly:

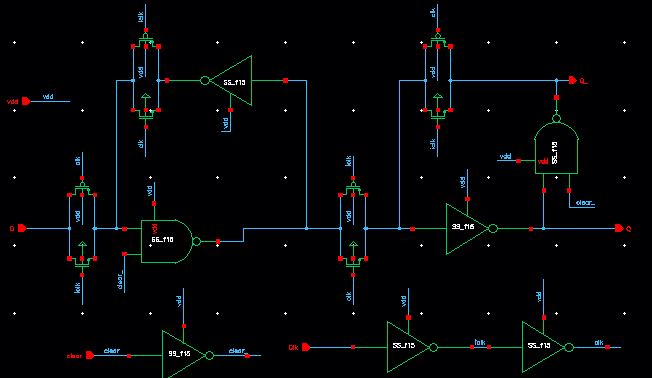

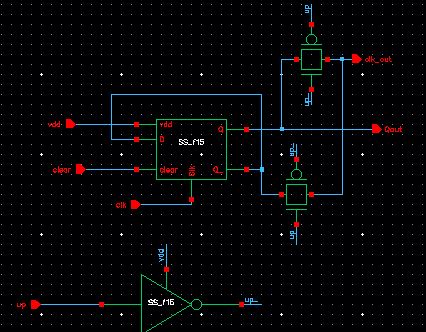

DFF register cells with the TGs for the up/down counting are created as follows:

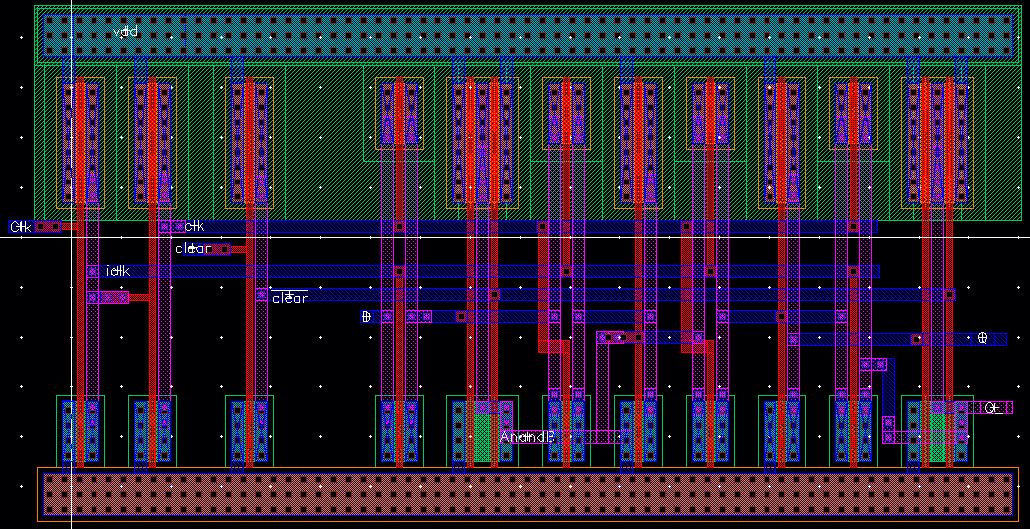

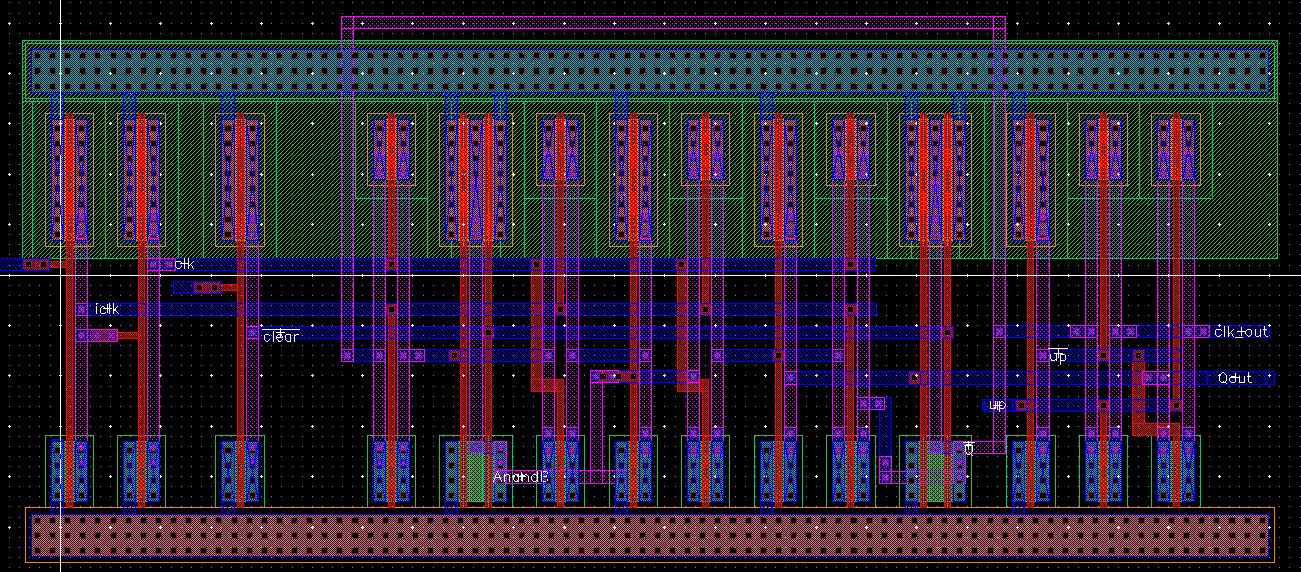

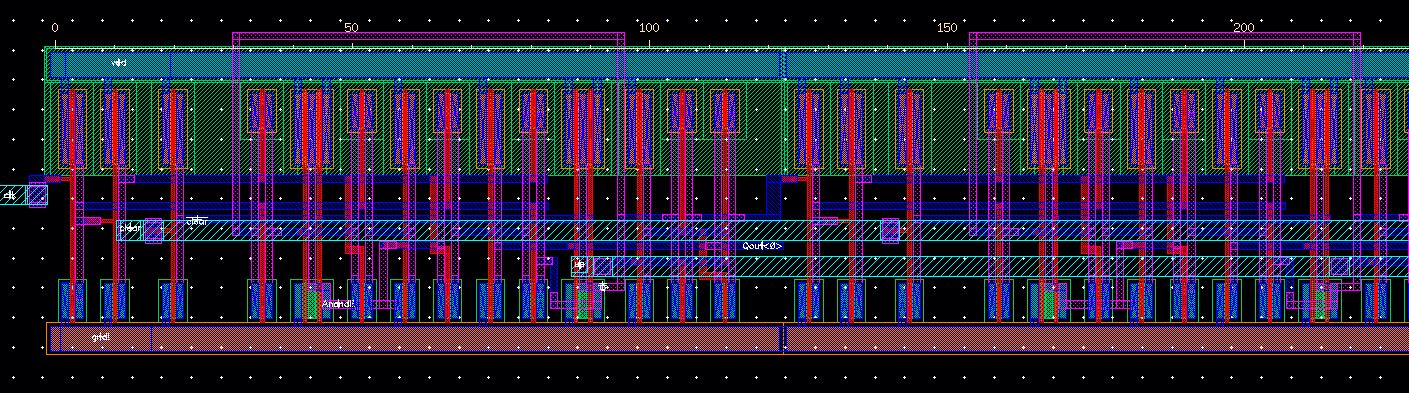

And the layout for these cells looks like this:

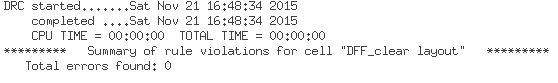

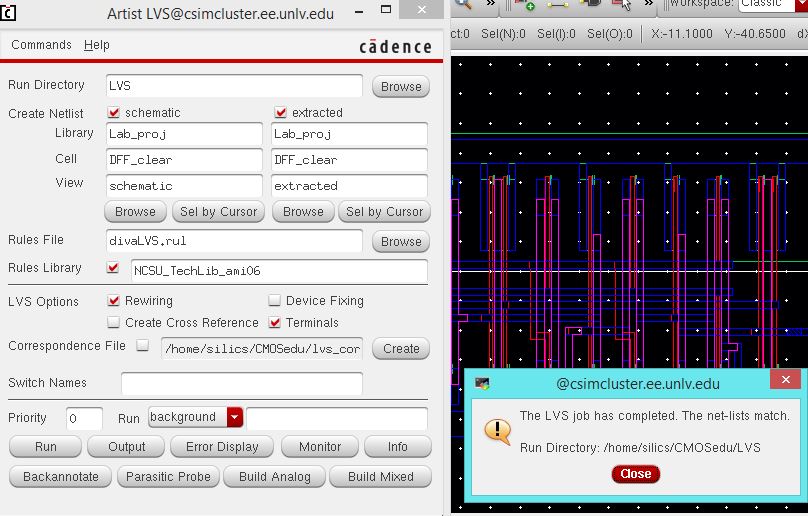

DRC and LVS checks:

Finaly, we can construct the entire up-down counter using 7 of the cells with TGs and the 8th cell without them.

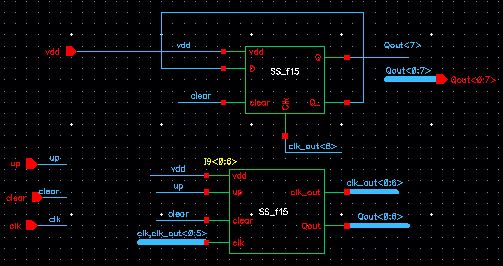

Schematic for complete up-down counter with clear:

Two cells are shown below:

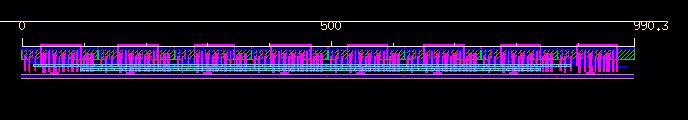

The complete counter measures about 980 um by 50 um:

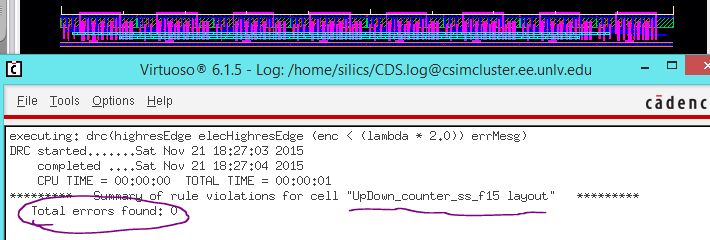

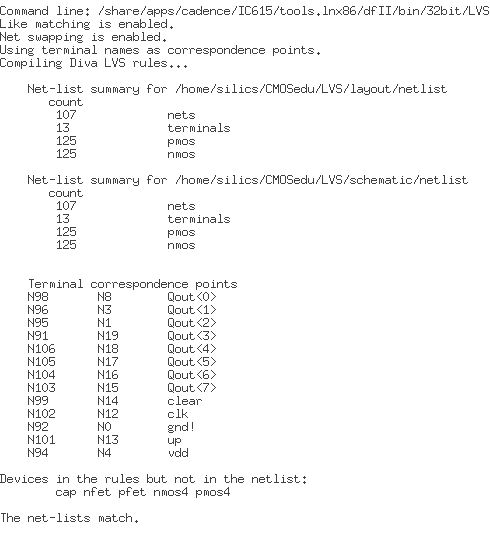

The layout DRCs and LVSs properly:

DRC:

LVS:

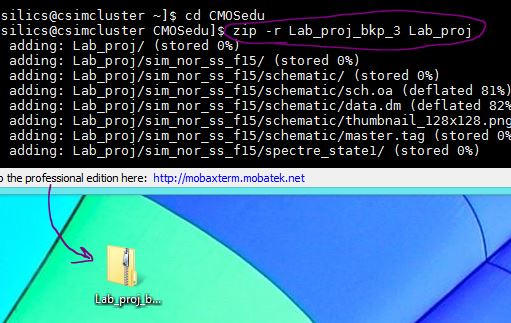

All work is backed up, the project is saved in a zipped folder on my pc and in my rebelmail inbox:

This concludes the report for the second part of the project.

The layout and the entire project can be found in my design directory here

Return to EE421L Fall 2015 page

Return to my labs