Lab 6 - EE 421L

Authored

by Shada Sharif,

sharifs@unlv.nevada.edu

19 October 2015

Pre-lab work:

- Back-up all of your work from the lab and the course.

- Go through Tutorial 4 seen here.

- Read through the lab in its entirety before starting to work on it.

Lab Description:

- This lab will be about the design, layout, and simulations of a CMOS logic gates.

Lab Report should include:

- Schematic, and layout of the CMOS inverter.

- Schematic, and layout of the CMOS NAND gate.

- Schematic, and the layout of the CMOS XOR gate.

- Schematic, and the layout of the CMOS Full Adder.

- All layouts with LVS match and DRC no errors.

- Simulation of all the possible logic inputs of the gates.

Experiment #1

- The

first part of this lab is to do the prelab, which is going through

tutorial 4. The first thing we did was copying all the files from lab3

since we will be using the inverter schematic, symbol, and layout.

- All the PMOS and NMOS used in this lab were 6u/600n.

- Below is the schematic of the inverter as well as the symbol that will be used in the simulations.

- There is the layout, the extracted layout, DRC with no errors, and the LVS extracted matched with the schematic.

- All the bodies of the PMOS were connected to vdd! and all the bodies of the NMOS were connected to gnd!.

- All the cell names for the gates were named following the instruction as shown below.

- After

being done with the inverter, we start working on the NAND gate. The

nand gate uses the inverter gate along with some additions.

- Again

the following pictures show the schematic, symbol for simulations,

layout, extracted layout, DRC no errors, and the LVS match.

- We again used the vdd!, and the gnd! for the bodies of the PMOS and the NMOS. All the inputs and output pins were metal 1.

- In

building the NAND gate we used the flattening property in order to

modify the NMOS and remove the contact cuts just as explained in the

tutorial.

- After

being done with layout and schematic of the NAND gate, we check its

operation by having one input as vdd, which is a 1, and input of 1's

and 0's.

- We see that the output of

the schematic shows that the circuit is working fine, for example 1 and

1 outputs 0, and 1 and 0 outputs 1.

- We set the vdd! to 5V in the Stimuli since it is a global net.

Experiment #2

- The

second part of this lab is about making an XOR gate, to make the XOR

gate the inverter was once again used since some of the inputs for the

XOR are inverted.

- Below

we have the schematic, on the left side we see two inverter schematic

used where one is to invert input A and the other is to invert input B.

The output of the inverters used the no connection since we did not

want to leave the node floating or put a pin that would be added to the

symbol and would create problems later.

- We

have the schematic, the symbol of the XOR, as well as the layout,

extracted layout, final DRC with not errors, and the matched LVS.

- In

the layout we used the standard cell frame, which has the vdd! and the

gnd! snapped end to end. The top part has an n-well, and the bottom

part is in a p-well but since the p-substrate is a default layer it was

not added in the layout.

- The PMOS devices sit in the n-well and

connecting its body to vdd!, and the NMOS devices lay in the p-sub and

the bodies are connected to gnd!.

- Since there is many

connection between the devices in the layout, metal 2 was used to avoid

shorting terminals together. Using metal 2 allows us to cross over

metal 1 without worrying that we could short a terminal. It is like

jumping to another layer, and when we reached the input/output we

jumped back to metal 1.

- Now

we have all the gates needed to build the Full Adder, but before doing

so we are testing the operation of all possible inputs for the gates.

| A | B | NOT A | NAND | XOR |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 |

- We

see that the gates are operating correctly looking at the output

waveforms for each gate. In the XOR gate output we see a glitch that

happened, this could be due to the input timing (the rise and fall time

of the inputs too) since each gate has a different delay and also there

is a short and long paths to the circuit where one input reaches the

gate faster than another input and this could cause the output to

change before reaching its final value with the other input reaching

after a certain time. So all this can cause a glitch in the output as

seen above.

Experiment #3

- The

last part of the lab was making a full adder. For the FA schematic we

used the NAND and XOR gate symbols that we made earlier and combined

them as seen in the schematic below.

- The symbol for the FA was created, and it has 3 inputs along with 2 outputs.

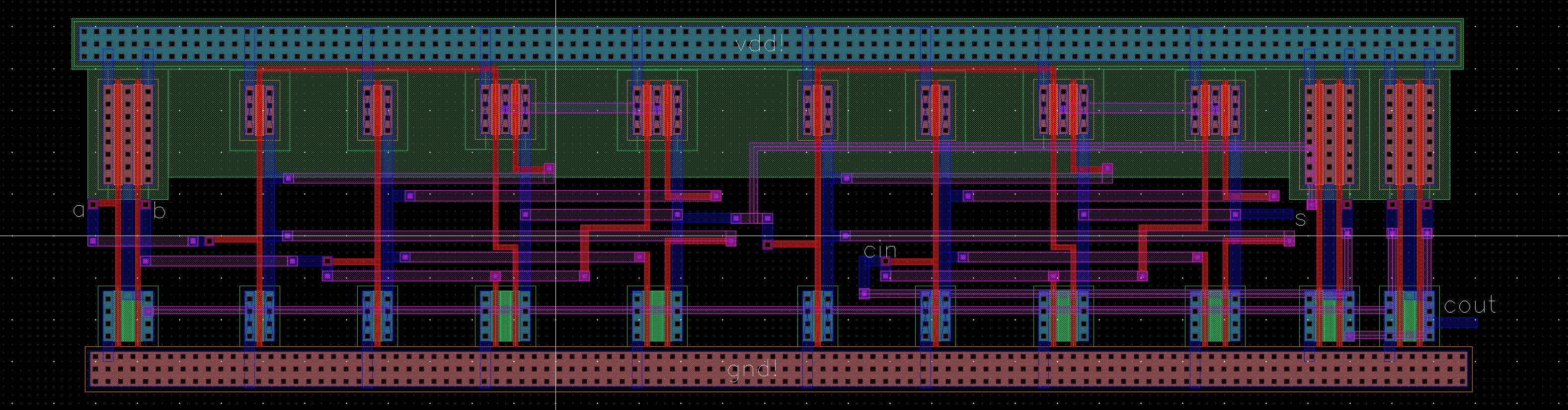

- For the FA layout, we used two XOR gates and three NAND gates.

We instantiated the XOR and the NAND layouts that we made earlier,

connected them as close end to end, and after that we flattened the

layout in order to start editing and wiring the inputs and outputs for

the FA.

- We

again used a standard cell frame as explained previously, and we made

sure all the bodies of the PMOS and NMOS were connected to vdd! and

gnd! accordingly.

- In

making the layout of the FA, once again metal 2 was used due to the

close use of metal 1, and all the inputs and outputs were using metal 1.

- The

FA layout is the only layout that had many problems and it was hard for

the LVS to match the schematic. The first attempt in making the layout

I had from left to right two XOR gates and the three NAND were after on

the right. This placing in the layout caused many spacing issues and

many netlists did not match. So I had to re-layout the FA by placing

one NAND at the beginning following two XOR and the remaining two NAND

at the end. After fixing the spacing DRC errors, and connecting

everything as in the schematic, I had forgotten a via 1 which caused

two terminals to merge and LVS to fail but after figuring out this

problem the LVS matched, and no further problems were encountered.

- Below we see the layout, the extracted layout, final DRC with no errors, and the matched LVS netlist.

- Click on the FA layout image to enlarge the picture.

- Now we do the same thing for the FA, and test the circuit with all the possible inputs.

- We tested the schematic, as well as the extracted layout to make sure it is operating correctly.

| a | b | cin | s | cout |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

- Below the netlist display is shown to show that the extracted layout is what Spectre used for simulation.

- We

again see glitches in the output of the circuits, and it is again for

the same reason as explained before due to the timing of the gates and

each gate having its own propagation delay.

- When making the

simulations the rise and fall time of the input sources were 1ns and

there were many glitches in the output, but changing the rise and fall

time to 1 ps caused only the XOR gate to have a glitch in its output.

Back Up

- All the lab work was zipped and backed up to Dropbox as shown below.

Lab 6 zipfile

Return to EE 421L Labs