Lab 4 - ECE 421L

3. Create a schematic cell called NMOS_IV_3. The "3" indicates the use of a 3-terminal transistor.

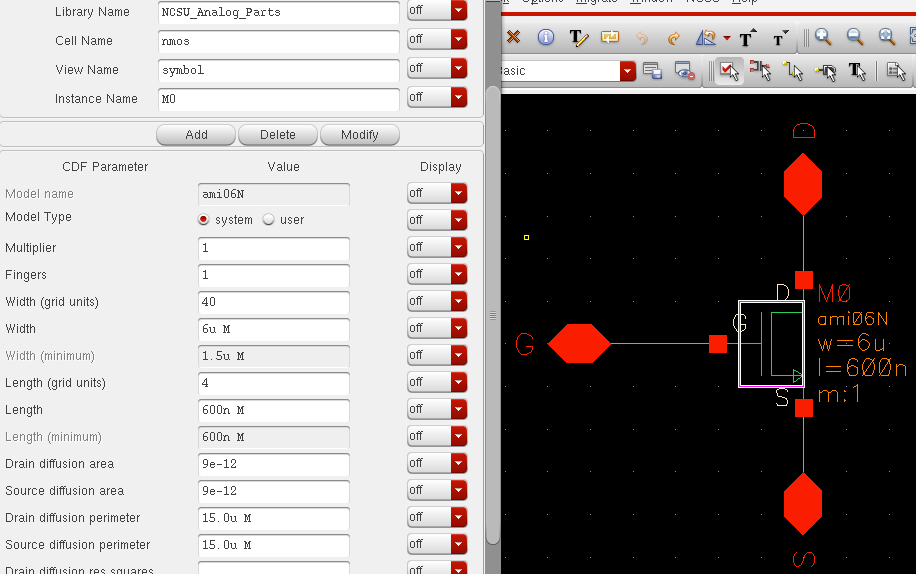

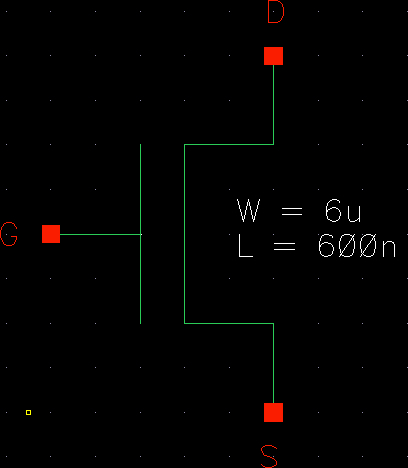

4. Instantiate an nmos from the NCSU_Analog_Parts > N_Transistors library, with a width of Width = 6u and Length = 600n.

5. Add Pins with the direction set to InputOutput and wires as seen below. Check and Save the schematic when finished.

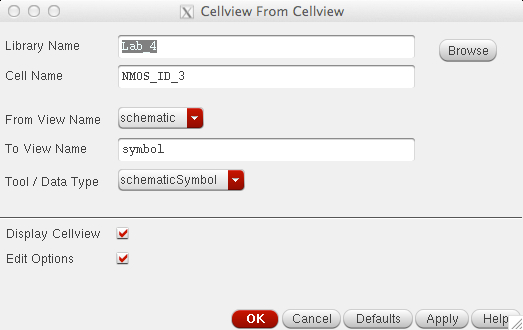

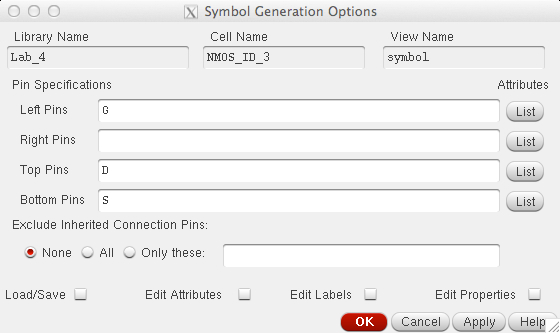

6. From the schematic, create a symbol view (Create > Cellview > From Cellview). Follow through the windows making the necessary changes to ensure the symbol will be created like the one below.

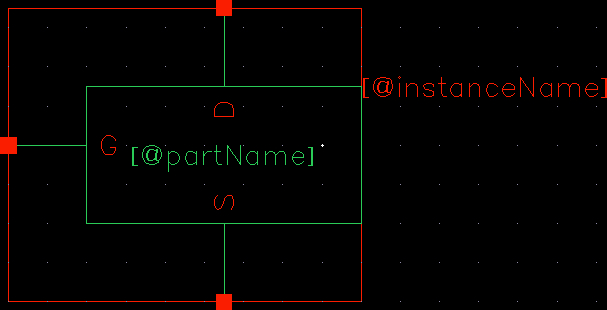

7. Delete everything in the symbol except for the pins. Select all pins and edit their properties with the edit hotkey (q). Select "all selected" and display "value" as seen below.

8. Draw a MOSFET symbol and move the pins (rotate if needed) to get a drawing similar to the one displayed. Use commands Create > Shape > Line to draw the lines and Create > Note > Text to include the width and length text.

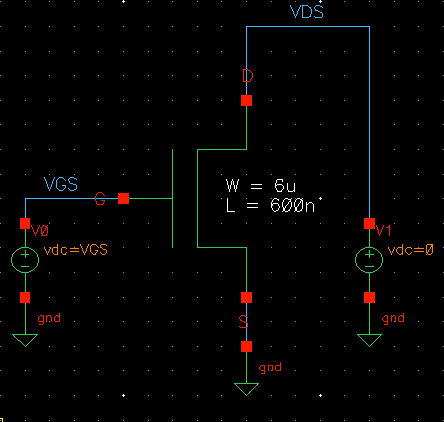

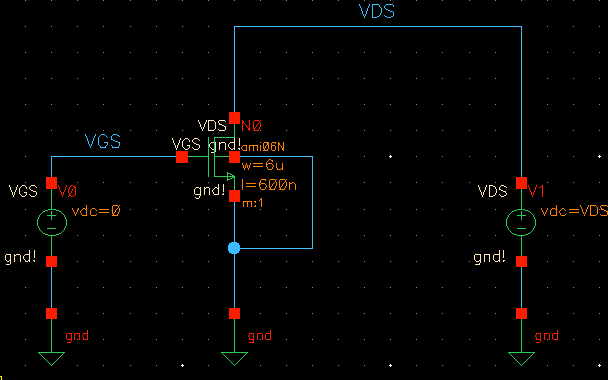

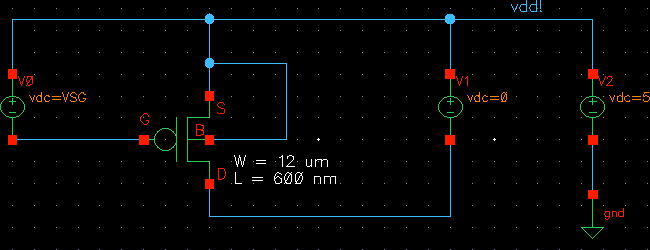

9. Create a schematic cell called sim_NMOS_IV_3. Instantiate the NMOS_IV_3 symbol that was just created and voltage sources. Build the schematic below paying attention to the values of the voltage sources. Check and Save.

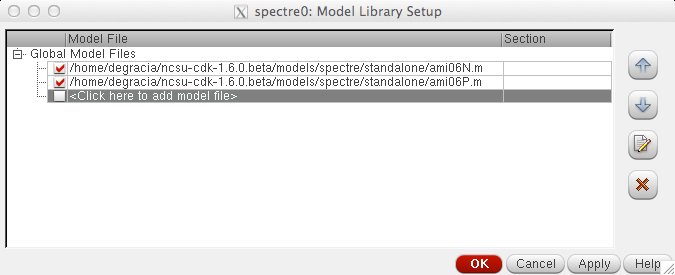

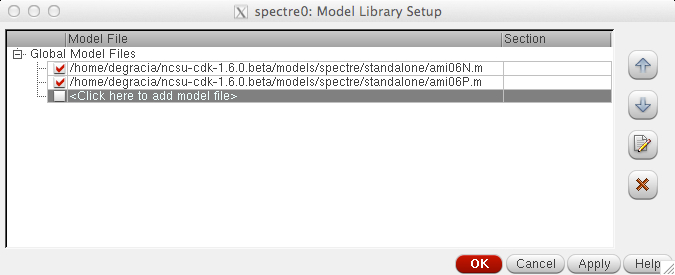

10. Launch ADE and go to Setup > Model Libraries. Set the library to /$HOME /ncsu-cdk-1.6.0.beta/models/spectre/standalone/ami06N.m.

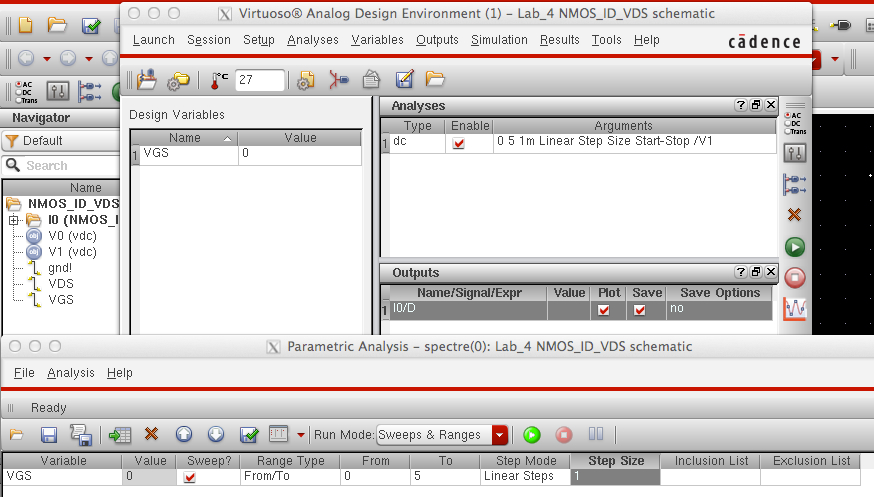

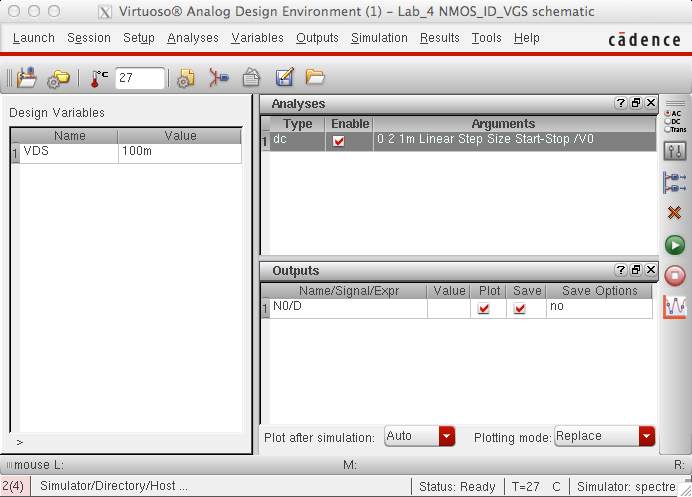

11. In the ADE window, select Variables > Edit, and add VGS = 0 as a parameter.

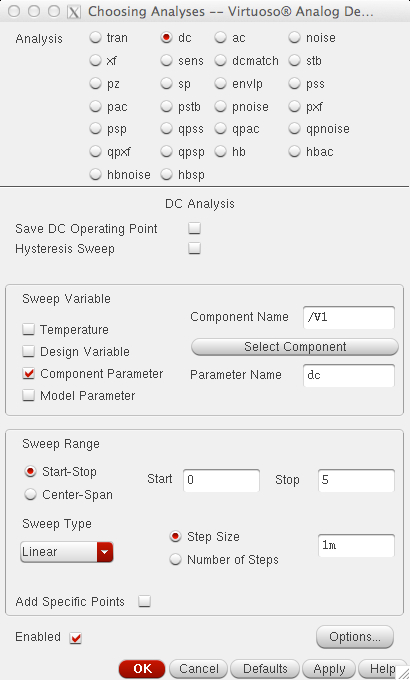

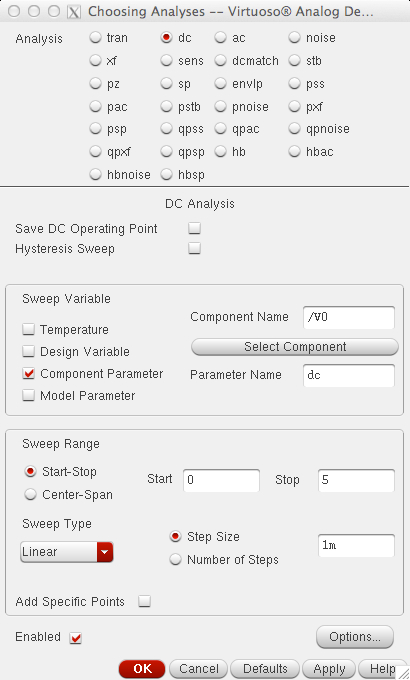

12. Set the Analysis as displayed below.

13. Select Output > To Be Plotted > Select on Schematic. Choose the D pin to be plotted for its current analysis.

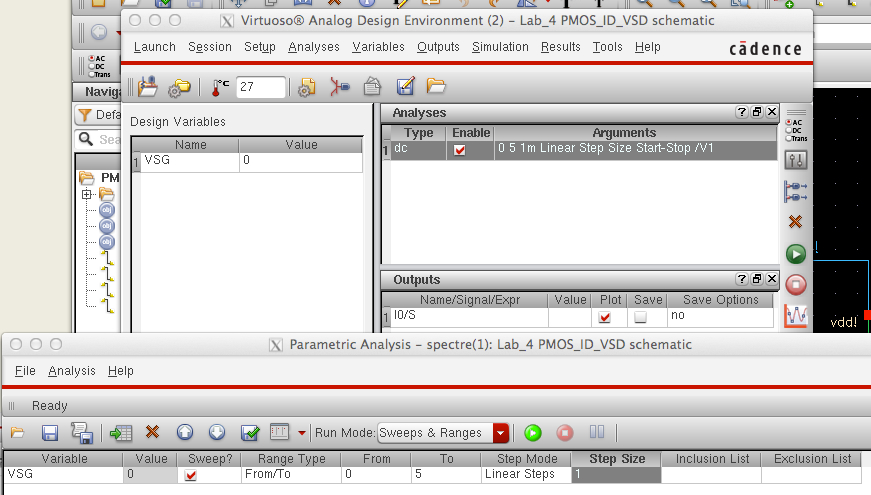

15. Lastly, choose Tools > Parametric Analysis and set the parameters seen below. Click the Green button with an arrow inside to start the Parametric Analysis and simulate the MOSFET IV curves.

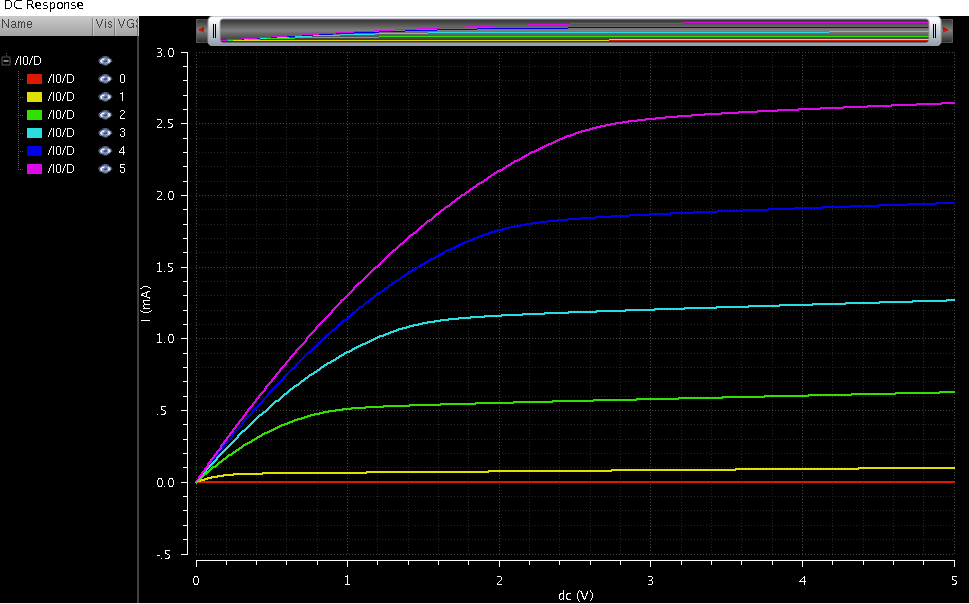

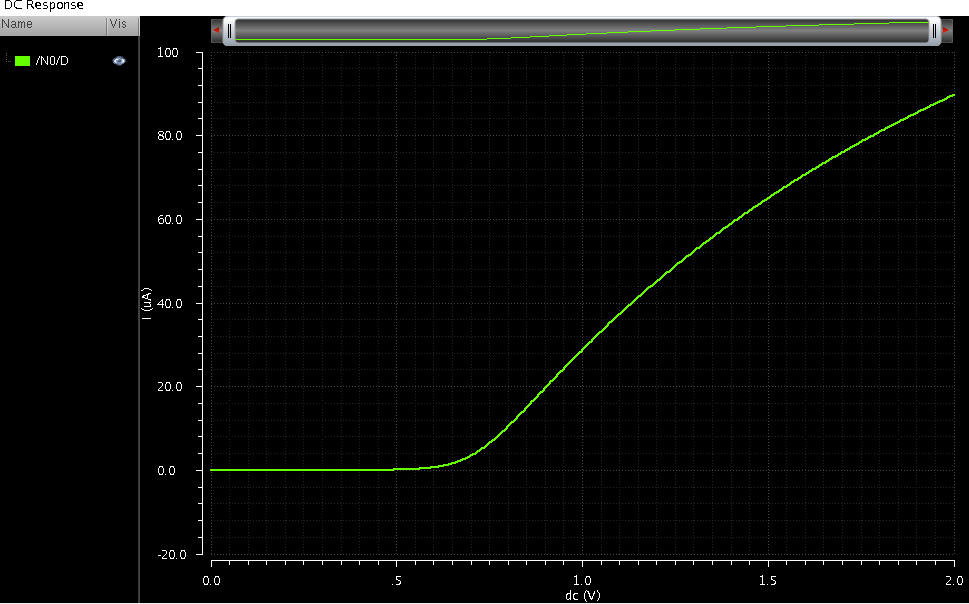

16. Save the simulation state in the cellview. The DC Response should look like the one below.

17. Close all cellviews. Create a layout view for NMOS_IV_3.

18. Instantiate an nmos device that is 6um wide and 600nm long, ptap cell (metal1 connection to p+). DRC the layout.

19. Instatiate a metal1-connection-to-poly cell (m1_poly). In the metal1 layer, add rectangles to connect the source to the p-substrate and the the drain. In the poly layer, add a rectangle to connect the gate to m1_poly. DRC the layout.

20. Add D, G, and S pins on the metal1 layer with I/O type set to InputOutput as seen below. DRC once again and Save the cell.

21. Once DRC finds no errors, extract the layout and open the extracted view. Then LVS the extracted view.

22. An error will be displayed. The

error is related to the bulk (p-substrate) connection for the NMOS.

Again, as mentioned above when the 3 terminal MOSFET symbol is used

it’s assumed

23. Delete the metal1 rectangle and S pin to the ptap. Add seperate rectangles on S and B metal. Save and DRC.

24. Run the extractor and open the extracted view. LVS it again and errors will still be displayed.

25. Open the Library Manager and rename NMOS_IV_3 to NMOS_IV.

26. Open the extracted view and perform an LVS. The LVS should have no errors this time around do the the change from nmos to nmos4.

27. Simulate the extracted layout. Open the schematic view of sim_NMOS_IV and then launch ADE L. Run through the same process as earlier with only one change. Select Setup > Environment and enter "extracted" before "schematic" so the extracted view is used before the schematic view when initiated.

28. Run the Parametric Analysis, which should display the same DC Response graph.

PMOS Device (Similiar to the NMOS Device)

29. Create a schematic Cell View called PMOS_IV with 4 pins as seen below. Note the W and L of the PMOS device. Check and Save.

30. Create a symbol for the schematic. Check and Save.

31. Create a layout and instantiate a pmos cell, m1_poly and ntap. Draw the metal1 rectangles and Pins as displayed below. DRC and Save the layout.

32. Extract the layout and open the extracted view. Save and close all cellviews.

33. Next create a cell called sim_PMOS_IV and draft the following schematic.

34. Launch the ADE then go to Setup > Model Libraries and select the PMOS models for AMI06P.m. Then go to Variables -> Edit and Add VSG with a value of 0 (not VGS).

35. Go through the same process for simulation as we did for the NMOS in the previous steps. This includes adding "extracted" before "schematic"in the enviroment options.

Back up files

Afterwards,

it is always important to backup files by either creating a folder on

your personal computer, emailing the files to yourself and/or backing

it up on a cloud (dropbox, icloud, google drive).

Post-Lab

2. Create a symbol from the schematic (Create > Cellview > From Cellview) and set the pins based on the topology of the schematic above.

3. From the new symbol

4. With the new symbol created, open a new schematic and create the one below following the guidelines in the overview.

5. Launch ADE L for simulation and setup the model libraries to the ones displayed (Setup > Model Libraries). In most cases, the only library needed would be for the device you are simulating, NMOS or PMOS, but I put both in as a habit for when we will start create schematics with both.

6. Setup the DC Analysis in which we set the values of VDS using "Component Parameters."

7. Since we want to plot different values of VGS as well, we will have to do a Parametric Analysis (Tools > Parametric Analysis).

ID v. VGS of an NMOS Device

9. Launch ADE L and setup the DC Analysis.

10. Setup the Model Libraries like earlier.

ID v. VSD of a PMOS Device

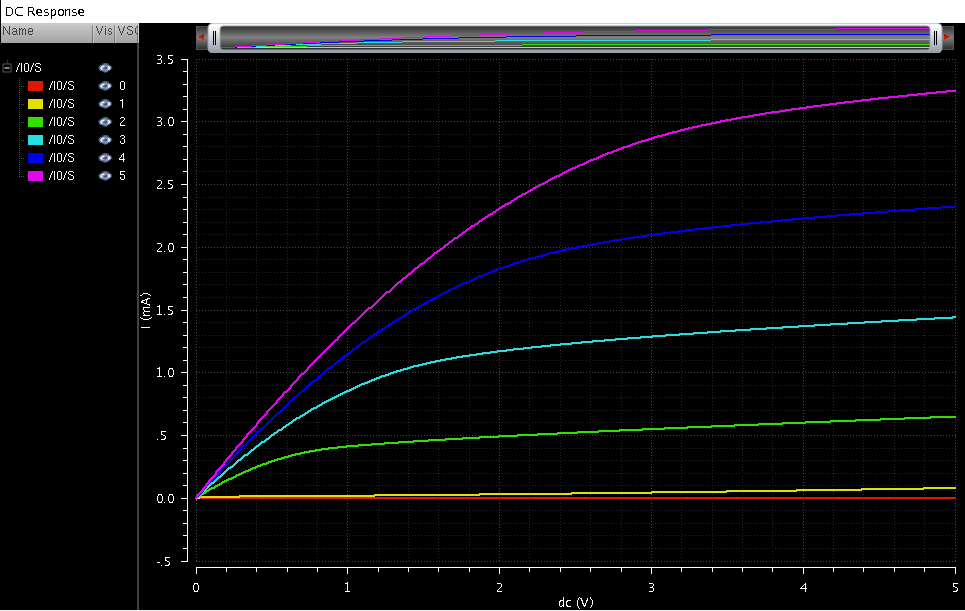

12. Launch ADE L and setup according to the pictures below. Be sure to also set the Model Libraries.

The following DC Response should be displayed, similar to the ID v. VDS of an NMOS device in the first analysis.

ID v. VSG of a PMOS device

14. Setup the Model Libraries once again and the following parameters for the DC Analysis.

15. The following response will then be shown.

Layout a 6u/0.6u NMOS Device w/ 4 Probe Pads

DRC

Schematic

Extracted

LVS

17. Open up the schematic once more and instantiate probe pads to each corresponding pins.

18. Open the layout of the NMOS and following the topology of the schematic, instantiate 4 probe pads and connect them using the appropriate connecters and layers. DRC to make sure you do not encounter any errors such as spacing or layer issues.

19. Extract the layout and LVS to ensure netlists match.

Layout a 12u/0.6u PMOS Device w/ 4 Probe Pads

21. Open up the layout of the PMOS Device and instantiate probe pads following the topology above.

Connect them using the appropriate connecters and layers. DRC to make sure you do not encounter any errors such as spacing or layer issues.

22. Extract the layout and LVS to ensure netlists match.

Back up files

Afterwards,

it is always important to backup files by either creating a folder on

your personal computer, emailing the files to yourself and/or backing

it up on a cloud (dropbox, icloud, google drive).