Simulation Schematic of Ideal ADC and DAC with 2MHz Sinwave Input.

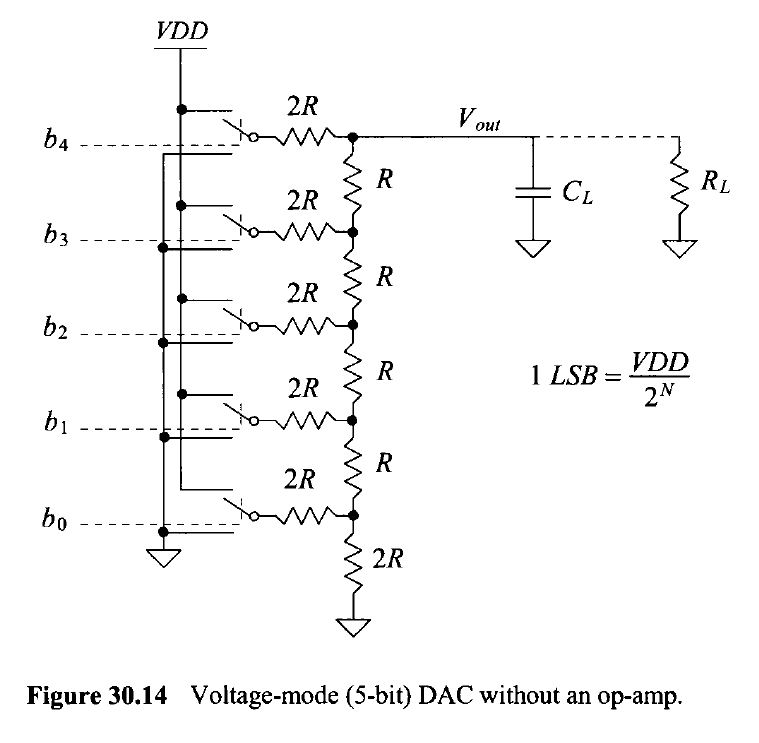

Below is an inside look of the ideal DAC with all of its switches (seen in every DAC_Bit block).

Single Bit of Ideal DAC (Switches)

Ideal DAC Schematic

Plotting

the simulation will result in the following waveform where the input is

a clear, analog, continuous-time sinewave and the output is a digital

(discrete in voltage levels), continuous-time signal that follows the

input curve. The update speed (width of steps) is due to the speed of

the clock.

Simulation of the Above, Ideal Design