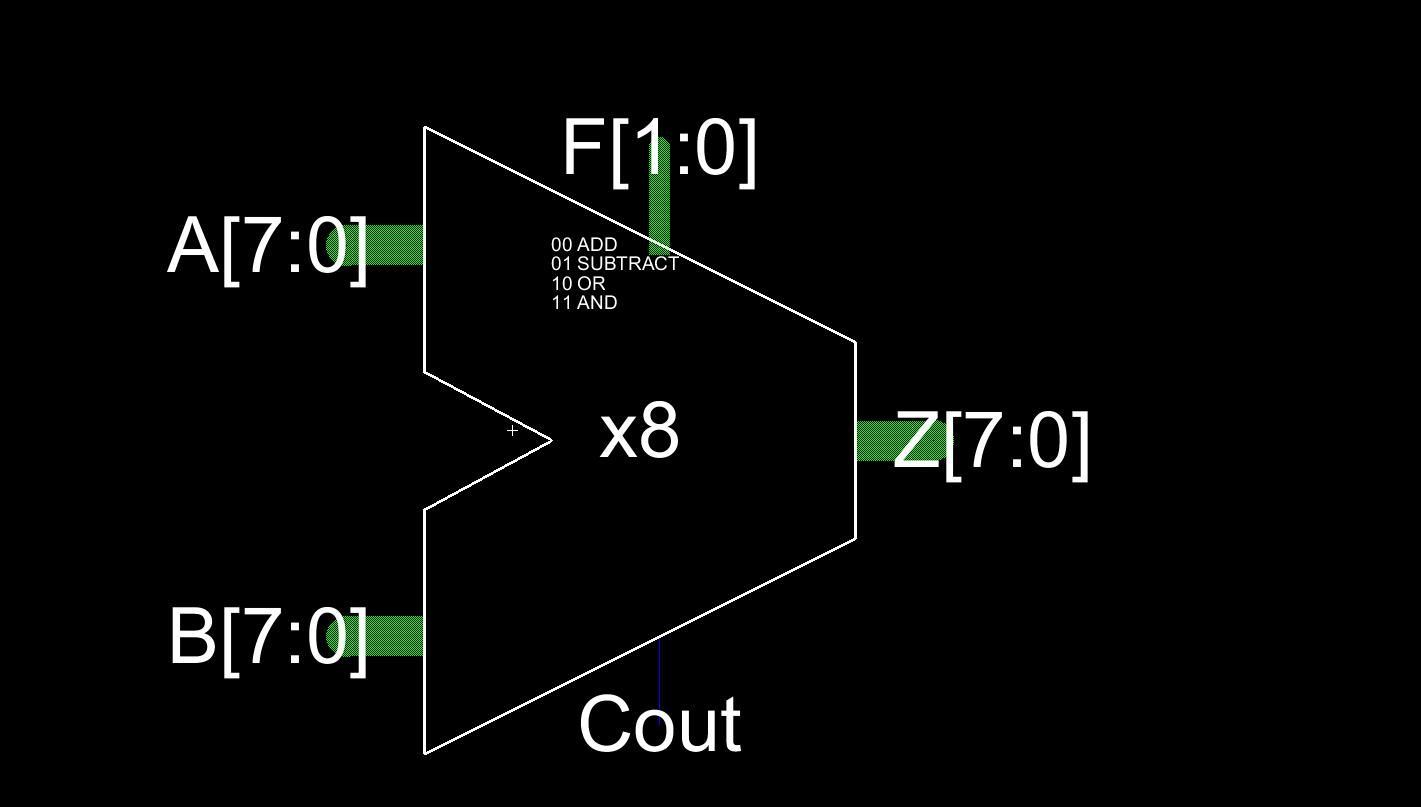

ALU Schematic: (UPDATED LAYOUT)

When F= 00 the ALU calls for addition. The white highlighted buses show the path of addition.

Adder siumulation:

F=00

A=1111 1111 or 255 in Decimal

B=0000 0001 or 1 in Decimal

A+B= 256 or in 8bits it is 0000 0000 with a carry out = 1

When all A inputs were initially set high all the Z outputs went high. After B0 went high all Z outputs dropped low. This is a good simulation because it shows the internal carry bits are working as expected.

When F= 01 the ALU calls for Subtration. The white highlighted buses show the path of subtration.

Here A-B=A+Bi+1 (2's Complement)

Subtration Simulations:

F=01

A= 1111 1111 in Decimal = 255

B=0000 0001 in Decimal = 1

A-B= 1111 1110 in Decimal = 254

This is also a good simulation because it shows that all internal carries are working correctly

When F= 10 the ALU calls for A OR B. The white highlighted buses show the path of A OR B.

F=10

A=0000 1111

B=1111 1000

A OR B=1111 1111

When F= 11 the ALU calls for A AND B. The white highlighted buses show the path of A AND B.

F=11

A=1111 1111

B=0011 1100

A AND B=0011 1100

All the simulations verify that the constructed ALU's four function are working properly and as expected.

Layout of the 8bit ALU

IRSIM of the Layout

The Discription of the Layout

DRC, NCC, and Well check

UX$iFKa{Q3^F

Last Backup all work!!!