Lab 6 - EE 420L

Authored

by Tyler Ferreira,

ferret1@unlv.nevada.edu

March 22, 2017

Pre-lab work

- This lab will utilize the ZVN3306A and ZVP3306A MOSFETs.

- Review these datasheets and become familiar with these transistors.

- Verify that the simulations seen in lab6_sims.zip reasonably model the behavior of the transistors' ID v. VGS, ID v. VDS, and gm v. VGS curves.

- Finally, watch the video single_stage_amps and review single_stage_amps.pdf

- Below are schematics for NMOS and PMOS source followers amplifiers (also known as common-drain amplifiers).

- In your lab report discuss the operation of these circuits.

- The

common-drain amplifier will have the input on the gate and the output

on the source. This means the input signal and output signal will both

be common to the drain of the transistor. The DC voltage on the gate is

found by voltage division with the power supply voltage. The NMOS DC

voltage on the source is found by multiplying the DC current by the 1k

resistor. The PMOS DC voltage on the source is found by subtracting the

voltage drop across the source resistor from the power supply voltage.

- The

AC gain of common-drain amplifiers is close to 1. It is found by

multiplying the AC current by the output resistance. The output

resistance is the output resistance of the transistor in parallel with

the 1k resistor.

- Simulate the operation of these amplifiers.

|  |

NMOS

| PMOS

|

NMOS Offset

| PMOS Offset

|

- Hand

calculate, and then verify your hand calculations with experimentation

and simulations, the gains and the input and output

resistances ensuring that your test signals are at a high enough

frequency that the caps have negligible impedance but not so high that

the gain is dropping off.

| Important Values | NMOS | PMOS |

| Rin | 33.3k | 33.3k |

| Rout | 52.9 | 86.2 |

| gm | 17.9mA/V | 10.6mA/V |

| Vin Operating Point | 3.33V | 1.66V |

| Vout Pperating Point | 1.3V | 4.61V |

| Schematic | LTspice Simulation | Experimental |

NMOS Input Resistance

|  |  |

NMOS Output Resistance

|  |  |

PMOS Input Resistance

|  |  |

PMOS Output Resistance

|  |  |

| NMOS | Hand Calculations | LTspice | Experimental |

| Gain | 0.947 | 1 | ~1 |

| Rin | 33.3k | 33.3k | 33k |

| Rout | 52.9 | 52.9 | 51 |

| PMOS | Hand Calculations | LTspice | Experimental |

| Gain | 0.914 | 1 | ~1 |

| Rin | 33.3k | 33.3k | 33k |

| Rout | 86.2 | 86.2 | 80 |

- If

you build this circuit using electrolitic capacitors, assuming the

input AC signal swings around ground, put the "+" terminal of the cap

on the gate of the MOSFET. Please indicate, in your lab report, that

you understand why the capacitor is connected this way.

- The electrolytic capacitor

is connected with the negative towards the function generator because

the AC signal has a 0V offset. The gate voltage has the 3.33V from the

voltage divider. The positive of the electrolytic capacitor should be

towards the higher potential.

- In your lab report discuss, in your own words, how to measure the input resistance.

- To

measure the input resistance of my amplifier circuit I would insert a

resistor in series with my signal generator. I would then measure the

difference in voltage over that resistor to find the current. Once I

have the current I would divide the the output voltage of the resistor by my measured current to find the input resistance.

- Again, in your lab report discuss how to measure the output resistance.

- To

measure the output resistance of my amplifier I would insert a resistor

from my output to ground. The resistor would be close to what I

calculated in my hand calculations and I would measure the output

voltage to be around half of the original voltage. If this is true that

means the resistor that I added is close to the output resistance of my

circuit since this would create a2 to 1 voltage divider.

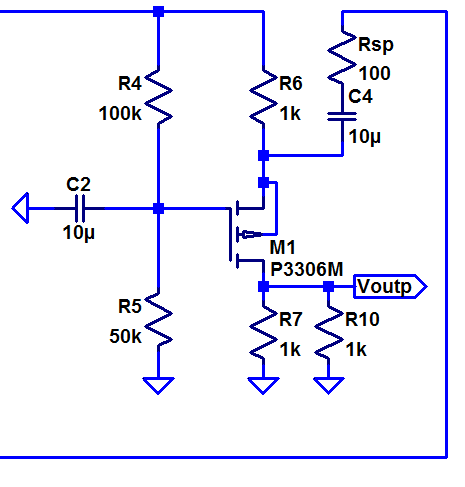

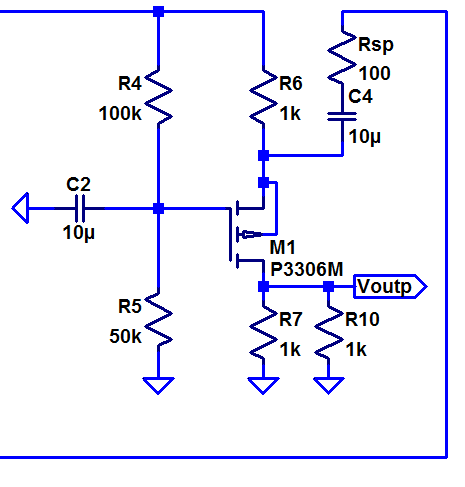

- Below are two common-source amplifiers.

- Discuss the operation of these amplifiers in your lab report including both DC and AC operation.

- The

common-source

amplifier will have the input on the gate and the output on the drain.

This means the input signal and output signal will both be common to

the source of the transistor. The DC voltage on the gate is found by

voltage division with the power supply voltage. The NMOS DC voltage on

the drain is found by subtracting the power supply voltage by the

voltage drop across the drain resistor. For the PMOS DC voltage on the

drain it is just the DC current multiplied by the drain resistor.

|  |

NMOS

| PMOS

|

NMOS Offset

| PMOS Offset

|

- Hand calculate the gains and the input/output resistances.

| Important Values | NMOS | PMOS |

| Rin | 33.3k | 33.3k |

| Rout | 1k | 1k |

| gm | 17.9mA/V | 10.6mA/V |

| Vin Operating Point | 3.33V | 1.66V |

| Vout Operating Point | 3.7V | 0.39V |

- How does the source resistance, Rsn or Rsp, influence the gain.

- Increasing

Rsn or Rsp will decrease the gain of the amplifier circuit. This is

because they are inversely proportional to the gain of the circuit.

- Again compare your hand calculations to simulation and experimental results.

| Schematic | LTspice Simulation | Experimental |

NMOS Input Resistance

|  |  |

NMOS Output Resistance

|  |  |

PMOS Input Resistance

|  |  |

PMOS Output Resistance

|  |  |

| NMOS | Hand Calculations | LTspice | Experimental |

| Gain | -6.813 | -7 | -6.13 |

| Rin | 33.3k | 33.3k | 33k |

| Rout | 1k | 1k | 1k |

| PMOS | Hand Calculations | LTspice | Experimental |

| Gain | -5.4 | -5 | -1.2 |

| Rin | 33.3k | 33.3k | 33k |

| Rout | 1k | 1k | 1k |

- Below are two common-gate amplifiers.

- Discuss the operation of these amplifiers in your lab report including both DC and AC operation.

- The common-gate

amplifier will have the input on the source and the output on the drain.

This means the input signal and output signal will both be common to

the gate of the transistor. The DC voltage on the gate is found by

voltage division with the power supply voltage. The NMOS DC voltage on

the drain is found by subtracting the power supply voltage by the

voltage drop across the drain resistor. For the PMOS DC voltage on the

drain it is just the DC current multiplied by the drain resistor.

|  |

NMOS

| PMOS

|

NMOS Offset

| PMOS Offset

|

- Hand calculate the gains and the input/output resistances.

| Important Values | NMOS | PMOS |

| Rin | 152.9 | 186.2 |

| Rout | 1k | 1k |

| gm | 17.6mA/V | 10.6mA/V |

| Vin Operating Point | 3.33V | 1.66V |

| Vout Operating Point | 3.7 | 0.39 |

- How does the source resistance, Rsn or Rsp, influence the gain.

- Increasing

Rsn or Rsp will decrease the gain of the amplifier circuit. This is

because they are inversely proportional to the gain of the circuit.

- Again compare your hand calculations to simulation and experimental results.

| Schematic | LTspice Simulations | Experimental |

NMOS Input Resistance

|  |  |

NMOS Output Resistance

|  |  |

PMOS Input Resistance

|  |  |

PMOS Output Resistance

|  |  |

| NMOS | Hand Calculations | LTspice | Experimental |

| Gain | 6.19 | 6 | 5.5 |

| Rin | 152.9 | 152.9 | 150 |

| Rout | 1k | 1k | 1k |

| PMOS | Hand Calculations | LTspice | Experimental |

| Gain | 4.91 | 5 | 2.61 |

| Rin | 186.2 | 186.2 | 180 |

| Rout | 1k | 1k | 1k |

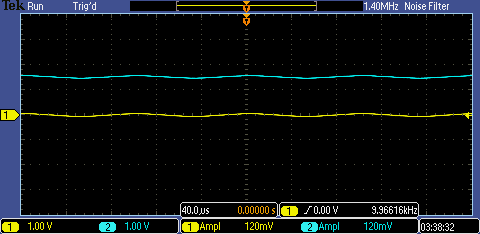

- Below is a push-pull amplifier.

- Discuss the operation of this amplifier in your lab report including both DC and AC operation.

- The

push pull amplifier has an inverter topology. The input signal is on

the gates of the MOSFETs and the output is on the drains of the

MOSFETs. The gain of this amplifier is controlled by the resistor

connected from the gate to the drain multiplied by the parallel

resistance of the transistors. The higher the gate drain resistor the

higher the gain will be.

- Hand calculate the gain of this amplifier.

- Do you expect this amplifier to be good at sourcing/sinking current? Why or why not?

- I expect this amplifier to be goot at both sourcing/sinking current

because the input and the output are connected to both a PMOS and an

NMOS. This means if the PMOS is turned on, the NMOS is turned off and

the circuit is good at sourcing current. When the NMOS is on, the PMOS

is off and the circuit is good at sinking current.

- What happens to the gain if the 100k resistor is replaced with a 510k resistor? Why?

- According

to my hand calculations the gain of the circuit will increase when the

gain drain resistor is increased. When testing this in the lab the gain

does indeed increase with a larger resistor.

- Again compare your hand calculations to simulation and experimental results.

| Experiment with 100k Resistor | Experiment with 510k Resistor |

|  |

| Hand Calculations | LTspice | Experimental |

| Gain with 100k | -2.85k | -2k | 1280 |

| Gain with 510k | -14.5k | -7k | 1920 |

- Note

that the gain of this amplifier is large so the output may saturate at

VDD and Ground. To avoid this saturation you can reduce the AC input

voltage using a voltage divider.

- In

the lab I setup my function generator to output 2mVpp and then

connected it to a voltage divider before connecting to the circuit. The

divider brought the 2mVpp to 1mVpp to keep the output from saturating.

I will backup my work on to my OneDrive and my desktop:

Return to the directory listing of my labs

Return to the directory listing of students in EE 420L, Spring 2017

Return to the EE 420L, Spring 2017 webpage