ECE 421L - Lab 9

For this lab we will be using the CD4007 CMOS transistor array.

The models we used for all our simulations can be found here.

We will build our BMR design and characterize it as we did in the prelab.

We used this design from our prelab for our BMR.

As specified from our prelab, we will be using a large resistor (10G ohms) for the start-up current, this is done by the leakage currrent going through the resistor.

We had to double the widths of our PMOS devices because of the different in the KPP and KPN values in our models.

We will also be using the W/L of 500um/5um from the previous lab.

We picked the resistor to be 50k so that we get the expected gm of 20uA/V since gm = 1/R.

Simulation our above design gives us our desires results.

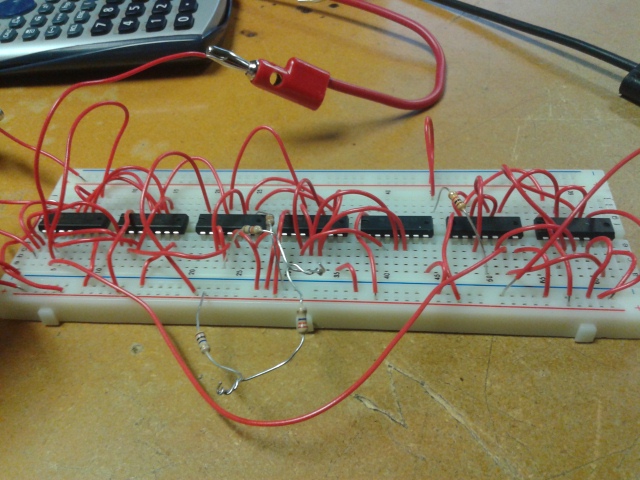

Putting the BMR together we had to use 7 CD4007 transistors.

Using this we then measured the Vbiasn and Vbiasp voltages while we adjusted our VDD voltage from 0 to 10V.

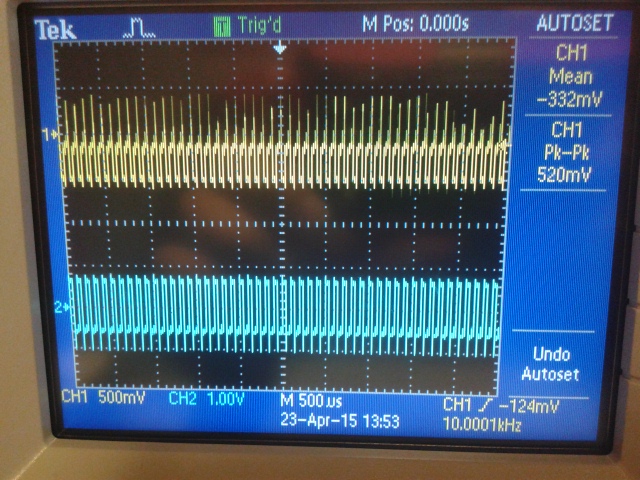

In order to show that a large capacitance across the resistor becomes unstable we did the following experiment:

We shunt the 50k resistor with a 1000uF capacitor and put a 0 to 1V (VDD) square pulse signal as an input.

The following experiment resulted in the following graph

Using our BMR to bias we created a NMOS and PMOS current mirror

Measuring the current through each current mirror as the voltage across the mirror changes.

From our simulation we can see that the curves are a close representation of the simulation curves.

Where ID(M5) is the PMOS and ID(M6) is the NMOS.

For the NMOS the voltage only went up to 1.2 volts because the current after that point stayed the same till 5V.

For the PMOS the voltage was increasingly steadily even up to 5V therefore we kept the small increasing amounts of current for our graphs.

Now using these two devices we are to drive two gate-drain connected transistors.

NMOS current mirror driving two PMOS gate-drain connected devices (cascode)

Measuring the current as we sweep VDD we get the following.