University of Nevada Las Vegas, Department of Electrical and Computer Engineering Laboratories.

Class: CPE300L Semester: Fall 2021

Points Document author: Jerrod Batu

Author's email: batuj1@unlv.nevada.edu

Document topic: Postlab 4

Instructor's comments:

## 1. Introduction / Theory of Operation

Throughout this lab, I will continue Verilog review by learning more about latches and flip-flops, synchronous and asynchronous operations, and asynchronous system design. Some of these latches and flip-flops would include a gated D latch with asynchronous Set' and Clear', JK flip-flop with synchronous clear, D flip flop with asynchronous low clear, etc.

- 1. A **D** flip-flop is a digital electronic circuit that delays output state change until its next rising edge where an input would be called upon. Specifically, the D flip-flop behaves similar to memory as the output will stay constant until it is altered from the D input at the rising clock edge. They are, in fact, utilized as building block shift registers that can store clock cycles. A **JK** flip-flop, in general, is a gated S-R latch with the AND and NOR gates replaced as NAND gates. JK flip-flops are the most used flip-flop designs because they are very universal. The two inputs "J" and "K" are named after the inventor Jack Kilby. The JK flip-flop acts only at a rising clock edge, and the output would toggle from state to state. When J and K are both low, the output is retained and no changes would occur.

- 2. Waveforms are used to check the correctness of a circuit by comparing inputs to the outputs in a "form of a wave"; therefore, the inputs would be clocked at a specific time period that the output would follow based on the combinational logic of the electronic circuit. Waveforms would not be ideal for a large number of inputs as this would become a long and tedious process. Testbenches enhances this process by comparing the user's Verilog code to its expected output; hence, comparing a large number of inputs and outputs would allow the user to efficiently check the correctness of a circuit.

### 2. Prelab

$\frac{https://docs.google.com/document/d/18KNm2l3hURA8lTZ1jOOj9OqBpmHYE14P/edit?usp=sharing\&ouid=102808507017671072128\&rtpof=true\&sd=true$

This is the link to my prelab 4 submission.

# 3. Results of Experiments

# Experiment 1

a.

```

module asyncDFF (D, Clock, ClearN, Q, QN);

input D, Clock, ClearN;

2

3

output Q, QN;

4

reg Q;

5

6

always @ (posedge Clock, negedge ClearN)

7

begin

8

if (~ClearN)

9

Q = 0;

10

11

Q = D;

12

13

assign QN = ~Q;

14

endmodule

15

```

This is the Verilog code for a D flip flop with asynchronous low clear and complementary output.

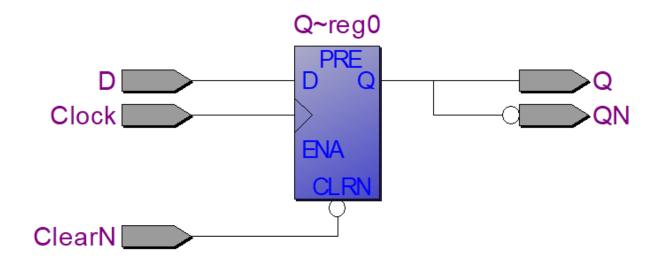

This is the RTL view for my D flip flop with asynchronous low clear and complementary output.

## **Experiment 2**

a.

```

1

`timescale 1 ns / 100 ps

2

3

module regDFF (D, Clock ,ClearN, Q, QN);

4

input [3:0] D;

5

input Clock, ClearN;

6

output [3:0] Q, QN;

7

8

asyncDFF DFF0 (D[0], Clock, ClearN, Q[0], QN[0]);

9

asyncDFF DFF1 (D[1], Clock, ClearN, Q[1], QN[1]);

10

asyncDFF DFF2 (D[2], Clock, ClearN, Q[2], QN[2]);

11

asyncDFF DFF3 (D[3], Clock, ClearN, Q[3], QN[3]);

12

endmodule

13

14

// asynchronous D Flip Flop

15

module asyncDFF (D, Clock, ClearN, Q, QN);

16

input D, Clock, ClearN;

17

output Q, QN;

18

reg Q;

19

20

always @ (posedge Clock, negedge ClearN)

21

begin

22

if (~ClearN)

23

Q  <= 0;

24

else

25

Q \le D;

26

end

27

assign QN = \sim Q;

28

endmodule

29

```

This is the Verilog code for instantiating the DFF from experiment 1 into a 4-bit register which uses D flip-flops.

```

b.

`timescale 1 ns / 100 ps

2

3

// register D Flip Flop Testbench

4

module regDFF_tb;

5

reg [3:0] Dtb;

reg Clocktb = 1'b1;

7

reg ClearNtb = 1'b1;

8

wire [3:0] Qtb, QNtb;

9

'define PERIOD 10

11

always

13

#(`PERIOD/2) Clocktb = ~Clocktb;

14

15

regDFF U0 (

16

.D (Dtb).

.Clock (Clocktb),

17

18

.ClearN (ClearNtb),

19

.Q (Qtb),

20

.QN (QNtb)

21

22

23

initial begin

24

$timeformat (-9, 1, "ns", 9);

25

$monitor ( "time=%t Dtb = %b

ClrNtb = %b

Qtb = %b

QNtb = %b", $time, Dtb,

ClearNtb,

Qtb,

QNtb);

#(`PERIOD * 100)

26

27

$display ( "TESTING TIMEOUT" );

28

$finish:

29

end

31

task expectedResult (input [3:0] expected);

if (Qtb !== expected)

33

begin

34

$display ( "Qtb=%b, but expected value is %b", Qtb, expected);

35

$display ( "Test Failed" );

36

$finish;

37

end

38

endtask

39

task expectedResultN (input [3:0] expectedN);

40

if (QNtb !== expectedN)

41

42

begin

43

$display ( "QNtb=%b, but expected value is %b", QNtb, expectedN);

$display ( "Test Failed" );

44

45

$finish;

46

end

47

endtask

48

49

initial

50

begin

51

@ (negedge Clocktb)

52

{ ClearNtb, Dtb } = 5'bl XXXX; @(negedge Clocktb) expectedResult ( 4'bxxxx ); @(negedge Clocktb) expectedResultN ( 4'bxxxx );

53

{ ClearNtb, Dtb } = 5'b0_XXXX; @(negedge Clocktb) expectedResult ( 4'b0000 ); @(negedge Clocktb) expectedResultN ( 4'b1111 );

{ ClearNtb, Dtb } = 5'bl_XXXX; @(negedge Clocktb) expectedResult ( 4'bxxxx ); @(negedge Clocktb) expectedResultN ( 4'bxxxx );

{ ClearNtb, Dtb } = 5'bl_1101; @(negedge Clocktb) expectedResult ( 4'bl101 ); @(negedge Clocktb) expectedResultN ( 4'b0010 );

55

{ ClearNtb, Dtb } = 5'bl_1010; @(negedge Clocktb) expectedResult ( 4'b1010 ); @(negedge Clocktb) expectedResultN ( 4'b0101 );

57

{ ClearNtb, Dtb } = 5'b0_XXXX; @(negedge Clocktb) expectedResult ( 4'b0000 ); @(negedge Clocktb) expectedResultN ( 4'b1111 );

{ ClearNtb, Dtb } = 5'bl_XXXX; @(negedge Clocktb) expectedResult ( 4'bxxxx ); @(negedge Clocktb) expectedResultN ( 4'bxxxx );

58

{ ClearNtb, Dtb } = 5'bl_1010; @(negedge Clocktb) expectedResult ( 4'b1010 ); @(negedge Clocktb) expectedResultN ( 4'b0101 );

59

{ ClearNtb, Dtb } = 5'bl_1101; @(negedge Clocktb) expectedResult ( 4'b1101 ); @(negedge Clocktb) expectedResultN ( 4'b0010 );

$display ( "****Test PASSED*****" );

61

$finish;

63

end

64

endmodule

65

```

This is the Verilog code for the 4-bit register which uses D flip-flops testbench.

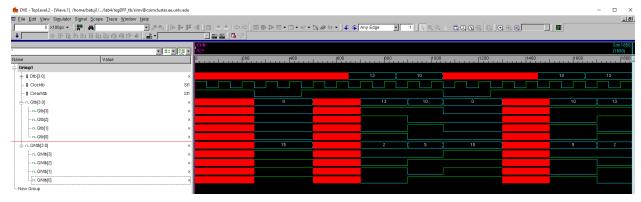

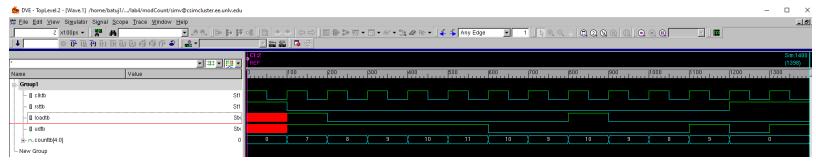

These are my VCS waveforms for the 4-bit DFF register. The blocks of red indicate delay or if the output is a "don't care (X) value".

d.

```

Chronologic VCS simulator copyright 1991-2017

Contains Synopsys proprietary information.

Compiler version N-2017.12-SP2-14; Runtime version N-2017.12-SP2-14; Sep 21 23:24 2021

VCD+ Writer N-2017,12-SP2-14 Copyright (c) 1991-2017 by Synopsys Inc.

The file '/home/batuj1/Fall2021/lab4/regDFF_tb/inter.vpd' was opened successfully.

Dtb = xxxx

time=

0.0ns

ClrNtb = 1

Qtb = xxxx

QNtb = xxxx

time=

25.0ns

Dtb = xxxx

C1rNtb = 0

Qtb = 0000

QNtb = 1111

time=

Qtb = 0000

45,0ns

Dtb = xxxx

ClrNtb = 1

QNtb = 1111

Dtb = xxxx

Qtb = xxxx

time=

50,0ns

ClrNtb = 1

QNtb = xxxx

Dtb = 1101

ClrNtb = 1

Qtb = xxxx

time=

65.0ns

QNtb = xxxx

70,0ns

Dtb = 1101

ClrNtb = 1

Qtb = 1101

QNtb = 0010

time=

85.0ns

Dtb = 1010

ClrNtb = 1

Qtb = 1101

QNtb = 0010

time=

Dtb = 1010

ClrNtb = 1

Qtb = 1010

QNtb = 0101

time=

<u>90.0ns</u>

Dtb = xxxx

C1rNtb = 0

Qtb = 0000

QNtb = 1111

time=

105,0ns

125,0ns

Dtb = xxxx

ClrNtb = 1

Qtb = 0000

QNtb = 1111

time=

ClrNtb = 1

QNtb = xxxx

130,0ns

Dtb = xxxx

Qtb = xxxx

time=

Dtb = 1010

ClrNtb = 1

QNtb = xxxx

145,0ns

Qtb = xxxx

time=

150,0ns

Dtb = 1010

ClrNtb = 1

Qtb = 1010

QNtb = 0101

time=

time=

165,0ns

Dtb = 1101

ClrNtb = 1

Qtb = 1010

QNtb = 0101

Qtb = 1101

QNtb = 0010

time=

170,0ns

Dtb = 1101

ClrNtb = 1

*****Test PASSED*****

$finish called from file "regDFF_tb.v", line 62.

$finish at simulation time

Simulation complete, time is 185000 ps.

```

This is my VCS simulation console for the 4-bit DFF register.

## Experiment 3

a.

```

1

timescale 1 ns / 100 ps

2

3

module regBehaveDFF (D, Clock, ClearN, Q, QN);

4

input [3:0] D;

5

input Clock, ClearN;

6

output reg [3:0] Q;

7

output [3:0] QN;

8

9

always @ (posedge Clock, negedge ClearN)

10

begin

11

if (~ClearN)

12

Q = 4'b00000;

13

14

Q = D;

15

end

16

assign QN = ~Q;

17

18

endmodule

19

```

This is my behavioral Verilog code for instantiating the DFF from experiment 1 into a 4-bit register which uses D flip-flops.

b.

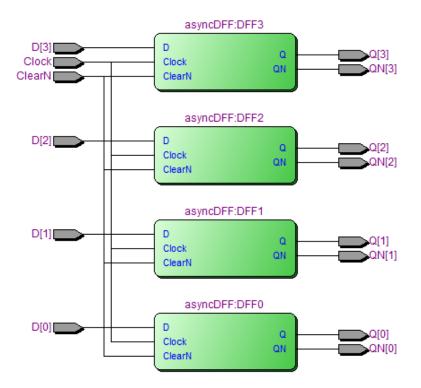

This is the RTL View of the structural 4-bit DFF register.

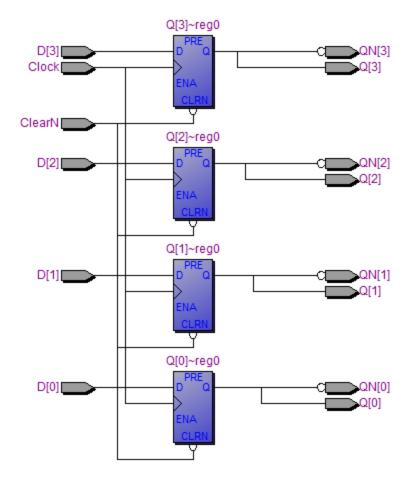

This is the RTL View of the behavioral 4-bit DFF register.

From the RTL view of both behavioral and structural, both are quite similar in the lower hierarchy. For example, by clicking on each "green" block of the structural RTL view, the instantiation of the DFF is the same as the behavioral RTL view. The reason for the "green" blocks for the structural RTL view is due to the instantiation of the DFF module. Since there is no instantiation for the behavioral model, the D flip-flops can easily be seen in the behavioral view because the 4 bits are designated to each individual D flip-flop within the code. The "green" blocks of the structural code simply just show instantiation of another module; whereas, the behavioral code would show the 4 bits spread to each D flip-flop.

### Experiment 4

a.

```

`timescale 1 ns / 100 ps

3

module modCount (inclk, rst, ud, load, data, count, segments1, segments2);

input inclk, rst, ud, load;

4

5

input [4:0] data;

6

output reg [4:0] count = 0;

output reg [6:0] segments1, segments2;

8

wire outclk;

9

onehertz U0(

10

// calls to the onehertz module

11

.clk_50mhz (inclk),

.clk_lhz (outclk)

12

13

14

15

always @ (posedge outclk, posedge rst)

16

begin

17

if (rst == 1)

// dont count if reset

18

count = 0;

19

else if (load)

// load input into output

20

count = data;

21

else

22

if (ud == 1)

// count up

23

if (count == 25)

24

begin

25

// counter is 0 when reached 25

count = 0;

26

end

27

else

28

begin

// increment counter

29

count = count + 1;

30

end

31

else

// count down

þ

32

begin

33

if (count == 0)

// if there is not count...

34

begin

35

count = 25;

// counter starts at 25

36

end

37

else

38

begin

39

count = count - 1; // decrement counter

40

41

end

42

end

43

44

// 7-segment display

日日日

45

always @ (count) begin

46

case (count)

47

0 : begin

segments1 = 7'b0000001;

48

segments2 = 7'b0000001;

49

50

end

4

51

1 : begin

52

segments1 = 7'b1001111;

53

segments2 = 7'b0000001;

54

end

中

55

2 : begin

segments1 = 7'b0010010;

56

segments2 = 7'b0000001;

57

```

```

上

58

end

59

3 : begin

60

segments1 = 7'b0000110;

61

segments2 = 7'b0000001;

62

63

4 : begin

64

segments1 = 7'b1001100;

segments2 = 7'b0000001;

65

66

end

67

5 : begin

segments1 = 7'b0100100;

68

69

segments2 = 7'b00000001;

70

end

6 : begin

71

72

segments1 = 7'b01000000;

73

segments2 = 7'b00000001;

74

end

75

7 : begin

76

segments1 = 7'b0001111;

77

segments2 = 7'b00000001;

78

end

79

8 : begin

80

segments1 = 7'b00000000;

81

segments2 = 7'b00000001;

82

end

83

9 : begin

84

segments1 = 7'b0000100;

85

segments2 = 7'b0000001;

86

87

10 : begin

segments1 = 7'b0000001;

88

89

segments2 = 7'b1001111;

90

end

91

11 : begin

92

segments1 = 7'b1001111;

segments2 = 7'b1001111;

93

94

end

95

12 : begin

96

segments1 = 7'b0010010;

97

segments2 = 7'b1001111;

98

end

99

13 : begin

100

segments1 = 7'b0000110;

101

segments2 = 7'b1001111;

102

end

103

14 : begin

104

segments1 = 7'b1001100;

105

segments2 = 7'b1001111;

106

end

107

15 : begin

108

segments1 = 7'b0100100;

109

segments2 = 7'b1001111;

110

end

111

16 : begin

segments1 = 7'b0100000;

112

113

segments2 = 7'b1001111;

114

```

```

115

17 : begin

116

segments1 = 7'b00011111;

117

segments2 = 7'b10011111;

118

end

\vdash

119

18 : begin

120

segments1 = 7'b00000000;

121

segments2 = 7'b1001111;

122

end

19 : begin

123

124

segments1 = 7'b0000100;

segments2 = 7'b1001111;

125

126

end

127

20 : begin

128

segments1 = 7'b00000001;

129

segments2 = 7'b0010010;

130

end

131

21 : begin

132

segments1 = 7'b1001111;

133

segments2 = 7'b0010010;

134

end

135

22 : begin

136

segments1 = 7'b0010010;

137

segments2 = 7'b0010010;

138

end

139

23 : begin

140

segments1 = 7'b0000110;

141

segments2 = 7'b0010010;

142

end

143

白

24 : begin

144

segments1 = 7'b1001100;

145

segments2 = 7'b0010010;

146

end

147

25 : begin

148

segments1 = 7'b0100100;

149

segments2 = 7'b0010010;

150

151

26 : begin

152

segmentsl = 7'b01000000;

153

segments2 = 7'b0010010;

154

end

155

default:

156

begin

157

segments1 = 7'bllllllll;

158

segments2 = 7'b11111111;

159

end

160

endcase

161

end

162

163

endmodule

164

165

module onehertz(clk_50mhz, clk_lhz);

166

input clk 50mhz;

167

output clk_lhz;

168

reg clk_lhz;

169

reg [24:0] count;

170

always @ (posedge clk_50mhz)

171

begin

```

```

if(count == 24999999) begin

173

count <= 0;

174

$dumpfile("f.vcd");

175

clk_lhz <= ~clk_lhz;

176

end

177

else begin

178

count <= count + 1;

179

end

180

end

181

endmodule

182

```

This is my Verilog code for the 5-bit mod-25 up/down counter including a clock divider and a 7 segment display.

b.

```

`timescale 1 ns / 100 ps

module modCount_tb;

reg clktb = 1'bl;

reg rsttb = 1'bl;

reg udtb;

reg loadtb;

reg [4:0] datatb;

wire [4:0] counttb;

wire [6:0] segl, seg2;

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

'define PERIOD 10

#('PERIOD/2) clktb = ~clktb;

modCount U0 (

.clk (clktb),

.rst (rsttb),

.ud (udtb),

.load (loadtb),

.data (datatb),

.count (counttb)

.segmentsl (segl)

.segments2 (seg2)

$timeformat (-9, 1, "ns", 9);

$monitor ( "time=%t datatb

#(`PERIOD * 100)

datatb = %b

rsttb = %b

udtb = %b counttb = %b", $time, datatb, rsttb, udtb, counttb);

$display ( "TESTING TIMEOUT" );

$finish;

32

33

34

35

36

37

38

40

41

42

43

44

45

46

47

48

49

50

51

task expectedResult (input [4:0] expected);

if (counttb !== expected)

begin

$display ( "counttb=%b, but expected value is %b", counttb, expected);

$finish;

end

initial

begin

54

55

{ rsttb, loadtb, udtb, datatb } = 8^{\circ}b_0 = 1_0 = 0.000; & (posedge clktb) expectedResult ( 5^{\circ}b = 0.000); { rsttb, loadtb, udtb, datatb } = 8^{\circ}b_1 = 0.0000; & (posedge clktb) expectedResult ( 5^{\circ}b = 0.0000); { (rsttb, loadtb, udtb, datatb) = 8^{\circ}b_1 = 0.00000; & (posedge clktb) expectedResult ( 5^{\circ}b = 0.00000); & (display ( "******Test PASSED******* );

$finish;

endmodule

```

This is my Verilog code for the 5-bit mod-25 up/down counter testbench.

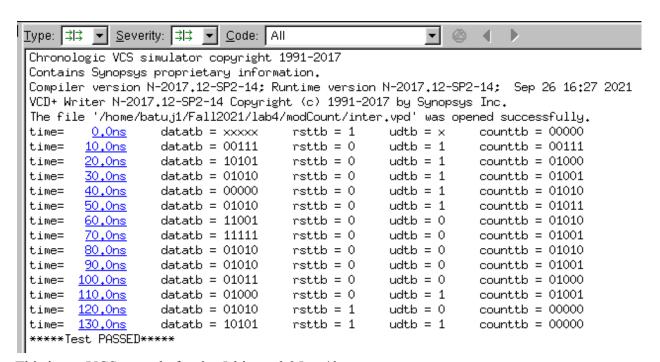

These are my VCS waveforms for the 5-bit mod-25 up/down counter.

This is my VCS console for the 5-bit mod-25 up/down counter.

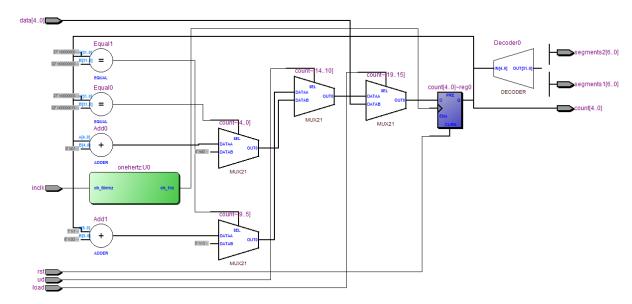

This is my RTL view for the 5-bit mod-25 up/down counter including a clock divider and a 7 segment display.

e.

| Fitter Status                      | Successful - Sun Sep 26 16:58:40 2021           |

|------------------------------------|-------------------------------------------------|

| Quartus II 64-Bit Version          | 13.0.1 Build 232 06/12/2013 SP 1 SJ Web Edition |

| Revision Name                      | modCount                                        |

| Top-level Entity Name              | modCount                                        |

| Family                             | Cyclone II                                      |

| Device                             | EP2C35F672C6                                    |

| Timing Models                      | Final                                           |

| Total logic elements               | 95 / 33,216 ( < 1 % )                           |

| Total combinational functions      | 95 / 33,216 ( < 1 % )                           |

| Dedicated logic registers          | 31 / 33,216 ( < 1 % )                           |

| Total registers                    | 31                                              |

| Total pins                         | 28 / 475 ( 6 % )                                |

| Total virtual pins                 | 0                                               |

| Total memory bits                  | 0 / 483,840 (0 %)                               |

| Embedded Multiplier 9-bit elements | 0 / 70 (0 %)                                    |

| Total PLLs                         | 0/4(0%)                                         |

|                                    |                                                 |

This is my compilation report of the total utilization, combinational ALUTs, and dedicated logic registers for the 5-bit mod-25 up/down counter including a clock divider and a 7 segment display.

# f. <a href="https://drive.google.com/file/d/1hoacqdml03irNyL9vXW9phvNSH5imaPM/view?usp=sh">https://drive.google.com/file/d/1hoacqdml03irNyL9vXW9phvNSH5imaPM/view?usp=sh</a> aring

This is the link to my video delivery of 4(b). The video will also be included within the batuj1\_postlab\_4.zip file.

## 4. Answers to questions

### **Question 1:**

Regarding Logic Utilization from the Quartus Compilation Report, the ALUT is utilized to show half-ALMS (half-adaptive logic modules). Half-ALMS are half-adaptive logic modules, meaning that the ALUT has 2 combinational logic look up tables (LUTs) and 2 registers becoming one total adaptive look up table (ALUT). ALUTs show the actual number of partial or final half-ALMs in the design after it is placed. In general, the ALUT reveals the combinational logic needed for each register or flip-flop to form. The Dedicated Logic Registers are the two registers within the ALM. The ALM is the essential building block of supported device families and is made to maximize the performance of registers as well as resource usage. Each adaptive logic module can hold up to 8 inputs and 8 outputs. The reason for the ALM is to show the logic registers used to complete the total logic elements within the Verilog code design.

### **Question 2**:

Clock-gating is when the clock is directed to each flip-flop within the design to reveal that each flip-flop is clocked continuously rather than individually. The purpose of clock-gating is to reduce unnecessary clocking to each register; thus, registers do not need to be clocked if the input data does not change. Clock-gating is inserted in two ways: local clock-gating and global clock-gating. Local clock-gating has the logic synthesizer find and utilize local gating opportunities and the RTL code would have the clock-gating cell instantiated within it. Global clock-gating specifically specifies the clock gating within the RTL code and follows the local clock-gating where the clock-gating cell is instantiated within it. Overall, clock-gating saves unnecessary clocking to each register by continuous clocking rather than individual clocks assigned to each individual register.

### **Question 3**

The key difference between tasks and functions is that a function is to return a single value in regards to processing the input; whereas, a task can return multiple values and return these values using the output arguments. Tasks can also contain timing simulations where functions cannot utilize any timing. Tasks and functions are used when an operation is continuously repeated throughout the Verilog code. Instead of rewriting that same code, the task or function operation can be used. This reduces copy and paste errors and permits faster development time as well as making a code cleaner and easier to read.

### **5. Conclusions & Summary**

This lab was one of the easier labs, and I was able to go more in depth with my knowledge of flip-flops and registers. In the CPE 200 lab, I had a hard time implementing the clock within my code; therefore, the provided clock divider definitely helped for the 4th experiment. The main issues within this lab occurred with experiment 4. When I originally coded my design, I did not take into account the clock behaving differently than my own interpretation of it; therefore, I used the clock divider. Although I had already completed the testbench, VCS console, and the VCS waveforms of my code, the clock divider gave several issues within my assignment. Without the clock divider, I would not be able to properly output my code into the DE2 board and make it properly output. I hope this issue does not continue into more labs, and I will be able to fix it for the future.