### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

| In re Patent of:  | Iihola et al.                          |                                   |

|-------------------|----------------------------------------|-----------------------------------|

| U.S. Patent No .: | 11,716,816                             | Attorney Docket No. 50095-0199IP1 |

| Issue Date:       | August 1, 2023                         |                                   |

| Appl. Serial No.: | 17/364,593                             |                                   |

| Filing Date:      | June 30, 2021                          |                                   |

| Title:            | METHOD FOR MANUFACTURING AN ELECTRONIC |                                   |

|                   | MODULE AND                             | ELECTRONIC MODULE                 |

#### **DECLARATION OF DR. R. JACOB BAKER**

I declare that all statements made herein on my own knowledge are true and that all statements made on information and belief are believed to be true, and further, that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of the Title 18 of the United States Code.

Dated: 2/5/2025 By: <u>A. J. Dan</u> R. JACOB BAKER, PH.D., P.E.

# **Table of Contents**

| I.    | Materials Considered5                                                           |                                |                                                       |    |

|-------|---------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------|----|

| II.   | Quali                                                                           | Qualifications And Background7 |                                                       |    |

| III.  | Relevant Legal Standards10                                                      |                                |                                                       | 10 |

| IV.   | 7. Technology Background                                                        |                                |                                                       | 13 |

|       | A.                                                                              | Semi                           | conductor Components for Multi-chip Modules           | 13 |

|       | B.                                                                              | Bond                           | ing Techniques                                        | 24 |

|       |                                                                                 | i.                             | Ultrasonic Bonding                                    | 25 |

|       |                                                                                 | ii.                            | Thermo-compression Bonding                            | 26 |

| V.    | Perso                                                                           | n of O                         | rdinary Skill in the Art                              | 26 |

| VI.   | Over                                                                            | view o                         | f the Subject Patent US 11,716,816, "The '816 Patent" |    |

| VII.  | Prosecution History of the '816 Patent                                          |                                |                                                       |    |

| VIII. | Clain                                                                           | Claim Construction             |                                                       |    |

| IX.   | Over                                                                            | erview of Conclusions Formed   |                                                       |    |

| Х.    | GROUND 1A – Tsubosaki010 in View of Tsubosaki405 Renders Obvious<br>Claims 1-14 |                                |                                                       |    |

|       | A.                                                                              | Tsub                           | osaki010 Overview (APPLE-1005)                        | 33 |

|       | B.                                                                              | Tsub                           | osaki405 Overview (APPLE-1011)                        | 36 |

|       | C.                                                                              | The 7                          | Subosaki010-Tsubosaki405 Combination Overview         |    |

|       | D. Analysis                                                                     |                                | 43                                                    |    |

|       |                                                                                 | i.                             | Claim 1                                               | 43 |

|       |                                                                                 | ii.                            | Claim 2                                               | 58 |

|       |                                                                                 | iii.                           | Claim 3                                               | 59 |

|       |                                                                                 | iv.                            | Claim 4                                               | 60 |

|      |     | v.                                                                                  | Claim 5                                      | .61 |

|------|-----|-------------------------------------------------------------------------------------|----------------------------------------------|-----|

|      |     | vi.                                                                                 | Claim 6                                      | .62 |

|      |     | vii.                                                                                | Claim 7                                      | .63 |

|      |     | viii.                                                                               | Claim 8                                      | .64 |

|      |     | ix.                                                                                 | Claim 9                                      | .69 |

|      |     | X.                                                                                  | Claim 10                                     | .69 |

|      |     | xi.                                                                                 | Claim 11                                     | .70 |

|      |     | xii.                                                                                | Claim 12                                     | .71 |

|      |     | xiii.                                                                               | Claim 13                                     | .71 |

|      |     | xiv.                                                                                | Claim 14                                     | .72 |

| XI.  | GRC | UND                                                                                 | 1B: Tsubosaki010 Renders Obvious Claims 1-14 | .74 |

| XII. |     | GROUND 2: Oya in View of Shugg Renders Obvious Claims 1, 3-4, 6<br>10-11, and 13-14 |                                              |     |

|      | A.  | -                                                                                   | Overview                                     |     |

|      | B.  | Shug                                                                                | g Overview                                   | .77 |

|      | C.  | The (                                                                               | Oya-Shugg Combination Overview               | .78 |

|      | D.  | Anal                                                                                | ysis                                         | .81 |

|      |     | i.                                                                                  | Claim 1                                      | .81 |

|      |     | ii.                                                                                 | Claim 3                                      | .94 |

|      |     | iii.                                                                                | Claim 4                                      | .95 |

|      |     | iv.                                                                                 | Claim 6                                      | .96 |

|      |     | v.                                                                                  | Claim 7                                      | .98 |

|      |     | vi.                                                                                 | Claim 8                                      | .99 |

|       | vii.                 | Claim 10 |     |

|-------|----------------------|----------|-----|

|       | viii.                | Claim 11 | 115 |

|       | ix.                  | Claim 13 | 117 |

|       | Х.                   | Claim 14 | 120 |

| XIII. | . Additional Remarks |          |     |

| XIV.  | . Listing of Claims  |          |     |

I, R. Jacob Baker, Ph.D., P.E., do hereby declare:

1. I have been engaged by Fish & Richardson P.C. ("Fish") on behalf of Apple, Inc. ("Apple" or "Petitioner") to provide my independent analysis of issues relating to the patentability of claims of U.S. Patent No. 11,716,816.

2. I am being compensated for my work in this matter at my standard hourly rate for consulting services. My compensation in no way depends on the outcome of this proceeding or the content of my testimony.

# I. MATERIALS CONSIDERED

3. In preparing this Declaration, I considered the following materials:

| APPLE-1001 | U.S. Patent No. 11,716,816 (the "'816 Patent")                                                                                        |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| APPLE-1002 | Excerpts from the Prosecution History of the '816 Patent                                                                              |

| APPLE-1004 | U.S. Pub. 2004/0000710 A1 ("Oya")                                                                                                     |

| APPLE-1005 | U.S. Pub. 2002/0180010 A1 ("Tsubosaki010")                                                                                            |

| APPLE-1006 | Shugg, W. Tillar, HANDBOOK OF ELECTRICAL AND<br>ELECTRONIC INSULATING MATERIALS, 2nd Edition, Wiley-<br>IEEE Press, 1995 ("Shugg")    |

| APPLE-1007 | U.S. Pub. 2003/0102572 A1 ("Nathan 1")                                                                                                |

| APPLE-1008 | Scarlett, J.A., AN INTRODUCTION TO PRINTED CIRCUIT<br>BOARD TECHNOLOGY, Electromechanical Publication<br>Limited, 1984 ("Scarlett 1") |

| APPLE-1009 | Scarlett, J.A., MULTILAYER PRINTED CIRCUIT BOARD<br>HANDBOOK, Electromechanical Publication Limited, 1985<br>("Scarlett 2")                                                                                              |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPLE-1010 | Farr, I. V., "SYNTHESIS AND CHARACTERIZATION<br>OF NOVEL POLYIMIDE GAS SEPARATION<br>MEMBRANE MATERIAL SYSTEMS," Dissertation<br>submitted to the Virginia Polytechnic Institute and State<br>University (Jul 26, 1999). |

| APPLE-1011 | U.S. Patent No. 5,714,405 ("Tsubosaki405")                                                                                                                                                                               |

| APPLE-1016 | Yu et al., "Surface characterizations of potassium-<br>hydroxide-modified Upilex-S® polyimide at an elevated<br>temperature," European Polymer Journal, Vol. 37, Issue 9,<br>September 2001, pp. 1791-1799               |

| APPLE-1019 | Yamamoto et al., <i>A Composite Electrical Insulation in</i><br>Superconducting Magnets, 44 Advances in Cryogenic Eng'g<br>(Materials) 239 (1998) ("Yamamoto")                                                           |

| APPLE-1020 | U.S. Patent No. 6,709,897 ("Cheng")                                                                                                                                                                                      |

| APPLE-1022 | U.S. Patent No. 11,071,207 ("Tuominen207")                                                                                                                                                                               |

| APPLE-1024 | U.S. Publication No. 2002/0159242 to Nakatani et al. ("Nakatani")                                                                                                                                                        |

| APPLE-1025 | Japanese Patent Publication No. 1999-191574 to Matsuda with Certified Translation ("Matsuda")                                                                                                                            |

| APPLE-1026 | U.S. Patent No. 4,068,022 to Glick ("Glick")                                                                                                                                                                             |

| APPLE-1028 | Simon Thomas, 3D-Integration: Trends and Opportunities – An Overview (Materials Research Society 2003)                                                                                                                   |

| APPLE-1029 | R. Kujala, et. al., Solderless Interconnection and Packaging<br>Technique for Embedded Active Components (IEEE 1999)                                              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPLE-1030 | U.S. Patent Publication No. 2001/0026010 to Horiuchi ("Horiuchi")                                                                                                 |

| APPLE-1031 | U.S. Patent No. 6,038,133 to Nakatani et al. ("Nakatani-II")                                                                                                      |

| APPLE-1032 | U.S. Patent No. 5,250,843 to Eichelberger ("Eichelberger")                                                                                                        |

| APPLE-1033 | International Patent Application WO1996012296 to Suwa et al. and Certified Translation ("Suwa")                                                                   |

| APPLE-1034 | U.S. Patent No. 7,609,527 ("Tuominen527")                                                                                                                         |

| APPLE-1105 | Exhibit 18 to Complaint for Patent Infringement –<br>Infringement Claim Chart for '816 Patent (February 5,<br>2024), Case No. 1-24-cv-00129 (WDTX), Document 1-17 |

#### II. QUALIFICATIONS AND BACKGROUND

4. I am currently a Professor Emeritus of Electrical and Computer Engineering at the University of Nevada, Las Vegas (UNLV). My curriculum vitae is provided (as Appendix A).

5. I have been teaching electrical engineering at UNLV since 2012. Prior to this position, I was a Professor of Electrical and Computer Engineering at Boise State University from 2000. Prior to my position at Boise State University, I was an Associate Professor of Electrical Engineering between 1998 and 2000 and Assistant Professor of Electrical Engineering between 1993 and 1998 at the University of Idaho. I have been teaching electrical engineering since 1991.

6. I received a Bachelor of Science and Master of Science degrees in Electrical Engineering from UNLV, in 1986 and 1988, respectively. In 1993, I also received a Ph.D. in Electrical Engineering from the University of Nevada, Reno. From 1985 to 1993, I worked for EG&G Energy Measurements and the Lawrence Livermore National Laboratory designing nuclear diagnostic instrumentation for underground nuclear weapon tests at the Nevada Test Site. During this time, I designed, and oversaw the fabrication and manufacture of over 30 electronic and electronic-optic instruments including high-speed cable and fiber-optic receiver/transmitters, PLLs, frame and bit-syncs, data converters, streak-camera sweep circuits, Pockels cell drivers, micro-channel plate gating circuits, and analog oscilloscope electronics.

7. From 1997 to 1999, I served as a Consultant for Tower Semiconductor, in the design of CMOS integrated circuit cells for various modem chips, interfaces, and serial buses, including charging circuits based upon power up-down circuits using an MOS or bandgap reference, pre-amplifiers, and comparators. I was also a Senior Designer at Micron Technology from 1994 to 2008, working on the development of Dynamic Random Access Memory (DRAM) semiconductor integrated circuit chips, CMOS Image Sensors (CISs), and power supply design. My more recent industry experience includes working with

Freedom Photonics on the integration, fabrication, and design of optoelectronics with CMOS integrated circuits, including the design of compact optical transceiver for range finding applications, Geiger mode SiGe receiver for long-range communications, and packaging and testing of numerous chips fabricated in both CMOS and SiGe technologies. I have worked as a consultant at other companies designing electronic circuits, including Sun, Oracle, Contour Semiconductor, Lockheed-Martin, and OmniVision.

8. I have taught courses in integrated circuit design (analog, digital, mixed signal, memory circuit design, etc.), linear circuits, microelectronics, communication systems, power electronics, and fiber optics. I have been the main advisor to over 100 Master's and Doctoral students.

9. I am the author of several books covering the area of integrated circuit design including: DRAM Circuit Design: Fundamental and High-Speed Topics (two editions), CMOS Circuit Design, Layout, and Simulation (four editions), and CMOS Mixed-Signal Circuit Design (two editions). I have also authored, or coauthored, more than 100 papers and presentations in the areas of electronic circuit design. I am the named inventor on over 150 granted U.S. patents.

10. I have received numerous awards for my work, including the Frederick Emmons Terman (the "Father of Silicon Valley") Award. The Terman

Award is bestowed annually upon an outstanding young electrical/computer engineering educator in recognition of the educator's contributions to the profession.

11. I am a Fellow of the IEEE for contributions to memory circuit design.I have also received the IEEE Circuits and Systems Education Award (2011).

12. I have received the President's Research and Scholarship Award (2005), Honored Faculty Member recognition (2003), and Outstanding Department of Electrical Engineering Faculty recognition (2001), all from Boise State University.

13. I have also received the Tau Beta Pi Outstanding Electrical and Computer Engineering Professor award four of the years I have been at UNLV.

14. In forming my opinions, I have relied on my knowledge and experience in designing, developing, and researching integrated circuit packaging and my knowledge of electrical circuit design and fabrication and electrical engineering fundamentals. I am not an attorney and offer no legal opinions, but in the course of my work, I have had experience studying and analyzing patents and patent claims from the perspective of a person having ordinary skill in the art.

#### III. RELEVANT LEGAL STANDARDS

15. I have been asked to provide my opinions as to whether claims 1-14 of the '816 Patent would have been obvious to a person of ordinary skill in the art

as of the earliest claimed priority date of the '816 patent, which I understand is September 18, 2003 ("Critical Date").

16. I am an engineer by training and profession. The opinions I express in this declaration involve the application of my technical knowledge and experience to the evaluation of certain prior art with respect to the '816 patent. In addition, I understand that the following legal principles apply.

17. It is my understanding that, in determining whether claims of the '816 patent are obvious in this proceeding, the claim terms are generally given their ordinary and customary meaning as understood by a person of ordinary skill in the relevant art. A person of ordinary skill in the art would read the claim terms in the context of the entire patent specification in which they appear, as well as the prosecution history of the patent.

18. It is my understanding that a claim is unpatentable under 35 U.S.C. § 103 if the claimed subject matter as a whole would have been obvious to a person of ordinary skill in the art at the time of the alleged invention. I also understand that an obviousness analysis takes into account the scope and content of the prior art, the differences between the claimed subject matter and the prior art, and the level of ordinary skill in the art at the time of the invention.

19. In determining the scope and content of the prior art, it is my understanding that a reference is considered relevant prior art if it falls within the field of the inventor's endeavor. In addition, a reference is prior art if it is reasonably pertinent to the particular problem with which the inventor was involved. A reference is reasonably pertinent if it logically would have commended itself to an inventor's attention in considering his problem. If a reference relates to the same problem as the claimed invention, that supports use of the reference as prior art in an obviousness analysis.

20. To assess the differences between prior art and the claimed subject matter, it is my understanding that 35 U.S.C. § 103 requires the claimed invention to be considered as a whole. This "as a whole" assessment involves showing that one of ordinary skill in the art at the time of invention, confronted by the same problems as the inventor and with no knowledge of the claimed invention, would have selected the elements from the prior art and combined them in the claimed manner.

21. It is my further understanding that several rationales may be applied for combining references or modifying a reference to show obviousness of claimed subject matter. These rationales include: combining prior art elements according to known methods to yield predictable results; simple substitution of one known

element for another to obtain predictable results; a predictable use of prior art elements according to their established functions; applying a known technique to a known device (method or product) ready for improvement to yield predictable results; choosing from a finite number of identified, predictable solutions, with a reasonable expectation of success; and some teaching, suggestion, or motivation in the prior art that would have led one of ordinary skill to modify a prior art reference or to combine prior art teachings to arrive at the claimed invention.

#### IV. TECHNOLOGY BACKGROUND

#### A. Semiconductor Components for Multi-chip Modules

22. Persons of Ordinary Skill In The Art (POSITAs) have continuously looked for solutions to provide multiple component integration into electronic modules to provide higher levels of system functionality without added signal delay and power dissipation in order to integrate components (such as transistors) in integrated circuits in accordance with Moore's law. APPLE-1036, Abstract. As Simon Thomas explained, "[t]he growth of the semiconductor industry has historically depended on the integration of more components on a chip through transistor and interconnects scaling and manufacturing technology." Thomas describes that functionality has increased through "System-on-Chip (SoC) and System in Package (SiP) approaches." *Id*.

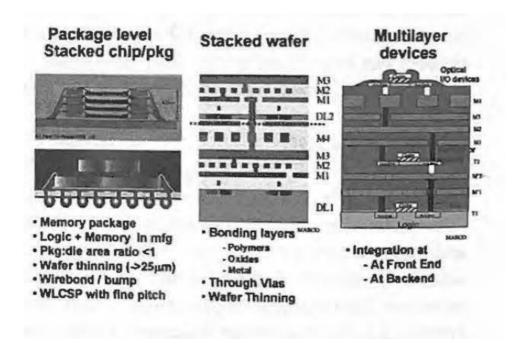

In addition, the increasing drive to integrate diverse component technologies for enhanced SoC functionality, presents a multitude of technical and business challenges. For example, a single chip SoC for a cell phone handset could require GaAs, MEMS, digital, analog, power, and passives technologies. RF circuits integrated with microprocessor in a 3D format, to facilitate wireless communication, has attracted major interest. Another motivation for 3D is the need to reduce footprint of the packaged device, especially for portable applications. There are multiple technology approaches for 3-D integration, currently at varying levels of maturity and each with its own unique strengths and issues. These approaches include [Fig: 1]: - Stacked chips or stacked packages - Stacked wafers through wafer bonding - Device fabrication in multiple planes on the same wafer.

APPLE-1036, 2.

Fig: 1. Schematic of 3D integration schemes.

#### **APPLE-1036, 2**

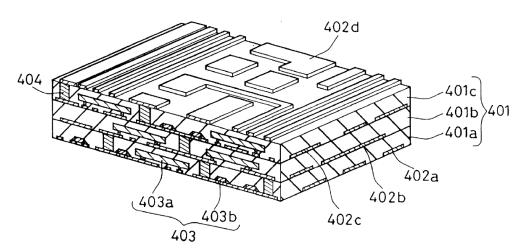

23. Nakatani-II exemplifies how stacking multiple wafers on top of each other was a well-known technique for achieving multiple component integration in a module. For example, Nakatani-II's Figure 4 shows a three-layered "built-in module":

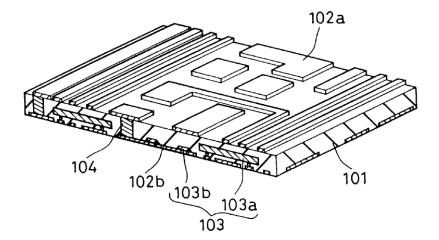

Referring to FIG. 4, the circuit component built-in module 400 in Embodiment 4 includes an insulating substrate 401 comprising insulating substrates 401a, 401b and 401c, wiring patterns 402a, 402b, 402c and 402d formed on one principal plane and in the internal portion of the insulating substrate 401, a circuit component 403 arranged in the internal portion of the insulating substrate 401 and connected to the wiring patterns 402a, 402b or 402c, and an inner via 404 for electrical connection between the wiring patterns 402a, 402b, 402c and 402d.

APPLE-1039, 11:12-22.

FIG. 4

#### **APPLE-1039, FIG. 4**

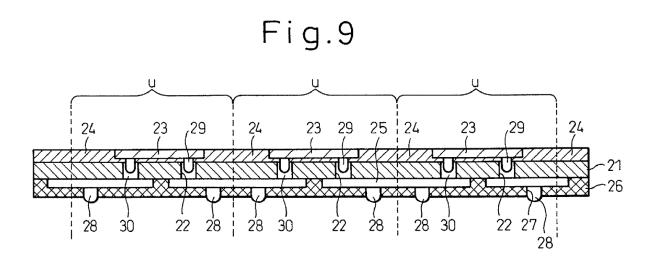

24. "A plurality of semiconductor devices... may be stacked in layers... to form a thin multilayer semiconductor device" in U.S. Patent Application Publication No. 2001/0026010 to Horiuchi et al. ("Horiuchi"). APPLE-1038, [0105]. Horiuchi describes a method including producing an initial structure containing multiple electrical components which are then "cut into semiconductor package units 'u'... to obtain individual semiconductor devices 20." Id., [0101], [0115], [0127], [0143], [0154]. For example, Horiuchi's Figure 9 (reproduced below) shows semiconductor elements 23 which are bonded and mounted to the top surface of the tape substrate 21 "by heating the semiconductor elements 23 to a temperature near the melting point of the low melting point metal 30 and pushing the connection terminals 29 into the low melting point metal 30 in the through holes 22." Id., [0094]. "A sealing resin layer 24 covering the top surface of the tape substrate 21" is then ground and polished to a predetermined thickness. Id., [0097]-[0099]. After the grinding and polishing, the external connection terminals 28 are formed and the "assembly is cut into semiconductor package units 'u' at the positions shown by the broken lines in FIG. 9 to obtain individual semiconductor devices." Id., [0100]-[0101].

**APPLE-1038, FIG. 9**

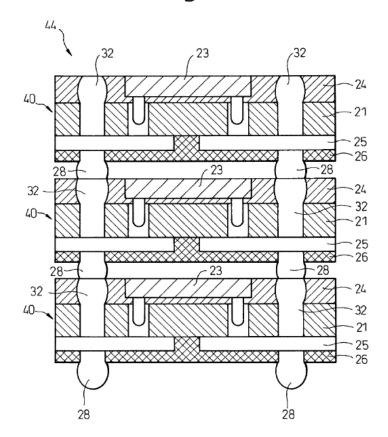

# 25. Following the cutting procedure, Horiuchi's cut semiconductor

devices "may be stacked in layers as shown in FIG. 11 to form a thin multilayer

semiconductor device 44" by:

connecting the top ends of the low melting point metal conductors 32 of a bottom semiconductor device 40 and the bottom ends of the external connection terminals 28 of a top semiconductor device 40, a single semiconductor device 4 comprised of an integral circuit including a plurality of semiconductor elements 23 (in this example, three) in a multilayer structure is formed.

APPLE-1038, [0105].

Fig.11

**APPLE-1038, FIG. 11**

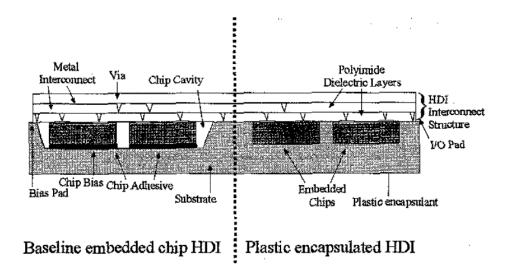

26. As Thomas notes, "[a]nother interesting concept of multilayer device integration is to build active devices within an interconnect level." APPLE-1036, 6-7. This type of technology had "become increasingly attractive" during the 90's. APPLE-1029, 1. For example, in 1999, A. Kujala, R. Tuominen, and J.K. Kivilahti, explained that, "General Electric (GE) introduced high density interconnection technology for embedded chips. HDI technology is a 'chip first' solution where active components are placed in cavities formed in a ceramic or

embedded into plastic encapsulant." APPLE-1037, 1. As shown below in Figure 2, the chips are interconnected through laser ablated vias. *Id.*, 2. "The HDI technology enables the fabrication of complex [multi-chip modules] with a very high packaging density and low interconnect impedance" while providing "good protection both mechanically and chemically." *Id*.

Fig. 2 Schematic presentation of embedded HDI chips [5].

#### **APPLE-1037, FIG. 2**

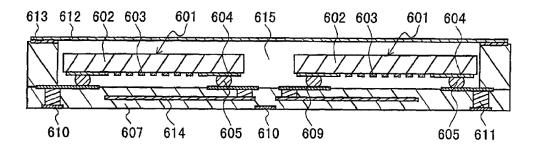

27. For example, Nakatani, Eichelberger, Suwa, and Nakatani-II show mounting multiple chips in a single layer. Specifically, due to the increased demand for smaller-sized higher-density circuit boards, Nakatani discloses "at least two electric elements (203) such as semiconductor chips or surface acoustic wave devices ... mounted on wiring patterns." APPLE-1007, Abstract, [0003], [0017] ("In FIG. 7, numeral 601 denotes surface acoustic wave devices…"), [0127]; *see also infra* §X.A. Nakatani's "first wiring patterns 609 and [] metal bumps 605 are electrically connected" using "heat and ultrasonic wave[s]" to melt the metal bumps 605 for the connection of the components (surface acoustic wave devices 601) with the circuit board. *Id.*, [0016], [0020], [0125]. Nakatani describes that by including a plurality of components in a single layer, the semiconductor package's thickness is improved by having the multiple thin chips successfully mounted on a thinner substrate. *Id.*, [0011]-[0012].

# FIG . 7 PRIOR ART

#### **APPLE-1007, FIG. 7**

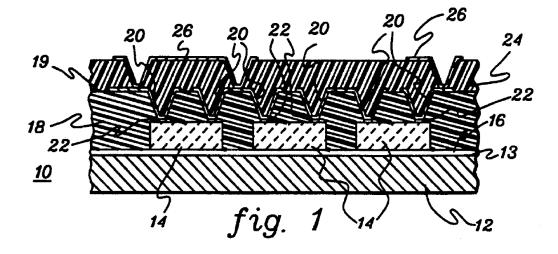

28. Similarly, U.S. Patent No. 5,250,843 to Eichelberger discloses a "multichip integrated circuit package comprises a substrate having a flat upper surface to which is affixed one or more integrated circuit chips having

interconnection pads." APPLE-1040, Abstract. As shown below in Figure 1, Eichelberger's multichip module includes multiple semiconductor components 14 arranged in one single layer. Eichelberger's multichip module structure has high I/O capacity with optimal heat removal, has been optimized for speed, and has the ability to incorporate an assortment of components of varying thickness and functions into the module. *Id.*, 1:17-27.

**APPLE-1040, FIG. 1**

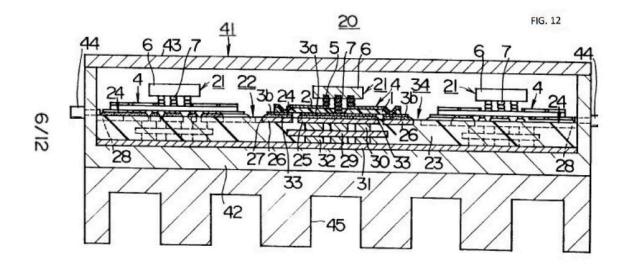

29. International Patent Application WO1996012296 to Suwa et al. ("Suwa") also discloses a multi-chip module. *See* APPLE-1041. Suwa's multi-chip module (MCM) 20 is provided with a plurality of chip assemblies 21 "in which the IC chip 6 is facedown-bonded to the tape 4." *Id.*, 12. "A plurality (four in the illustrated example) of the chip assemblies 21 is used in the MCM 20, and

passive elements and active elements are incorporated into each chip assembly 21." *Id.*, 12-13.

**APPLE-1041, FIG. 12**

30. Suwa describes that since the IC chips 6, are "mounted on the wiring board 22 via the tape 4 with a thickness of approximately 50  $\mu$ m, the level difference between the wiring board 22 and the IC chip 6 can be extremely minimalized, and therefore a drop in the impedance can be suppressed when a high-speed signal is transmitted, and impedance matching of the highspeed signal line 2b can be easily ensured." APPLE-1041, 16. Furthermore, Suwa describes that since "IC chip 6 is surface-mounted in the wiring board 22 in the chip assembly 21, no cavity needs to be formed in the wiring board 22, and therefore

the manufacturing costs of the wring board 22 as well as of the MCM 20 can be reduced." *Id.*

31. As I explained above, Nakatani-II also exemplifies multiple components in a single insulating substrate layer. As shown in Figure 1, Nakatani-II's circuit components 103 are "connected to the wiring pattern 102b and arranged in the insulating substrate 101, and an inner via 104 for electric connection between the wiring patterns 102a and 102b." APPLE-1039, 6:67-7:3.

100

FIG. 1

#### **APPLE-1039, FIG. 1**

32. In summary, it was well-recognized by POSITAs to mount a plurality of chips on a substrate, and further to stack a plurality of chip modules accordingly.

### **B.** Bonding Techniques

33. Preparation of a semiconductor package or chip requires that components be electrically connected to wiring patterns on a printed circuit board or other substrate, so that the package or chip can be supplied with power and be grounded, as well as connecting the package or chip to other components. APPLE-1022, 1 ("A printed circuit board is a piece of plastic material on which electronic components can be mounted for mechanical support, and which also electrically interconnects all the components it supports by means of a pattern of metal tracks on its outer surfaces and sometimes on inside layers"). By the Critical Date, a variety of techniques for bonding components to wiring of printed circuit boards were well known and in use, including solderless techniques including ultrasonic bonding and thermocompression. See e.g., APPLE-1037 (1999 article in IEEE reporting on "Solderless Interconnection and Packaging Technique for Embedded Active Components"). The '816 patent does not purport to have invented these techniques, and indeed, ultrasonic and thermocompression bonding techniques (*i.e.*, "solderless techniques") were well-known years before the filing date of the '816 patent. Id.; APPLE-1001, 6:46-48 ("Methods and devices for creating

ultrasound joints (ultrasonic bonding) are commercially available."), 6:63-65

(Methods and devices for making thermo-compressed joints (thermo-compression

bonding) are also commercially available").

# i. Ultrasonic Bonding

34. The Tuominen patent offers the following description of ultrasonic

bonding:

The ultrasonic method then refers to a method, in which two pieces containing metal are pressed against each other while vibration energy at an ultrasound frequency is brought to the area of the joint. Due to the effect of the ultrasound and the pressure created between the surfaces to be joined, the pieces to be joined are bonded metallurgically. Methods and equipment for ultrasonic bonding are commercially available. Ultrasonic bonding has the advantage that a high temperature is not required to form a bond.

APPLE-1034, 6:41-49.

35. Ultrasonic bonding techniques combine ultrasonic vibrations and heat or pressure to bond two metal components to one another. For example, Matsuda describes a technique that combines ultrasonic methods with thermocompression. Matsuda describes that electrodes 4 of a semiconductor chip are aligned with metal bumps 5 (*e.g.*, Ni or Au) formed on a substrate and then the pieces are "subjected to pressure by a bonding tool while applying ultrasonic vibrations and heat." APPLE-1009, [0007], [0006], [0012]. "The bumps 5 are deformed to form an Au/Al alloy on the contact surface, and the chip electrodes 4 and bumps 5 are

thermocompressed." Id., [0007], [0013], FIGS. 2A-B.

### ii. Thermo-compression Bonding

36. Similarly, the '816 patent gives the following description related to

thermo-compression bonding methods:

The term thermo-compression method refers in turn to a method, in which two pieces containing metal are pressed against each other while thermal energy is brought to the area of the joint. The effect of the thermal energy and the pressure created between the surfaces to be joined cause the pieces to be joined to be bonded metallurgically. Methods and equipment for thermo-compression bonding are also commercially available.

*Id.*, 6:58-65.

37. Glick explains that " [t]hermocompression bonding is a solid-phase bonding technique which forms the bond between two members by inducing a suitable amount of material flow in one or both members." APPLE-1020; 3:33-36. "[M]aterial flow [between the two members] is induced by the application of heat and pressure, which are maintained for a suitable length of time so that adhesion takes place without the presence of a liquid phase." *Id.*, 3:36-39.

# V. PERSON OF ORDINARY SKILL IN THE ART

38. It is my understanding that when interpreting the claims of the '816 patent I must do so based on the perspective of the POSITA. For purposes of my

analysis in this declaration, as noted above, I have been asked to assume that the priority date of the '816 patent is September 18, 2003 ("Critical Date"). I understand that the factors considered in determining the ordinary level of skill in a field of art include the level of education and experience of persons working in the field; the types of problems encountered in the field; the teachings of the prior art, and the sophistication of the technology at the time of the alleged invention. I understand that a POSITA is not a specific real individual, but rather is a hypothetical individual having the qualities reflected by the factors above. I understand that a POSITA would also have knowledge from the teachings of the prior art, including the art cited below.

39. Taking these factors into consideration, it is my opinion that one of ordinary skill in the art would have had a Bachelor's degree in electrical engineering, materials science, applied physics, or a related technical field, and 2-3 years of experience in the research, design, development, or testing of circuit board or microcircuit components, or the equivalent. Additional graduate education could substitute for professional experience, or additional professional experience could substitute for formal education.

40. I possessed the qualifications of a POSITA since the Critical Date of the '816 patent, and long before.

### VI. OVERVIEW OF THE SUBJECT PATENT US 11,716,816, "THE '816 PATENT"

41. The '816 patent is titled Method for manufacturing an electronic module and electronic module, filed as U.S. Application No. 17/364,593 (the " '593 application"). It was filed on June 30, 2021 as a continuation of U.S. Application No. 16/788,701 (filed on February 12, 2020, which is a Continuation of U.S. patent application Ser. No. 14/580,257, filed on Dec. 23, 2014, which is a Continuation-in-Part of U.S. patent application Ser. No. 10/572,340, filed on Sep. 15, 2004). APPLE-1001, Cover. Although not listed on the cover of the '816 patent, the U.S. priority application was filed as a U.S. national stage entry of PCT/FI2004/000053 (filed September 15, 2004). APPLE-1002, 53. The '816 application also claims priority to Finnish Application No. 20030167, filed on April 2, 2003. *Id*.

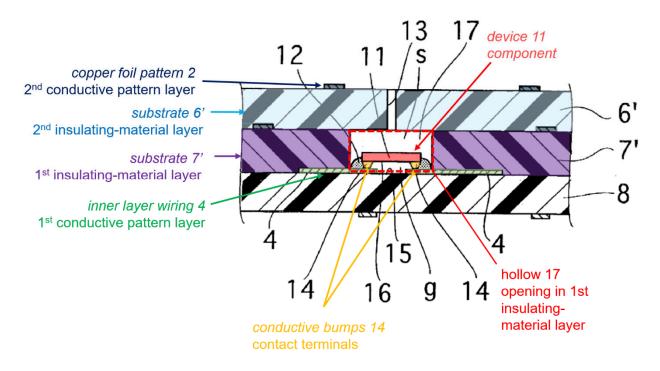

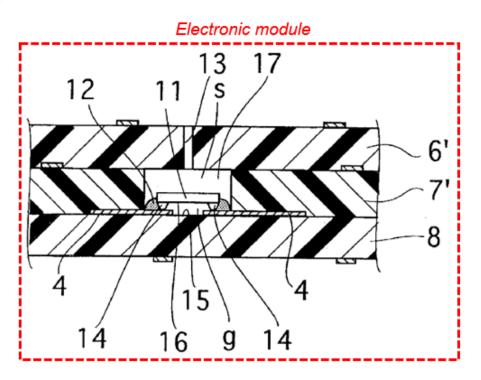

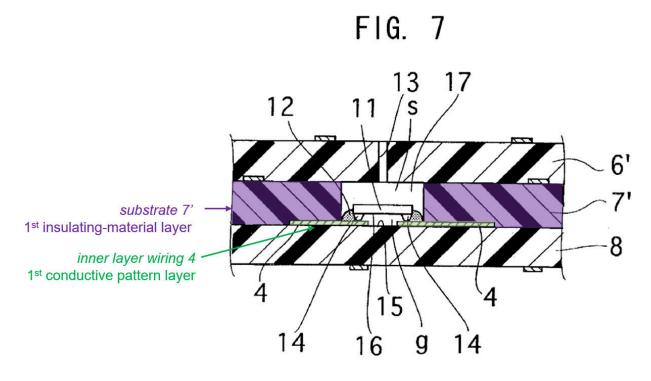

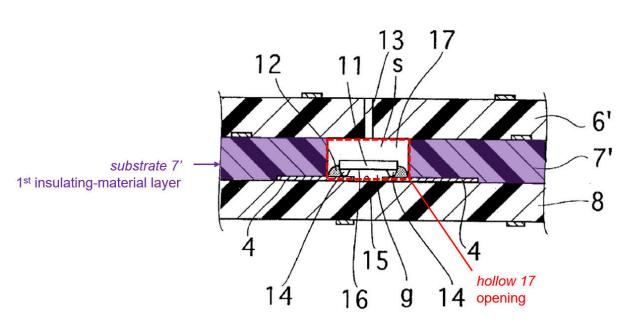

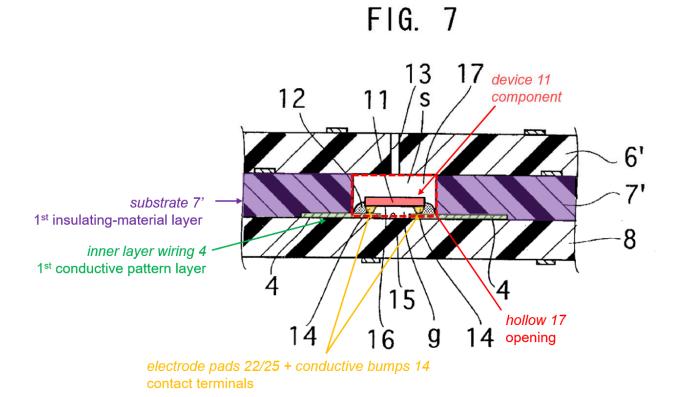

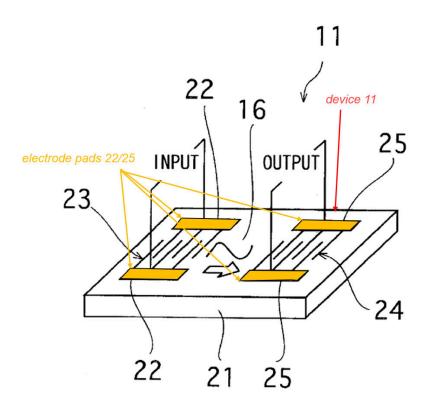

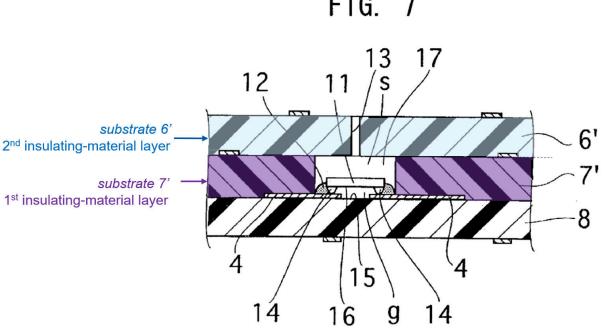

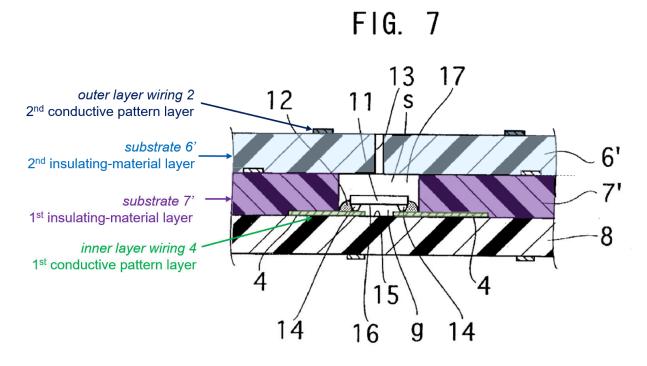

42. The '816 Patent generally describes techniques for fabricating "electronic modules" containing a semiconductor chip, or other component, embedded in an installation base such as a circuit board. APPLE-1001, 1:28-33. The specification explains that "[e]mbodiments of the invention are based on commencing manufacture [of the electronic module] from an insulating board, which is surfaced on at least one side with a conductive layer." APPLE-1001, 3:21-23. "After this, a recess or opening is made in the insulation, which opens onto one surface of the board, but does not penetrate the conductive layer on the opposite surface of the board." *Id.*, 3:23-26. "A component is attached to the recess or opening and electrical contacts are formed between the conductive layer and the contact areas, or contact protrusions of the component." *Id.*, 3:26-29. "After the attachment of the component, conductive patterns are formed from this conductive layer, which become part of the circuit-board structure, or other electronic module." *Id.*, 3:29-32; *see also id.*, 3:16-4:9 (discussing alleged advantages of the designs disclosed in the '816 Patent).

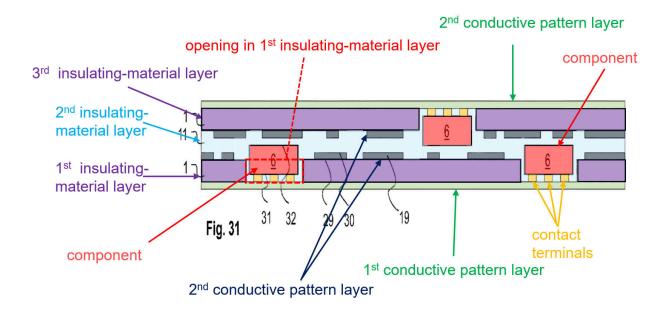

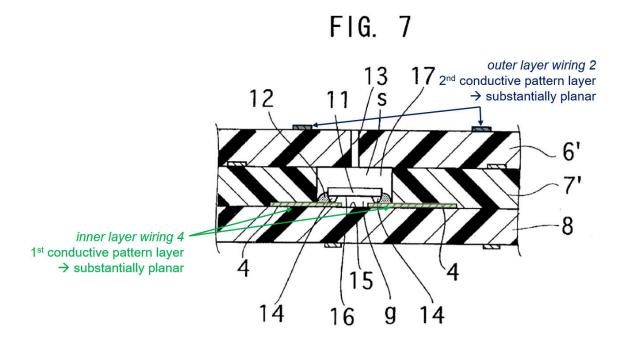

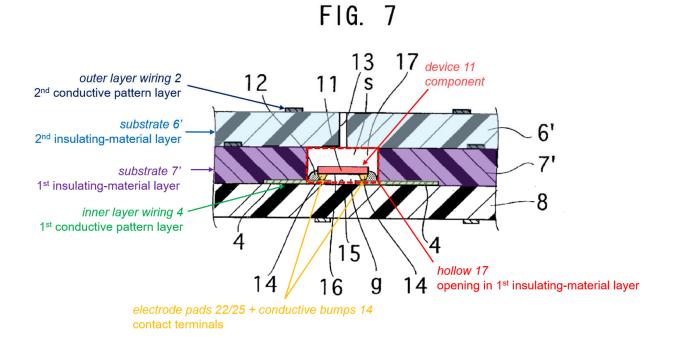

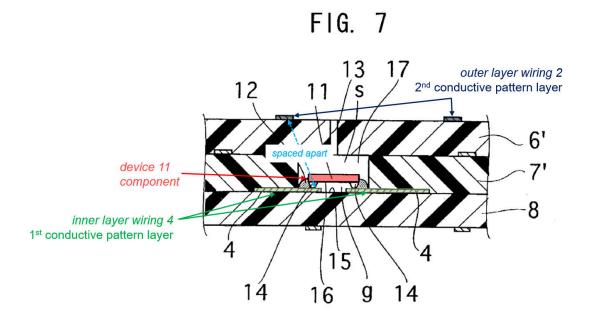

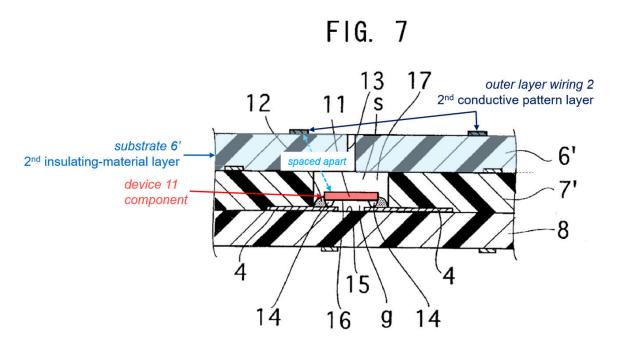

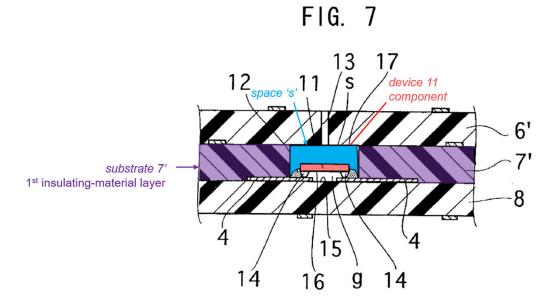

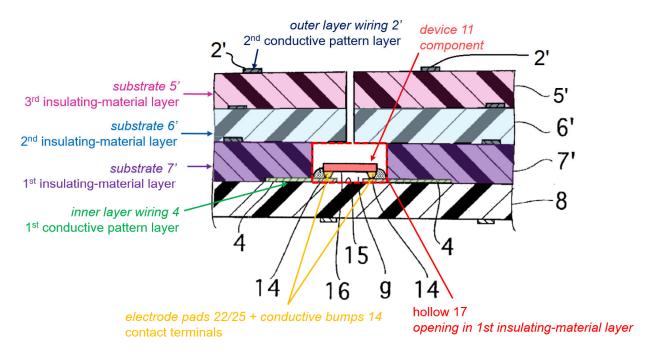

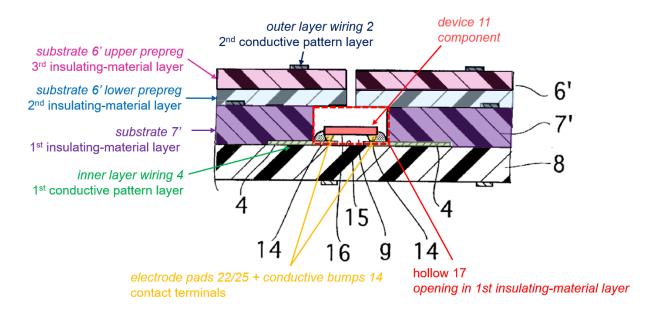

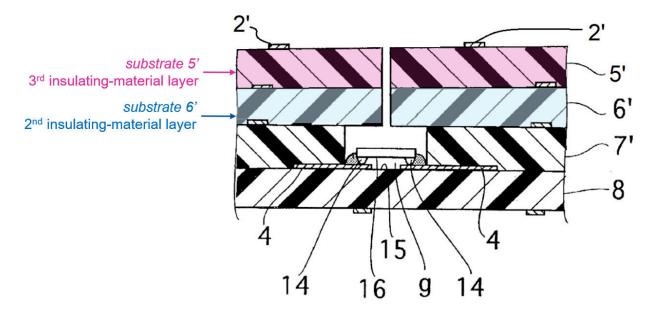

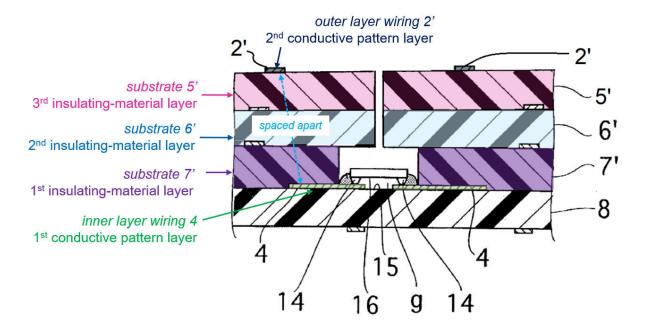

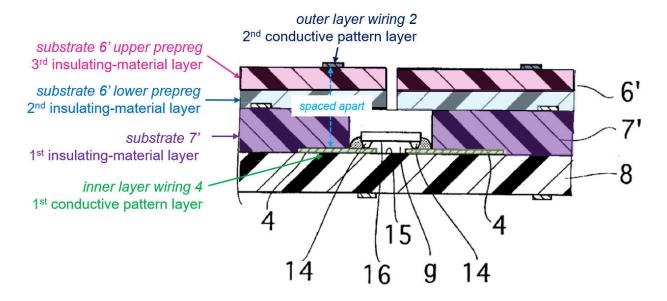

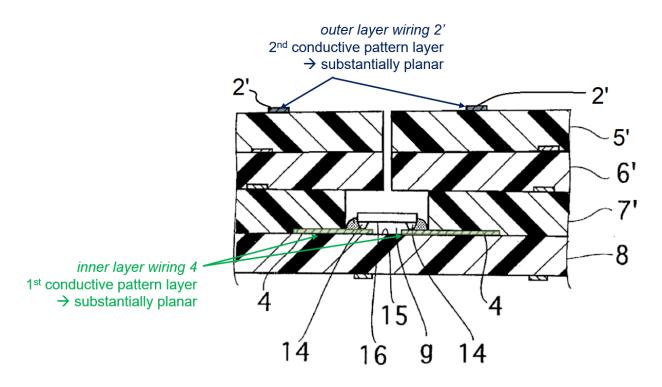

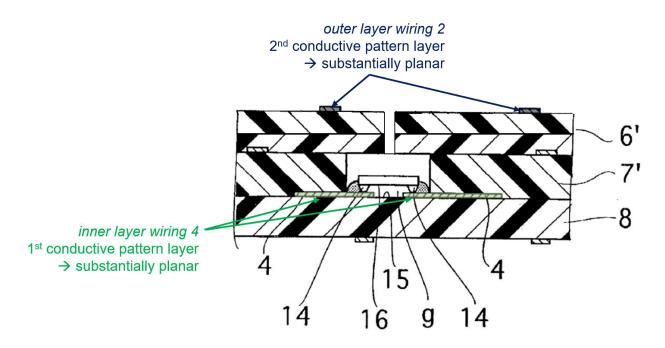

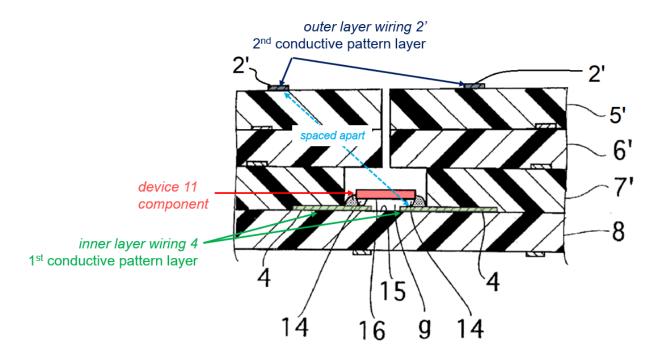

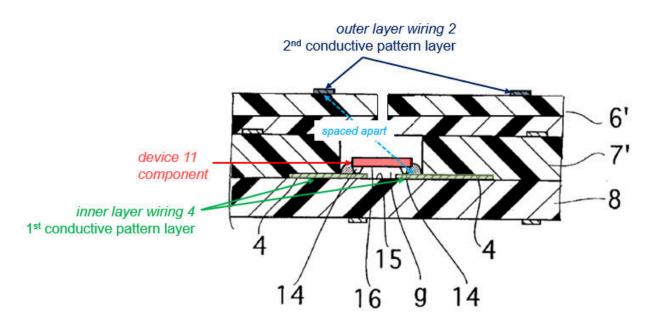

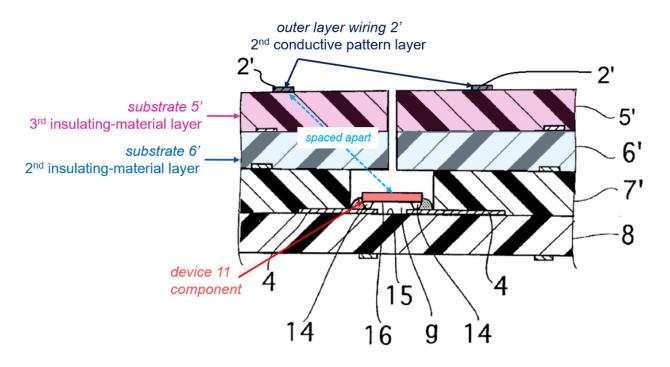

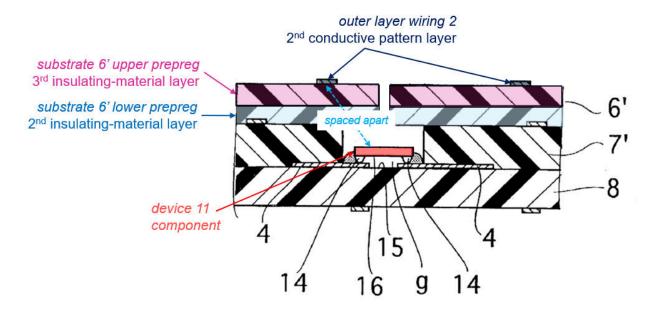

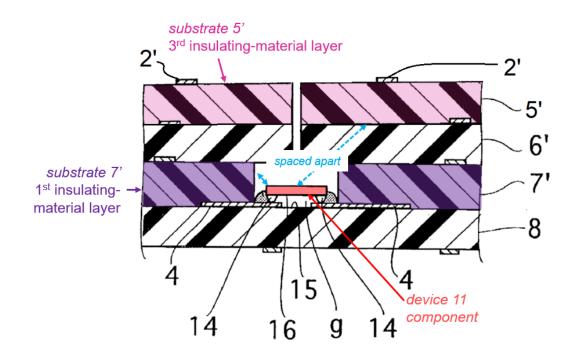

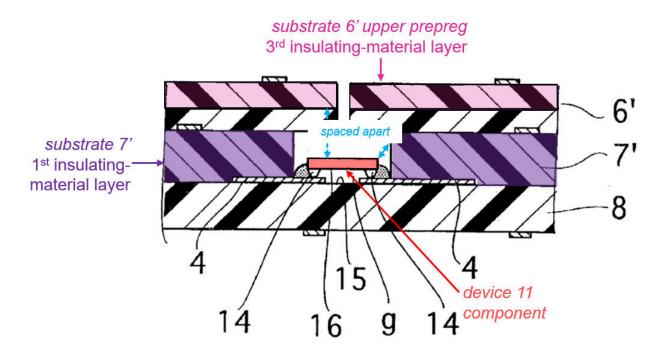

43. By way of example, FIG. 31 depicts one embodiment of an electronic module disclosed in the '816 Patent:

#### APPLE-1001, FIG. 31 (annotated)<sup>1</sup>

44. As shown above, the disclosed module includes a first insulating material layer 1 toward a bottom portion of the module, a second insulating material layer 11 around a middle portion of the module, and a third insulating material layer 1 toward a top portion of the module. APPLE-1001, 13:3-61; *see also id.*, 5:20-26, FIGS. 30-31. First and second conductive pattern layers are formed on opposite sides of the first and third insulating material layers, respectively. *Id.* The first and third insulating material layers further include openings sized to receive components 6 (*e.g.*, semiconductor chips), thereby permitting electrical connection of the contact terminals of the components 6 to the first or second conductive pattern layers. *Id.*

#### VII. PROSECUTION HISTORY OF THE '816 PATENT

45. I have reviewed the file history of U.S. Application No. 17/364,593 ("the '593 application), from which the '816 patent issued.

46. I understand that the application was rejected only one time during prosecution. In the only Office Action issued during prosecution of the

<sup>&</sup>lt;sup>1</sup> While the metal conductive layers (shaded green) are shown as continuous surfaced material in FIG. 30, they are later patterned to form the first and second conductive pattern layers according to the processes described in the '816 Patent. APPLE-1001, 13:3-61; *see also id.*, FIGS. 36-38.

application, the Examiner The office action rejected each of the independent claims and most dependent claims pending at the time as anticipated by Cheng (APPLE-1020). APPLE-1002, 19-25. Two dependent claims were identified as reciting allowable subject matter, however. APPLE-1002, 25-26. These claims recited that "the first conductive pattern layer and the second conductive pattern layer are each substantially planar." *Id.* The applicant responded to the action by amending the independent claims to incorporate language based on the features recited in the allowable dependent claims:

1. (currently amended) An electronic module, comprising:

a first conductive pattern layer, and a first insulating-material layer arranged on at least one surface of the first conductive pattern layer;

at least one opening in the first insulating-material layer that extends through the first insulating-material layer;

a component comprising contact terminals, the component being arranged at least partially within the at least one opening, the contact terminals electrically connected to the first conductive pattern layer;

a second insulating-material layer disposed on the first insulating-material layer; and a second conductive pattern layer spaced apart from the first conductive pattern layer by at least the first and second insulating-material layers,

wherein the first conductive pattern layer and the second conductive pattern layer are each substantially planar.

APPLE-1002, 2-3; generally id., 11-16.

47. Following the applicant's response, the examiner agreed to allow the application in a notice of allowance dated March 13, 2023. APPLE-1002, 3-10. As Grounds 1A-2 of this Petition demonstrate, however, the '816 Patent never should have been allowed. The conventional features recited in the Challenged

Claims—including "substantially planar" conductive pattern layers—were all well known in the prior art before the alleged invention, and the claims fail to recite these features in any innovative or non-obvious arrangement.

48. However, as I will discuss below, all features recited in the Challenged Claims are disclosed in one or more of Tsubosaki, Oya, and Shugg, none of which were considered by the Office or cited in the Office Action, and the claimed combinations of these features would have been obvious before the Critical Date.

#### **VIII. CLAIM CONSTRUCTION**

49. I do not believe that any term requires explicit construction. I understand that claim terms in an *inter partes* review proceeding are given their plain and ordinary meaning in light of the specification and file history. For purposes of my analysis in this declaration, I have applied claim interpretations consistent with the patent owner's allegations of infringement against Apple in the parallel district court proceeding. *See* APPLE-1105.

50. I reserve the right to offer opinions on any claim constructions proposed in this proceeding or to offer opinions on additional constructions that are raised in the parallel district court proceeding.

# IX. OVERVIEW OF CONCLUSIONS FORMED

51. This expert Declaration explains the conclusions that I have formed based on my analysis. To summarize those conclusions:

- Based upon my knowledge and experience and my review of the prior art publications listed above, I believe that claims 1-14 of the '816 patent are rendered obvious by Tsubosaki010 in view of Tsubosaki405.

- Based upon my knowledge and experience and my review of the prior art publications listed above, I believe that claims 1-14 of the '816 patent are rendered obvious by Tsubosaki010.

- Based upon my knowledge and experience and my review of the prior art publications listed above, I believe that claims 1, 3-4, 6-8, 10-11, and 13-14 of the '816 patent are rendered obvious by Oya in View of Shugg.

# X. GROUND 1A – TSUBOSAKI010 IN VIEW OF TSUBOSAKI405 RENDERS OBVIOUS CLAIMS 1-14

# A. Tsubosaki010 Overview (APPLE-1005)

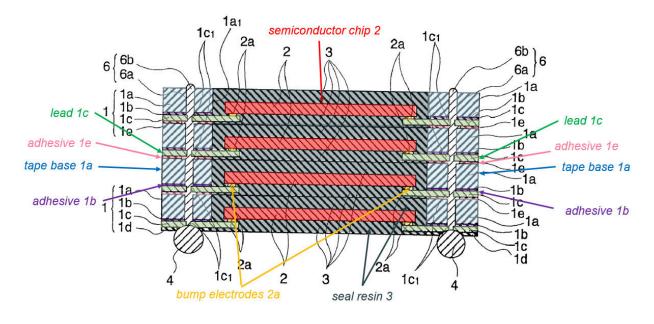

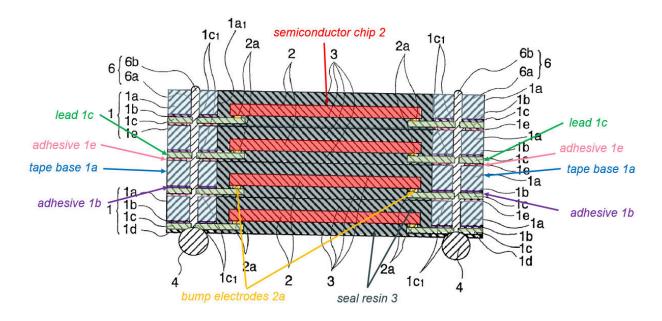

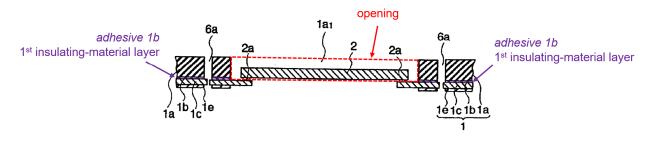

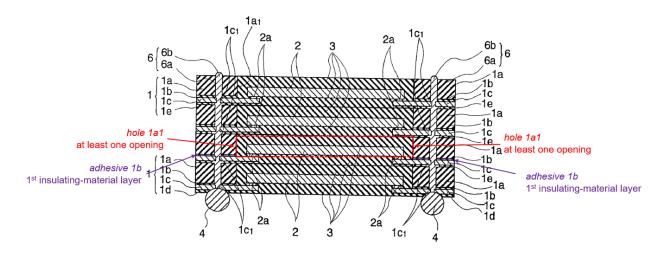

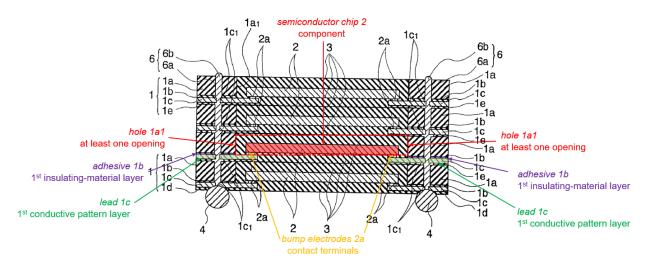

52. Tsubosaki010's disclosure "relates generally to semiconductor devices and manufacturing methodology thereof, and more particularly to technologies usefully applicable to high-density mountable semiconductor devices with tape carrier package (TCP) structures along with fabrication methods thereof." Tsubosaki010, ¶[0011]. "The TCP is a package structured including a tape carrier having a plurality of conductive leads formed thereon in a repeated pattern, wherein a semiconductor chip is placed on or in the tape carrier with its electrode pads lamination-contacted with corresponding ones of the carrier leads for electrical interconnection therebetween, the semiconductor chip being sealed by a sealing resin or the like." Tsubosaki010, ¶[0003]. For example, a unitary TCP can include "a semiconductor chip 2 [] disposed within a device hole [1a1] as formed in a tape base material 1a of a tape carrier 1, which chip is less in thickness than the tape base material 1a." Tsubosaki010, Abstract; *see also id.*, ¶[0062].

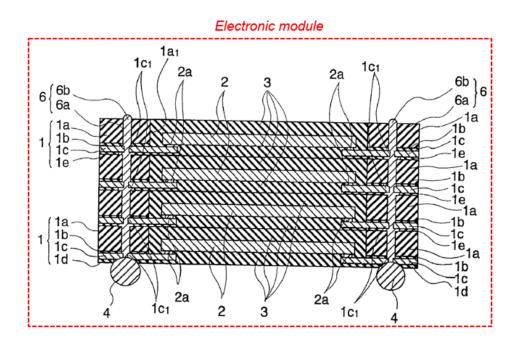

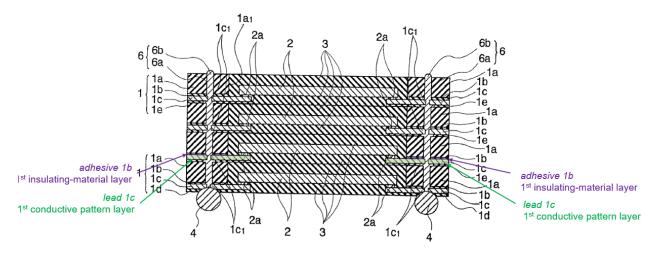

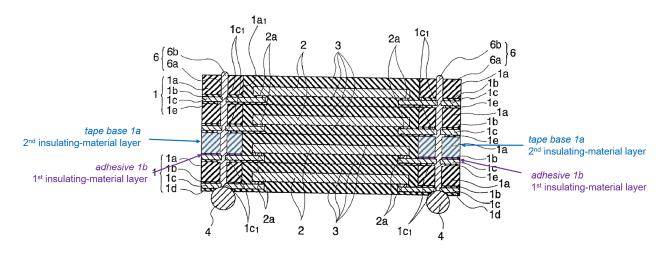

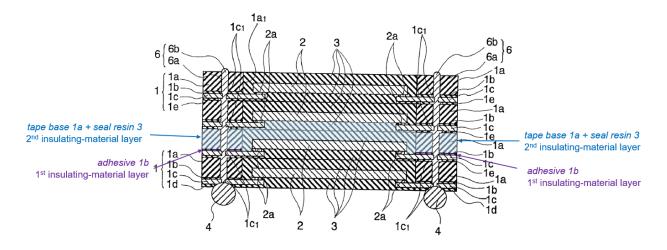

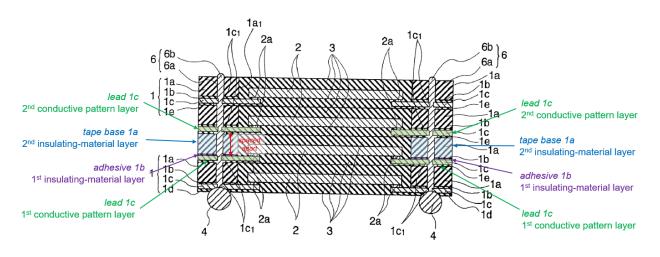

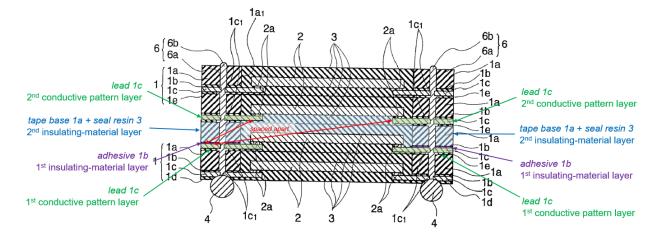

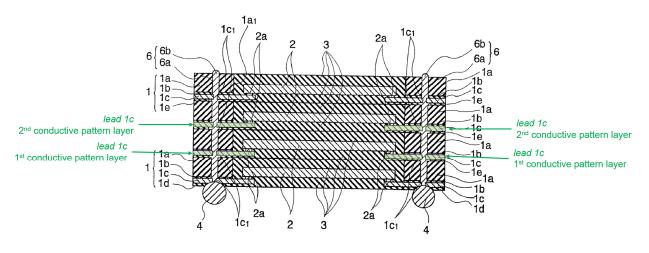

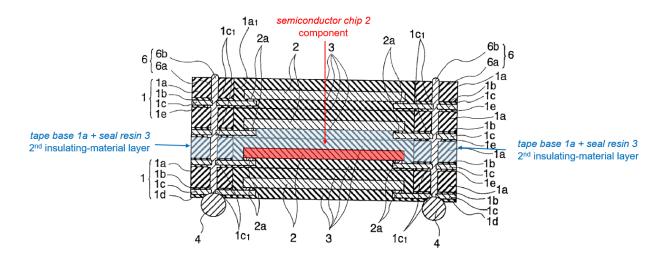

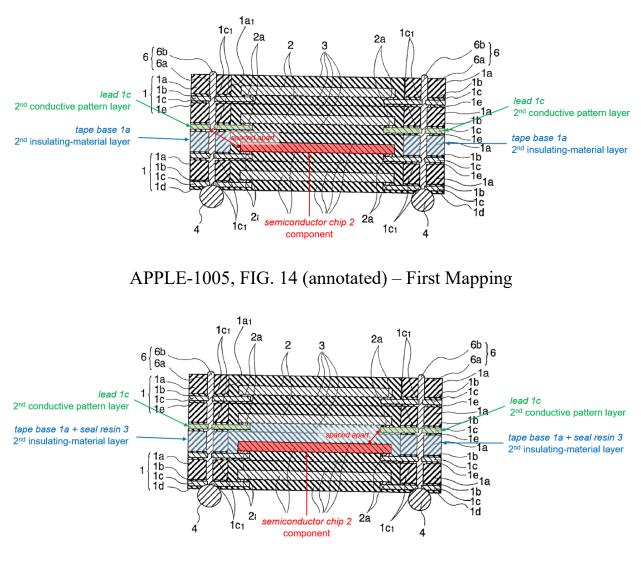

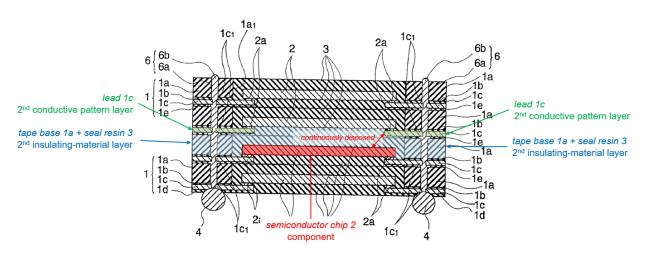

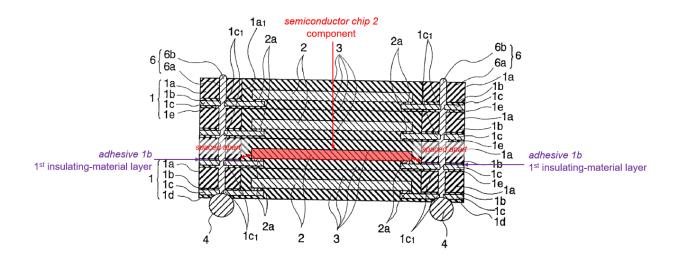

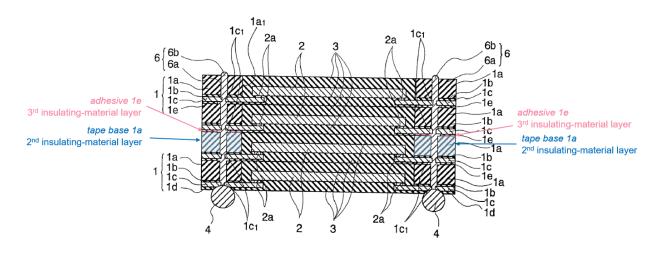

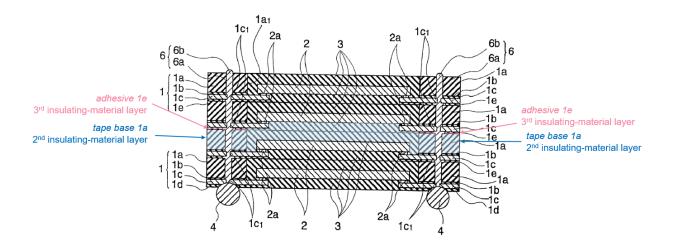

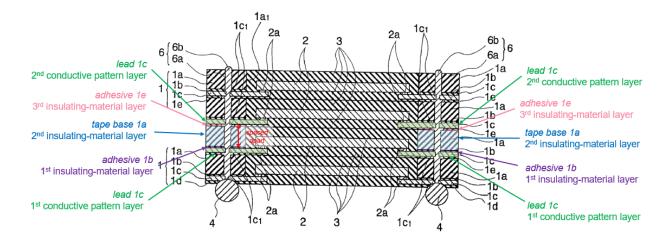

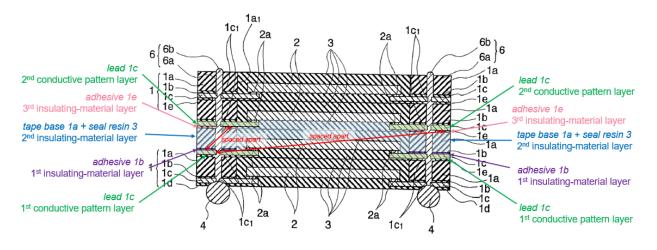

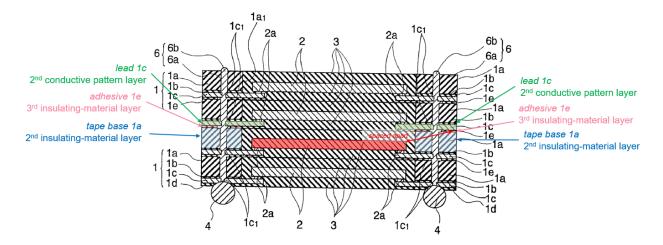

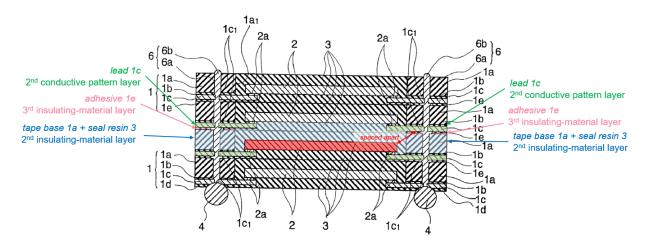

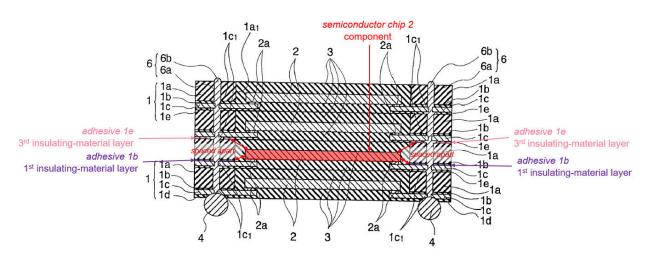

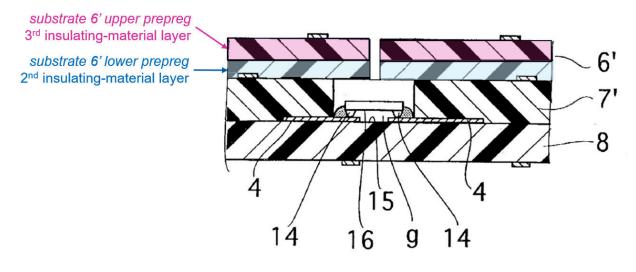

53. With reference to FIGS. 14-21, Tsubosaki010 describes techniques for manufacturing "a multi-layered TCP structure" comprising a stack of unitary TCPs laminated atop each other. *See* Tsubosaki010, FIGS. 14-21, ¶¶[0108]-[0130]. The multi-layered TCP structure allows multiple unitary TCPs to be formed into a larger module comprising multiple semiconductor chips 2 with outbound leads that connect electrical terminals of the chips 2 to other circuit components and wiring. *Id.*, ¶¶[0108]-[0114].

APPLE-1005, FIG. 14

54. Tsubosaki010 explains that each TCP in the multi-layered structure includes a device hole 1a1 formed in a tape base 1a and adhesive layer 1b. *Id.*,  $\P[[0116]$ . Copper film is bonded to the tape base 1a by the adhesive1b. The copper film is later etched to form a patterned layer comprising conductive leads 1c. *Id.*,  $\P\P[0116]$ -[0117]; FIGS. 16-17. A semiconductor chip 2 is placed within the device hole 1a1 of the tape base 1a. *Id.*,  $\P[0120]$ . The semiconductor chip 2's bump electrodes 2a and leads1c of the TCP are aligned and bonded to form an electrical connection. *Id.*,  $\P[0120]$ . A layer of adhesive 1e that coats the top surface of the tape base 1a secures the stacked TCPs to each other to form the multi-layer TCP structure shown in FIG. 14 (sectional view) and FIG. 15 (plan view). *Id.*  $\P\P[0111]$ ,  $\P\P[0124]$ -[0125]; *see also id.*,  $\P\P[0141]$ -[0154] & FIGS. 27-30

(describing option for sealing the semiconductor chips 2 in sealing resin 3 using a single molding process for the entire stacked structure). Tsubosaki010's Fifth and Seventh embodiments include substantially similar structures that map to the Challenged Claims in a generally equivalent manner.

## APPLE-1005, FIG. 14

# B. Tsubosaki405 Overview (APPLE-1011)

55. Like Tsubosaki010, Tsubosaki405 describes structures and uses of conventional carrier tapes for electronic packaging.<sup>2</sup> Tsubosaki405, Abstract. For example, Tsubosaki405 discloses "insulating adhesive films (tapes) 2, 7 ... in the form of a tape having a thermosetting or thermoplastic single layer (an adhesive

<sup>&</sup>lt;sup>2</sup> The first-named inventor on both Tsubosaki010 and Tsubosaki405 is Kunihiro Tsubosaki.

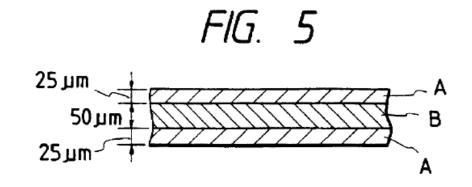

material only), or a double adhesive layer (not less than three layer construction)." Tsubosaki405, 7:33-41. "In the case of a three-layer insulating adhesive film 27 shown in FIG. 5, for instance, it is multilayer in construction, having a base B interposed between adhesive layers A, and composed of, *e.g.*, polyetheramideimide 25  $\mu$ m/captone 50  $\mu$ m/polyetheramideimide 25  $\mu$ m." *Id.*, 7:35:40: *see also id.*, 7:40-41 ("In this case, any other polyimide film may replace the captone.").<sup>3</sup>

APPLE-1011, FIG. 5

<sup>&</sup>lt;sup>3</sup> Tsubosaki405 makes clear that its adhesive film is composed of insulating materials, including materials that it identifies as polyetheramideimide and captone. APPLE-1011, 7:35-41. To the extent Tsubosaki405 suggests that the adhesive film can also be constructed from layers of polyester amide imide / Kapton / polyester amide imide, a POSITA would have understood that these materials are likewise electrically insulative. Kapton tape is commonly used in electronics and printed circuits boards.

56. Tsubosaki405's insulating adhesive films are used for bonding structures to circuitry leads 3 made from thin metal films such as iron or copper. *See, e.g.*, Tsubosaki405, 1:65-2:22, 6:44-48 ("[T]he insulating adhesive films 2, 3 are bonded to the leadframe in position. The lead 3 is in the form of a sheet or foil of Fe (42 Ni-Fe material) or Cu ..."), FIGS. 1-2.

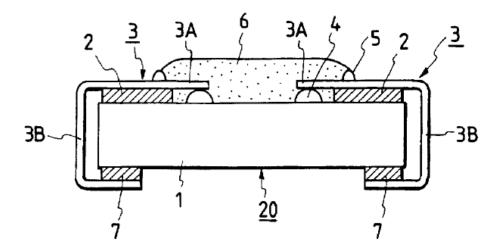

APPLE-1011, FIG. 2

#### C. The Tsubosaki010-Tsubosaki405 Combination Overview

57. As discussed above, Tsubosaki010 discloses a tape base 1a of a tape carrier 1 that can be "made of polyimide resin or other similar suitable materials." Tsubosaki010, ¶[0064]; *see also id.*, ¶¶[0111], [0118]. A thin copper film patterned to form leads 1c is bonded to the tape base 1a by an adhesive 1b. *Id.*, ¶[0116]-[0117], [0063]. "Adjacent ones of the laminated unitary TCPs are bonded together by adhesive 1e," which can be "made of a thermally deformable polyimide resin material." *Id.*, ¶[0111]; *see also id.*, [0118], FIG. 18.

58. To the extent Tsubosaki010 does not expressly disclose that the tape base layer 1a and adhesive layers 1b and 1e are made from insulating materials, it would have been obvious to a POSITA to use insulating materials for these components based on the teachings of Tsubosaki405. Recall, for example, that Tsubosaki405 describes conventional carrier tapes in which both the base member and adhesives on either side of the base member are insulating materials. Tsubosaki405, 7:33-41 (describing "a three-layer insulating adhesive film 27 ... having a base B interposed between adhesive layers A"), FIG. 5. Applying Tsubosaki405's teachings to Tsubosaki010, tape base 1a, adhesive 1b, and adhesive 1e would each predictably be made of insulating materials in a manner analogous to the three-layer adhesive film disclosed in Tsubosaki405. In the combination, in some examples, base 1a may include "captone" or "any other polyimide film," adhesive 1b may include "polyetheramideimide," and adhesive 1e may be an insulating "thermally deformable polyimide resin" based on the teachings of Tsubosaki405 and Tsubosaki010. See, e.g., Tsubosaki405, 7:33-41; Tsubosaki010, ¶¶[0064], [0111], [0116]-[0118]. Other suitable insulating materials may also be used.

59. A POSITA would have been motivated to implement Tsubosaki010's tape base 1a and adhesives 1b and 1e with insulating materials based on the teachings of Tsubosaki405 for multiple reasons.

*First*, a POSITA would have implemented Tsubosaki010's tape base 60. 1a and adhesives 1b and 1e as insulating materials to ensure that different conductive leads 1c within each TCP in the stack and/or conductive leads 1c from different TCPs in the stack are electrically isolated from each other. As FIG. 15 of Tsubosaki010 shows, each TCP 1 can include dozens of leads 1c that function as separate power and/or signal lines delivering power and/or signals to respective terminals of the semiconductor chip 2. Tsubosaki010, FIG. 15; see also id., ¶[0017]-[0022], [0062], [0110]. Because the tape base 1a and adhesives 1b, 1e are situated between conductive leads within and between TCPs of Tsubosaki010's multi-layer structure, a POSITA would have sought to implement these components with insulating materials to ensure the leads are electrically isolated and to reduce the risk of a short circuit due to undesired connections between different leads and conductors in the module. See id., APPLE-1008, 556.

61. <u>Second</u>, a POSITA would have appreciated that due to power and electrical signals being connected with conductive leads 1c to the semiconductor chip 2, no need exists for the tape base 1a or adhesives 1b and 1e to similarly be

conductive to deliver power or signals either to chip 2 or any other module component. Indeed, neither tape base 1a nor adhesives 1b and 1e are electrically connected to the terminals of semiconductor chip 2, and they are therefore neither intended nor able to practicably serve as power or signal lines for the chip 2 or other components in Tsubosaki 010's module. *See, e.g.*, Tsubosaki010, FIGS. 14-21. A POSITA therefore would have had no reason to implement conductive materials for the tape base 1a or adhesives 1b or 1e, and it would have been obvious to instead choose insulating materials given that conductive materials would serve no evident purpose.

62. <u>*Third*</u>, a POSITA would have found insulating materials for the tape base 1a and adhesives 1b and 1e obvious to try. There exist a finite number of classes of materials that could be used to implement tape base 1a and adhesives 1b and 1e—namely, insulating materials or conductive materials—and a POSITA would have had ample reason to try insulating materials for each of the reasons described herein (*e.g.*, to promote electrical isolation between leads 1c, semiconductor chips 2, and other components of the module).

63. <u>Fourth</u>, a POSITA would have understood that insulators such as the polyimide-based materials suggested in Tsubosaki405 were commonly used in electronic devices before the Critical Date. These and similar materials (*e.g.*,

polyamides) were known to be useful in "prevent[ing] cross-talk between conducting vias, and as adhesives between polymer-polymer and polymer-metal interface." APPLE-1010, 42. Such materials can also provide "excellent performance at elevated temperatures" and exhibit beneficial "corrosion resistance." APPLE-1010, 42.

64. <u>*Fifth*</u>, a POSITA would have found insulating materials such as the polyimides described in Tsubosaki405 obvious and desirable to use when implementing Tsubosaki010's tape base 1a and adhesives 1b and 1e to gain the benefit of their low dielectric constants and other favorable properties. Polyimides were "used as dielectric layers in a variety of microelectronic applications since they have good processability, low dielectric constant, high thermal stability, low moisture absorption, and good mechanical properties." APPLE-1016, Intro..

65. <u>Sixth</u>, implementing tape base 1a and adhesives 1b and 1e with insulating materials would have been obvious as a predictable application of Tsubosaki405's known materials to Tsubosaki010's known structures to achieve merely predictable results.

66. A POSITA would have reasonably expected success implementing the tape base 1a and adhesives 1b and 1e in the Tsubosaki010-Tsubosaki405 combination. Insulating materials were commonly used with adhesive films in

tape carriers before the '816 Patent, and Tsubosaki010 and Tsubosaki405 both contemplated the use of similar polyimide-based materials for similar tape base member and adhesive structures. *Id.* Indeed, Tsubosaki 010 notes that tape base 1a and adhesive 1e can each be made of polyimide materials, although Tsubosaki010 does not disclose the same specificity as Tsubosaki405. *Id.*; Tsubosaki010, ¶¶[0064], [0111], [0118]. Tsubosaki010 and Tsubosaki405 are both also analogous art in that they are both in the same field of endeavor and/or reasonably pertinent to the problem faced by the inventors of the '816 Patent. For example, like the '816 Patent, Tsubosaki010 and Tsubosaki405 both describe techniques for manufacturing and packaging electronic modules. APPLE-1001, 1:17-39; *supra*, §§X.A-B; *In re Bigio*, 381 F.3d 1320, 1325 (Fed. Cir. 2004).

#### **D.** Analysis

#### i. Claim 1

#### [1pre] An electronic module, comprising:

67. To the extent the preamble is limiting, the Tsubosaki010-

Tsubosaki405 combination renders it obvious. For example, Tsubosaki010 discloses that "a plurality of TCPs ... are laminated on one another to constitute a multi-layered TCP structure" that corresponds to an "*electronic module*" as claimed. Tsubosaki010, ¶[0110]; *generally id.*, ¶¶[0108]-[0130], FIGS. 14-21. Tsubosaki010's modules are "adaptable for use with a semiconductor device as built in electronic equipment—such as computers, portable or mobile radiotelephone handsets, video cameras or the like—or integrated circuit (IC) cards or memory cards; for example, the semiconductor device is arranged to have a tape carrier package (TCP) structure which includes a semiconductor chip 2 disposed within a device hole 1a1 of a tape carrier 1" Tsubosaki010, ¶[0062].

APPLE-1005, FIG. 14 (annotated)

### [1a] a first conductive pattern layer, and a first insulating-material layer arranged on at least one surface of the first conductive pattern layer;

68. The Tsubosaki010-Tsubosaki405 combination renders obvious

Element [1a]. For example, in the combination, leads 1c from a given one of the

TCPs in the stacked TCP module corresponds to a "first conductive pattern layer"

and adhesive layer 1b from the same TCP corresponds to a "first insulating-

*material layer*" arranged on at least one surface (*i.e.*, a top surface) of the leads 1c as claimed. Tsubosaki010, ¶[0116]-[0117] ("a tape base 1a with *adhesive 1b bonded to its one surface*"; "*bond a Cu thin-film* for example to one surface of the tape base 1a by using the adhesive 1b attached thereto; thereafter, *pattern the Cu thin film* by etching methods or the like to thereby *form a plurality of leads 1c* ...")<sup>4</sup>, FIGS. 14, 16-17, 21; *see also id.*, ¶[0063], [0066], [0068].

APPLE-1005, FIG. 14 (annotated)

69. To the extent Tsubosaki010 does not expressly disclose that adhesive layer 1b is made from an insulating material, Tsubosaki405 discloses "*insulating* adhesive films ... in the form of a tape" having insulative adhesive such as polyetheramideimide" bonded between a lead and a tape base member in a semiconductor package similar to Tsubosaki010's adhesive layer 1b.

<sup>&</sup>lt;sup>4</sup> All emphasis added unless indicated otherwise.

Tsubosaki405, 7:33-41, FIG. 5; *supra*, §X.B. It would have been obvious based on Tsubosaki405 to implement Tsubosaki010's adhesive layer 1b as an insulatingmaterial layer for each of the reasons described above in the overview of the Tsubosaki010-Tsubosaki405 combination. *Supra*, §X.C.

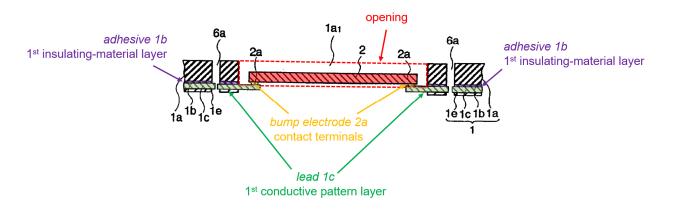

#### [1b] at least one opening in the first insulating-material layer that extends through the first insulating-material layer;

70. The Tsubosaki010-Tsubosaki405 combination renders obvious Element [1b]. For example, Tsubosaki010 discloses a device hole 1a1 (*at least one opening*) formed in tape base 1a and adhesive layer 1b (*first insulatingmaterial layer*), where the device hole 1a1 extends through the entire thickness of the adhesive layer 1b (*first insulating-material layer*). Tsubosaki010, ¶[0116] ("form by mechanical die-punching techniques a device hole 1a1"), ¶[0120] ("place a semiconductor chip 2 within the device hole 1a1"), FIGS. 16-19; see also *id.*, Abstract ("A semiconductor chip 2 is disposed within a device hole as formed in a tape base material 1a of a tape carrier 1 …"), ¶¶[0062]-[0065], FIGS. 14, 21.<sup>5</sup>

<sup>&</sup>lt;sup>5</sup> Nothing in the plain language of Element [1c] requires that a thickness of the "at least one opening" be coterminous with the thickness of first insulatingmaterial layer. Even if this were required, however, the portion of device hole 1a1 that spans the space between adhesive layer 1b, to the exclusion of the portion of

71. FIG. 19 shows the hole 1a1 (*at least one opening*) formed in the tape base 1a and adhesive layer 1b at an intermediate stage of manufacturing the electronic module:

APPLE-1005, FIG. 19 (annotated)

72. FIG. 14 shows a sectional view of the finished electronic module in

which hole 1a1 is filled with a sealing resin 3 around semiconductor chip 2:6

device hole 1a1 that spans the space between tape base 1a, provides an alternative mapping to the claimed "at least one opening."

<sup>6</sup> Like Tsubosaki010, the '816 Patent also discloses that after forming the opening in the first insulating-material layer and mounting the component (e.g., chip) in the opening, the opening can then be filled in the finished module with resin material. '816 Patent, 13:47-53 ("[P]repreg can be used as the second insulating-material layer 11. ... With the aid of the prepreg, excellent filling is achieved in the space between the elements, as shown in the example of FIG. 29."), 12:54-54-63 ("As can be seen from FIG. 28, the resin contained in the prepreg fills the space between the component 6 and its surroundings."), FIGS. 28-31.

APPLE-1005, FIG. 14 (annotated)

[1c] a component comprising contact terminals, the component being arranged at least partially within the at least one opening, the contact terminals electrically connected to the first conductive pattern layer;

73. The Tsubosaki010-Tsubosaki405 combination renders obvious

Element [1c]. For example, Tsubosaki010 discloses a semiconductor chip 2 (*component*) comprising bump electrodes 2a (*contact terminals*) being arranged at least partially within device hole 1a1 (*opening*), the bump electrodes 2a (*contact terminals*)<sup>7</sup> electrically connected to leads 1c (*first conductive pattern layer*) of the TCP in which the chip 2 is disposed. Tsubosaki010, ¶[0120] ("Subsequently, place

<sup>&</sup>lt;sup>7</sup> The semiconductor chip 2's bonding pads 2b or the combination of bonding pads 2b and bump electrodes 2a provide alternative mappings to the claimed "*contact terminals*" and likewise render the challenged claimed features obvious. *See* Tsubosaki010, [0068], [0072]-[0073], [0160]-[0163], FIG. 32.

a semiconductor chip 2 within the device hole 1a1 of the tape base 1a. Then, perform position alignment between the semiconductor chip 2's bump electrodes 2a and leads 1c. Thereafter, contact the bump electrodes 2a with leads 1c by all-atonce inner-lead bonding techniques as shown in FIG. 19."), FIGS. 19-21; *see also id.*, ¶¶[0068] ("The distal end of each lead 1c is electrically connected via bump electrode 2a to the semiconductor chip 2. This bump electrode 2a is made for example of Au ... Accordingly, the bump electrode 2a and its associated lead 1c are in contact with each other by Au-Au junction or the like."), [0062] ("chip 2 disposed within a device hole 1a1 of a tape carrier 1[] ... while causing electrodes of the semiconductor chip 2 to be externally drawn via bump electrodes 4 associated therewith"), [0069], [0072]-[0073], [0081], [0094], Abstract, FIG. 14.

APPLE-1005, FIG. 19 (annotated)

APPLE-1005, FIG. 14 (annotated)

### [1d] a second insulating-material layer disposed on the first insulatingmaterial layer, and;

74. The Tsubosaki010-Tsubosaki405 combination renders obvious

Element [1d]. For example, in a first mapping, Tsubosaki010 discloses a tape base

1a that, in the combination, provides a "second insulating-material layer"

disposed on adhesive layer 1b (first insulating-material layer) as claimed.

Tsubosaki010, ¶¶[0110], [0116], FIGS. 14, 16, 19, 21; see also id., [0063], [0064]

("tape base 1a is made of polyimide resin or other suitable materials"), [0068].

APPLE-1005, FIG. 14 (annotated) - First Mapping

75. Alternatively, in the combination, Tsubosaki010's tape base 1a together with seal resin 3 collectively provide a "*second insulating-material layer*" disposed on adhesive layer 1b (*first insulating-material layer*) as claimed. Tsubosaki010, [0110], [0116], FIGS. 14, 16, 19, 21; *see also id.*, [0063]-[0064], [0068]. Tsubosaki010 explains that seal resin 3 is formed by injection molding, in some examples. Tsubosaki010, [0121] ("Thereafter place the tape carrier 1 mounting thereon the semiconductor chip 2 within a molding die 5 as shown in FIG. 8; then, inject a molten seal resin material, which has been fed to inside a runner 5b of the molding die 5, into a cavity as formed of the tape base 1a's device hole 1a1 and the molding die 5 through a subrunner 5c and a gate 5a as well as a seal resin injection port 1a2 of the tape base 1a."), [0065]-[0067], [0082], FIG. 8; *see also id.*, [0141]-[0154] & FIGS. 28-31 (describing a technique for "[i]ntegral

molding of the seal resin 3 of the multilayer TCP" such that there are "no gaps [] formed between layers of seal resin 3").<sup>8</sup>

APPLE-1005, FIG. 14 (annotated) – Second Mapping

76. To the extent Tsubosaki010 does not expressly disclose that tape base1a is made from an insulating material, Tsubosaki405 discloses "*insulating*

<sup>&</sup>lt;sup>8</sup> Petitioner maps tape base 1a and seal resin 3 collectively to the claimed "second insulating-material layer" under Patent Owner's broader application of the term "layer" as reflected in Patent Owner's infringement charts in the related district court litigation. *See* APPLE-1105, 3-7, 9-11 (pointing to portions of Petitioner's product that encompass multiple strata of materials as the claimed first and second insulating-material layers, respectively). The '816 Patent likewise refers to a "two-layered insulation layer" made of multiple materials. APPLE-1001, 2:22-26; *see also* APPLE-1022, 14:43-45 (claim 1) (Patent Owner claiming a first or second conductive-pattern layer that "comprises *at least two layers* of at least two different materials" in a related patent asserted against Petitioner).

adhesive films ... in the form of a tape" having an insulative tape base member made from captone or other suitable polyimide film. Tsubosaki405, 7:33-41, FIG. 5; *supra*, §X.A; Tsubosaki010, [0064] ("tape base 1a is made of polyimide resin or other suitable materials"). It would have been obvious based on Tsubosaki405 to implement Tsubosaki010's tape base 1a as an insulating-material for each of the reasons described above in the overview of the Tsubosaki010-Tsubosaki405 combination. *Supra*, §X.C.

77. A POSITA also would have understood and found it obvious to implement Tsubosaki010's seal resin 3 as an insulating material, especially as seal resin 3 fills the space between different leads, electrodes, and semiconductor dies in the multi-layered TCP structure, and an insulating-material would be important to electrically isolate these structures while preventing short circuits. For example, Tsubosaki010 explains that the seal resin 3 can be made of an epoxy-based resin, which a POSITA would have understood to ordinarily be an insulating material. Tsubosaki, ¶[0076]; *see also id.*, APPLE-1006, 250 ("since 1947, [epoxy resins] are second in usage in insulation varnishes only to polyesters"), 8 ("[e]poxies are noted for their excellent dielectric properties"), 185-186, 271, 360. At minimum, and even if the insulative properties of Tsubosaki010's epoxy-based seal resin 3 are not expressly disclosed, a POSITA would have been motivated to use an insulating seal resin 3 in the Tsuboaski010-Tsubosaki405 combination to ensure different conductive components in the TCP structure were electrically isolated. In this manner, the seal resin 3 and tape base 1a cooperate to form a layer that supports and electrically isolate disparate conductive components in the TCP stack of the Tsubosaki010-Tsubosaki405 combination.<sup>9</sup> *Id.*

### [1e] a second conductive pattern layer spaced apart from the first conductive pattern layer by at least the first and second insulatingmaterial layers;

78. The Tsubosaki010-Tsubosaki405 combination renders obvious Element [1e]. For example, Tsubosaki010 discloses that the multi-layered TCP structure includes a second set of leads 1c (*second conductive-pattern layer*) of a second tape carrier 1 (*i.e.*, an upper tape carrier) positioned above a first tape carrier 1 (*i.e.*, a lower tape carrier) containing a first set of leads 1c (*first conductive-pattern layer*). Tsubosaki010, ¶¶[0108]-[0114], FIGS. 14, 21, 31; see *also id.*, ¶¶[0116]-[0117] ("Subsequently, *bond a Cu thin-film* for example to one surface of the tape base 1a by using the adhesive 1b attached thereto; thereafter, *pattern the Cu thin film* by etching methods or the like to thereby *form a plurality of leads 1c* ..."), [0063], [0066], [0068], FIGS. 16-17.

<sup>&</sup>lt;sup>9</sup> Supra, Footnote 11.

79. For both the first and second alternative mappings of the "*second insulating-material layer*" described above in connection with Element [1d], the upper set of leads 1c (*second conductive-pattern layer*) is spaced apart from the lower set of leads 1c (*first conductive-pattern layer*) by at least the adhesive layer 1b (*first insulating-material layer*) and tape base 1a (*second insulating-material layer*) or tape base 1a together with seal resin 3 (*second insulating-material layer* (first mapping).

APPLE-1005, FIG. 14 (annotated) - First Mapping

APPLE-1005, FIG. 14 (annotated) - Second Mapping

## [1f] wherein the first conductive pattern layer and the second conductive pattern layer are each substantially planar.

80. The Tsubosaki010-Tsubosaki405 combination renders obvious

Element [1f]. Tsubosaki describes techniques for forming sets of leads 1c

including a lower set (first conductive-pattern layer) and an upper set (second

*conductive-pattern layer*) in the multi-layered TCP structure that are each

substantially planar. See, e.g., Tsubosaki010, [0114], [0118], FIGS. 14-21. The

substantially planar leads 1c are shown in FIG. 14, for example:

APPLE-1005, FIG. 14 (annotated)

That leads 1c of the first and second conductive-pattern layers are 81. substantially planar also would have been obvious to a POSITA based on Tsubosaki010's descriptions of how the leads 1c are formed. For instance, Tsubosaki010 discloses that tape base 1a with its hole 1a1 have a "planar rectangular shape" and that the copper (or other suitable metal) film that is patterned to form leads 1c is bonded to the tape base 1a via adhesive 1b. Tsubosaki, ¶¶[0064], [0116]-[0117]. Tsubosaki010 also describes a "stress neutral plane A [that] is the plane parallel to the principal surface of the semiconductor chip 2, which is a specific plane on which the stress applied to the semiconductor chip 2 becomes neutral in the direction along the thickness of the semiconductor chip 2." Tsubosaki010, ¶[0075], FIG. 1; see also id., ¶¶[0074], [0088], [0094]-[0095], [0098]-[0099], [0106] (referring to stress neutral planes A and A1). Even where portions of the tape carrier 1 may be subjected to stress, Tsubosaki010

describes techniques to mitigate resulting deformation. For example, Tsubosaki010 teaches that "[i]n cases where the stress neutral plane A1 of the semiconductor chip 2 and the stress neutral plane A of the TCP as a whole are little deviated from each other due to any possible thickness differences among respective constituent parts or components of the TCP, such deviation is corrected by adjustment of the bending amount of the lead 1 c." Tsubosaki010, ¶[0098].

#### ii. Claim 2

#### [2] The electronic module of claim 1, wherein the second insulatingmaterial layer directly contacts the component.

82. The Tsubosaki010-Tsubosaki405 combination renders obvious Claim [2]. For example, Tsubosaki010 discloses that seal resin 3 (*i.e.*, a component of the *second insulating-material layer* according to the second mapping discussed above in Element [1d]) directly contacts the semiconductor chip 2 (*component*). Tsubosaki010, ¶[0120]-[0123] ("both of the principal surface and back surface of the semiconductor chip 2 are coated with the seal resin 3"), [0011], [0062]-[0063], [0065]-[0066], FIG. 14; *supra*, Element [1d].

APPLE-1005, FIG. 14 (annotated) – Second Mapping

iii. Claim 3

[3] The electronic module of claim 1, wherein the second conductive pattern layer is spaced apart from the first conductive pattern layer by the component.

83. The Tsubosaki010-Tsubosaki405 combination renders obvious Claim

[3]. For example, Tsubosaki010 discloses that the second (upper) set of leads 1c

(second conductive-pattern layer) is spaced apart from the first (lower) set of leads

1c (first conductive-pattern layer) by the semiconductor chip 2 (component).

Tsubosaki010, ¶¶[0108]-[0126], FIG. 14.

#### Attorney Docket No. 50095-0199IP1 IPR of U.S. Patent No. 11,716,816 1a1 1c1 101 2a2a 2 6b 6b 6 6 6a 6a -1a 1a ĺb 1b 1c 1c 1 1e ( **1**e -1a lead 1c -1b lead 1c 2<sup>nd</sup> conductive pattern layer 1c2<sup>nd</sup> conductive pattern layer te 1a lead 1c -1b lead 1c 1st conductive pattern layer 1b 1c 1d 1c 1st conductive pattern layer 1 <sup>1e</sup>1a 1b -1c 1d 2; 2a semiconductor chip 2 1C1 101 component 4

APPLE-1005, FIG. 14 (annotated)

iv. Claim 4

# [4] The electronic module of claim 3, wherein the second conductive pattern layer is spaced apart from the component by the second insulating-material layer.

84. The Tsubosaki010-Tsubosaki405 combination renders obvious Claim

[4]. For example, Tsubosaki010 discloses that the second (upper) set of leads 1c (*second conductive-pattern layer*) is spaced apart from the semiconductor chip 2 (*component*) by the tape base 1a or the tape base 1a together with seal resin 3 (*second insulating-material layer*). *See* Tsubosaki010, ¶¶[0120]-[0123] ("both of the principal surface and back surface of the semiconductor chip 2 are coated with the seal resin 3"), [0011], [0062]-[0063], [0065]-[0066], FIG. 14; *supra*, Element [1d]; *generally id.*, Tsubosaki010, [0108]-[0126], FIGS. 14-21.

APPLE-1005, FIG. 14 (annotated) – Second Mapping

v. Claim 5

#### [5] The electronic module of claim 4, wherein the second insulatingmaterial layer is continuously disposed between the second conductive pattern layer and the component.

85. The Tsubosaki010-Tsubosaki405 combination renders obvious Claim

[5]. For example, Tsubosaki010 discloses that seal resin 3 (i.e., a component of the

second insulating-material layer according to the second mapping discussed

above in Element [1d]) is continuously disposed between the upper set of leads 1c (*second conductive-pattern layer*) and the semiconductor chip 2 (*component*). Tsubosaki010, ¶[0120]-[0123] ("both of the principal surface and back surface of the semiconductor chip 2 are coated with the seal resin 3"), [0140] ("no gaps are formed between layers of seal resin 3"), [0011], [0062]-[0063], [0065]-[0066], FIG. 14; *supra*, Element [1d]; *generally* Tsubosaki010, [0108]-[0126], FIGS. 14-21 & [0139]-[0154], FIGS. 27-30.

APPLE-1005, FIG. 14 (annotated) – Second Mapping

vi. Claim 6

### [6] The electronic module of claim 1, wherein the first insulatingmaterial layer is spaced apart from the component.

86. The Tsubosaki010-Tsubosaki405 combination renders obvious Claim

[6]. For example, Tsubosaki010 discloses that the adhesive layer 1b (first

insulating-material layer) is spaced apart from the semiconductor chip 2

(*component*). Tsubosaki010's seal resin 3 surrounds the semiconductor chip 2 thus separating the semiconductor chip 2 from the adhesive layer 1b. Tsubosaki010, ¶¶[0065], [0082]-[0085]; *see also id.*, ¶[0092] ("the thickness D1 of the seal resin 3 [can] be equal to the thickness D2 of tape carrier 1"), [0063], [0108]-[0126], FIGS. 14-21.

APPLE-1005, FIG. 14 (annotated)

vii. Claim 7

#### [7] The electronic module of claim 1, wherein the first insulatingmaterial layer comprises a different material than a material of the second insulating-material layer.

87. The Tsubosaki010-Tsubosaki405 combination renders obvious Claim

[7]. As discussed above, in the Tsubosaki010-Tsubosaki405 combination,

adhesive layer 1b provides a "first insulating-material layer," tape base 1a

provides a "second insulating-material layer" according to a first mapping, and