#### UNITED STATES PATENT AND TRADEMARK OFFICE

#### **BEFORE THE PATENT TRIAL AND APPEAL BOARD**

#### **BOE Technology Group Co., Ltd.** Petitioner

v.

Optronic Sciences LLC Patent Owner

Inter Partes Review No.: IPR2025-00239

## PETITION FOR INTER PARTES REVIEW OF U.S. PATENT NO. 8,502,757 UNDER 35 U.S.C. §§ 311-319 AND 37 C.F.R. §§ 42.1-100, ET SEQ

# TABLE OF CONTENTS

# Page

| I.   | INTRODUCTION         |                                      |         |                                          |                         |  |

|------|----------------------|--------------------------------------|---------|------------------------------------------|-------------------------|--|

| II.  | STA                  | ATEMENT OF PRECISE RELIEF REQUESTED1 |         |                                          |                         |  |

| III. | THE                  | THE 757 PATENT1                      |         |                                          |                         |  |

|      | A.                   | Over                                 | view o  | of the 757 Patent                        | 1                       |  |

|      | B.                   | Over                                 | view o  | of the 757 patent's File History         | 2                       |  |

|      | C.                   | Perso                                | on of C | Ordinary Skill in the Art                | 2                       |  |

|      | D.                   | Clain                                | n Cons  | struction Under 37 C.F.R. § 42.104(b)(3) | 3                       |  |

|      |                      | 1.                                   | Mear    | ns-Plus-Function Limitations             | 3                       |  |

|      |                      |                                      | a.      | [1e] "an input unit…"                    | 4                       |  |

|      |                      |                                      | b.      | [1f] "a voltage adjustment unit…"        | 5                       |  |

|      |                      |                                      | c.      | [1g] "a couple unit…"                    | 6                       |  |

|      |                      |                                      | d.      | [1h] "a driving unit…"                   | 7                       |  |

|      |                      |                                      | e.      | [1i] "a first reset unit…"               | 8                       |  |

|      |                      |                                      | f.      | [1j] "a second reset unit…"              | 9                       |  |

|      |                      |                                      | g.      | [11] "an emission enable unit"           | 10                      |  |

|      |                      |                                      | h.      | Abridged Claim Listing Summary           | 11                      |  |

|      |                      | 2.                                   | "first  | /second reference voltage"               | 12                      |  |

|      |                      |                                      | a.      | Primary Construction                     | 12                      |  |

|      |                      |                                      | b.      | Alternative Construction                 | 13                      |  |

| IV.  | OVE                  | RVIE                                 | WOF     | THE PRIOR ART REFERENCES                 | 13                      |  |

|      | A.                   | EX10                                 | 004 - I | Kim406                                   | 13                      |  |

|      | B.                   | EX10                                 | )05 – I | Kim730                                   | 13                      |  |

|      | C.                   | EX10                                 | 006 – 5 | Senda                                    | 13                      |  |

|      | D.                   | Anal                                 | ogous   | Art                                      | 13                      |  |

| V.   |                      |                                      |         | AIMS 1-12 AND 14-19 ARE ANTICIPATED BY   | 11                      |  |

|      | KIM406<br>A. Claim 1 |                                      |         |                                          |                         |  |

|      | <b>1 1</b> .         | Juin                                 |         |                                          | · • • • • • • • • • • • |  |

|    | 1.    | [1pre]14 |

|----|-------|----------|

|    | 2.    | [1a]14   |

|    | 3.    | [1b]15   |

|    | 4.    | [1c]16   |

|    | 5.    | [1d]16   |

|    | 6.    | [1e]17   |

|    | 7.    | [1f]19   |

|    | 8.    | [1g]20   |

|    | 9.    | [1h]22   |

|    | 10.   | [1i]24   |

|    | 11.   | [1j]26   |

|    | 12.   | [1k]29   |

|    | 13.   | [11]     |

| B. | Claim |          |

| C. | Claim | 3:       |

| D. | Claim |          |

| E. | Claim |          |

| F. | Claim |          |

| G. | Claim |          |

| H. | Claim |          |

| I. | Claim | 9:       |

| J. | Claim |          |

| K. | Claim |          |

| L. | Claim |          |

| M. | Claim |          |

| N. | Claim |          |

| O. | Claim |          |

| P. | Claim |          |

|    | 1.    | [17pre]  |

|      |                                                  | 2.    | [17a]                               |    |

|------|--------------------------------------------------|-------|-------------------------------------|----|

|      |                                                  | 3.    | [17b]                               |    |

|      |                                                  | 4.    | [17c]                               |    |

|      |                                                  | 5.    | [17d]                               |    |

|      |                                                  | 6.    | [17e]                               |    |

|      |                                                  | 7.    | [17f]                               |    |

|      |                                                  | 8.    | [17g]                               |    |

|      |                                                  | 9.    | [17h]                               |    |

|      |                                                  | 10.   | [17i]                               |    |

|      |                                                  | 11.   | [17j]                               |    |

|      |                                                  | 12.   | [17k]                               |    |

|      |                                                  | 13.   | [171]                               |    |

|      |                                                  | 14.   | [17m]                               |    |

|      |                                                  | 15.   | [17n]                               |    |

|      |                                                  | 16.   | [170]                               |    |

|      |                                                  | 17.   | [17p]                               | 40 |

|      |                                                  | 18.   | [17q]                               | 41 |

|      |                                                  | 19.   | [17r]                               | 41 |

|      |                                                  | 20.   | [17s]                               | 41 |

|      |                                                  | 21.   | [17t]                               | 42 |

|      |                                                  | 22.   | [17u]                               | 42 |

|      | Q.                                               | Clain | n 18:                               | 42 |

|      | R.                                               | Clain | n 19:                               | 42 |

| VI.  | GRO                                              | UND 2 | 2: CLAIMS 1-20 ARE OBVIOUS OVER THE |    |

|      | COM                                              | IBINA | TION OF KIM406 AND KIM730           | 43 |

|      | A.                                               | Com   | pination Rationale                  | 44 |

|      | В.                                               | Clain | ns 13, 20                           | 46 |

|      | C.                                               | Clain | ns 1-20                             | 46 |

| VII. | GROUND 3: CLAIMS 1-21 ARE ANTICIAPTED BY SENDA47 |       |                                     |    |

| A. | Send  | a's Modified Third Embodiment | 47 |

|----|-------|-------------------------------|----|

| B. | Clain | n 1                           | 50 |

|    | 1.    | [1pre]                        | 50 |

|    | 2.    | [1a]                          | 52 |

|    | 3.    | [1b]                          | 53 |

|    | 4.    | [1c]                          | 53 |

|    | 5.    | [1d]                          | 54 |

|    | 6.    | [1e]                          | 55 |

|    | 7.    | [1f]                          | 57 |

|    | 8.    | [1g]                          | 59 |

|    | 9.    | [1h]                          | 61 |

|    | 10.   | [1i]                          | 64 |

|    | 11.   | [1j]                          | 66 |

|    | 12.   | [1k]                          | 68 |

|    | 13.   | [11]                          | 69 |

| C. | Clain | n 2:                          | 71 |

| D. | Clain | n 3:                          | 71 |

| E. | Clain | n 4:                          | 71 |

| F. | Clain | n 5:                          | 72 |

| G. | Clain | n 6:                          | 72 |

| H. | Clain | n 7:                          | 72 |

| I. | Clain | n 8:                          | 72 |

| J. | Clain | n 9:                          | 72 |

| K. | Clain | n 10:                         | 73 |

| L. | Clain | n 11:                         | 73 |

| M. | Clain | n 12:                         | 73 |

| N. | Clain | n 13:                         | 73 |

| O. | Clain | n 14:                         | 73 |

| P. | Clain | n 15:                         | 74 |

|       | Q.  | Claim | 16:                                  | .74 |

|-------|-----|-------|--------------------------------------|-----|

|       | R.  | Claim | 17:                                  | .74 |

|       |     | 1.    | [17pre]                              | .74 |

|       |     | 1.    | [17a]                                | .75 |

|       |     | 2.    | [17b]                                | .75 |

|       |     | 3.    | [17c]                                | .76 |

|       |     | 4.    | [17d]                                | .76 |

|       |     | 5.    | [17e]                                | .76 |

|       |     | 6.    | [17f]                                | .76 |

|       |     | 7.    | [17g]                                | .77 |

|       |     | 8.    | [17h]                                | .77 |

|       |     | 9.    | [17i]                                | .77 |

|       |     | 10.   | [17j]                                | .78 |

|       |     | 11.   | [17k]                                | .78 |

|       |     | 12.   | [171]                                | .78 |

|       |     | 13.   | [17m]                                | .79 |

|       |     | 14.   | [17n]                                | .79 |

|       |     | 15.   | [170]                                | .80 |

|       |     | 16.   | [17p]                                | .80 |

|       |     | 17.   | [17q]                                | .81 |

|       |     | 18.   | [17r]                                | .82 |

|       |     | 19.   | [17s]                                | .83 |

|       |     | 20.   | [17t]                                | .83 |

|       |     | 21.   | [17u]                                | .84 |

|       | S.  | Claim | 18:                                  | .84 |

|       | Т.  | Claim | 19:                                  | .84 |

|       | U.  | Claim | 20                                   | .85 |

|       | V.  | Claim | 21                                   | .86 |

| VIII. | GRO | UND 4 | : CLAIMS 1-21 ARE OBVIOUS OVER SENDA | .86 |

|     | A.   | Clair | Claims 1-21                                      |    |  |

|-----|------|-------|--------------------------------------------------|----|--|

|     | B.   | Clair | n 21                                             | 88 |  |

| IX. | DISC | CRETI | ONARY DENIAL IS NOT WARRANTED                    | 90 |  |

|     | A.   | 35 U  | .S.C. § 314(a) Analysis                          | 90 |  |

|     |      | 1.    | Stay                                             | 90 |  |

|     |      | 2.    | Trial Date                                       | 91 |  |

|     |      | 3.    | Parallel Proceeding                              | 91 |  |

|     |      | 4.    | Issue Overlap                                    | 91 |  |

|     |      | 5.    | Same Party                                       | 91 |  |

|     |      | 6.    | Other Considerations                             | 92 |  |

|     | B.   | 35 U  | .S.C. § 325(b) Analysis                          | 92 |  |

| X.  | COM  | IPLIA | NCE WITH FORMAL REQUIREMENTS                     | 92 |  |

|     | A.   | Mano  | datory Notices Under 37 C.F.R. §§ 42.8(b)(1)-(4) | 92 |  |

|     |      | 1.    | Real Party-In-Interest                           | 92 |  |

|     |      | 2.    | Related Matters                                  | 92 |  |

|     |      | 3.    | Lead and Backup Counsel                          | 93 |  |

|     |      | 4.    | Service Information                              | 93 |  |

| XI. | CON  | CLUS  | ION                                              | 94 |  |

# **INDEX OF EXHIBITS**

| Exhibit No. | Description                                                      |  |  |  |

|-------------|------------------------------------------------------------------|--|--|--|

| 1001        | U.S. Patent No. 8,502,757 (" <b>757 patent</b> ")                |  |  |  |

| 1002        | Declaration of R. Jacob Baker, Ph.D., P.E.                       |  |  |  |

| 1003        | File History of U.S. Patent No. 8,502,757                        |  |  |  |

| 1004        | U.S. 2007/0103406 (" <b>Kim406</b> ")                            |  |  |  |

| 1005        | U.S. 2005/0110730 (" <b>Kim730</b> ")                            |  |  |  |

| 1006        | U.S. 2009/0040150 ("Senda")                                      |  |  |  |

| 1007        | R. Jacob Baker, et al., CMOS Circuit Design, Layout, and         |  |  |  |

|             | Simulations (1 <sup>st</sup> ed. 1998)                           |  |  |  |

| 1008        | U.S. Pat. App. Pub. No. 2007/0170990 ("Park")                    |  |  |  |

| 1009        | Order Setting Jury Selection for May 4, 2026                     |  |  |  |

| 1010        | Patent Owner's Infringement Contentions for the 757 patent dated |  |  |  |

|             | January 21, 2025                                                 |  |  |  |

| 1011        | Dong-Wook Park, et. al., 53.5: High-Speed AMOLED Pixel           |  |  |  |

|             | Circuit and Driving Scheme, SID 10 Digest (2010).                |  |  |  |

| 1012        | Jung Chul Kim, et. al., A Novel OLED Pixel Circuit with          |  |  |  |

|             | Controllable Threshold Voltage Compensation Time, IDW '19        |  |  |  |

|             | (2019).                                                          |  |  |  |

| 1013        | Chih-Lung Lin, et. al., Compensation Pixel Circuit to Improve    |  |  |  |

|             | Image Quality for Mobile AMOLED Displays, IEEE Journal of        |  |  |  |

|             | Solid-State Circuits (2018).                                     |  |  |  |

| 1014        | Docket Sheets Search                                             |  |  |  |

| 1015        | Curriculum Vitae of Dr. R. Jacob Baker                           |  |  |  |

[1pre] An organic light emitting display, comprising:

[1a] a data line for transmitting a data signal;

[1b] a first scan line for transmitting a first scan signal;

[1c] a second scan line for transmitting a second scan signal;

[1d] a transmission line for transmitting an emission signal;

[1e] an input unit, electrically connected to the data line and the first scan line,

for outputting a preliminary control voltage according to the data signal and the first scan signal;

[1f] a voltage adjustment unit, electrically connected to the transmission line and the input unit, for adjusting the preliminary control voltage according to the emission signal and a second reference voltage;

[1g] a couple unit, electrically connected to the input unit and the voltage adjustment unit, for adjusting a control voltage through coupling a change of the preliminary control voltage;

[1h] a driving unit, electrically connected to the couple unit, for providing a driving current and a driving voltage according to the control voltage and a first power voltage;

[1i] a first reset unit, electrically connected to the driving unit and the second scan line, for resetting the driving voltage according to the second scan signal and a first reference voltage;

[1j] a second reset unit, electrically connected to the driving unit, the first reset unit and the first scan line, for resetting the control voltage according to the first scan signal and the driving voltage;

[1k] an organic light emitting diode for generating output light according to the driving current; and

[11] an emission enable unit, electrically connected to the transmission line, the driving unit and the organic light emitting diode, for providing a control of furnishing the driving current to the organic light emitting diode according to the emission signal.

[2] The organic light emitting display of claim 1, wherein the input unit comprises a first transistor, the first transistor having a first end electrically connected to the data line, a gate end electrically connected to the first scan line, and a second end electrically connected to the voltage adjustment unit and the couple unit.

[3] The organic light emitting display of claim 2, wherein the first transistor comprises a thin film transistor or a field effect transistor.

# CHART OF CLAIMS

[4] The organic light emitting display of claim 1, wherein the driving unit comprises a second transistor, the second transistor having a first end for receiving the first power voltage, a gate end for receiving the control voltage, and a second end for outputting the driving current and the driving voltage.

[5] The organic light emitting display of claim 4, wherein the second transistor comprises a thin film transistor or a field effect transistor.

[6] The organic light emitting display of claim 1, wherein the couple unit comprises a capacitor electrically connected between the input unit and the driving unit.

[7] The organic light emitting display of claim 1, wherein the first reset unit comprises a third transistor, the third transistor having a first end for receiving the first reference voltage, a gate end electrically connected to the second scan line, and a second end electrically connected to the driving unit, the second reset unit and the emission enable unit.

[8] The organic light emitting display of claim 7, wherein the third transistor comprises a thin film transistor or a field effect transistor.

[9] The organic light emitting display of claim 1, wherein the second reset unit comprises a fourth transistor, the fourth transistor having a first end electrically connected to the driving unit, the first reset unit and the emission enable unit, a gate end electrically connected to the first scan line, and a second end electrically connected to the couple unit and the driving unit.

[10] The organic light emitting display of claim 9, wherein the fourth transistor comprises a thin film transistor or a field effect transistor.

[11] The organic light emitting display of claim 1, wherein the voltage adjustment unit comprises a fifth transistor, the fifth transistor having a first end for receiving the second reference voltage, a gate end electrically connected to the transmission line, and a second end electrically connected to the input unit and the couple unit.

[12] The organic light emitting display of claim 11, wherein the fifth transistor comprises a thin film transistor or a field effect transistor.

[13] The organic light emitting display of claim 11, wherein the second reference voltage is the first power voltage.

[14] The organic light emitting display of claim 1, wherein the emission enable unit comprises a sixth transistor, the sixth transistor having a first end electrically connected to the driving unit, the first reset unit and the second reset unit, a gate end electrically connected to the transmission line, and a second end electrically connected to the organic light emitting diode.

## CHART OF CLAIMS

[15] The organic light emitting display of claim 14, wherein the sixth transistor comprises a thin film transistor or a field effect transistor.

[16] The organic light emitting display of claim 1, wherein the organic light emitting diode comprises an anode electrically connected to the emission enable unit and a cathode for receiving a second power voltage.

[17pre] A driving method, comprising:

[17a] outputting a preliminary control voltage by an input unit according to a data signal and a first scan signal;

[17b] adjusting the preliminary control voltage by a voltage adjustment unit according to an emission signal and a second reference voltage;

[17c] adjusting a control voltage by a couple unit through coupling a change of the preliminary control voltage;

[17d] providing a driving current and a driving voltage by a driving unit according to the control voltage and a power voltage;

[17e] resetting the driving voltage by a first reset unit according to a second scan signal and a first reference voltage;

[17f] resetting the control voltage by a second reset unit according to the first scan signal and the driving voltage;

[17g] generating output light by an organic light emitting diode according to the driving current;

[17h] providing a control of furnishing the driving current to the organic light emitting diode by an emission enable unit according to the emission signal;

[17i] providing the first scan signal with a first level to the input unit and the second reset unit, providing the second scan signal with the first level to the first reset unit, providing the emission signal with a second level different from the first level for disabling a voltage adjusting operation of the voltage adjustment unit and disabling a current furnishing operation of the emission enable unit, and providing the data signal to the input unit during a first interval;

[17j] outputting the preliminary control voltage by the input unit according to the data signal and the first scan signal during the first interval;

[17k] resetting the driving voltage by the first reset unit according to the second scan signal and the first reference voltage during the first interval;

[171] resetting the control voltage by the second reset unit according to the first scan signal and the driving voltage during the first interval;

[17m] switching the second scan signal from the first level to the second level for disabling a resetting operation of the first reset unit during a second interval following the first interval;

# CHART OF CLAIMS

[17n] performing a threshold voltage compensation operation on the control voltage by the second reset unit and the driving unit according to the first scan signal and the power voltage during the second interval;

[170] switching the first scan signal from the first level to the second level for disabling a resetting operation of the second reset unit and disabling an inputting operation of the input unit during a third interval following the second interval;

[17p] switching the emission signal from the second level to the first level during a fourth interval following the third interval;

[17q] adjusting the preliminary control voltage by the voltage adjustment unit according to the emission signal and the second reference voltage during the fourth interval;

[17r] adjusting the control voltage by the couple unit through coupling a change of the preliminary control voltage during the fourth interval;

[17s] providing the driving current by the driving unit according to the control voltage and the power voltage during the fourth interval;

[17t] furnishing the driving current to the organic light emitting diode by the emission enable unit according to the emission signal during the fourth interval; and

[17u] generating output light by the organic light emitting diode according to the driving current during the fourth interval.

[18] The driving method of claim 17, wherein the second level is greater than the first level.

[19] The driving method of claim 17, wherein the first level is greater than the second level.

[20] The driving method of claim 17, wherein the second reference voltage is the power voltage.

[21] The driving method of claim 17, wherein a length of the second interval is greater than a length of the first interval.

### I. INTRODUCTION

BOE Technology Group Co. LTD. ("Petitioner") requests inter partes review

of claims 1-21 ("Challenged Claims") of U.S. Patent No. 8,502,757 ("757 patent,"

EX1001), owned by Optronic Sciences LLC ("PO").

This petition relies upon the declaration of Dr. R. Jacob Baker (EX1002) and

copies large portions of that declaration herein.

Petitioner certifies that the 757 patent is available for *inter partes* review.

# II. STATEMENT OF PRECISE RELIEF REQUESTED

In accordance with 35 U.S.C. § 311, Petitioner requests cancelation of

claims 1-21 of the 757 patent in view of the following grounds:

| Ground | Claims      | Stat. Basis     | Prior Art                |

|--------|-------------|-----------------|--------------------------|

| 1      | 1-12, 14-19 | 35 U.S.C. § 102 | Kim406                   |

| 2      | 1-20        | 35 U.S.C. § 103 | Kim406 in view of Kim730 |

| 3      | 1-21        | 35 U.S.C. § 102 | Senda                    |

| 4      | 1-21        | 35 U.S.C. § 103 | Senda                    |

# III. THE 757 PATENT

# A. Overview of the 757 Patent

The 757 patent was filed on November 15, 2011, and issued on August 6,

# 2013. EX1001; EX1002, ¶45.

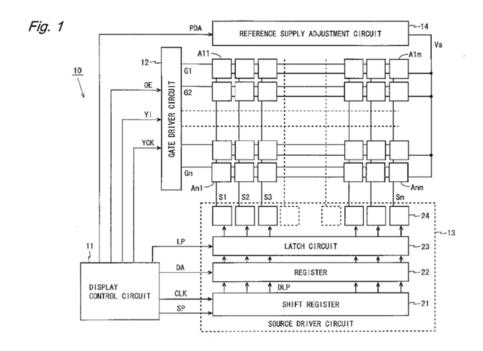

The 757 patent purports to improve on a prior art pixel driving circuit

(Figure 1) by adding reset and threshold voltage compensation mechanisms to

avoid image retention and pixel brightness distortion. EX1001, 7:4-9; EX1002, ¶46.

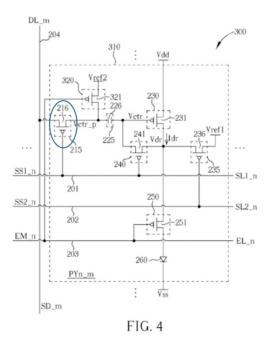

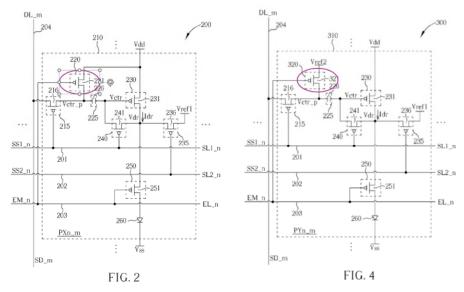

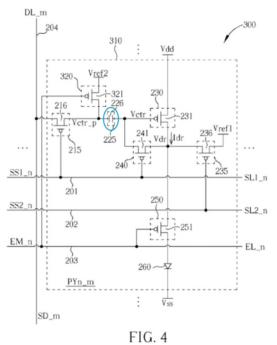

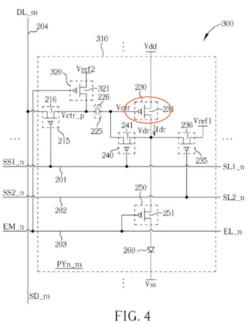

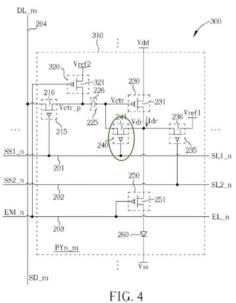

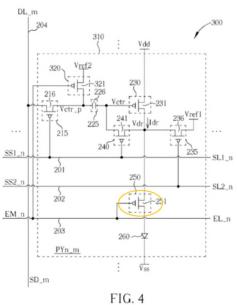

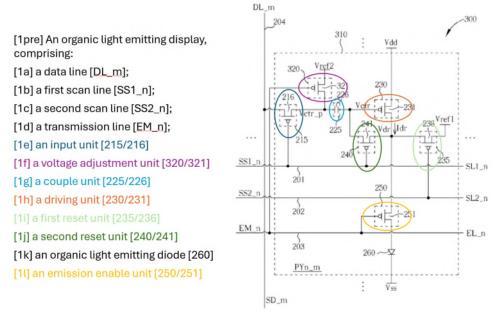

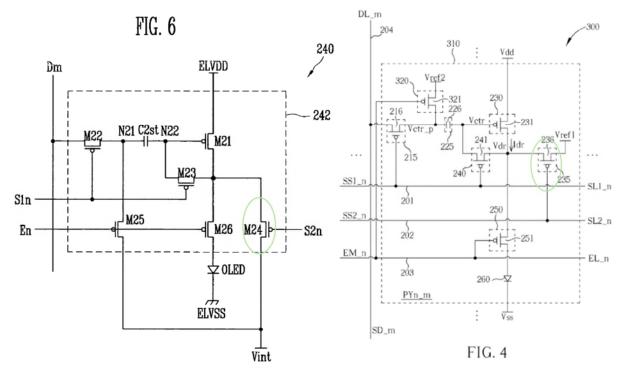

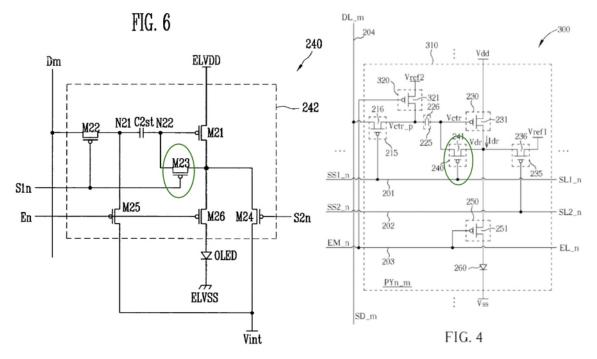

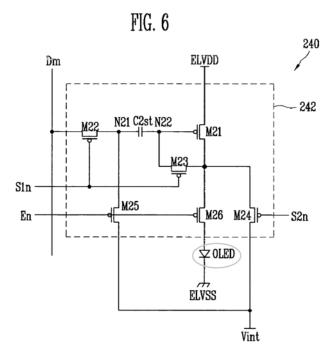

The 757 patent discloses a pixel driving circuit with two embodiments— Figures 2 and 4. In the embodiment in Figure 2, the voltage adjustment unit uses Vdd as the second reference voltage. *See* Fig. 2 (unit 220 is transistor 221 with electrode connected to Vdd). In the embodiment in Figure 4, the voltage adjustment unit uses Vref2. *See* Fig. 4 (unit 320 is transistor 321 with electrode connected to Vref2). The embodiments are otherwise identical and the timing of the circuit is provided in Figure 3 and accompanying text. EX1002, ¶47.

#### **B.** Overview of the 757 patent's File History

The claims of the 757 patent were allowed on the first office action (with amendments to claim 17 under *Ex Parte Quayle*). EX1003, 80-92 (April 25, 2013 Office Action). The Examiner found none of the prior art of record disclosed the voltage adjustment unit and first reset unit in combination with the other limitations of the claims. *Id.* The prior art asserted herein discloses those limitations as shown below. EX1002, ¶48.

#### C. Person of Ordinary Skill in the Art

A person of ordinary skill in the art ("POSITA") at the time of the alleged invention of the 757 patent (November 15, 2011), and for that matter, at all subsequent times through the present, would have had a Bachelors' degree in

electrical engineering or a comparable field of study, plus approximately one or more years of professional experience with electronic and optoelectronic system design. Additional graduate education could substitute for professional experience, and significant experience in the field could substitute for formal education. EX1002, ¶49.

#### D. Claim Construction Under 37 C.F.R. § 42.104(b)(3)

Any claim terms not listed below should be construed according to their plain and ordinary meaning to a POSITA at the time of the 757 patent. EX1002, ¶50.

#### 1. Means-Plus-Function Limitations

Claim 1 recites several limitations as "... unit ... for" performing a claimed function. The lack of the word "means" raises the presumption that these terms are not subject to Section 112f, but that presumption is rebutted because none of the terms recite sufficient structure for performing the claimed function. EX1002, ¶51.

Each term follows the same format: a functional qualifier, the nonce word "unit," an appositive reciting connections, and "for" followed by a function. The "voltage adjustment unit" in limitation [1f] is reproduced below as an example.

a voltage adjustment unit, electrically connected to the transmission line and the input unit, for adjusting the preliminary control voltage according to the emission signal and a second reference voltage

#### EX1001, [1f]. EX1002, ¶52.

In each limitation, the initial functional qualifier is merely a shorthand paraphrasing of the function and does not impart structure to a POSITA. The word "unit" does not recite structure because it is merely a nonce word for any circuitry that would perform the function. The claimed connections add some limitations as to how the structure is connected but is not sufficient structure for performing the claimed function. The "for" clause then recites the function without any structure for performing the function. Thus, each limitation would not be recognized by one of ordinary skill in the art as reciting sufficiently definite structure for performing the claimed function. EX1002, ¶53.

This Petition applies the prior art under both the ordinary meaning of the claim and under the correct means-plus-function constructions. The prior art invalidates the claims under each construction. EX1002, ¶54.

Each limitation subject to 112f is presented below with its <u>function</u> <u>underlined</u> (the functions are entitled to their ordinary meaning and do not require further construction) followed by the corresponding structure disclosed and linked in the specification for performing the claimed function. EX1002, ¶55.

#### a. [1e] "an input unit..."

"An input unit, electrically connected to the data line and the first scan line, for outputting a preliminary control voltage according to the data signal and the

first scan signal" has the corresponding structure: transistor 216 connected as

disclosed in Figures 2, 4 and 4:34-38.

This structure is linked to this function. EX1001, Fig. 3, 3:54-57, 5:13-15. EX1002, ¶¶56-57.

# b. [1f] "a voltage adjustment unit..."

"A voltage adjustment unit, electrically connected to the transmission line and the input unit, <u>for adjusting the preliminary control voltage according to the</u> <u>emission signal and a second reference voltage</u>" has the corresponding structure:

a) transistor 221 connected as disclosed in Figure 2 and 4:34-38 (to Vdd), or

b) transistor 321 connected as disclosed in Figure 4 and 6:36-42 (to Vref2).

Each of these structures is linked to this function. EX1001, Fig. 3, 3:58-61 (221), 5:45-55 (Vdd), 6:31-63 (321), 6:43-51 (Vref2). EX1002, ¶¶58-59.

# c. [1g] "a couple unit…"

"A couple unit, electrically connected to the input unit and the voltage adjustment unit, <u>for adjusting a control voltage through coupling a change of the</u> <u>preliminary control voltage</u>" has the corresponding structure: capacitor 226 connected as disclosed in Figures 2 and 4 and 4:42-44.

This structure is linked to this function. EX1001, Fig. 3, 3:62-65, 5:50-55, 6:46-51. EX1002, ¶¶60-61.

# d. [1h] "a driving unit…"

"A driving unit, electrically connected to the couple unit, <u>for providing a</u> <u>driving current and a driving voltage according to the control voltage and a first</u> <u>power voltage</u>" has the corresponding structure: transistor 231 connected as disclosed in Figures 2, 4 and 4:38-41.

This structure is linked to this function. EX1001, 3:65-4:2, 5:56-60, 6:53-64. EX1002, ¶62-63.

# e. [1i] "a first reset unit..."

"A first reset unit, electrically connected to the driving unit and the second scan line, <u>for resetting the driving voltage according to the second scan signal and</u> <u>a first reference voltage</u>" has the corresponding structure: transistor 236 connected as disclosed in Figures 2, 4 and 4:44-48.

This structure is linked to this function. EX1001, 4:2-5. EX1002, ¶¶64-65.

# f. [1j] "a second reset unit..."

"A second reset unit, electrically connected to the driving unit, the first reset unit and the first scan line, <u>for resetting the control voltage according to the first</u> <u>scan signal and the driving voltage</u>" has the corresponding structure: transistor 241 connected as disclosed in Figures 2, 4 and 4:48-52.

This structure is linked to this function. EX1001, 4:5-9. EX1002, ¶¶66-67.

# g. [11] "an emission enable unit..."

"An emission enable unit, electrically connected to the transmission line, the driving unit and the organic light emitting diode, <u>for providing a control of furnishing the driving current to the organic light emitting diode according to the emission signal</u>" has the corresponding structure: transistor 221 connected as disclosed in Figures 2, 4 and 4:54-58.

This structure is linked to this function. EX1001, 4:9-14; EX1002, ¶68-69.

## h. Abridged Claim Listing Summary

An abridged claim listing summarizing the 112f terms is reproduced below next to the corresponding structure as shown in Figure 4 (the alternative structure of 220/221 for the voltage adjustment unit in Figure 2 is not shown). EX1002, ¶70.

#### 2. "first/second reference voltage"

#### a. **Primary Construction**

The claims encompass first and second reference voltages that are the same or different from each other. The claims use "first" and "second" as labels to refer to two reference voltages in the independent claims. The claims themselves make clear that differently labelled voltages in the independent claims can be the same voltage. For example, claim 1 recites a "second reference voltage" and a "first power voltage" and then dependent claim 13 recites "wherein the second reference voltage is the first power voltage." EX1001, claims 1, 13. There is no definition or disclaimer in the specification or file history that would require limiting the "first" and "second" reference voltages to only the same voltage or to only different voltages. The disclosed embodiments do not explicitly state, or implicitly require, that the reference voltages be different from each other, so it is not possible to read such a limitation in from the specification (which would be legally improper, even if it were possible). Finally, the ordinary meaning of "first" and "second" reference voltages encompasses reference voltages that are the same or different. See. e.g., EX1007 (Fig. 29.30); EX1008, [0039] (VREF1 and VREF2 may be the same or different voltage values). Thus, the claims encompass "first" and "second" reference voltages that are the same or different. EX1002, ¶71 (explaining specification further).

#### **b.** Alternative Construction

Under an alternative construction, the "first" and "second" voltages are limited to different voltages. EX1002, ¶72.

## IV. OVERVIEW OF THE PRIOR ART REFERENCES

#### A. EX1004 – Kim406

U.S. Pat. App. Pub. 2007/0103406 to Kim406 was published on May 10,

2007 and is prior art under pre-AIA Section 102(b). EX1002, ¶73.

## B. EX1005 – Kim730

U.S. Pat. App. Pub. 2005/0110730 to Kim730 was published on May 26,

2005 and is prior art under pre-AIA Section 102(b). EX1002, ¶74.

# C. EX1006 – Senda

U.S. Pat. App. Pub. 2009/0040150 to Senda was published on February 12,

2000 and is prior art under pre-AIA Section 102(b). EX1002, ¶75.

# D. Analogous Art

Each of the references is analogous art to the 757 patent because each relates to an OLED display with threshold voltage compensation and driving method. EX1002, ¶76.

# V. GROUND 1: CLAIMS 1-12 AND 14-19 ARE ANTICIPATED BY KIM406

#### A. Claim 1

#### 1. [1pre]

Kim406 discloses "An organic light emitting display, comprising (see

following limitations)." EX1002, ¶77.

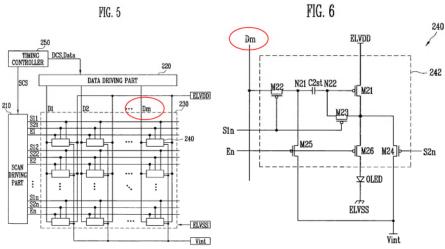

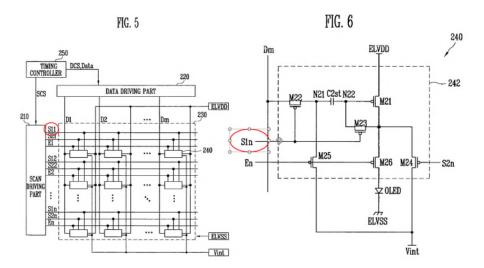

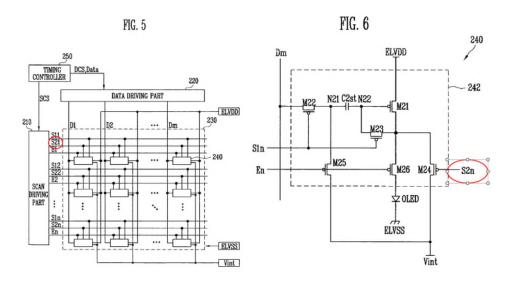

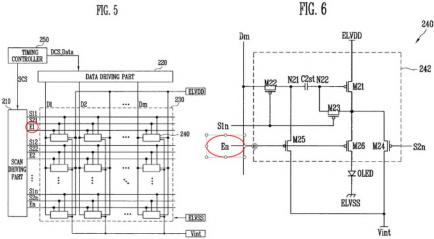

EX1004, Title, Figs. 5-7, [0003], [0045] ("organic light emitting display device"), [0046]-[0072], claims 1-20; EX1002, ¶78.

# 2. [1a]

Kim406 discloses "a data line (Dm) for transmitting a data signal (data signal)." EX1002, ¶79.

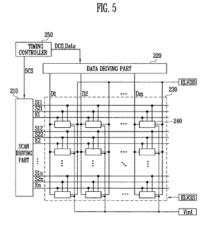

EX1004, Figs. 5 (Data Driving Part 220 and lines D1 to Dm), Fig. 6 (line Dm), [0049] (Data Driving Part 220 sends data signals on data lines Dm), [0054] (pixel receives data signals from data lines Dm), [0064] (data signal supplied on Dm). EX1002, ¶80.

# 3. [1b]

Kim406 discloses "a first scan line (S1n) for transmitting a first scan signal (first scan signal)." EX1002, ¶81.

U.S. Patent No. 8,502,757 Petition for *Inter Partes* Review EX1004, Figs. 5 (Scan Driving Part 210), Fig. 6 (S1n), Fig. 7 (S1n), [0048] (scan driving part 210 transmits first scan signal on S1n), [0054] (pixel receives first scan signal on S1n), [0062]-[0064] (first scan signal supplied on S1n). EX1002, ¶82.

#### 4. [1c]

Kim406 discloses "a second scan line (S2n) for transmitting a second scan signal (second scan signal)." EX1002, ¶83.

EX1004, Fig. 5 (Scan Driving Part 210), Fig. 6 (S2n), Fig. 7 (S2n), [0048]

(scan driving part 210 transmits second scan signal on S2n), [0054] (pixel receives second scan signal on S2n), [0062]-[0064] (second scan signal supplied on S2n). EX1002, ¶84.

#### 5. [1d]

Kim406 discloses "a transmission line (En) for transmitting an emission signal (emission control signal)." EX1002, ¶85.

EX1004, Fig. 5 (Scan Driving Part 210), Fig. 6 (En), Fig. 7 (En), [0048] (scan driving part 210 transmits emission control signal on En), [0062]-[0063], [0067] (emission control signal). EX1002, ¶86.

# 6. [1e]

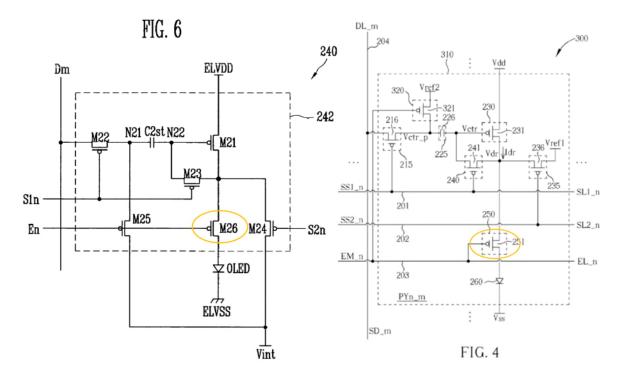

Kim406 discloses "an input unit (M22), electrically connected to the data line (Dm) and the first scan line (S1n), for outputting a preliminary control voltage (outputting preliminary control voltage to node N21) according to the data signal (data signal on Dm) and the first scan signal (first scan signal on S1n)." EX1002, ¶87.

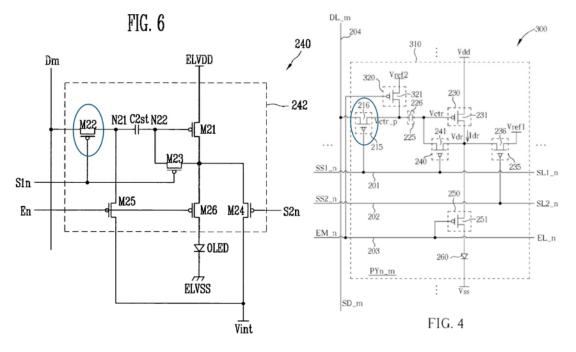

Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M22 is a PMOS transistor with a gate coupled to S1n, a first electrode coupled to the data line Dm, and a second electrode coupled to first node N21, such that during T2 and T3, M22 outputs a preliminary control voltage to the first node N21 according to the data signal on Dm and the low first scan signal on S1n. EX1004, Figs. 6-7, [0055], [0063] (PMOS), [0064] (T2 and T3). The second electrode of M22 is electrically connected to the voltage adjustment unit (M25) and couple unit (C2st). *Id.*, Fig. 6, [0055], [0059], [0061]. Under 112f, Kim406's PMOS transistor M22 as connected performs the claimed function and is identical to the corresponding structure for the input unit 215 (PMOS transistor 216 as connected). EX1001, Fig. 4, 4:34-38; EX1002, ¶88.

#### 7. [1f]

Kim406 discloses "a voltage adjustment unit (M25), electrically connected to the transmission line (En) and the input unit (M22), for adjusting the preliminary control voltage (voltage at N21) according to the emission signal (emission control signal on En) and a second reference voltage (Vint)." EX1002, ¶89.

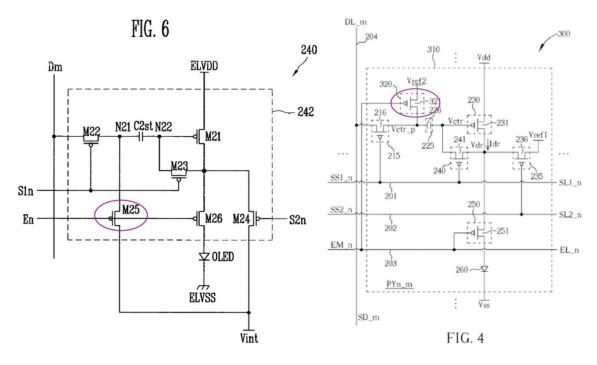

Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M25 is a PMOS transistor with a gate coupled to En, a first electrode connected to M22 and C2st (first node N21), and a second electrode coupled to initialization power source Vint, such that during T5, M25 adjusts the preliminary control voltage (voltage on first node N21) according to the low emission control signal on En and Vint. EX1004, Figs. 6-7, [0059], [0063] (PMOS), [0067] (when the fifth transistor M25 is turned on, the voltage value of

the first node N21 is reduced to the voltage value of the initialization power source Vint). *See* EX1001, 5:47-52, 6:43-48. Under 112f, Kim406's PMOS transistor M25 as connected performs the claimed function and is identical to the corresponding structure for the voltage adjustment unit 320 disclosed in the 757 patent (PMOS transistor 321 as connected). EX1001, Fig. 4, 6:36-42; EX1002, ¶90.

Kim406 discloses M25 is connected to "Vint" while the corresponding structure 321 is connected to "Vref2," but this difference in naming convention is not relevant. Vint in Kim406 is a reference voltage, which is all that is required under the primary construction. Under the alternative construction, see below for [1i]. EX1002, ¶91.

#### 8. [1g]

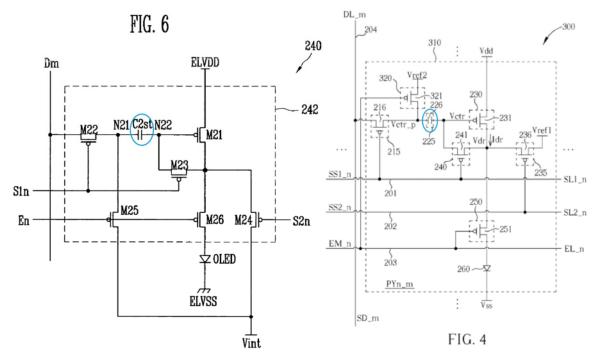

Kim406 discloses "a couple unit (C2st), electrically connected to the input unit (M22) and the voltage adjustment unit (M25), for adjusting a control voltage (voltage on N22) through coupling a change of the preliminary control voltage (capacitor C2st couples the change of the preliminary control voltage at N21 to adjust the voltage at N22)." EX1002, ¶92.

U.S. Patent No. 8,502,757 Petition for *Inter Partes* Review

Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses storage capacitor C2st is between N21 and N22 and is charged during T3 to the voltage difference between N21 and N22. EX1004, Fig. 6, [0061], [0065]. N22 is floated in T4 and T5 by turning off M23, and in T5 when the preliminary control voltage at N21 is changed from the preliminary data signal voltage by application of Vint (*see* [1f]), capacitor C2st couples that change in voltage to N22, causing the voltage on N22 to change by the same amount. *Id.*, Fig. 7, [0066] (T4 turns off M22 and M23), [0067] (reducing voltage of N21 from data to Vint, and adjusting voltage of N22 with a reduction corresponding to the reduction of N21 to maintain a difference in C2st), [0069], claims 7 (second terminal (N22) floats), 8 (explaining how voltage at second terminal of capacitor

(N22) is reduced corresponding to the voltage drop at first terminal (N21)). EX1002, ¶93.

Under 112f, Kim406's capacitor C2st as connected performs the claimed function and is identical to the corresponding structure for the couple unit 225 in the 757 patent (capacitor 226 as connected). EX1001, Fig. 4, 4:42-44. EX1002, ¶94.

# 9. [1h]

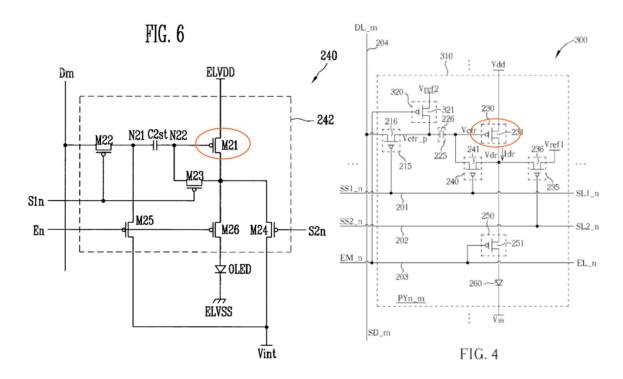

Kim406 discloses "a driving unit (M21), electrically connected to the couple unit (C2st), for providing a driving current and a driving voltage (current and voltage at second electrode of M21), according to the control voltage (voltage at N22) and a first power voltage (ELVDD)." EX1002, ¶95.

#### U.S. Patent No. 8,502,757

Petition for Inter Partes Review

Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M21 is a PMOS transistor with a gate coupled to C2st via node N22, a first electrode coupled to ELVDD, and a second electrode coupled to an unlabeled node with M23, M24, and M26, such that during T5 when M21 is turned on by the control voltage at N22 and EN turns on M26, M21 provides a driving current and driving voltage at its second electrode. EX1004, Figs. 6-7, [0056], [0063] (PMOS), [0067]-[0070] (describing M21 driving OLED through M26). Under 112f, Kim406's PMOS transistor M21 as connected performs the claimed function and is identical to the corresponding structure for the driving unit disclosed in the 757 patent (PMOS transistor 231 as connected). EX1001, Fig. 4, 4:38-41. EX1002, ¶96.

Kim406 explicitly discloses that M21 provides a driving current at its second electrode which, during T5 when M26 is on, will drive the OLED. EX1004, Fig. 7, [0056], [0067]-[0070]. And Kim406 discloses that driving current provided by M21 is provided according to ELVDD and the control voltage at N22 applied to the gate of M21. *Id.*; EX1002, ¶97.

Kim406 inherently discloses that M21 provides a "driving voltage." A POSITA would have known it was inherent from the electrical properties of Kim406's circuit that M21 is also providing a driving voltage with the driving current. To provide a driving current as disclosed in Kim406 a POSITA would

have known that there must also be a driving voltage, i.e., the difference in potential between the second electrode of M21 and ELVSS. A POSITA would have known that without that difference in potential, there would be no driving current as disclosed in Kim406 and the OLED would not emit light. A POSITA would have known that the precise magnitude of the driving voltage provided by M21 would be ELVDD minus the voltage drop across M21. EX1004, [0065], [0069]; EX1002, ¶98 (explaining diode equation).

#### 10. [1i]

Kim406 discloses "a first reset unit (M24), electrically connected to the driving unit (M21) and the second scan line (S2n), for resetting the driving voltage (voltage at second electrode of M21) according to the second scan signal (S2n) and a first reference voltage (Vint)." EX1002, ¶99.

U.S. Patent No. 8,502,757 Petition for *Inter Partes* Review

Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M24 is a PMOS transistor with a gate coupled to S2n, a first electrode coupled to the second electrode of M21 (and first electrode of M23 and first electrode of M26), and a second electrode coupled to the initialization power source Vint, such that during T2 when M24 is turned on by the second scan signal on S2n, it resets the driving voltage at the second electrode of M21 to Vint. EX1004, Figs. 6-7, [0058], [0063] (PMOS), [0064] (disclosing how during T2 M24 provides Vint to the node including the second electrode of M21, so that M23 can provide Vint to N22). *See* EX1001, 5:16-22. Vint provides a first reference voltage for M24 and a second reference voltage for M25 under the primary construction that encompasses the same voltage. Under 112f, Kim406's PMOS

transistor M24 as connected performs the claimed function and is identical to the corresponding structure for the first reset unit disclosed in the 757 patent (PMOS transistor 236 as connected). EX1001, Fig. 4, 4:44-48. EX1002, ¶100.

Kim406 discloses M24 is connected to "Vint" while the corresponding structure 326 is connected to "Vref1," but this difference in naming convention is not relevant. Vint in Kim406 is a reference voltage, which is all that is required under the primary construction. EX1002, ¶101.

### 11. [1j]

Kim406 discloses "a second reset unit (M23), electrically connected to the driving unit (M21), the first reset unit (M24), and the first scan line (S1n), for resetting the control voltage (voltage at N22) according to the first scan signal (S1n) and the driving voltage (voltage at second electrode of M21)." EX1002, ¶102.

U.S. Patent No. 8,502,757 Petition for *Inter Partes* Review

Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M23 is a PMOS transistor with a gate coupled to S1n, a first electrode coupled to the second electrode of M21 (and M24 and M26), and a second electrode coupled to the gate of the M21 and C2st (N22), such that when M23 is turned on by the first scan signal on S1n, the driving voltage (voltage at second electrode of M21) is applied to reset the control voltage at N22. EX1004, Figs. 6-7, [0057], [0063]-[0065]. EX1002, ¶103.

During T2, the control voltage (N22) is reset according to low scan signal (S1n) and the driving voltage Vint (voltage at second electrode of M21). Specifically, S1n and S2n are supplied turning M23 and M24 on, such that the voltage on Node N22 is reset to Vint. EX1004, Figs. 6-7, [0064]; EX1002, ¶104.

# U.S. Patent No. 8,502,757

Petition for Inter Partes Review

During T3, the control voltage (N22) is reset according to low scan signal (S1n) and the driving voltage ELVDD-|Vth| (voltage at second electrode of M21). Specifically, S1n is still supplied keeping M23 on, but S2n is not supplied and M24 is turned off, such that the voltage on Node N22 is reset to ELVDD-|Vth|. EX1004, Figs. 6-7, [0065] (disclosing how current flows through M21 as a diode until "the voltage value of the second node N22 is obtained by subtracting the threshold voltage value of the first transistor M21 from the voltage value of the first power source ELVDD"). Kim406 discloses this reset is performed to compensate for the threshold voltage of M21. *Id.*, [0067]-[0069]; EX1002, ¶105.

Kim406's disclosure in this regard is identical to the disclosure of the 757 patent wherein during T1, Vctrl is reset to Vref1 through 236 and 241 to ensure the driving transistor is in a conductive state, and during T2, Vctrl is reset to VDD-|Vth| through 241 to compensate for the threshold voltage of the driving transistor. EX1001, Fig. 3, 5:15-22 (T1), 5:23-38 (T2). EX1002, ¶106.

Under 112f, Kim406's PMOS transistor M23 as connected performs the claimed function and is identical to the corresponding structure for the second reset unit disclosed in the 757 patent (PMOS transistor 241 as connected). EX1001, Fig. 4, 4:48-52. EX1002, ¶107.

### 12. [1k]

Kim406 discloses "an organic light emitting diode (OLED) for generating output light according to the driving current." EX1002, ¶108.

Kim406 discloses that the OLED is driven by the driving current provided by M21 to generate output light. EX1004, Fig. 6, [0052]-[0054], [0056], [0060], [0067]-[0070]. The amount of control voltage at N22 on the gate of M21 determines the amount of driving current M21 provides and, therefore, the brightness of the OLED. *Id.* EX1002, ¶109.

# 13. [11]

Kim406 discloses "an emission enable unit (M26), electrically connected to the transmission line (En), the driving unit (M21), and the organic light emitting diode (OLED), for providing a control of furnishing the driving current to the

organic light emitting diode according to the emission signal (En)." EX1002,

¶110.

Annotated Kim406 Figure 6 (left) and 757 patent Figure 4 (right) are shown above. Kim406 discloses M26 is a PMOS transistor with a gate coupled to En, a first electrode coupled to the second electrode of M21 (and M23 and M24), and a second electrode coupled to the anode of the OLED, such that during T5 when M26 is turned on by the emission control signal on En, it furnishes the driving current from the second electrode of M21 to the OLED. EX1004, Figs. 6-7, [0060], [0063] (PMOS), [0067]-[0070] (disclosing how during T5 the low emission control signal causes M26 to turn on such that the driving current from the second electrode of M21 flows through M26 and drives the OLED). Under 112f, Kim406's PMOS transistor M26 as connected performs the claimed function and is

identical to the corresponding structure for the emission enable unit disclosed in the 757 patent (PMOS transistor 251 as connected). EX1001, Fig. 4, 4:54-58. EX1002, ¶111.

#### B. Claim 2:

Kim406 discloses claim 1 "wherein the input unit (M22) comprises a first transistor (M22), the first transistor having a first end (first electrode) electrically connected to the data line (Dm), a gate end electrically connected to the first scan line (S1n), and a second end (second electrode) electrically connected to the voltage adjustment unit (M25) and the couple unit (C2st)." *See* [1e]. EX1002, ¶112.

### C. Claim 3:

Kim406 discloses claim 2, "wherein the first transistor (M22) comprises a thin film transistor or a field effect transistor (PMOS or NMOS)." EX1002, ¶113.

Kim406 discloses its transistors are PMOS or NMOS transistors. EX1004, [0026], [0063]. A POSITA would have known that PMOS and NMOS transistors are types of field effect transistors (FETs). Specifically, a POSITA would have known that PMOS and NMOS transistors are types of MOSFETs. EX1007, page 23; EX1002, ¶114.

### D. Claim 4:

Kim406 discloses claim 1, "wherein the driving unit (M21) comprises a second transistor (M21), the second transistor (M21) having a first end (first

electrode) for receiving the first power voltage (ELVDD), a gate end for receive the control voltage (N22), and a second end (second electrode) for outputting the driving current and the driving voltage. *See* [1h]. EX1002, ¶115.

### E. Claim 5:

See Claim 3, 4. EX1002, ¶116.

# F. Claim 6:

Kim406 discloses claim 1 "wherein the couple unit (C2st) comprises a capacitor (C2st) electrically connected between the input unit (M22) and the driving unit (M21). *See* [1g]. EX1002, ¶117.

# G. Claim 7:

Kim406 discloses claim 1 "wherein the first reset unit (M24) comprises a third transistor (M24), the third transistor having a first end (second electrode) for receiving the first reference voltage (Vint), a gate end electrically connected to the second scan line (S2n), and a second end (first electrode) electrically connected to the drive unit (M21), the second reset unit (M23) and the emission enable unit (M26). *See* [1i], [1j]-[11]; EX1002, ¶118.

### H. Claim 8:

See Claim 3, 7. EX1002, ¶119.

# I. Claim 9:

Kim406 discloses claim 1 "wherein the second reset unit (M23) comprises a fourth transistor (M23), the fourth transistor having a first end (first electrode)

# U.S. Patent No. 8,502,757

Petition for Inter Partes Review

electrically connected to the driving unit (second electrode of M21), the first reset unit (M24) and the emission enable unit (M26), a gate end electrically connected to the first scan line (S1n), and a second end (second electrode) electrically connected to the couple unit (C2st) and the driving unit (gate of M21). *See* [1j], [1h]-[11]. EX1002, ¶120.

### J. Claim 10:

*See* Claim 3, 9. EX1002, ¶121.

### K. Claim 11:

Kim406 discloses claim 1 "wherein the voltage adjustment unit (M25) comprises a fifth transistor (M25), the fifth transistor having a first end for receiving the second reference voltage (Vint), a gate end electrically connected to the transmission line (En), and a second end electrically connected to the input unit (M22) and the couple unit (C2st)." *See* [1f], [1e]-[1g]. EX1002, ¶122.

### L. Claim 12:

See Claim 3, 11. EX1002, ¶123.

### M. Claim 14:

Kim406 discloses claim 1 "wherein the emission enable unit (M26) comprises a sixth transistor (M26), the sixth transistor having a first end electrically connected to the driving unit (M21), the first reset unit (M24) and the second reset unit (M23), a gate end electrically connected to the transmission line

(En), and a second end electrically connected to the organic light emitting diode (OLED). *See* [11], [1e], [1h], 7, 9. EX1002, ¶124.

### N. Claim 15:

See Claim 3, 14. EX1002, ¶125.

### **O.** Claim 16:

Kim406 discloses claim 1 "wherein the organic light emitting diode (OLED) comprises an anode electrically connected to the emission enable unit (M26) and a cathode for receiving a second power voltage (ELVSS)." *See* [1k]; EX1004, Fig. 6, [0053] ("The anode electrode of the OLED is coupled to the pixel circuit 242 and the cathode electrode of the OLED is coupled to the second power source ELVSS."); EX1002, ¶126.

#### **P.** Claim 17:

#### 1. [17pre]

Kim406 discloses "a driving method, comprising." Kim406 discloses the pixel circuit in Figure 6 to drive an OLED as shown above. *See* Claim 1. Kim406 discloses in Figure 7 "a method of driving the pixel" of Figure 6. EX1004, Fig. 7, [0021]; EX1002,  $\P$ 17.

### **2.** [17a]

Kim406 discloses "outputting a preliminary control voltage (voltage at N21) by an input unit (M22) according to a data signal (data signal on Dm) and a first scan signal (first scan signal on S1n)." *See* [1e]; EX1002, ¶128.

### 3. [17b]

Kim406 discloses "adjusting the preliminary control voltage (voltage on N21) by a voltage adjustment unit (M25) according to an emission signal (emission control signal on En) and a second reference voltage (Vint)." *See* [1f]; EX1002, ¶129.

# 4. [17c]

Kim406 discloses "adjusting a control voltage (adjusting voltage on N22) by a couple unit (C2st) through coupling a change of the preliminary control voltage (capacitor C2st couples the change of the preliminary control voltage at N21 to the voltage at N22)." *See* [1g]; EX1002, ¶130.

### 5. [17d]

Kim406 discloses "providing a driving current and a driving voltage (current and voltage at second electrode of M21) by a driving unit (M21) according to the control voltage (voltage at N22) and a power voltage (ELVDD)." *See* [1h]; EX1002, ¶131.

### 6. [17e]

Kim406 discloses "resetting the driving voltage (voltage at second electrode of M21) by a first reset unit (M24) according to a second scan signal (S2n) and a first reference voltage (Vint)." *See* [1i]; EX1002, ¶132.

# 7. [17f]

Kim406 discloses "resetting the control voltage (voltage at N22) by a second reset unit (M23) according to the first scan signal (S1n) and the driving voltage (voltage at second electrode of M21)." *See* [1j]; EX1002, ¶133.

# 8. [17g]

Kim406 discloses "generating output light by an organic light emitting diode (OLED) according to the driving current (current at second electrode of M21)." *See* [1k]; EX1002, ¶134.

# 9. [17h]

Kim406 discloses "providing a control of furnishing the driving current to the organic light emitting diode (OLED) by an emission enable unit (M26) according to the emission signal (En)." *See* [11]; EX1002, ¶135.

# 10. [17i]

Kim406 discloses "providing the first scan signal (S1n) with a first level (low) to the input unit (M22) and the second reset unit (M23), providing the second scan signal (S2n) with the first level (low) to the first reset unit (M24), providing the emission signal (En) with a second level (high) different from the first level (low) for disabling a voltage adjusting operation of the voltage adjustment unit (M25) and disabling a current furnishing operation of the emission enable unit (M26), and providing the data signal (Dm) to the input unit (M22) during a first interval (T2)." *See* [1e]-[1f], [1i]-[1j], [11]; EX1004, Fig. 7 (at T2 showing S1n Petition for *Inter Partes* Review low, S2n low and En high), [0063]-[0064] (explaining that in T2 low signals on S1n and S2n turn on PMOS transistors M22, M23, M24 and high signal on En turns off PMOS transistors M25 and M26), [0026]; EX1002, ¶136 (explaining PMOS/NMOS).

U.S. Patent No. 8,502,757

### 11. [17j]

Kim406 discloses "outputting the preliminary control voltage by the input unit (M22) according to the data signal (Dm) and the first scan signal (S1n) during the first interval (T2)." *See* [1e] (M22), [17a] (same), [17i] (T2); EX1002, ¶137.

### 12. [17k]

Kim406 discloses "resetting the driving voltage by the first reset unit (M24) according to the second scan signal (S2n) and the first reference voltage (Vint) during the first interval (T2)." *See* [1i] (M24), [17e] (same), [17i] (T2); EX1002, ¶138.

### 13. [17l]

Kim406 discloses "resetting the control voltage by the second reset unit (M23) according to the first scan signal (S1n) and the driving voltage (voltage at second electrode of M21) during the first interval (T2)." *See* [1j] (M23), [17f] (same), [17i] (T2); EX1002, ¶139.

# 14. [17m]

Kim406 discloses "switching the second scan signal (S2n) from the first level (low) to the second level (high) for disabling a resetting operation of the first reset unit (M24) during a second interval (T3) following the first interval (T2)." *See* EX1004, Fig. 7 (T3), [0063]-[0065] (explaining during T3 S2n goes high turning off PMOS transistor M24); EX1002, ¶140.

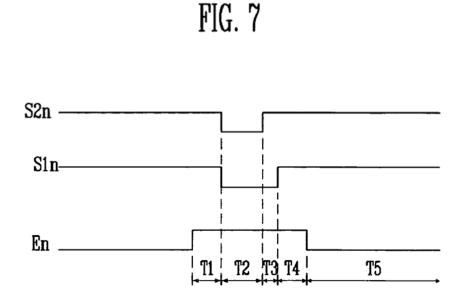

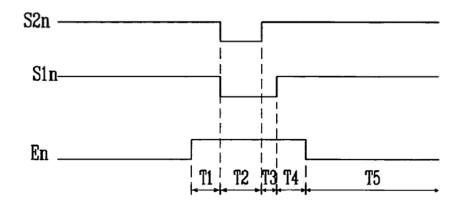

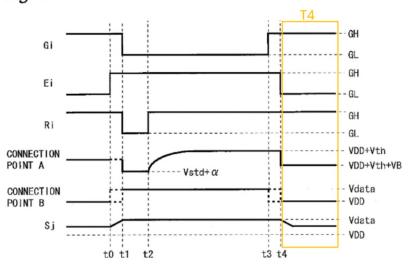

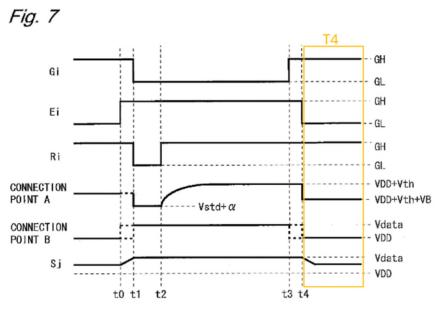

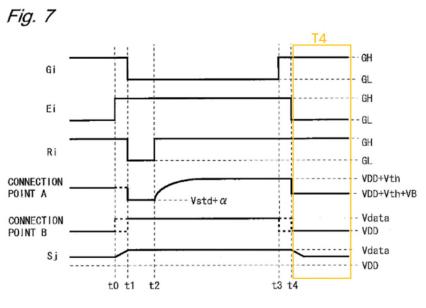

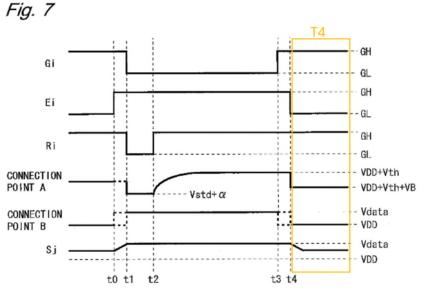

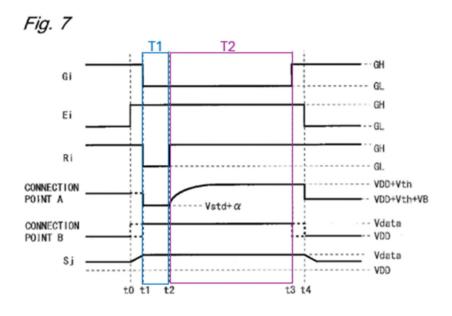

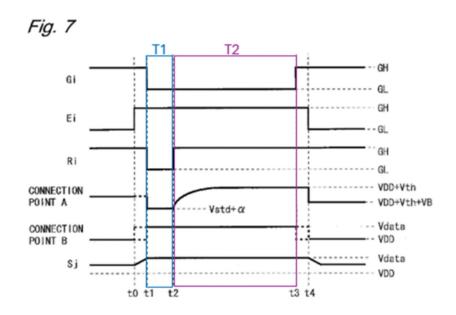

FIG. 7

### 15. [17n]

Kim406 discloses "performing a threshold voltage compensation operation on the control voltage (voltage at N22) by the second reset unit (M23) and the driving unit (M21) according to the first scan signal (S1n) and the power voltage (ELVDD) during the second interval (T3)." *See* [1j] (explaining voltage compensation), [17f]; EX1004, [0065] (explaining that during T3, M21 serves as a diode such that a voltage according to ELVDD minus the threshold voltage of M21 is applied to N22), [0069] (explaining how this achieves voltage threshold compensation such that correct brightness is created "regardless of the threshold voltage" of M21); EX1002, ¶141.

### **16.** [170]

Kim406 discloses "switching the first scan signal (S1n) from the first level (low) to the second level (high) for disabling a resetting operation of the second reset unit (M23) and disabling an inputting operation of the input unit (M22) during a third interval (T4) following the second interval (T3)." EX1004, Fig. 7, [0066] (explaining that during T4, S1n goes high turning off PMOS transistors M22 and M23); EX1002, ¶142.

. .....

FIG. 7

17. [17p]

Kim406 discloses "switching the emission signal (En) from the second level (high) to the first level (low) during a fourth interval (T5) following the third interval (T4)." *See* [11]; EX1004, Fig. 7, [0067]-[0069]; EX1002, ¶143.

FIG. 7

### **18.** [17q]

Kim406 discloses "adjusting the preliminary control voltage (voltage at N21) by the voltage adjustment unit (M25) according to the emission signal (En) and the second reference voltage (Vint) during the fourth interval (T5)." *See* [1f] (M25), [17b] (same); EX1004, Fig. 7, [0067] (explaining En going low turns on PMOS transistor M25 such that N21 is changed by applying Vint); EX1002, ¶144.

### 19. [17r]

Kim406 discloses "adjusting the control voltage (adjusting the voltage at N22) by the couple unit (C2st) through coupling a change of the preliminary control voltage (coupling change in voltage at N21 to adjust the voltage at N22 by same amount) during the fourth interval (T5)." *See* [1g] (C2st), [17c] (same); EX1004, Fig. 7, [0067] (explaining C2st couples the change in N21 to N22 during T5); EX1002, ¶145.

### **20.** [17s]

Kim406 discloses "providing the driving current (current provided on second electrode of M21) by the driving unit (M21) according to the control voltage (voltage at N22) and the power voltage (ELVDD) during the fourth interval (T5)." *See* [1h] (M21), [17d]; EX1004, [0067-[0069] (explaining during T5 M21 provides driving current to drive OLED according to the voltage at N22 and ELVDD); EX1002, ¶146.

# 21. [17t]

Kim406 discloses "furnishing the driving current to the organic light emitting diode (OLED) by the emission enable unit (M26) according to the emission signal (En) during the fourth interval (T5)." *See* [11] (M26), [17e]; EX1004, Fig. 7, [0067]-[0069] (explaining that during T5 En goes low turning PMOS transistor M26 on to provide driving current to OLED); EX1002, ¶147.

# 22. [17u]

Kim406 discloses "generating output light by the organic light emitting diode (OLED) according to the driving current during the fourth interval (T5)." *See* [1k] (OLED), [17g] (same); EX1004, [0068]-[0069] (OLED generates light according to driving current during T5); EX1002, ¶148.

### **Q.** Claim 18:

Kim406 discloses the method of claim 17, "wherein the second level (high) is greater than the first level (low)." *See* [17i]; EX1002, ¶149.

### **R.** Claim 19:

Kim406 discloses the method of claim 17, "wherein the first level (high) is greater than the second level (low)." EX1002, ¶150.

As shown above, Kim406 discloses PMOS transistors with a second level (high-turn off) voltage which is greater than the first level (low-turn on) voltage. *See* [17i] (PMOS), 18; EX1002, ¶151.

# U.S. Patent No. 8,502,757

Petition for Inter Partes Review

Claim 19 reverses the levels, such that the first level (high-turn on) is greater than the second level (low-turn off). Kim406 discloses the PMOS transistors, which are turned on by low gate voltages and off by high gate voltages, can instead be NMOS transistors, which are turned on by high gate voltages and off by low gate voltages. EX1004, [0063] (NMOS uses the different signals). A POSITA would have been familiar with PMOS and NMOS transistors and known they were turned on and off by opposite gate voltages. Thus, Kim406 teaches that its PMOS embodiment can be implemented as an NMOS embodiment using the opposite gate voltages. EX1002, ¶152.

In Kim406's NMOS embodiment the voltage levels shown in Figure 7 would have been reversed to maintain the same functionality, i.e., the second level that turns the transistors off during the correct time periods would be low and the first level that turns the transistors on during the correct time periods would be high. Thus, in Kim406's NMOS embodiment, the first level (on, high) is greater than the second level (off, low). EX1002, ¶153.

# VI. GROUND 2: CLAIMS 1-20 ARE OBVIOUS OVER THE COMBINATION OF KIM406 AND KIM730

Kim406 discloses the second reference voltage is Vint. *See* [1f]. It would have been obvious to a POSITA that Vint could have been ELVDD, the first power voltage. EX1002, ¶154.

### A. Combination Rationale

Kim730 shares the common inventor with Kim406 and discloses similar OLED pixel driving circuits. EX1002, ¶155.

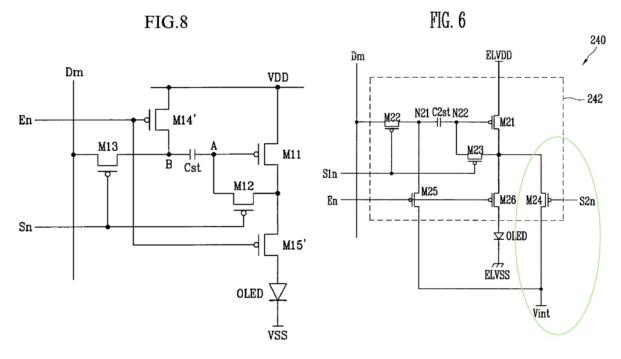

Above are Figure 8 (left) of Kim730 and Figure 6 (right) of Kim406. The differences in the circuits are 1) Kim730's voltage adjustment unit (M14') is connected to VDD while Kim406's (M25) is connected to Vint and 2) Kim406 includes a first reset unit M24 for resetting the driving voltage using S2n, first reference voltage Vint and also as a second reference voltage Vint for M25. EX1002, ¶156.

It would have been obvious to a POSITA to modify the adjustment unit in Kim406 (M25) to use VDD as the reference voltage, instead of Vint, based on the teachings of Kim730. Kim730 explains how the voltage adjustment unit M14' can

be connected to VDD to make a voltage adjustment. EX1005, Figs. 7-8, [0052]-[0060], [0067]. Kim730 explains how M14' can be connected to a third voltage "V<sub>sus</sub>" to make a voltage adjustment. *Id.*, Fig. 10 [0062]-[0068]. Thus, a POSITA would have understood each of these options was a known design choice. And because it was known to connect voltage adjustment units to VDD, VSS, or a third voltage source, none of those design choices is novel or non-obvious. In the combination a POSITA would have also understood to continue to use Vint (instead of VDD) at M24 to ensure M23 and M24 ensure M21 is put in a conductive state for reset as disclosed by Kim406 and because the voltage value of the "initialization power source Vint is set to be smaller than the voltage value of the data signal" which would not be true for VDD. EX1004, [0064]; EX1002, ¶157.

A POSITA would also have been motivated to use different reference voltage sources for each unit in order to use the optimum reference voltage for that unit to improve the efficiency and performance of the pixel circuit. Each of these voltage adjustments is different. Thus, using a reference voltage that is tailored to each particular desired voltage adjustment would improve the speed of the pixel circuit and reduce the overall power consumption of the pixel circuit. It was known that using different reference voltage sources would also reduce the voltage swing for driving the OLED display. A POSITA would have known of these

advantages and how significant they can become for large displays with thousands of pixels. EX1002, ¶158.

A POSITA would have had a reasonable expectation of success in making the modification. Kim730 teaches it was a known technique in the art to use VDD to perform a positive voltage adjustment and that each of the design choices could be used for a circuit. EX1004, Figs. 6-10 and accompanying text. EX1002, ¶159.

### B. Claims 13, 20

The combination discloses "the organic light emitting display of claim 11, wherein the second reference voltage is the first power voltage" (claim 13) and "the driving method of claim 17, wherein the second reference voltage is the power voltage" (claim 20). *See* Ground 1, claims 11 and 17. In this combination, Kim406's voltage adjustment unit (M25) would have been connected to the first power voltage ELVDD in Kim406, based on the teachings in Kim730 as explained above. *See* [1f] (M25 connected to Vint), 11 (same); EX1005, Figs. 7-8, [0052]-[0061]; EX1002, ¶160.

### C. Claims 1-20

Under the alternative construction that requires the first and second voltages in independent claims 1 and 17 to be different voltages, claims 1-20 are rendered obvious by the combination because, in the combination, the first reference voltage

is still Vint as taught by Kim406, while the second reference voltage has been changed to VDD as taught by Kim730 as explained above. EX1002, ¶161.

### VII. GROUND 3: CLAIMS 1-21 ARE ANTICIAPTED BY SENDA

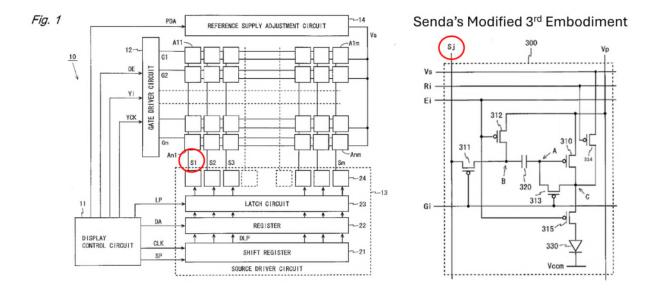

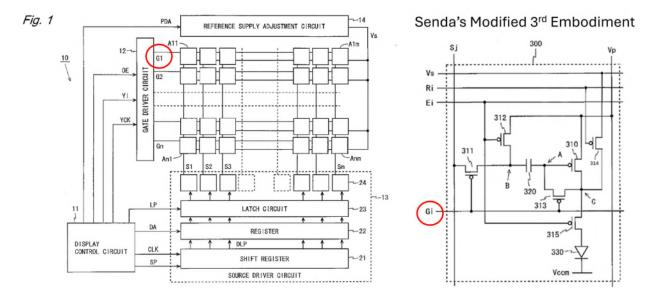

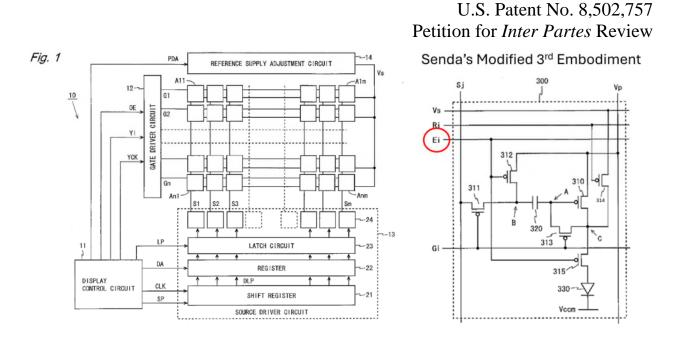

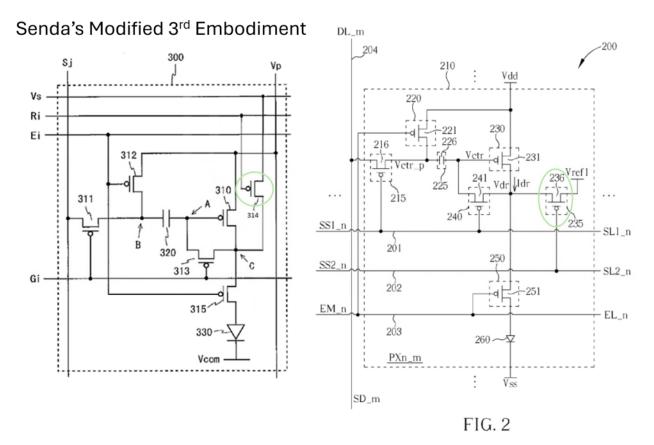

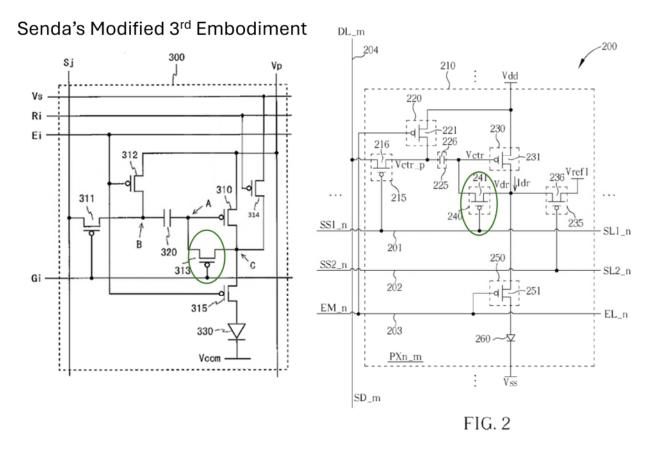

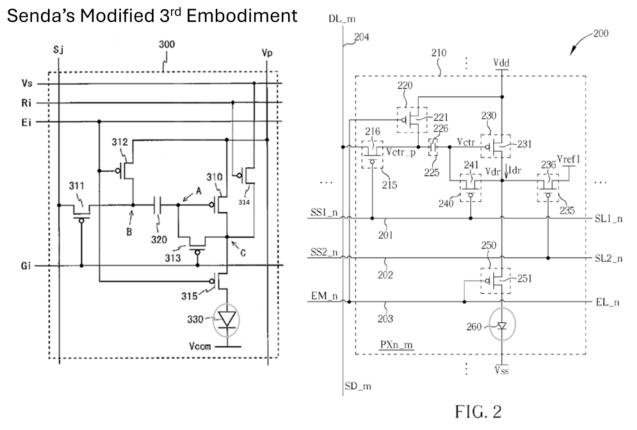

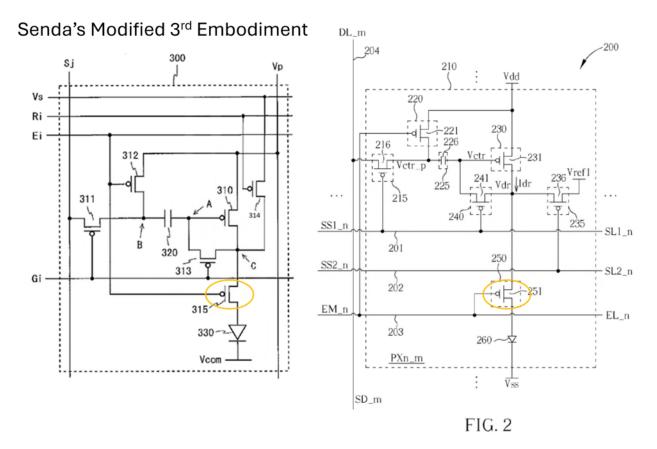

### A. Senda's Modified Third Embodiment

Senda anticipates the claims because Senda expressly discloses a modified third embodiment that practices the claims, thereby disclosing to a POSITA within its four corners all elements of the claims as arranged in the claims. Specifically, Senda discloses its third embodiment (Fig. 6) should be modified as explained with respect to the seventh embodiment (Fig. 15) by connecting the PMOS transistor 314 shown in Figure 6 to Node C as illustrated by transistor 714 in Figure 15. EX1006, [0218]-[0219]. Senda discloses the modification initially with reference to the fifth embodiment (Fig. 11) by explaining that the first reset transistor connected to Node A (as showing in Fig. 11) should instead be connected to Node C (as shown in Fig. 15). Id. Senda explains this modification reduces leakage at Node A and thereby enhances display quality. Id. Senda then discloses this modification should also be made for embodiments 1-4 and 6. Id. Senda discloses no other modification should be made to the third embodiment, other than to move the connection of the relevant transistor (PMOS transistor 314 in the case of the third embodiment) from Node A to Node C. Id. Senda claims the modified third embodiment in dependent claim 5. Id., claim 1 (claiming fourth switching element

in either position), claim 3 (claiming position of third embodiment), claim 5 (claiming position of modified third embodiment). Thus, Senda's "Modified 3rd Embodiment" can also be referred to as Senda's "claim 5 embodiment." EX1002, ¶162.

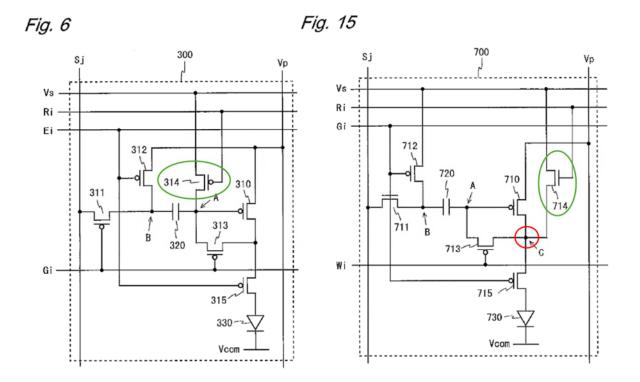

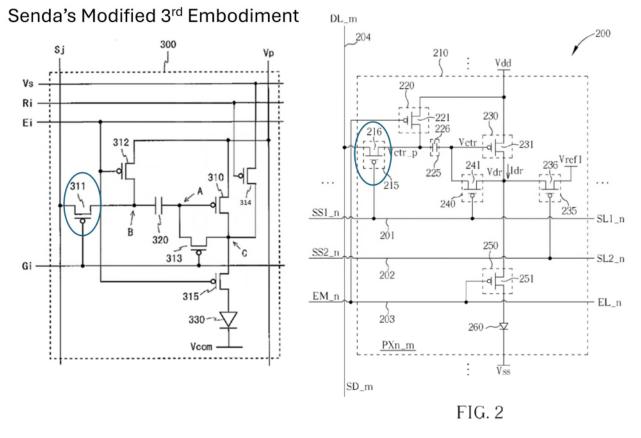

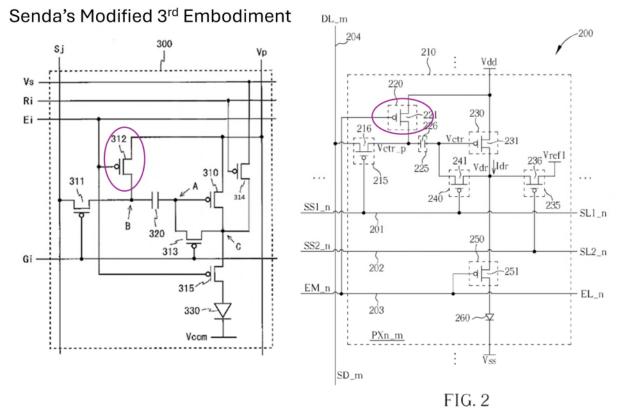

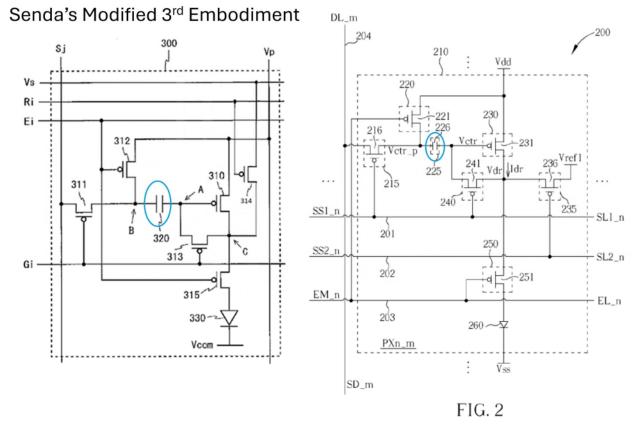

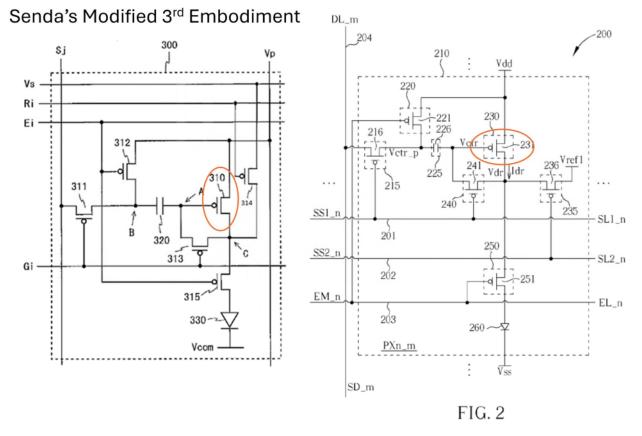

Figures 6 and 15 of Senda are shown below with annotations highlighting transistors 314 and 714. EX1002, ¶163.

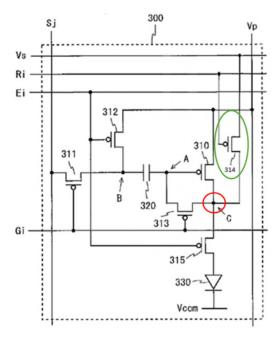

A modified Figure 6 is shown below, which illustrates Senda's Modified 3rd Embodiment with PMOS transistor 314 connected to Node C, with no other changes to the third embodiment, as disclosed and claimed by Senda. EX1006, [0218]-[0219]; EX1002, ¶164.

Senda's Modified 3<sup>rd</sup> Embodiment

This modification of Figure 6 illustrating Senda's Modified 3rd Embodiment will be used in the analysis of the claims below. Evidentiary citations will still be made to the original Figure 6 transistor 314, as well as Senda's disclosure to connect that transistor to Node C. EX1002, ¶165.

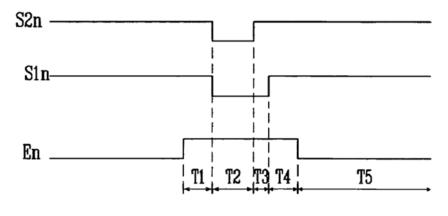

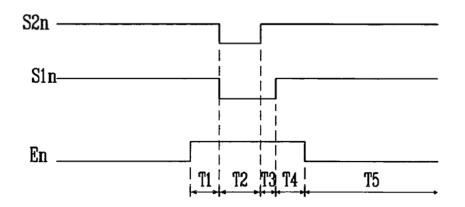

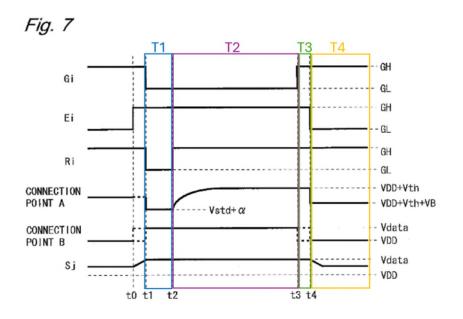

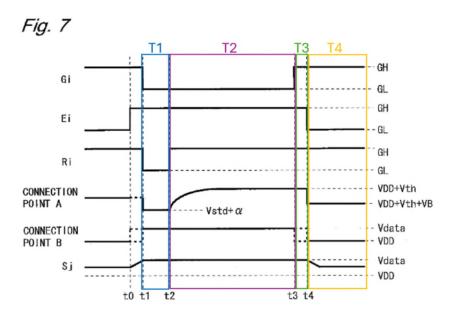

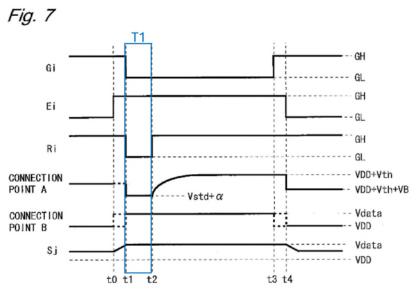

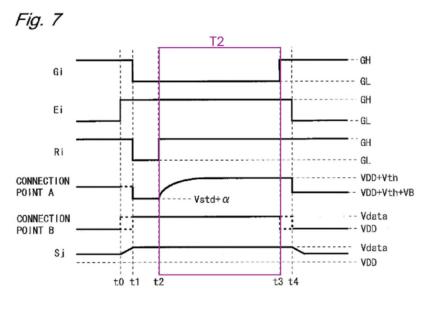

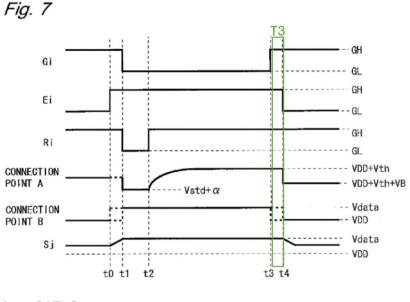

Based on Senda's disclosure that the only modification that should be made to the third embodiment is to connect the transistor to Node C, a POSITA would have understood the Modified 3rd Embodiment to still use the timing chart of Figure 7. Furthermore, a POSITA would have understood Figure 7 to still provide the relevant timing diagram for the Modified 3<sup>rd</sup> Embodiment because when reset transistor 314 is connected to Node C it would still perform its function during T1 of resetting the voltage at Node A to "a little higher" than Vstd to ensure

# U.S. Patent No. 8,502,757

Petition for Inter Partes Review

the driving transistor 310 is in a conductive state, prior to the voltage compensation period in T2. EX1006, [0169]-[0175], [0209]-[0217]. Because Ri turns off 314 in every period except T1, the operation of the circuit is not impacted in any other time period, other than to achieve a reduction of leakage current at Node A as disclosed by Senda. An annotated Figure 7 is shown below adding annotations for time period T1 (time after t1), T2 (time after t2), T3 (time after t3) and T4 (time after t4). This annotated timing diagram will be used in the analysis below. EX1002, ¶¶166-171 (explaining the application of the timing in annotated Figure 7 to the Modified 3rd Embodiment).

### B. Claim 1

# 1. [1pre]

Senda discloses "An organic light emitting display, comprising (see following limitations)." EX1002, ¶172.

EX1006, Figs. 1-16, Abstract, [0001] (invention relates to a display device such as an organic EL display, [0117] ("130 ... 330, and 730: organic EL element"), [0125] ("[a] display device according to each embodiment includes a pixel circuit ... the pixel circuit includes an organic EL element"), [0135]-[0137], [0163], [0209]; EX1002, ¶173.

As discussed above, Senda discloses a Modified 3rd Embodiment, wherein Senda's third embodiment (Figs. 6-7, [0163]-[0174]) is modified as disclosed for the seventh embodiment (Fig. 15, [0209]-[0220]) to connect PMOS transistor 314 to Node C to reduce leakage at Node A. EX1006, [0218]-[0219], claims 1, 3, and 5. Senda discloses figure 1 and [0125]-[0134] apply to each of the first, third, and

seventh embodiments. *Id.*, [0125]-[0127]. Thus, Senda discloses all elements of the challenged claims, as arranged in the claims, as further explained for each limitation below. EX1002, ¶174.

# 2. [1a]

Senda discloses "a data line (Sj) for transmitting a data signal (Vdata)." EX1002, ¶175.

EX1006, Figs. 1 (annotated) (left), 6 (annotated and modified) (right) (data lines Sj are connected to the source driver circuit 13), 7 (data on Sj), [0128]-[0131] (circuit 13 functions as a display signal output circuit that provides potentials according to display data to the data lines Sj), [0124], [0163]-[0164], [0166] (data on Sj), [0169]-[0171] (Vdata on Sj); EX1002, ¶176.

# 3. [1b]

Senda discloses "a first scan line (Gi) for transmitting a first scan signal." EX1002, ¶177.

EX1006, Fig. 1 (annotated) (left) (a plurality of scanning lines Gi), 6 (annotated and modified) (right) (Gi), 7 (GL and GH on Gi), 15 (scanning line Gi), [0123] (Gi: scanning line), [0127]-[0128] (scanning lines Gi ... are connected to the gate driver circuit 12), [0130] (gate driver circuit 12 functions as a scanning signal output circuit that selects a write-target pixel circuit using a corresponding scanning line Gi), [0136]-[0142], [0163]-[0172] (GL and GH on Gi), [0211]-[0212]; EX1002, ¶178.

# 4. [1c]

Senda discloses "a second scan line (Ri) for transmitting a second scan signal." EX1002, ¶179.

#### Petition for Inter Partes Review Fig. 1 Senda's Modified 3rd Embodiment PDA REFERENCE SUPPLY ADJUSTMENT CIRCUIT 300 A1 A1m Si 12 10 61 CIRCUIT 0E 62 DRIVER YI 312 YCK GATE 310 Gn 311 Sm -24 B 320 °C 313 LATCH CIRCUIT 11 -23 Gi DA REGISTER 315 DISPLAY CONTROL CIRCUIT DLP CLK 330 SHIFT REGISTER SP Vcom SOURCE DRIVER CIRCUIT

U.S. Patent No. 8,502,757

EX1006, Fig. 1, Fig. 6 (annotated and modified) (right) (Ri), 7 (GL and GH on Ri), 15 (Ri), [0122] (Wi, Ri, and Ei: control line), [0128] (scanning lines Gi and control lines Wi, Ri, etc. are connected to the gate driver circuit 12), [0130] (output from the logic operation corresponding control lines Wi, Ri, etc.), [0136], [0138]-[0140], [0143]-[0148], [0164]-[0174] (GL and GH on Ri control line), [0211]-[0218]; EX1002, ¶180.

# 5. [1d]

Senda discloses "a transmission line (Ei) for transmitting an emission signal." EX1002, ¶181.

EX1006, Figs. 1, 6 (annotated and modified) (right) (control line Ei), 7 (GL and GH on Ei), [0122] (Wi, Ri, and Ei: control line), [0164] ("[t]he potential of the control line Ei is controlled by the gate driver circuit 12"), [0165]-[0174] (GL and GH on Ei), [0211]-[0218]; EX1002, ¶182.

# 6. [1e]

Senda discloses "an input unit (311), electrically connected to the data line (Sj) and the first scan line (Gi), for outputting a preliminary control voltage (outputting preliminary control voltage to Node B) according to the data signal (data signal on Sj) and the first scan signal (first scan signal on Gi)." EX1002, ¶183.