# UNITED STATES PATENT AND TRADEMARK OFFICE \_\_\_\_\_

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

MEDIATEK, INC. and MEDIATEK USA, INC., Petitioners,

v.

REDSTONE LOGICS LLC, Patent Owners.

IPR2025-00085 U.S. Patent No. 8,549,339

PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 8,549,339

Mail Stop "Patent Board" Patent Trial and Appeal Board U.S. Patent and Trademark Office P.O. Box 1450 Alexandria, VA 22313-1450

# TABLE OF CONTENTS

|      |      | <u>rage</u>                                                                                    |

|------|------|------------------------------------------------------------------------------------------------|

| I.   | MAN  | NDATORY NOTICES1                                                                               |

|      | A.   | Real Party-In-Interest (37 C.F.R. §42.8(b)(1))                                                 |

|      | B.   | Identification of Related Matters (37 C.F.R. §42.8(b)(2))1                                     |

|      | C.   | Counsel and Service Information (37 C.F.R. §§42.8(b)(3) & (b)(4))2                             |

|      | D.   | Payment of Fees (37 C.F.R. §42.103)3                                                           |

| II.  | INTE | RODUCTION3                                                                                     |

| III. | CHA  | TEMENT OF PRECISE RELIEF REQUESTED FOR EACH LLENGED CLAIM/REQUIREMENTS FOR INTER PARTES IEW    |

|      | A.   | Grounds for Standing (37 C.F.R. § 42.104(a))                                                   |

|      | B.   | Claims for Which Review Is Requested (37 C.F.R. § 42.104(b))4                                  |

|      | C.   | Statutory Grounds of Challenge                                                                 |

| IV.  | CLA  | IM CONSTRUCTION6                                                                               |

| V.   | A PE | RSON HAVING ORDINARY SKILL IN THE ART6                                                         |

| VI.  | OVE  | RVIEW OF THE '339 PATENT7                                                                      |

|      | A.   | Purported Invention Of The '339 Patent7                                                        |

|      | B.   | Priority Date9                                                                                 |

| VII. | OVE  | RVIEW OF THE STATE OF THE ART9                                                                 |

|      | A.   | U.S. Patent Application Publication No. 2009/0158078 A1 to Knoth ("Knoth") (Ex[1005])9         |

|      | B.   | U.S. Patent No. 8,122,270 to Allarey et al. ("Allarey") (Ex[1006])11                           |

|      | C.   | U.S. Patent Application Publication No. 2005/0034002 A1 to Flautner ("Flautner") (Ex[1007])    |

|      | D.   | U.S. Patent Application Publication No. 2011/0153984 A1 to Wolfe et al. ("Wolfe") (Ex[1008])   |

|      | A.   | U.S. Patent Application Publication No. 2007/0080696 A1 to Kumar et al. ("Kumar") (Ex[1009])14 |

|       | В. |       | Patent Application Publication No. 2010/0122101 A1 to ger et al. ("Naffziger") (Ex[1010]) | 15 |

|-------|----|-------|-------------------------------------------------------------------------------------------|----|

| VIII. |    | UND 1 | : CLAIMS 1, 5, 8-10, 14 AND 21 ARE OBVIOUS UNDER KNOTH IN VIEW OF ALLAREY                 |    |

|       | A. |       | ation to Combine Knoth and Allarey                                                        |    |

|       | B. |       | .1                                                                                        |    |

|       |    | 1.    | 1[pre]                                                                                    |    |

|       |    | 2.    | 1[a1]                                                                                     |    |

|       |    | 3.    | 1[a2]                                                                                     |    |

|       |    | 4.    | 1[b1]                                                                                     |    |

|       |    | 5.    | 1[b2]                                                                                     |    |

|       |    | 6.    | 1[b3]                                                                                     |    |

|       |    | 7.    | 1[b4]                                                                                     |    |

|       |    | 8.    | 1[c1]                                                                                     |    |

|       |    | 9.    | 1[c2]                                                                                     |    |

|       | C. | Claim | 5                                                                                         | 32 |

|       |    |       | 5[pre]                                                                                    |    |

|       |    | 2.    | 5[a]                                                                                      | 32 |

|       | D. |       | ndent Claim 8                                                                             |    |

|       |    | 1.    | 8[pre]                                                                                    | 36 |

|       |    | 2.    | 8[a]                                                                                      | 37 |

|       | E. | Depen | ndent Claim 9                                                                             | 42 |

|       |    | 1.    | 9[pre]                                                                                    | 42 |

|       |    | 2.    | 9[a]                                                                                      | 42 |

|       | F. |       | ndent Claim 10                                                                            |    |

|       |    | 1.    | 10[pre]                                                                                   | 44 |

|       |    | 2.    | 10[a]                                                                                     |    |

|       | G. | Depen | ndent Claim 14                                                                            |    |

|       |    | 1.    | 14[pre]                                                                                   |    |

|       |    | 2.    | 14[a]                                                                                     |    |

|     | Н.  | Inde  | pendent Claim 21                                                                        | 49 |

|-----|-----|-------|-----------------------------------------------------------------------------------------|----|

|     |     | 1.    | 21[pre]                                                                                 | 49 |

|     |     | 2.    | 21[a1]                                                                                  | 49 |

|     |     | 3.    | 21[a2]                                                                                  | 49 |

|     |     | 4.    | 21[b1]                                                                                  | 51 |

|     |     | 5.    | 21[b2]                                                                                  | 51 |

|     |     | 6.    | 21[b3]                                                                                  | 52 |

|     |     | 7.    | 21[b4]                                                                                  | 52 |

|     |     | 8.    | 21[c1]                                                                                  | 52 |

|     |     | 9.    | 21[c2]                                                                                  | 52 |

| IX. |     |       | 2: CLAIMS 2-4 ARE OBVIOUS UNDER §103 OVER KN<br>AREY IN VIEW OF FLAUTNER                |    |

|     | A.  | Moti  | vation To Combine Knoth, Allarey, And Flautner                                          | 52 |

|     | B.  | Clair | n 2                                                                                     | 54 |

|     |     | 1.    | 2[pre]                                                                                  | 54 |

|     |     | 2.    | 2[a]                                                                                    | 54 |

|     | C.  | Depe  | endent Claim 3                                                                          | 56 |

|     |     | 1.    | 3[pre]                                                                                  | 56 |

|     |     | 2.    | 3[a]                                                                                    | 56 |

|     | D.  | Clair | n 4                                                                                     | 56 |

|     |     | 1.    | 4[pre]                                                                                  | 56 |

|     |     | 2.    | 4[a]                                                                                    | 57 |

| X.  |     |       | 3: CLAIM 6 IS OBVIOUS UNDER §103 OVER KNOTH AT IN VIEW OF WOLFE, AND FURTHER IN VIEW OF |    |

|     | KUN | IAR   |                                                                                         |    |

|     | A.  |       | vation to Combine Knoth, Allarey, and Wolfe                                             |    |

|     | В.  |       | vation to Combine Knoth, Allarey, and Kumar                                             |    |

|     | C.  | Clair | n 6                                                                                     |    |

|     |     | 1.    | 6[pre]                                                                                  |    |

|     |     | 2.    | 6[a]                                                                                    | 60 |

|      |      | 3.   | 6[b]                                                                                   | 63 |

|------|------|------|----------------------------------------------------------------------------------------|----|

| XI.  |      |      | 4: CLAIM 11 IS OBVIOUS UNDER 35 U.S.C. § 103 OV<br>ND ALLAREY IN VIEW OF WOLFE         |    |

|      | KINO |      |                                                                                        |    |

|      |      | 1.   | 11[pre]                                                                                |    |

|      |      | 2.   | 11[a]                                                                                  |    |

| XII. |      |      | 5: CLAIMS 1-3, 5, 8-10, 14 AND 21 ARE OBVIOUS UN 103 OVER NAFFZIGER IN VIEW OF ALLAREY |    |

|      | A.   | Moti | vation to Combine Naffziger and Allarey                                                | 65 |

|      | В.   |      | n 1                                                                                    |    |

|      |      | 1.   | 1[pre]                                                                                 |    |

|      |      | 2.   | 1[a1]                                                                                  | 67 |

|      |      | 3.   | 1[a2]                                                                                  | 68 |

|      |      | 4.   | 1[b1]                                                                                  | 71 |

|      |      | 5.   | 1[b2]                                                                                  | 72 |

|      |      | 6.   | 1[b3]                                                                                  | 74 |

|      |      | 7.   | 1[b4]                                                                                  | 74 |

|      |      | 8.   | 1[c1]                                                                                  |    |

|      |      | 9.   | 1[c2]                                                                                  | 77 |

|      | C.   | Depe | endent Claim 2                                                                         |    |

|      |      | 1.   | 2[pre]                                                                                 | 79 |

|      |      | 2.   | 2[a]                                                                                   | 79 |

|      | D.   | Depe | endent Claim 3                                                                         | 82 |

|      |      | 1.   | 3[pre]                                                                                 | 82 |

|      |      | 2.   | 3[a]                                                                                   | 82 |

|      | Ε.   | Depe | endent Claim 5                                                                         | 82 |

|      |      | 1.   | 5[pre]                                                                                 | 82 |

|      |      | 2.   | 5[a]                                                                                   | 82 |

|      | F.   | Depe | endent Claim 8                                                                         | 84 |

|      |      | 1.   | 8[pre]                                                                                 | 84 |

|      |      | 2.   | 8[a]                                                                                   | 84 |

|       | G. | Depe                                                 | ndent Claim 9                                                                         | .86 |  |

|-------|----|------------------------------------------------------|---------------------------------------------------------------------------------------|-----|--|

|       |    | 1.                                                   | 9[pre]                                                                                | .86 |  |

|       |    | 2.                                                   | 9[a]                                                                                  | .86 |  |

|       | H. | Depe                                                 | ndent Claim 10                                                                        | .86 |  |

|       |    | 1.                                                   | 10[pre]                                                                               | .86 |  |

|       |    | 2.                                                   | 10[a]                                                                                 | .86 |  |

|       | I. | Claim                                                | ı 14                                                                                  | .87 |  |

|       |    | 1.                                                   | 14[pre]                                                                               | .87 |  |

|       |    | 2.                                                   | 14[a]                                                                                 | .87 |  |

|       | J. | Indep                                                | endent Claim 21                                                                       | .87 |  |

|       |    | 1.                                                   | 21[pre]                                                                               | .87 |  |

|       |    | 2.                                                   | 21[a1]                                                                                | .87 |  |

|       |    | 3.                                                   | 21[a2]                                                                                | .87 |  |

|       |    | 4.                                                   | 21[b1]                                                                                | .89 |  |

|       |    | 5.                                                   | 21[b2]                                                                                | .89 |  |

|       |    | 6.                                                   | 21[b3]                                                                                | .90 |  |

|       |    | 7.                                                   | 21[b4]                                                                                | .90 |  |

|       |    | 8.                                                   | 21[c1]                                                                                | .90 |  |

|       |    | 9.                                                   | 21[c2]                                                                                | .90 |  |

| XIII. |    |                                                      | 6: CLAIM 4 IS OBVIOUS UNDER §103 OVER NAFFZIGER<br>AREY IN VIEW OF FLAUTNER           |     |  |

|       | A. | Motiv                                                | vation to Combine Naffziger, Allarey and Flautner                                     | .91 |  |

|       | B. | Depe                                                 | ndent Claim 4                                                                         | .92 |  |

|       |    | 1.                                                   | 4[pre]                                                                                | .92 |  |

|       |    | 2.                                                   | 4[a]                                                                                  | .92 |  |

| XIV.  |    |                                                      | 7: CLAIM 6 IS OBVIOUS UNDER §103 OVER NAFFZIGER<br>AREY IN VIEW OF WOLFE AND/OR KUMAR | 2   |  |

|       | A. | Motiv                                                | vation to Combine Naffziger, Allarey and Wolfe                                        | .92 |  |

|       | B. | Motivation to Combine Naffziger, Allarey and Kumar93 |                                                                                       |     |  |

|       | C. | Deper                                                | ndent Claim 6                                                                         | .94 |  |

# Petition for *Inter Partes* Review of U.S. Patent No. 8,549,339

|      | 1.        | 6[pre]                                            | 94 |

|------|-----------|---------------------------------------------------|----|

|      | 2.        | 6[a]                                              | 94 |

|      | 3.        | 6[b]                                              | 95 |

| XV.  |           | 8: CLAIM 11 IS OBVIOUS UNDER 35 U.S.C. § 103 OVER |    |

|      | NAFFZIGI  | ER AND ALLAREY IN VIEW OF WOLFE                   | 95 |

|      | 1.        | 11[pre]                                           | 95 |

|      | 2.        | 11[a]                                             | 95 |

| XVI. | DISCRETI  | ONARY DENIAL IS NOT APPROPRIATE                   | 95 |

| XVII | . CONCLUS | ION                                               | 97 |

# **TABLE OF AUTHORITIES**

| <u>Page(</u>                                                                                             | <u>s)</u>      |

|----------------------------------------------------------------------------------------------------------|----------------|

| <u>Cases</u>                                                                                             |                |

| Amber.IO, Inc. D/B/A Two Tap v. 72Lux, Inc. D/B/A Shoppable, IPR2020-00015, Paper 8 (PTAB April 1, 2020) | .9             |

| Apple Inc. v. Fintiv, Inc., IPR2020-00019, Paper 11 (PTAB Mar. 20, 2020)95, 96, 9                        | €7             |

| Dish Network L.L.C. v. Broadband iTV, Inc., IPR2020-01359, Paper 15 (PTAB Feb. 12, 2021)9                | <del>)</del> 6 |

| Google LLC v. Uniloc 2017 LLC,<br>IPR2020-00115, Paper 10 (PTAB May 12, 2020)9                           | <del>)</del> 7 |

| Redstone Logics LLC v. MediaTek, Inc. and MediaTek USA, Inc., No. 7:24-cv-00029-DC-DTG (W.D. Tex.)passi  | m              |

| Redstone Logics LLC v. NXP Semiconductors N.V. et al, No. 7:24-cv-00028-DC-DTG (W.D. Tex.)               | . 1            |

| Redstone Logics LLC v. Qualcomm Inc. et al, No. 7:24-cv-00231-ADA (W.D. Tex.)                            | .1             |

| Redstone Logics LLC v. Samsung Electronics Co., Ltd. et al, No. 2:23-cv-00485-JRG (E.D. Tex.)            | .1             |

| Sotera, Wireless, Inc. v. Masimo Corp., IPR2020-01019, Paper 12 (PTAB Dec. 1, 2020)9                     | <del>)</del> 7 |

# **Statutes and Codes**

| United States Code                                 |           |

|----------------------------------------------------|-----------|

| Title 35, section 102(a)                           | 9         |

| Title 35, section 102(b)                           |           |

| Title 35, section 102(e)(1)                        | 9, 13, 15 |

| Title 35, section 102(e)(2)                        |           |

| Title 35, section 103                              |           |

| Title 35, section 325(d)                           |           |

| Rules and Regulations  Code of Federal Regulations |           |

| Title 37, section 42.10(b)                         | 2         |

| Title 37, section 42.15                            | 3         |

| Title 37, section 42.103-105                       | 3         |

| Title 37, section 42.106                           |           |

| Title 37, section 42.108(c)                        | 6         |

| Title 37, section 42.300                           | 4         |

# **EXHIBIT LIST**

| Exhibit No. | Description                                                                               |  |  |

|-------------|-------------------------------------------------------------------------------------------|--|--|

| 1001        | U.S. Patent No. 8,549,339 B2 to Wolfe et al.                                              |  |  |

| 1002        | File History for U.S. Patent No. 8,549,339 B2 to Wolfe et al.                             |  |  |

| 1003        | Declaration of Dr. R. Jacob Baker ("Baker Decl.")                                         |  |  |

| 1004        | Curriculum Vitae of Dr. R. Jacob Baker                                                    |  |  |

| 1005        | U.S. Patent Application Publication No. 2009/0158078 A1 to Knoth ("Knoth")                |  |  |

| 1006        | U.S. Patent No. 8,122,270 B2 to Allarey et al. ("Allarey")                                |  |  |

| 1007        | U.S. Patent Application Publication No. 2005/0034002 A1 to Flautner ("Flautner")          |  |  |

| 1008        | U.S. Patent Application Publication No. 2011/0153984 A1 to Wolfe et al. ("Wolfe")         |  |  |

| 1009        | U.S. Patent Application Publication No. 2007/0080696 A1 to Kumar et al. ("Kumar")         |  |  |

| 1010        | U.S. Patent Application Publication No. 2010/0122101 A1 to Naffziger et al. ("Naffziger") |  |  |

| 1011        | Complaint for Patent Infringement, Redstone Logics LLC v.                                 |  |  |

| 1012        | Returned Summons (Dkt. No. 6 of the Texas Action)                                         |  |  |

| Exhibit No. | Description                                                                            |

|-------------|----------------------------------------------------------------------------------------|

| 1013        | Unopposed Motion for Extension of Time to File Answer (Dkt. No. 8 of the Texas Action) |

| 1014        | Initial Infringement Contentions in the Texas Action, dated August 15, 2024            |

| 1015        | Scheduling Order (Dkt. No. 24 of the Texas Action)                                     |

| 1016        | August 15, 2024 email serving the Infringement Contentions                             |

| 1017        | '339 Patent Challenged Claim Elements                                                  |

#### I. MANDATORY NOTICES

### A. Real Party-In-Interest (37 C.F.R. §42.8(b)(1))

Petitioners MediaTek Inc. and MediaTek USA, Inc. ("Petitioners" or "MediaTek") are real parties-in-interest.

### B. Identification of Related Matters (37 C.F.R. §42.8(b)(2))

Patent Owner has asserted U.S. Patent No. 8,549,339 (the "'339 Patent") against Petitioners in co-pending civil litigation, *Redstone Logics LLC v. MediaTek, Inc. and MediaTek USA, Inc.*, No. 7:24-cv-00029-DC-DTG (W.D. Tex.) ("Texas Action"). Petitioner MediaTek USA, Inc. was served with the original complaint in the Texas Action on January 30, 2024. Ex[1012]. Petitioner MediaTek Inc. waived service of process on February 14, 2024. Ex[1013]. Patent Owner has asserted Claims 1, 5, 8-10, 14, and 21 of the '339 Patent against Petitioners. Ex[1014]. A schedule was entered in the Texas Action on August 27, 2024, which set trial for May 4, 2026. Ex[1015].

Patent Owner has also asserted the '339 Patent in *Redstone Logics LLC v. NXP Semiconductors N.V. et al*, No. 7:24-cv-00028-DC-DTG (W.D. Tex.), *Redstone Logics LLC v. Qualcomm Inc. et al*, No. 7:24-cv-00231-ADA (W.D. Tex.), and *Redstone Logics LLC v. Samsung Electronics Co., Ltd. et al*, No. 2:23-cv-00485-JRG (E.D. Tex.).

# C. Counsel and Service Information (37 C.F.R. §§42.8(b)(3) & (b)(4))

Petitioners designate the following Lead and Backup Counsel. Concurrently filed with this Petition is a Power of Attorney for appointing the following Lead and Backup Counsel, per 37 C.F.R. § 42.10(b). Service via hand-delivery may be made at the postal mailing addresses below. Petitioners consent to electronic service by email at the following address: Case-MediaTekIPRMembers@pillsburylaw.com.

| Lead Counsel                         | Back-Up Counsel                     |

|--------------------------------------|-------------------------------------|

| Robert C.F. Pérez                    | Christopher Kao                     |

| (Reg. No. 39,328)                    | (Pro Hac Vice to be requested)      |

| PILLSBURY WINTHROP SHAW              | Brock S. Weber                      |

| PITTMAN LLP                          | (Pro Hac Vice to be requested)      |

| 7900 Tysons One Place, Suite 500     | Surui Qu                            |

| Tysons, VA 22102                     | (Pro Hac Vice to be requested)      |

| Telephone: 703.770.7759              | PILLSBURY WINTHROP SHAW             |

| Facsimile: 703.770.7901              | PITTMAN LLP                         |

| Email: robert.perez@pillsburylaw.com | Four Embarcadero Center, 22nd Floor |

|                                      | San Francisco, CA 94111             |

|                                      | Telephone: 415.983.1000             |

|                                      | Facsimile: 415.983.1200             |

|                                      | christopher.kao@pillsburylaw.com    |

|                                      | brock.weber@pillsburylaw.com        |

|                                      | surui.qu@pillsburylaw.com           |

|                                      | Michael Liu (Reg No. 77,133)        |

|                                      | PILLSBURY WINTHROP SHAW             |

|                                      | PITTMAN LLP                         |

|                                      | 2550 Hanover Street                 |

|                                      | Palo Alto, CA 94304                 |

|                                      | Telephone: 650.233.4500             |

|                                      | Facsimile: 650.233.4545             |

|                                      | michael.liu@pillsburylaw.com        |

#### D. Payment of Fees (37 C.F.R. §42.103)

Petitioners authorize the Patent and Trademark Office to charge Deposit Account No. 033975 for the petition fee and for any other required fees.

#### II. INTRODUCTION

Petitioners hereby petition to institute *inter partes* review ("IPR") of Claims 1-6, 8-11, 14 and 21 ("Challenged Claims") of U.S. Patent No. 8,549,339 (the "'339 Patent," Ex[1001]), and cancel those claims as unpatentable under 35 U.S.C. § 103.

The prior art references presented in this Petition—Knoth (Ex[1005]), Allarey (Ex[1006]), Flautner (Ex[1007]), Wolfe (Ex[1008]), Kumar (Ex[1009]), and Naffziger (Ex[1010])—disclose multi-core processors with voltage and clock scaling functionality and related communications/control signaling that render the Challenged Claims obvious. None of the prior art presented in this Petition was cited or discussed during original prosecution.

# III. STATEMENT OF PRECISE RELIEF REQUESTED FOR EACH CHALLENGED CLAIM/REQUIREMENTS FOR INTER PARTES REVIEW

This Petition complies with all statutory and regulatory requirements 37 C.F.R. §§ 42.103-105 and 42.15 and should be accorded the filing date of this Petition pursuant to 37 C.F.R. §42.106.

# **A.** Grounds for Standing (37 C.F.R. § 42.104(a))

Petitioners certify that the '339 Patent is available for IPR and Petitioners are

not barred or estopped from requesting IPR of the Challenged Claims on the grounds identified in this Petition.

## B. Claims for Which Review Is Requested (37 C.F.R. § 42.104(b))

Petitioners respectfully request review of the Challenged Claims of the '339 Patent pursuant to 37 C.F.R. § 42.300 and cancellation of those claims as unpatentable.

# C. Statutory Grounds of Challenge

The Challenged Claims of the '339 Patent are unpatentable under 35 U.S.C. § 103 because they are obvious, as shown in the grounds below.

| Ground | Invalidity                                    | Exhibit(s)        |

|--------|-----------------------------------------------|-------------------|

| 1      | Claims 1, 5, 8-10, 14 and 21 would have been  | 1005, 1006        |

|        | obvious over Knoth (Ex[1005]) in view of      |                   |

|        | Allarey (Ex[1006]) under 35 U.S.C. § 103.     |                   |

| 2      | Claims 2-4 would have been obvious over Knoth | 1005, 1006, 1007  |

|        | (Ex[1005]) and Allarey (Ex[1006]) in view of  |                   |

|        | Flautner (Ex[1007]) under 35 U.S.C. § 103.    |                   |

| 3      | Claim 6 would have been obvious over Knoth    | 1005, 1006, 1008, |

|        | (Ex[1005]) and Allarey (Ex[1006]) in view of  | 1009              |

| Ground | Invalidity                                     | Exhibit(s)        |

|--------|------------------------------------------------|-------------------|

|        | Wolfe (Ex[1008]) and further in view of Kumar  |                   |

|        | (Ex[1009] under 35 U.S.C. § 103.               |                   |

| 4      | Claim 11 would have been obvious over Knoth    | 1005, 1006, 1008  |

|        | (Ex[1005]) and Allarey (Ex[1006]) in view of   |                   |

|        | Wolfe (Ex[1008]) under 35 U.S.C. § 103.        |                   |

| 5      | Claims 1-3, 5, 8-10, 14 and 21 would have been | 1006, 1010        |

|        | obvious over Naffziger (Ex[1010]) and Allarey  |                   |

|        | (Ex[1006]) under 35 U.S.C. § 103.              |                   |

| 6      | Claim 4 would have been obvious over Naffziger | 1006, 1007, 1010  |

|        | (Ex[1010]) and Allarey (Ex[1006]) in view of   |                   |

|        | Flautner (Ex[1007]) under 35 U.S.C. § 103.     |                   |

| 7      | Claim 6 would have been obvious over Naffziger | 1006, 1008, 1009, |

|        | (Ex[1010]) and Allarey (Ex[1006]) in view of   | 1010              |

|        | Wolfe (Ex[1008]) and further in view of Kumar  |                   |

|        | (Ex[1009] under 35 U.S.C. § 103.               |                   |

| Ground | Invalidity                                      | Exhibit(s)       |

|--------|-------------------------------------------------|------------------|

| 8      | Claim 11 would have been obvious over           | 1006, 1008, 1010 |

|        | Naffziger (Ex[1010]) and Allarey (Ex[1006]) in  |                  |

|        | view of Wolfe (Ex[1008]) under 35 U.S.C. § 103. |                  |

#### IV. CLAIM CONSTRUCTION

For the purposes of this Petition, Petitioners contend that, unless otherwise specifically noted herein, the claim terms in the '339 Patent are accorded their ordinary and customary meaning that they would have to a person having ordinary skill in the art at the time of the alleged invention ("PHOSITA"). Petitioners' interpretation of the claim terms is further explained for each limitation in relation to the prior art discussed in Grounds 1-8, below.

#### V. A PERSON HAVING ORDINARY SKILL IN THE ART

A PHOSITA with respect to the '339 Patent would have had at least a bachelor's degree in electrical engineering, computer engineering, computer

<sup>&</sup>lt;sup>1</sup> Petitioners reserve the right to address any claim construction positions taken by the Patent Owner in its Preliminary Response, including under 37 C.F.R. § 42.108(c).

science, or a similar field, and at least two years of industry or academic experience designing or analyzing electronic circuits, semiconductors, processors, or power management, and related firmware and software, or the equivalent. Ex[1003] (Declaration of Dr. R. Jacob Baker), ¶ 29.

#### VI. OVERVIEW OF THE '339 PATENT

## A. Purported Invention Of The '339 Patent

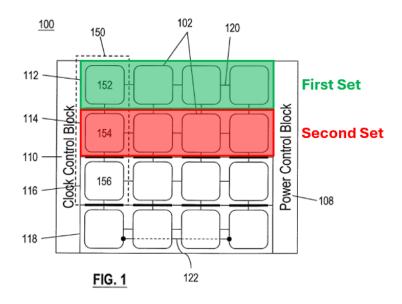

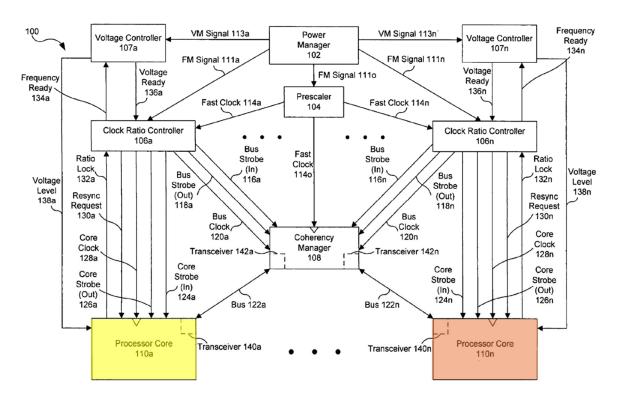

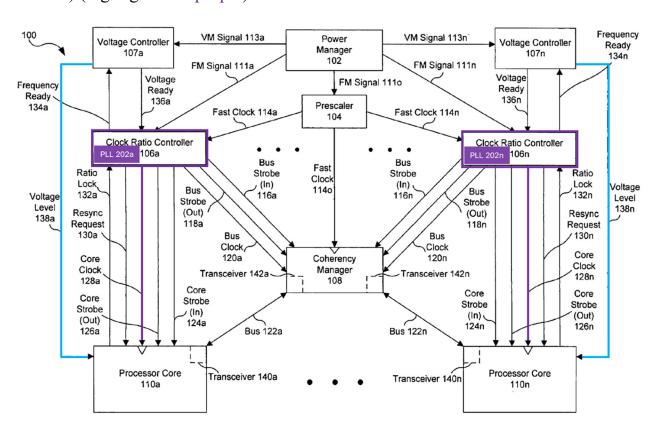

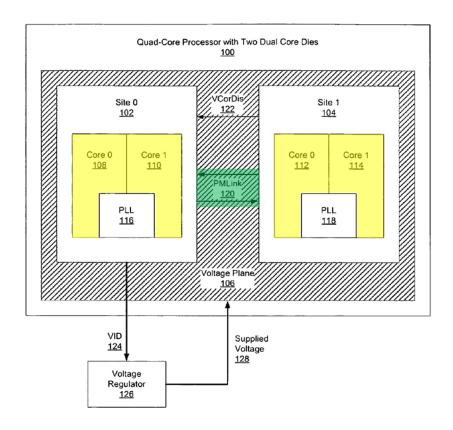

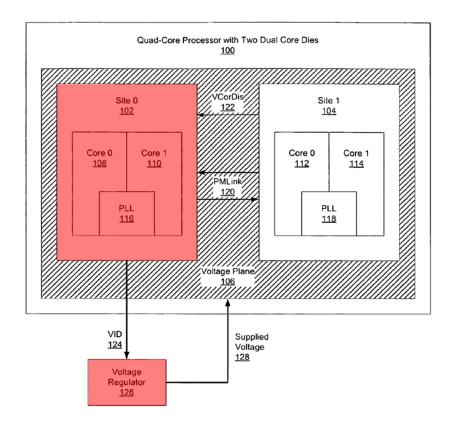

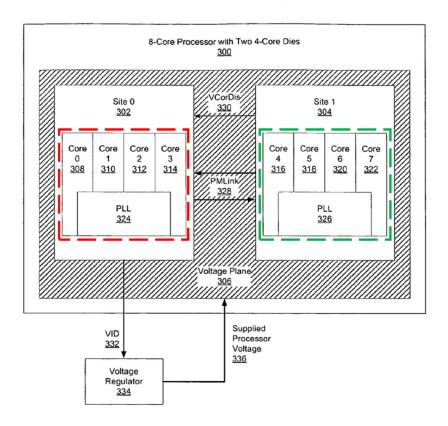

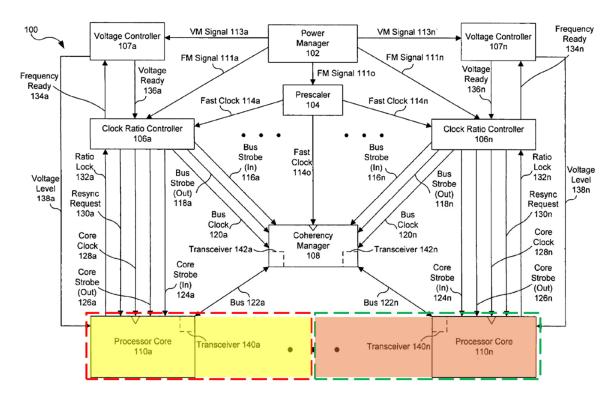

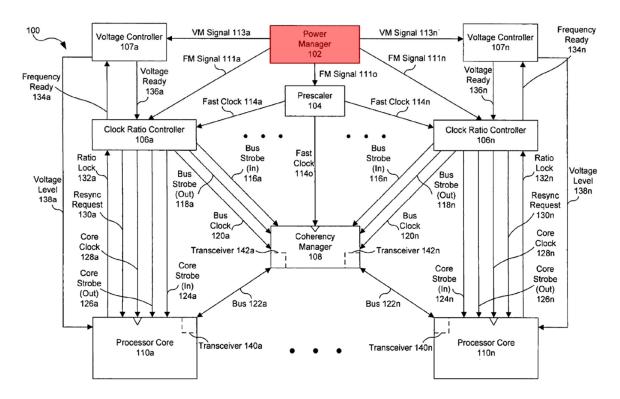

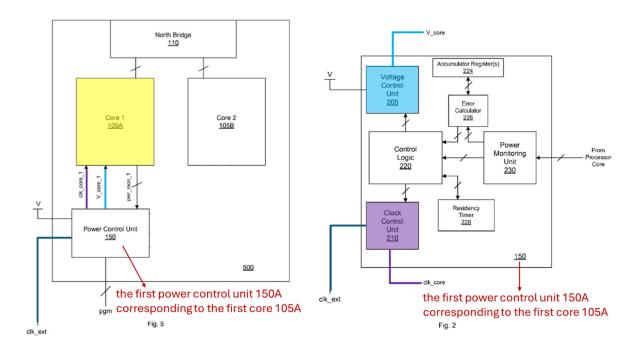

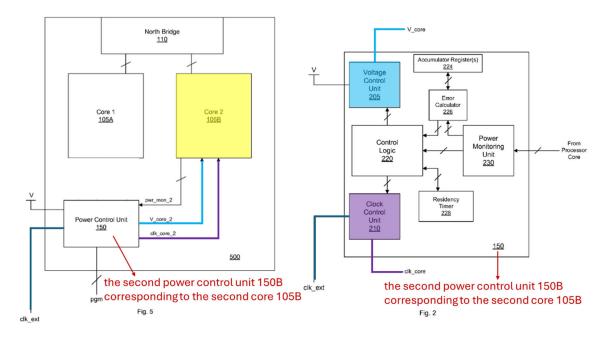

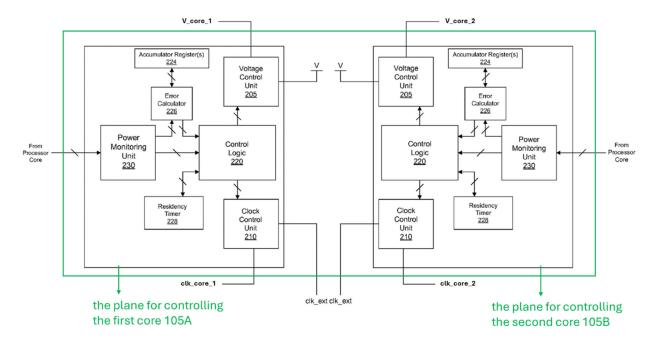

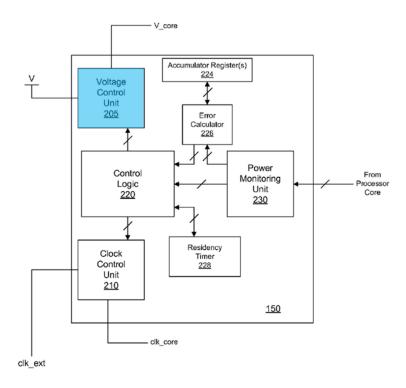

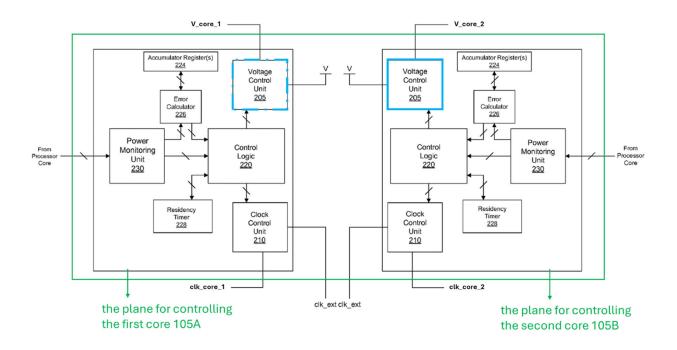

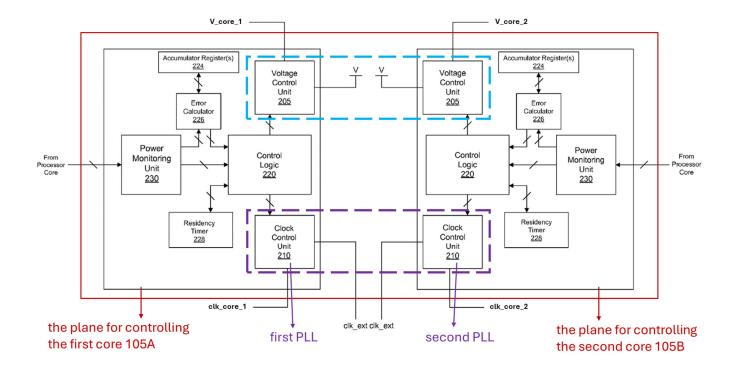

The '339 Patent concerns techniques for handling communication between processor cores of a multi-core processor. Ex[1001], Abstract. Figure 1 shows four sets of processor cores, with the first set and the second set of processor cores highlighted:

'339 Patent, Fig. 1 (annotated)

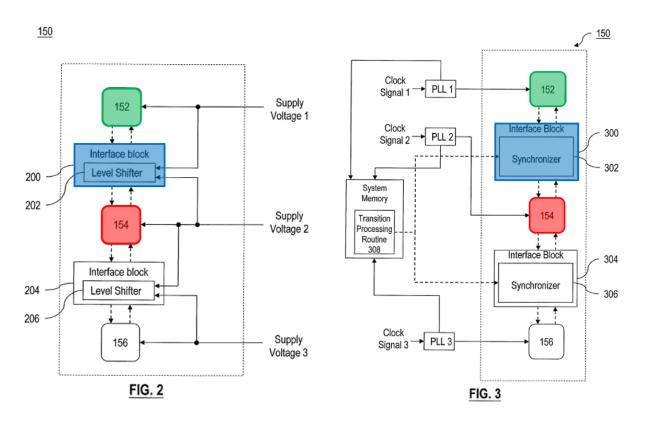

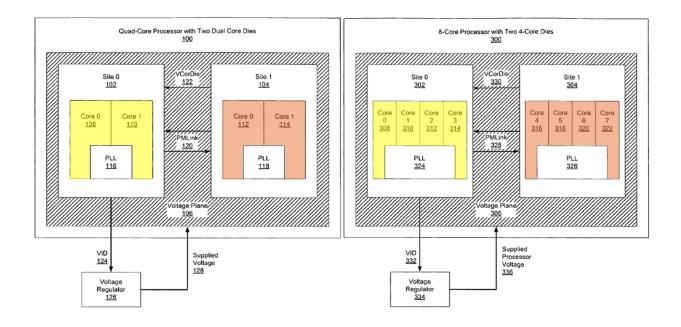

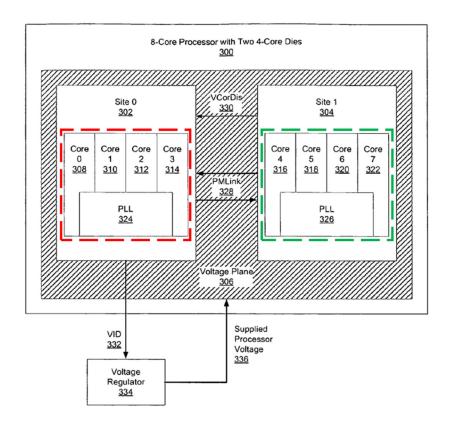

Figures 2 and 3 show an interface block coupled to the first and second sets

#### of processor cores:

'339 Patent. Figs. 2 and 3 (annotated)

The '339 Patent discloses dynamic voltage supply and clock speed control for the processor cores so that the multi-core processor may operate at high power and high clock frequency when needed and at low power when the computing requirements are reduced. *Id.*, 1:10-14. The power supplies for the first and second sets of processor cores are independent. Similarly, the clock signals of the first second sets of processor cores are independent. *Id.* at 2:25-31. As such, facilitating communication between two sets of processor cores is necessary and is performed by interface blocks. *Id.*, 3:21-23, 3:30-34, 4:4-8.

### **B.** Priority Date

The earliest possible priority for the '339 Patent is February 26, 2010, the date it was filed, which is what Patent Owner has contended in the Texas Action. Ex[1016]. Petitioners take no position on the proper priority date for each claim of the '339 Patent, but assume this earliest date as the priority date.

#### VII. OVERVIEW OF THE STATE OF THE ART

Petitioners present the references below, none of which were cited or discussed during prosecution of the '339 Patent. Ex[1002]. The Board should not deny institution under Section 325(d). *See Amber.IO, Inc. D/B/A Two Tap v. 72Lux, Inc. D/B/A Shoppable*, IPR2020-00015, Paper 8 at 18-20 (PTAB April 1, 2020).

# A. U.S. Patent Application Publication No. 2009/0158078 A1 to Knoth ("Knoth") (Ex[1005])

Knoth is a publication of a U.S. patent application filed on December 12, 2007 and published on June 18, 2009. Ex[1005] at 1. Knoth is prior art to the '339 Patent under at least 35 U.S.C. §§ 102(a) and 102(e)(1).

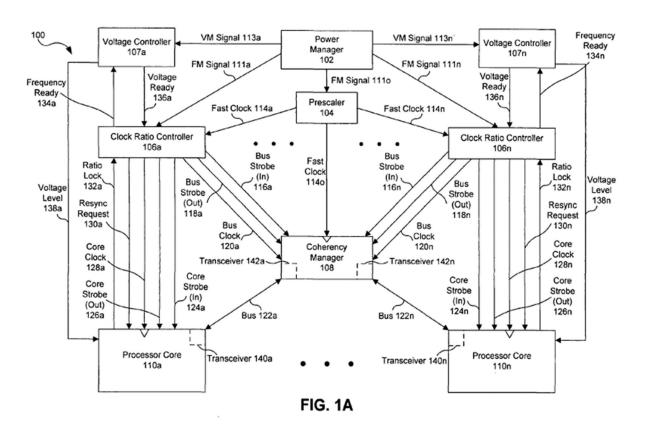

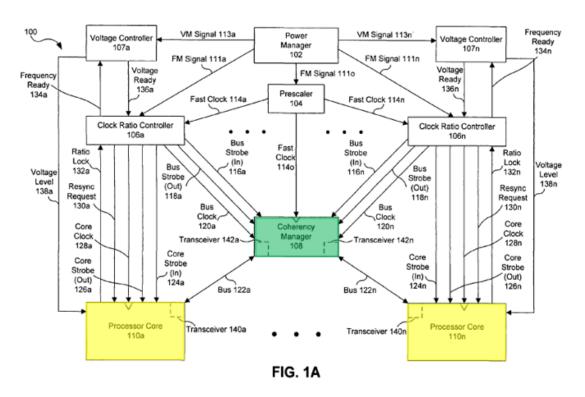

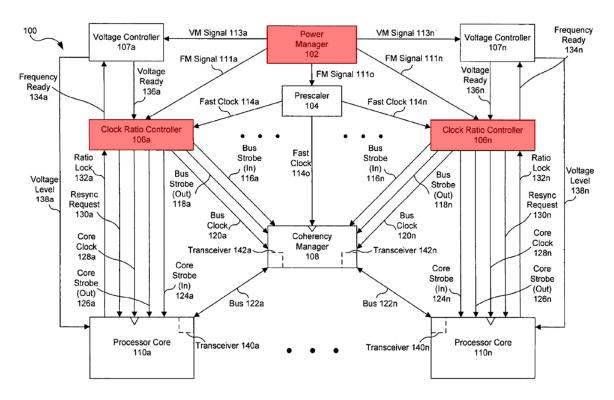

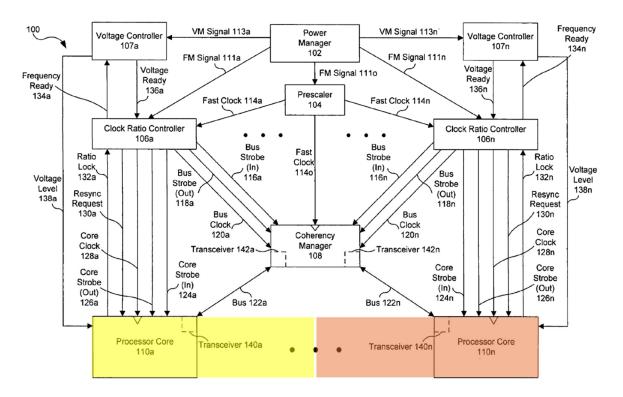

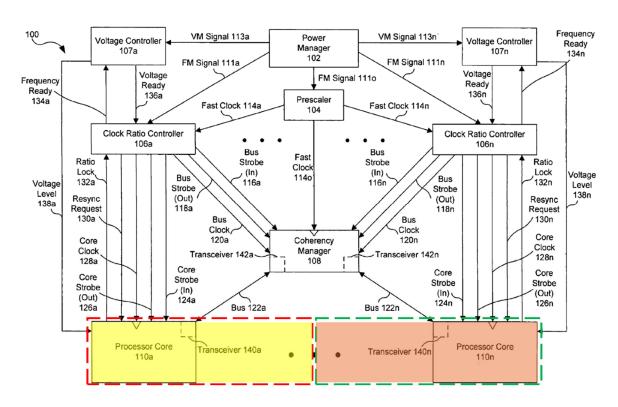

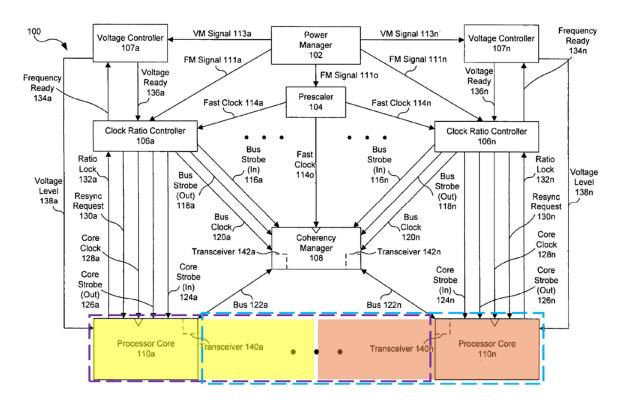

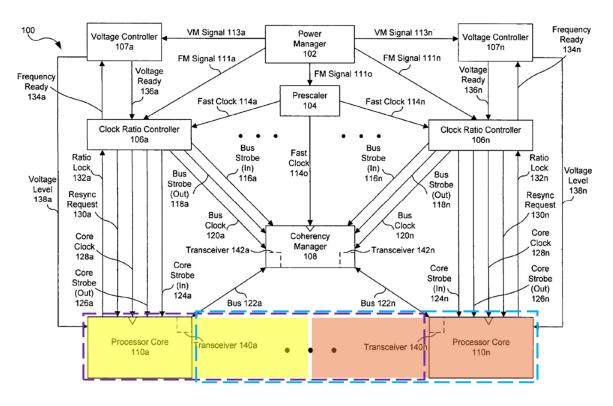

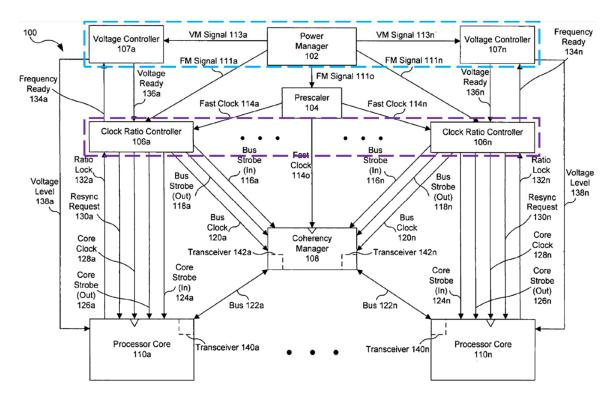

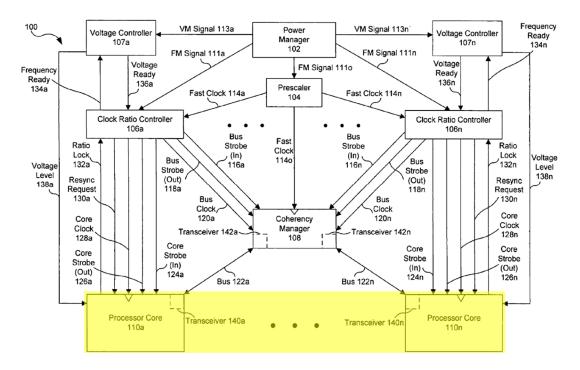

Knoth teaches a multiprocessor system that includes an arbitrary number of processor cores a-n. *Id.* at [0023]. Knoth's multi-core processor 100 includes a power management unit 102 that provides individual frequency management (FM) signals 111a-n to clock ratio controllers 106a-n to initiate frequency adjustments to independently control/scale the clock frequency of each processor core 110a-n;

power management unit 102 also provides individual management (VM) signals 113a-n to voltage controllers 107a-n to independently control the voltage of each processor core 110a-n. *Id.* at [0025], [0041]-[0042]. Coherency manager 108 is coupled to processor cores 110a-n to facilitate communications between the processor cores. *Id.* at [0006] and [0033].

FIG. 2A

FIGS. 1A and 2A of Knoth

# B. U.S. Patent No. 8,122,270 to Allarey et al. ("Allarey") (Ex[1006])

Allarey is a U.S. patent filed on September 29, 2008 and issued on February 21, 2012. Ex[1006] at 1. Allarey is prior art to the '339 Patent under at least 35 U.S.C. § 102(e)(2).

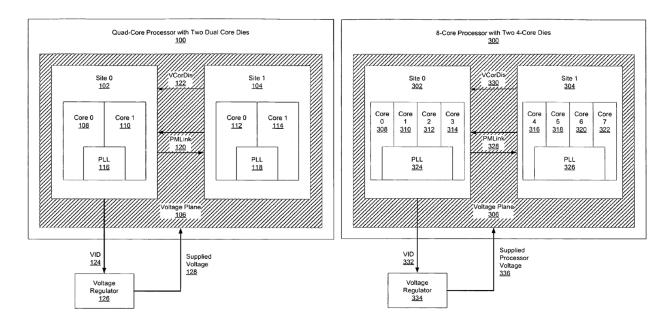

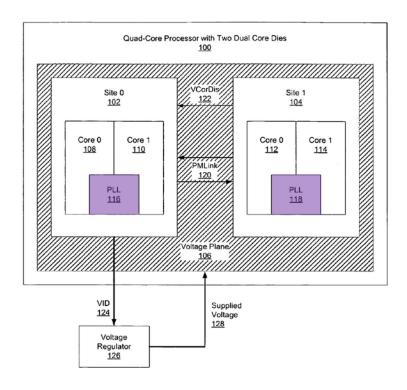

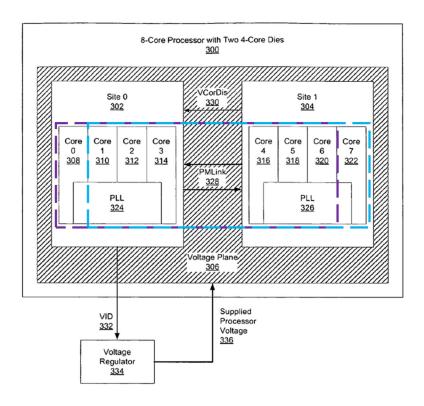

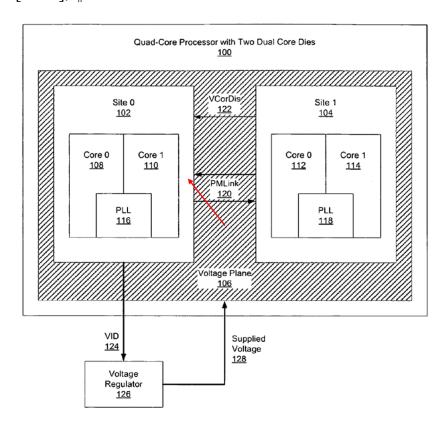

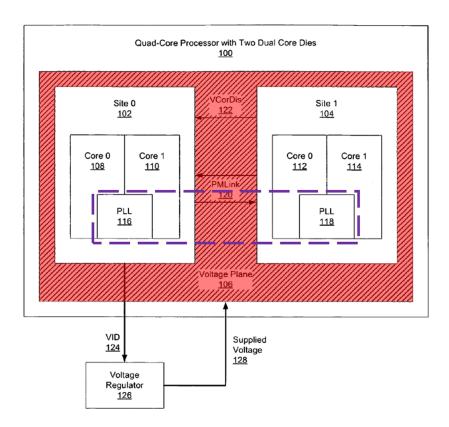

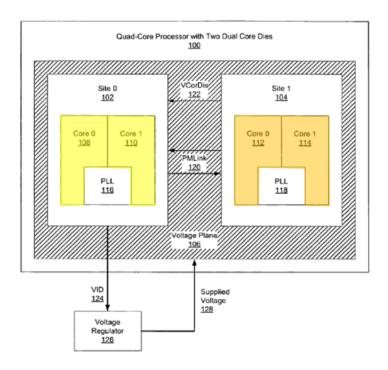

Allarey teaches a multi-core processor system comprising processor cores in two sites. The voltage supplied to the processor and the frequency of the cores in each site may be independently and dynamically modified. *Id.* at 1:15-24. Allarey discloses a power management link (PMLink) to couple the cores in the two sites. *Id.* at 2:59-3:3, 5:34-43.

FIGS. 1 and 3 of Allarey

# C. U.S. Patent Application Publication No. 2005/0034002 A1 to Flautner ("Flautner") (Ex[1007])

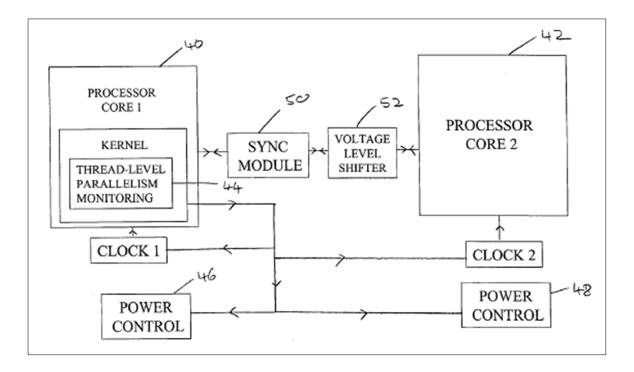

Flautner a publication of a U.S. patent application filed on August 4, 2003 and published on February 10, 2005. Ex[1007] at 1. Flautner is prior art to the '339 Patent under at least 35 U.S.C. § 102(b).

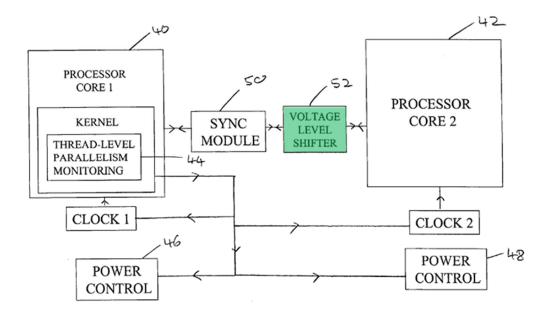

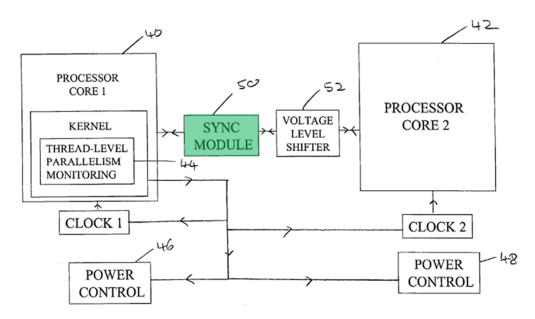

Flautner discloses a multi-core processor that includes a synchronisation module 50 and a voltage level shifter 52 to deal with clock synchronization issues and the different supply voltage levels between cores in two independent domains. *Id.* at [0047]-[0048].

FIG. 4 of Flautner

# D. U.S. Patent Application Publication No. 2011/0153984 A1 to Wolfe et al. ("Wolfe") (Ex[1008])

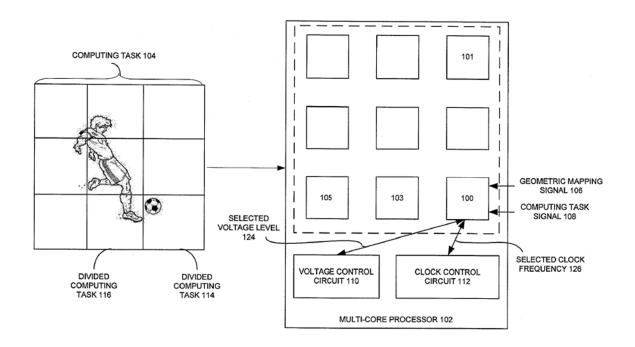

Wolfe is a publication of a U.S. patent application filed on December 21, 2009 and published on June 23, 2011. Ex[1008] at 1. Wolfe is prior art to the '339 Patent under at least 35 U.S.C. § 102(e)(1).

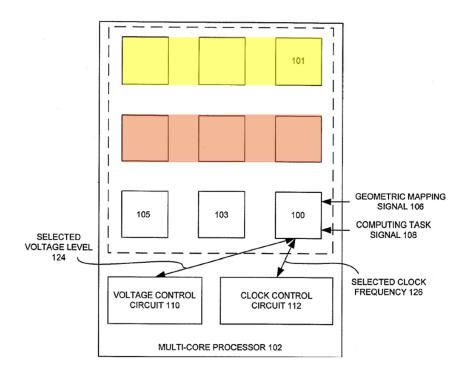

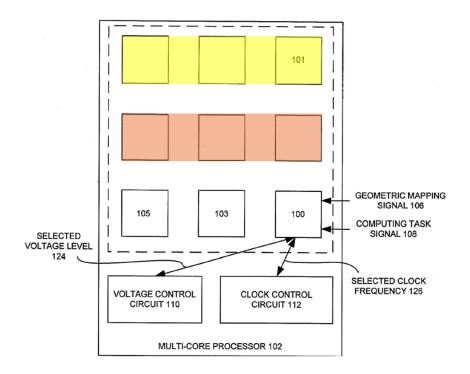

Wolfe teaches that processor cores may be "arranged in rows and columns in a 2-dimensional array." *Id.* at [0014]. Wolfe also discloses grouping cores based on geometric mapping. *Id.* at [0016], [0022].

FIGURE 1A of Wolfe

# A. U.S. Patent Application Publication No. 2007/0080696 A1 to Kumar et al. ("Kumar") (Ex[1009])

Kumar is a publication of a U.S. patent application filed on October 11, 2005 and published on April 12, 2007. Ex[1009] at 1. Kumar is prior art to the '339 Patent under at least 35 U.S.C. § 102(b).

Kumar discloses monitoring and adjusting a voltage  $V_1$  across one or more components 130 and a voltage  $V_2$  across one or more components 530 based on one or more predetermined relationships, including whether the absolute value of the difference between voltage  $V_1$  and the voltage  $V_2$  is less than, or equal to, a predetermined amount or a predetermined percentage of either  $V_1$  or  $V_2$ . See, e.g., id. at [0058]-[0059].

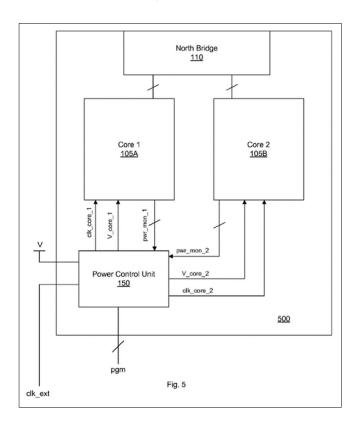

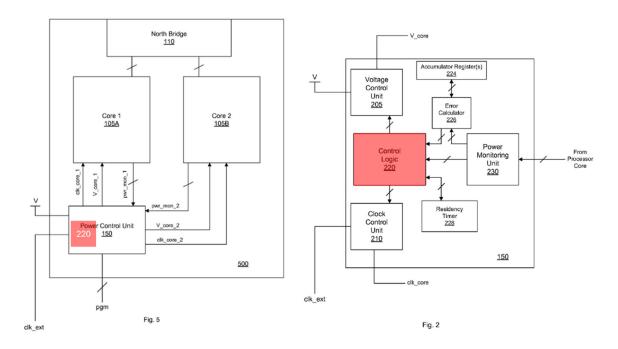

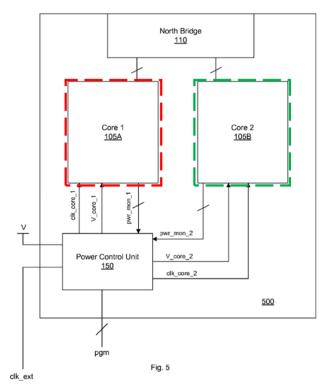

# B. U.S. Patent Application Publication No. 2010/0122101 A1 to Naffziger et al. ("Naffziger") (Ex[1010])

Naffziger is a publication of a U.S. patent application filed on November 11, 2008 and published on May 13, 2010. Ex[1010] at 1. Naffziger is therefore prior art to the '339 Patent under at least 35 U.S.C. § 102(e)(1).

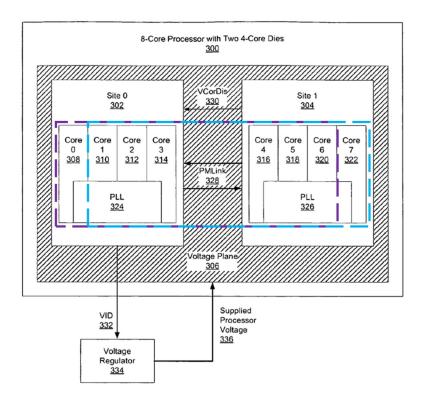

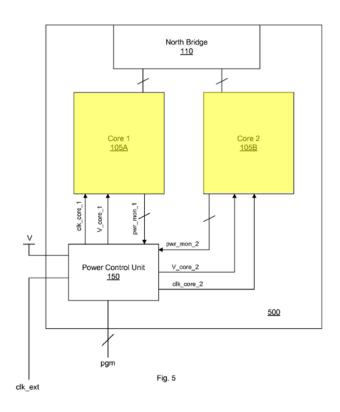

Naffziger teaches a multi-core processor, wherein the cores have separate, independent core supply voltage planes and are configured to receive separate, independently controlled core clock signals from PLL circuits. *Id.* at [0054].

FIG. 5 of Naffziger

## VIII. GROUND 1: CLAIMS 1, 5, 8-10, 14 AND 21 ARE OBVIOUS UNDER §103 OVER KNOTH IN VIEW OF ALLAREY

Knoth and Allarey, alone or in combination, disclose each and every limitation of Claims 1, 5, 8-10, 14 and 21.

### A. Motivation to Combine Knoth and Allarey

A PHOSITA would have been motivated to combine Knoth and Allarey and would have had a reasonable expectation of success in doing so, because they relate to the same well-known technologies. Ex[1003], ¶¶ 80-95.

Knoth and Allarey are directed to the same field of multi-core processors, address similar problems and propose similar solutions for managing voltage and frequency scaling of multi-core processors. Ex[1003], ¶¶ 80-86. For example, Knoth discloses solutions for multi-core processor systems to control power consumption that include changing operational states with different power consumptions by adjusting the voltage and clock frequency. *See* Ex[1005] at [0001]-[0003]. Allarey describes solutions to optimize the ability of multi-core processor systems to conserve power by dynamically modifying the voltage supplied to and the frequency of the processor. *See* Ex[1006] at 1:6-24.

Knoth is authored by MIPS engineers, and Allarey is authored by Intel engineers. Ex[1003], ¶¶ 87-89. A PHOSITA would have looked to publications by such leading companies in semiconductor design, such as MIPS and Intel, and considered the similar techniques disclosed in these references for optimizing the

power and/or performance of cores. Id.

A PHOSITA also would have found the combination obvious to try because it combines well-known techniques that are related—e.g., Knoth provides a system that dynamically adjusts clock signals without losing synchronization, focusing on coordination between different clock domains; Allarey provides a method to ensure stable voltage during these adjustments, crucial for the proper functioning of Knoth's clock ratio controller. *Id.*, ¶ 90. Knoth's method relies on stable voltage conditions during frequency adjustments, which Allarey's invention directly addresses. See, e.g., Ex[1005] at [0032]; Ex[1006] at 3:25-49; Ex[1003],  $\P$  91-93. A PHOSITA would have found synergy in combining dynamic power adjustments from Knoth with voltage stabilization from Allarey to improve overall processor performance and stability. Id. Therefore, a PHOSITA would have found that Knoth and Allarey provide complimentary solutions and would have been motivated to combine them to benefit from their respective teachings. *Id*.

Finally, a PHOSITA would have considerable expectation of success when combining these teachings because the combination would amount to a mere substitution of one known element (e.g., Knoth's core-level control) for another (Allarey's site-level control), applying a known technique to a known system ready for improvement, and/or use of known techniques to improve in a similar multi-core

environment. Id., ¶¶ 94-95. Therefore, the teachings and considerations of Allarey would allow a PHOSITA to improve on Knoth's systems effortlessly (and vice versa). Id.

#### B. Claim 1

### 1. 1[pre]

To the extent that the preamble is limiting, Knoth teaches a multi-core processor. Ex[1003], ¶¶ 96-98. For example, Knoth discloses that "digital system 100 is a multiprocessor digital system that includes at least two processor cores 110." Ex[1005] at [0023]. See, e.g., id. at FIG. 1A.

Allarey also discloses a "multi-core processor." Ex[1003], ¶¶ 99-102; Ex[1006] at 1:6-8. For example, Allarey discloses a quad-core processor 100 that includes two dual-core dies. *Id.* at 2:38-58; FIG. 1. As another example, Allarey discloses an 8-core processor with two 4-core dies 100. *Id.* at 5:13-23; FIG. 3.

### 2. 1[a1]

Knoth and Allarey, alone or in combination, disclose this limitation.  $Ex[1003], \P\P \ 103-109.$

Knoth discloses that "digital system 100 is a multiprocessor digital system that includes at least two processor cores 110." Ex[1005] at [0023], FIG. 1A.

FIG. 1A of Knoth, annotated

The multiprocessor digital system 100 includes a series of processor cores ann, with an explicit depiction of at least two processor cores 110a (highlighted in yellow) and 110n (highlighted in orange). Knoth discloses that the processor cores 110a-n operate independently through dedicated power and frequency management. Ex[1005] at [0025]-[0027], [0031]. The processor cores 110a and 110n disclose the recited first set of processor cores and the second set of processor cores of the multicore processor, to the extent that a "set" can include one or more. Ex[1003], ¶¶ 104-106.

To the extent it is argued that the processor cores 110a-n are individual cores,

or that a "set" means "two or more," it would have been obvious to a PHOSITA to extend the disclosed architecture of Knoth to include two distinct sets of cores, where each set of cores is managed separately. Id., ¶ 107. After all, Knoth discloses an arbitrary number of processor cores a-n and, therefore, more than two cores could be included in two distinct sets. *Id.* Extending Knoth's architecture to treat two cores or more in at least two distinct sets would have been a routine and desired modification for a PHOSITA, requiring only minor adjustments to the existing power and frequency management mechanisms, such as sending the power control signals to an individual core to a shared power domain or voltage plane for a set of cores that operates under the same conditions, which was common and wellunderstood adjustments a PHOSITA would have easily implemented. Id. A PHOSITA would have also understood that extending from individual cores to sets of cores would improve the system by enabling more efficient management of power and resources through grouped control, reducing complexity and enhancing scalability for handling diverse workloads. *Id*.

Furthermore, a PHOSITA would have been motivated to modify Knoth to have two sets of cores, rather than two individual cores, based on the teachings of Allarey. *Id.*, ¶ 108.

Allarey discloses a first set of processor cores in the form of a multi-core die in site 0 (highlighted in yellow) and a second set of processor cores in the form of a multi-core die in site 1 (highlighted in orange), as depicted below. Ex[1006] at 2:41-58, 5:17-33.

FIGs. 1 and 3 of Allarey, annotated

A PHOSITA would have understood that modifying Knoth based on Allarey to have sets of cores would achieve the benefits of reducing the complexity of individually managing each core, leading to improved scalability, reduced overhead, and more efficient resource allocation of the semiconductor system. Ex[1003], ¶ 107. Accordingly, Knoth and Allarey, alone or in combination, disclose this limitation. *Id.*, ¶¶ 103-109.

### 3. 1[a2]

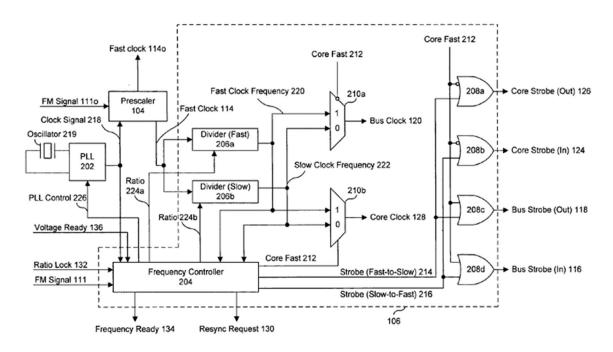

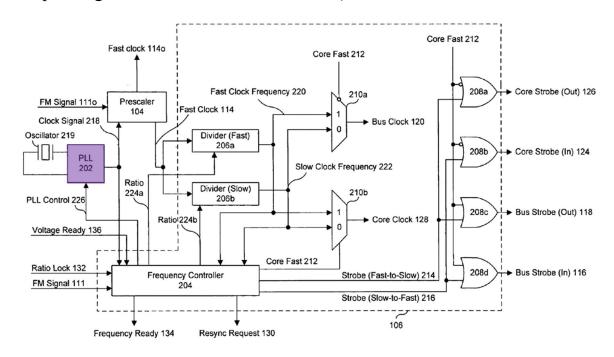

Knoth discloses this limitation. Ex[1003], ¶¶ 110-116. As depicted in FIG. 1A below, Knoth discloses that each of the processor cores 110a-n receives its respective voltage supply "voltage level signal 138a-n" (shown by blue lines) from its respective voltage controller 107a-n and its respective clock signal core clock signal 128a-n (shown by purple lines) output from respective clock ratio controller 106a-n (shown by purple boxes). Ex[1005] at [0027], [0031]. As explained below, each of clock ratio controllers 106a-n includes a phase locked loop (PLL) (for ease of discussion, referred to as PLL 202a-n corresponding to clock ratio controller 106a-n) (highlighted in purple).

### FIG. 1A of Knoth, modified to show PLL 202a and PLL 202n

As illustrated in FIG. 2A below, Knoth discloses clock ratio controllers 106a-n that each includes a phase locked loop (PLL) 202 (highlighted in purple) having as input "timing pulses generated by an oscillator 219" within the corresponding clock ratio controller 106 (for ease of discussion, referred to as oscillator 219a-n corresponding to clock ratio controller 106a-n). Ex[1005] at [0041]-[0042]. Alternatively, each PLL within clock ratio controller 106 receives as input a "PLL control signal 226" (for ease of discussion, referred to as PLL control signal 226a-n corresponding to clock ratio controller 106a-n).

FIG. 2A of Knoth, annotated

Processor cores 110a-n receive respective voltage supply "voltage level signal

138a-n" from voltage controller 107a-n and respective output clock signal "core clock signal 128a-n" from clock ratio controller 106a-n for "dynamic voltage and frequency scaled digital systems." *Id.* at [0001]. Specifically, Knoth discloses that each of voltage controllers 107a-n receives "individual voltage management (VM) signals 113a-n" that "individually control/scale the voltage of each processor core 110a-n" so that the voltage supply may increase or decrease. *Id.* at [0025], [0031]-[0032]. Processor cores 110a-n thus dynamically receive voltage level 138a-n.

Knoth also discloses that each of clock ratio controllers 106a-n receives "individual frequency management (FM) signals 111a-n" that "initiate frequency adjustments" to "individually control/scale the frequency of each processor core 110a-n" so that core clock signals 128a-n are dynamically modified. *Id.* at [0025], [0027], [0032]. Processor core 110a-n thus dynamically receives core clock 128a-n.

Thus, Knoth discloses that the first set of cores (processor core 110a extendable to include associated cores, or processor core 110a of Knoth modified in view of Allarey to include a set of multiple cores) dynamically receives a first supply voltage (voltage level 138a) and a first output clock signal (core clock 128a) of a first phase lock loop (PLL) (PLL 202a) having a first clock signal as input (the timing pulses from oscillator 219a, or alternatively, PLL control signal 226a); the second set of cores (processor core 110n extendable to include associated cores, or processor

core 110n of Knoth modified in view of Allarey to include a set of multiple cores) dynamically receives a second supply voltage (voltage level 138n) and a second output clock signal (core clock 128n) of a second phase lock loop (PLL) (PLL 202n) having a second clock signal as input (the timing pulses from oscillator 219n, or alternatively, PLL control signal 226n). Ex[1003], ¶ 116.

Allarey also discloses this limitation. Id., ¶¶ 117-121. Allarey discloses that the processor cores in site 0 and the processor cores in site 1 are supplied with voltage from voltage plane 106. Ex[1006] at 2:41-44, 2:59-3:24. "Site 1(104) may have different voltage requirements than site 0 (102) at any given time" and requests a different voltage. Id. at 3:20-24.

Further, Allarey discloses that the processor cores in site 0 (e.g., cores 108 and 110 in site 0 (102)) receive the clock signal generated by the PLL for site 0 (PLL 116) (highlighted in purple). *Id.* at 2:38-3:3. The processor cores in site 1 (e.g., cores 112 and 114 in site 1 (104)) receive the clock signal generated by the PLL for site 1 (PLL 118) (highlighted in purple). *Id.*

FIG. 1 of Allarey, annotated

"The voltage supplied to the processor and the frequency of the processor may be dynamically modified." *Id.* at 1:15-17. Allarey discloses "dynamically modify[ing]" "[t]he voltage supplied to the processor and the frequency of the processor." *Id.* at 1:12-24. Specifically, Allarey discloses "dynamically modify[ing] a voltage supplied to the first site" and "voltage regulator 126 ... regulates the supplied voltage 128 ... to supply to the voltage plane 106." *Id.* at Abstract and 3:4-19, FIG. 1. Accordingly, Allarey discloses that the cores in site 0 and site 1 dynamically receive respective supply voltages.

For the clock signaling, "[e]ach PLL can change the frequency of the clock signal." *Id.* at 2:41-58. Further, Allarey discloses that "[e]ach site includes a phase

locked loop (PLL) clock signal generation circuit" and "[e]ach PLL is capable of generating a clock signal." *Id.* at 2:41-58. Accordingly, Allarey discloses that the cores in site 0 and site 1 dynamically receive respective output clock signals of a PLL.

#### 4. 1[b1]

As explained for Claim 1[a1] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation.

#### 5. 1[b2]

As explained for Claim 1[a2] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation.

# 6. 1[b3]

Knoth discloses this limitation. Ex[1003], ¶¶ 124-126. Knoth discloses that the first and second sets of cores receive independent supply voltages. Knoth discloses that "VM signals 113a-n can be used to individually control/scale the voltage of each processor core 110a-n" and "[e]ach voltage controller 107a-n also sends a voltage or voltage level signal 138a-n to each processor core 110a-n to power each processor core 110a-n." Ex[1005] at [0025] and [0031]. Accordingly, Knoth teaches individually controlling each voltage level signal 138a-n such that the first supply voltage is independent from the second supply voltage.

Allarey also this limitation. Ex[1003], ¶¶ 127-128. The first and second sets of cores of Allarey receive independent supply voltages. Ex[1006] at 3:20-24 ("[s]ite 1 (104) may have different voltage requirements than site 0 (102) at any given time."). Accordingly, Allarey teaches different supply voltage requirements for the sets of processor cores such that the first supply voltage is independent from the second supply voltage.

#### 7. 1[b4]

Knoth discloses this limitation. Ex[1003], ¶¶ 129-134. Knoth discloses that clock ratio controllers 106a-n receive, respectively, "individual frequency management (FM) signals 111a-n" that are "used to individually control/scale the frequency of each processor core 110a-n." Ex[1005] at [0025]. Thus, clock ratio controllers 106a-n operate independently from each other. Ex[1003], ¶ 130. As such, the first clock signal of the first PLL within clock ratio controller 106a is independent from the second clock signal of the second PLL within clock ratio controller 106n. *Id.*

Furthermore, as explained for Claim 1[a2] in Ground 1, Knoth discloses that clock ratio controller 106a-n each includes a phase locked loop (PLL) 202 having as input "timing pulses generated by an oscillator 219" within the corresponding clock ratio controller 106. Ex[1006] at [0041]-[0042]. A PHOSITA would read Knoth to

include independent first and second PLLs within clock ratio controllers 106a and 106n, respectively, receiving the first and second clock signals (the timing pulses generated by oscillators 219a and 219n) that are independent from each other. Ex[1003], ¶¶ 131-132.

Alternatively, PLL control signals 226a and 226n of Knoth disclose that the first and second clock signals are independent of each other, as claimed. *Id.*, ¶ 133. Each PLL control signal 226 is generated based on its respective, independent "voltage ready signal 136" (136a-n) and "FM signal 111" (111a-n). Ex[1005] at [0055]. Specifically, each voltage ready signal 136a-n is provided by a separate voltage controller 107a-n operating independently from each other. *Id.* at [0025], [0031]. Knoth also discloses that "power management unit 102 provides individual frequency management (FM) signals 111a-n" that separate from each other. *Id.* at [0025].

Allarey also discloses this limitation. Ex[1003], ¶¶ 135-136. In Allarey, each site includes a PLL clock signal generation circuit. Ex[1006] at 2:41-58. The PLL clock signal generation circuits are independent of each other. Ex[1003], ¶ 136. Therefore, the first PLL clock signal generation circuit is independent from the second PLL clock signal generation circuit. *Id*.

## 8. 1[c1]

Knoth discloses this limitation. Ex[1003], ¶¶ 137-140. As depicted in FIG. 1A, Knoth discloses a coherency manager 108 (highlighted in green) coupled to the processor cores 110a and 110n (highlighted in yellow). Ex[1005] at [0033], FIG. 1A.

FIG. 1A of Knoth, annotated

Coherency manager 108 and processor cores 110a-n are coupled together by busses 122a-n. *Id.* at [0033]. Therefore, Knoth discloses an interface block (coherency manager 108) coupled to the first set of processor cores (110a) and the second set of processor cores (110n).

Allarey also discloses this limitation. Ex[1003], ¶¶ 141-143. As depicted in FIG. 1, Allarey discloses a power management link (PMLink) 120 (highlighted in green) that couples the cores in site 0 and site 1 (highlighted in yellow). Ex[1006] at 2:59-3:3, FIG. 1A. "[P]ower management link (PMLink) 120 communicatively couples site 0 and site 1." *Id.* at 2:59-3:3.

FIG. 1A of Allarey, annotated

# 9. 1[c2]

Knoth discloses this limitation. Ex[1003], ¶ 144. Knoth discloses that coherency manager 108 "facilitate[s] communications between the first digital circuit and the second digital circuit." Ex[1005] at [0006]. Accordingly, Knoth

teaches that the interface block (coherency manager 108) is configured to facilitate communications between the first set of processor cores 110a and the second set of processor cores 110n.

Allarey also discloses this limitation. Ex[1003], ¶¶ 145-146. Allarey teaches "power management link (PMLink) 120 communicatively couples site 0 and site 1," which is further described as "transmitting data back and forth between site 0 (102) and site 1 (104)." Ex[1006] at 2:59-3:3.

#### C. Claim 5

#### 1. 5[pre]

As explained above for Claim 1, Knoth and Allarey, alone or in combination, disclose each and every limitation of Claim 1.

#### 2. 5[a]

The '339 Patent provides no definition or explanation of the claimed "control signals."

Knoth discloses that "power management unit 102 provides individual frequency management (FM) signals 111a-n" and "individual voltage management (VM) signals 113a-n." Ex[1005] at [0025]. FM signals 111a-n "are used ... to initiate frequency adjustments" and "to individually control/scale the frequency of each processor core 110a-n." *Id.* VM signals 113a-n "are used ... to initiate voltage adjustments" and "to individually control/scale the Voltage of each processor core

110a-n." *Id.* As depicted below, power management unit 102 (highlighted in red) is located in the periphery of Knoth's multi-core processor. *Id.* at FIG. 1A (annotated).

Knoth also discloses that "clock ratio controllers 106a-n ... generate resynchronization (resync) requests 130a-n" that coordinates synchronization between the processor cores and controls timing of synchronization and frequency adjustments. *Id.* at [0029]. "[R]esynchronization requests 130a-n are an indication from clock ratio controllers 106a-n to processor cores 110a-n that a clock ratio adjustment is about to occur." *Id.* As depicted above, clock ratio controllers 106a-n (highlighted in red) are located in the periphery of Knoth's multi-core processor.

The '339 Patent provides no indication that the location of the control blocks would in any way alter their function. See Ex[1003], ¶¶ 153-154. A PHOSITA would have understood that to place a control block in the periphery, centrally, or in other same function of providing control signals locations serves the managing/coordinating the operations of processor cores. *Id.* A PHOSITA would have also understood that this function depends on the logical connections and signal routing, rather than the physical location of the control block relative to the processor. Id. Thus, a control block could be relocated from a substantially central location to the periphery (or vice versa) without affecting its ability to perform this function. Id. A PHOSITA would have understood that the physical location of a control block would have been driven by routine design preferences, such as minimizing of the length of critical paths to other components of the processor. *Id.* Therefore, a PHOSITA reading Knoth would have found it obvious that the control blocks of Knoth could be placed at a periphery of the multi-core processor. *Id.*, ¶¶ 149-154.

Allarey also discloses this limitation. Id., ¶¶ 155-159. Allarey discloses that "there is a master site and a slave site with respect to controlling the voltage level supplied to the voltage plane 106" that supplies supply voltages to the first and second sets of cores of Allarey. Ex[1006] at 2:65-3:3. Specifically, "logic within site

0 (102) dictates the supplied voltage to both site 0 (102) and site 1 (104)" by "send[ing] a voltage identification (VID) value 124 to a voltage regulator 126 external to the processor." *Id.* at 3:4-19. "The voltage regulator 126 interprets the VID value and based on that information, regulates the supplied voltage 128 to the processor 100." *Id.* Voltage identification (VID) value 124 "informs ... the new voltage to supply" "for supplied voltage modifications." *Id.* A PHOSITA reading Allarey would have understood that voltage regulator 126 is responsible for adjusting the voltage supplied to the processor cores and to carry out that function, voltage regulator 126 must internally generate one or more control signals that adjust the output voltage level. Ex[1003], ¶ 157. Such internal control signals are inherently part of how a voltage regulator operates. *Id.*

Therefore, Allarey teaches that the processor cores of Allarey receive one or more control signals including VID value 124 from logic within site 0 (102) (highlighted in red) and the control signals from voltage regulator 126 (highlighted in red). Ex[1006], FIG. 1 (annotated). As depicted below, voltage regulator 126 is located at a periphery of the multi-core processor of Allarey. *Id.*; *see also id.* at 3:5-6 (voltage regulator 126 is located "external to" the processor dies).

FIG. 1 of Allarey, annotated

Furthermore, as explained above, a PHOSITA reading Allarey would have found it obvious that the control blocks including voltage regulator 126 would be placed at a periphery of the multi-core processor without affecting its function of providing control signals to the processor cores. Ex[1003], ¶¶ 154, 159.

# D. Dependent Claim 8

# 1. 8[pre]

As explained above for Claim 1, Knoth and Allarey, alone or in combination, disclose each and every limitation of Claim 1.

# 2. 8[a]

The '339 Patent discloses that a "region" is simply a spatial grouping of cores. *See, e.g.*, Ex[1001] at 2:20-23 ("the regions of multi-core processor 100 may correspond to rows of the two-dimensional array, and the regions may or may not be overlapping"), FIG. 5 ("the second region is adjacent to the first region"); Ex[1003], ¶ 162.

Knoth discloses this limitation. *Id.*, ¶¶ 163-166. Knoth discloses that the multicore processor system comprises an arbitrary number of cores a through n, including at least two sets of processor cores, for example, 110a and the associated cores (e.g., cores b-i) (highlighted in yellow) and 110n and the associated cores (e.g., cores j-n) (highlighted in orange).

FIG. 1A of Knoth, annotated

The first set of cores (core 110a and associated cores 110b-i) are located, for instance, in the physical space depicted below in red dotted box; the second set of cores (core 110n and associated cores 110j-n) are located in the physical space depicted below in green dotted box. As such, Knoth includes a first region corresponding to the physical location reflected by the red dotted box, and a second region corresponding to the physical location reflected by the green dotted box.

FIG. 1A of Knoth, annotated

Alternatively, for instance, the first set of cores (core 110a and associated cores 110b-i) are located in the physical space depicted below in purple dotted box; the second set of cores (core 110n and associated cores 110j-n) of Knoth are located in the physical space depicted below in blue dotted box. As such, Knoth includes a first region corresponding to the physical location reflected by the purple dotted box, and a second region corresponding to the physical location reflected by the blue dotted box.

FIG. 1A of Knoth, annotated

Allarey also discloses this limitation. Ex[1003], ¶¶ 167-170. The multi-core processor system of Allarey comprises multiple cores physically located on two sites. *See, e.g.*, Ex[1006] at 1:52-53, 5:13-33. As discussed above, the multi-core processor of Allarey includes the first set of processor cores (e.g., core 0 (308), core 1 (310), core 2 (312), and core 3 (314)) and the second set of processor cores (e.g., core 4 (316), core 5 (318), core 6 (320), and core 7 (322)).

The first set of cores (core 0 (308), core 1 (310), core 2 (312), and core 3 (314)) of Allarey are located in the physical space depicted below in red dotted box; the second set of cores (core 4 (316), core 5 (318), core 6 (320), and core 7 (322)) of

Allarey are located in the physical space depicted below in green dotted box. As such, Allarey includes a first region corresponding to the physical location where cores 0-3 are located (in red dotted box), and a second region corresponding to the physical location where cores 4-7 are located (in green dotted box).

FIG. 3 of Allarey, annotated

Alternatively, the first set of cores (core 0 (308), core 1 (310), core 2 (312), and core 3 (314)) are located in the physical space depicted below in purple dotted box; the second set of cores (core 4 (316), core 5 (318), core 6 (320), and core 7 (322)) of Allarey are located in the physical space depicted below in blue dotted box.

As such, Allarey includes a first region where cores 0-6 are located, and a second region where cores 1-7 are located.

FIG. 3 of Allarey, annotated

# E. Dependent Claim 9

# 1. 9[pre]

As explained above for Claim 8, Knoth and Allarey, alone or in combination, disclose each and every limitation of Claim 8.

# 2. 9[a]

As explained for Claim 8[a] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation. Ex[1003], ¶¶ 162-171, 173-175.

Again, in Knoth, as depicted below the first set of cores (highlighted in yellow) are located in the physical space in purple dotted box; the second set of cores (highlighted in orange) are located in the physical space in blue dotted box. The first and second regions share some physical space and thus are overlapping.

FIG. 1A of Knoth, annotated

In Allarey, as depicted below, the first set of cores (e.g., core 0 (308), core 1 (310), core 2 (312), and core 3 (314)) are located in the first region in purple dotted box; the second set of cores (core 4 (316), core 5 (318), core 6 (320), and core 7 (322)) of Allarey are located in the second region in blue dotted box. The first and second regions share some physical space and thus are overlapping.

FIG. 3 of Allarey, annotated

## F. Dependent Claim 10

# 1. 10[pre]

As explained above for Claim 8, Knoth and Allarey, alone or in combination, disclose each and every limitation of Claim 8.

# 2. 10[a]

As explained for Claim 8[a] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation. Ex[1003], ¶¶ 162-171, 177-179.

Again, in Knoth, as depicted below, the first set of cores (highlighted in yellow) are located in the physical space in red dotted box; the second set of cores (highlighted in orange) of Knoth are located in the physical space in green dotted

box. The first and second regions are separate in physical layout and thus are nonoverlapping.

FIG. 1A of Knoth, annotated

In Allarey, as depicted below, the first set of cores (core 0 (308), core 1 (310), core 2 (312), and core 3 (314)) are located in the first region in red dotted box; the second set of cores (core 4 (316), core 5 (318), core 6 (320), and core 7 (322)) of Allarey are located in the second region in green dotted box. The first and second regions are separate in physical layout and thus are non-overlapping.

FIG. 3 of Allarey, annotated

# G. Dependent Claim 14

# 1. 14[pre]

As explained above for Claim 1, Knoth and Allarey, alone or in combination, disclose each and every limitation of Claim 1.

# 2. 14[a]

As explained for Claim 5[a] in Ground 1, Knoth discloses this limitation. Ex[1003], ¶¶ 150-152, 181-183. Knoth discloses the control blocks in the form of power management unit 102 (highlighted in red) and clock ratio controllers 106a-n, as depicted below. *Id*.

FIG. 1A of Knoth, annotated

As reviewed for Claim 8 in Ground 1, the '339 Patent provides that a "region" is simply a spatial grouping of cores. Power management unit 102 is positioned centrally relative to the first and second sets of cores Knoth (illustrated by processor core 110a and processor core 110n). *Id.*, ¶ 182.

Furthermore, as explained for Claim 5 in Ground 1, it was a known and obvious design option for a PHOSITA to place the control blocks of Knoth in a common region central to the first and second sets of processor cores. *Id.*, ¶ 183.

Allarey also discloses this limitation. *Id.*, ¶¶ 184-185. Allarey discloses the control blocks in the form of the logic within site 0 (102) and voltage regulator 126.

The logic within site 0 must be part of the circuitry within site 0. A PHOSITA would have understood that the logic within site 0 could be, for example, positioned towards the boundary of site 0 on the side of core 1, thus located substantially central to the first set of cores (illustrated by core 0 (108) and core 1 (110)) and the second set of cores (illustrated by core 0 (112) and core 1 (114)), as illustrated below by the red arrow. Ex[1003], ¶ 184.

FIG. 1 of Allarey, annotated

Furthermore, as explained for Claim 5 in Ground 1, it was a known and obvious design option for a PHOSITA to place the control blocks of Allarey in a common region central to the first and second sets of processor cores. Id., ¶ 185.

### H. Independent Claim 21

#### 1. 21[pre]

To the extent the preamble is limiting, for the same reasons described for Claim 1[Preamble] in Ground 1, Knoth and Allarey, alone or in combination, disclose a multi-core processor. Ex[1003], ¶ 186.

#### 2. 21[a1]

For the same reasons described for Claim 1[a1] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation. Ex[1003], ¶ 187.

#### 3. 21[a2]

For the same reasons described for Claim 1[a2] in Ground 1, Knoth and Allarey, alone or in combination, disclose "wherein each processor core from the first set of processor cores is configured to dynamically receive a first supply voltage" and "a first output clock signal from a first phase lock loop (PLL) having a first clock signal as input."

Knoth further discloses a power control block in the form of voltage controllers 107a-n (shown in dashed blue block) and a clock control block in the form of clock ratio controllers 106a-n (shown in dashed purple block). Ex[1005] at [0027], [0031]; Ex[1003], ¶ 189. Again, Knoth discloses that each processor core 110(a-n) receives its respective supply from voltage controller 107(a-n) and its respective output clock signals core clock signal 128(a-n) output from PLL 202 in

clock ratio controller 106(a-n). Ex[1005] at [0027], [0031]; Ex[1003], ¶ 189.

FIG. 1A of Knoth, annotated

Allarey further discloses a power control block in the form of voltage plane 106/306 (highlighted in red) and a clock control block in the form of PLL circuits 116 and 118 (or 324 and 326) (shown in dashed purple block). *Id.*, ¶ 190. Again, Allarey discloses that the first set of processor cores (e.g., core 0 (108) and core 1 (110) in site 0 (102)) receives the first supply voltage from voltage plane 106, and the first output clock signal from PLL 116 in the PLL circuits that includes PLL 116 and 118. Ex[1006] at 2:41-44, 3:59-3:24. The second set of processor cores (for example, core 0 (112) and core 1 (114) in site 1 (104)) receives the second supply

voltage from voltage plane 106, and the second output clock signal from PLL 118 in the PLL circuits that includes PLL 116 and 118. *Id*.

FIG. 1 of Allarey, annotated

# 4. 21[b1]

For the same reasons described for Claim 1[b1] in Ground 1 and as explained for Claim 21[a1] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation.

# 5. 21[b2]

For the same reasons described for Claim 1[a2], [b2] and Claim 21[a2] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation.

#### 6. 21[b3]

For the same reasons described for Claim 1[b3] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation.

#### 7. 21[b4]

For the same reasons described for Claim 1[b4] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation.

#### 8. 21[c1]

For the same reasons described for Claim 1[c1] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation.

#### 9. 21[c2]

For the same reasons described for Claim 1[c2] in Ground 1, Knoth and Allarey, alone or in combination, disclose this limitation.

# IX. GROUND 2: CLAIMS 2-4 ARE OBVIOUS UNDER §103 OVER KNOTH AND ALLAREY IN VIEW OF FLAUTNER

Knoth and Allarey, alone or in combination, further in view of Flautner disclose each and every limitation of Claims 2-4.

# A. Motivation To Combine Knoth, Allarey, And Flautner

A PHOSITA would have been motivated to combine Knoth and Allarey with Flautner. Ex[1003], ¶¶ 198-204.

To improve the coordination and communication efficiency between the processor cores managed by Knoth's and Allarey's interface block, a PHOSITA

would have been inclined to look beyond the teachings of these references to identify improved configurations as part of the normal course of his/her own research. *Id.*, ¶ 199. For example, a PHOSITA would have been inclined to seek references that cover specific components dedicated to the functions of clock synchronization and level shifting because the processor cores in Knoth and Allarey operate in different voltage domains with different voltage levels and at different frequencies. *Id*. Knoth and Allarey expressly indicate the need for the interface block to perform these functions. *See*, *e.g.*, Ex[1005] at [0002] ("communications and the exchange of data between various components are disrupted until a resynchronization occurs"), [0029]; Ex[1006] at 1:23-24 ("Asynchronous voltage changes during this time may disrupt a PLL lock process.").

Flautner, like Knoth and Allarey, discloses technology in the field of multicore processor systems, specifically addressing the challenges of managing different operational states and power domains within such systems. *See, e.g.*, Ex[1007] at [0047]-[0048] & Fig. 4. Flautner discloses the specific details of the components to handle clock synchronization and voltage level shifting between cores operating at different supply voltages and frequencies. *Id.*; Ex[1003], ¶¶ 200-202.

Applying these teachings to Knoth and Allarey does not require substantial changes and would yield predictable results because such changes amount to a

simple combination of known parts. Ex[1003], ¶ 203. In Knoth's architecture, the addition of Flautner's synchronization module and voltage level shifter would seamlessly integrate into the existing system of independent clock and voltage controllers, enhancing the system's capability to handle cores operating under diverse conditions. *Id.* Similarly, in Allarey's structure, incorporating Flautner's components would address the potential voltage mismatches between sites and improve overall communication efficiency, ensuring that signals are properly synchronized and translated between cores, regardless of their voltage and frequency differences. *Id.*

#### B. Claim 2

# 1. 2[pre]

As explained above for Claim 1, Knoth and Allarey, alone or in combination, disclose each and every limitation of Claim 1.

# 2. 2[a]

Flautner teaches the use of a level shifter. Ex[1003], ¶¶ 206-210. Flautner discloses that the first processor core 40 and the second processor core 42 within separate voltage domains receiving different supply voltage levels. Ex[1007] at [0047]-[0048]. A voltage level shifter 52 is provided between the first processor core 40 and the second processor core 42 to "deal with … the different supply voltage levels (voltage signaling levels) between the two domains." *Id.* Voltage level shifter

52 thus translates the voltage of a signal from the cores in one voltage domain to the expected level associated with the cores in the other domain.

Fig. 4 of Flautner, annotated

A PHOSITA reading Flautner would have understood that translating voltage levels inherently involves translating the corresponding logic levels associated with the cores. Ex[1003], ¶¶ 207-209. When a signal is transmitted between cores operating with different voltage levels, the signal's logic levels may not match the expected input levels of the receiving domain. *Id.* If a signal crosses from one domain to another without adjusting its voltage, it could be misinterpreted by the receiving core. *Id.* Therefore, a voltage level shifter must adjust the signal's voltage so that a logic '1' or '0' in one core remains a logic '1' or '0' in the other core, preserving the intended logic state despite different voltage requirements. *Id.*

To the extent it is argued or found that voltage level shifter 52 has the shared functions between the processor cores in two voltage domains, it would have been obvious to a PHOSITA that voltage level shifter 52 could have separate level shifter modules for the core(s) in each voltage domain because level shifters are standard, routine components and Flautner already has it in the multi-core processor system, and because adding a known level shifter in the processor layout of Knoth or Allarey would require this simple modification. *Id.*, ¶ 210. A PHOSITA would also be motivated to provide dedicated level shifters for each domain to further improve precision of voltage translation across voltage domains. *Id.*

# C. Dependent Claim 3

# 1. 3[pre]

As explained above for Claim 1, Knoth and Allarey, alone or in combination, disclose each and every limitation of Claim 1.

# 2. 3[a]