#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

#### BEFORE THE PATENT TRIAL AND APPEAL BOARD

Silicon Motion Inc.

Petitioner,

v.

K.Mizra, LLC

Patent Owner.

Case No. IPR2024-01241 U.S. Patent No. 9,111,608

# PETITION FOR *INTER PARTES* REVIEW OF CLAIMS 1-2, 4-15 OF U.S. PATENT NO. 9,111,608

. . . . . . . . . . . . . . . . . .

# TABLE OF CONTENTS

| I.          | Introduction1                                                                          |

|-------------|----------------------------------------------------------------------------------------|

| II.         | Mandatory Notices under 37 C.F.R. § 42.82                                              |

| A           | . Real Party in Interest2                                                              |

| B           | . Related Matters2                                                                     |

| С           | . Designation of Lead and Back-Up Counsel3                                             |

| D           | . Service Information                                                                  |

| E           | . Payment of Fees – 37 C.F.R. § 42.1034                                                |

| III.<br>Rev | Petitioner Meets Standing and Eligibility Requirements for <i>Inter Partes</i><br>iew4 |

| IV.         | Background4                                                                            |

| V.          | Summary of the '608 Patent6                                                            |

| A           | . Effective Filing Date and Date of Invention8                                         |

| B           | . Prosecution History of the '608 Patent8                                              |

| С           | . Level or Ordinary Skill in the Art9                                                  |

| VI.         | Claim Construction9                                                                    |

| VII.        | Relief Requested10                                                                     |

| A           | . Proposed Grounds10                                                                   |

| B           | . Qualifying Prior Art11                                                               |

| VIII        | . The Prior Art12                                                                      |

| A           | . Summary of Johnson12                                                                 |

| B           | . Summary of Stubbs15                                                                  |

| С           | . Summary of Moss18                                                                    |

| D           | . Summary of Liou19                                                                    |

| IX.         | Motivations to Combine22                                                               |

| Α           | . Motivation to Combine Johnson and Moss                                               |

| B. Motivation to Combine Johnson-Moss in further view of Liou                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C. Motivation to Combine Stubbs with Moss                                                                                                                                                                                                                                                                                                           |

| D. Motivation to Combine Stubbs-Moss in further view of Liou24                                                                                                                                                                                                                                                                                      |

| E. Motivation to Combine Stubbs-Moss in further view of Johnson25                                                                                                                                                                                                                                                                                   |

| X. Ground 1: Obvious over Johnson, in view of Moss25                                                                                                                                                                                                                                                                                                |

| A. Claim 125                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>B. Claim 2: "The IC memory controller according to claim 1, further comprising storage to store each of first and second delay values corresponding to the delays imparted to the first and second data signals."</li> <li>34</li> </ul>                                                                                                   |

| C. Claim 4: "The IC memory controller according to claim 1, wherein the first and second data signals are delayed to compensate for timing offset between the received first and second data signals."                                                                                                                                              |

| D. Claim 5: "The IC memory controller according to claim 4, further comprising: a first timing signal delay element associated with the first pin; and a second timing signal delay element associated with the second pin; wherein each of the first and second timing signal delay elements impart first and second delays to the strobe signal." |

| E. Claim 6: "The IC memory controller according to claim 1, wherein:<br>each of the first and second delay elements comprise locked-loop circuits<br>having plural serially connected delay elements."                                                                                                                                              |

| F. Claim 7: "The IC memory controller according to claim 6, wherein the first delay value is used to select delay elements of the first delay circuit and the second delay value is used to select delay elements of the second delay circuit."                                                                                                     |

| G. Claim 9: "The IC memory controller according to claim 1, further comprising a calibration circuit to, in a calibration mode, determine the first and second delay values."                                                                                                                                                                       |

| H. Claim 10:40                                                                                                                                                                                                                                                                                                                                      |

| I. Claim 11: "The method according to claim 10, further comprising: in a calibration mode, determining the first and second delay values; and storing the first and second delay values."43                                                                                                                                                         |

| <ul> <li>L. Claim 14: "The method according to claim 11, further comprising: during the calibration mode, calibrating a timing signal delay value corresponding to a delay for application to the strobe signal."</li></ul>                                                                                                                                                                                                                                                                                                                        | y<br>47<br>47<br>48<br>48 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| <ul> <li>during the calibration mode, storing the calibrated timing delay value."</li> <li>XI. Ground 2: Obvious over Johnson, in view of Moss, in further view of Liou 47 <ul> <li>A. Claim 8: "The IC memory controller according to claim 1, further comprising a calibration strobe delay element to impart a calibrated delay to the strobe signal."</li> <li>XII. Ground 3: Obvious over Stubbs, in view of Moss.</li> <li>A. Claim 1</li> <li>B. Claim 2</li> <li>C. Claim 4</li> <li>D. Claim 5</li> <li>E. Claim 6</li> </ul> </li> </ul> | ,47<br>,47<br>,48<br>,48  |

| <ul> <li>Liou 47</li> <li>A. Claim 8: "The IC memory controller according to claim 1, further comprising a calibration strobe delay element to impart a calibrated delay to the strobe signal."</li> <li>XII. Ground 3: Obvious over Stubbs, in view of Moss.</li> <li>A. Claim 1</li> <li>B. Claim 2</li> <li>C. Claim 4</li> <li>D. Claim 5</li> <li>E. Claim 6</li> </ul>                                                                                                                                                                       | y<br>.47<br>.48<br>.48    |

| <ul> <li>comprising a calibration strobe delay element to impart a calibrated delay to the strobe signal."</li> <li>XII. Ground 3: Obvious over Stubbs, in view of Moss.</li> <li>A. Claim 1</li> <li>B. Claim 2</li> <li>C. Claim 4</li> <li>D. Claim 5</li> <li>E. Claim 6</li> </ul>                                                                                                                                                                                                                                                            | .47<br>.48<br>.48         |

| <ul> <li>A. Claim 1</li> <li>B. Claim 2</li> <li>C. Claim 4</li> <li>D. Claim 5</li> <li>E. Claim 6</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                     | .48                       |

| <ul> <li>B. Claim 2</li> <li>C. Claim 4</li> <li>D. Claim 5</li> <li>E. Claim 6</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                           |

| <ul> <li>C. Claim 4</li> <li>D. Claim 5</li> <li>E. Claim 6</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53                        |

| <ul><li>D. Claim 5</li><li>E. Claim 6</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |

| E. Claim 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .56                       |

| F. Claim 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57                        |

| G. Claim 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .58                       |

| H. Claim 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .59                       |

| I. Claim 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .62                       |

| J. Claim 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .63                       |

| K. Claim 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .64                       |

| L. Claim 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .65                       |

| M. Claim 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .66                       |

XIII. Ground 4: Obvious over Stubbs, in view of Moss, in further view of Liou. 67

| А.        | Claim 8                                                               | 67 |

|-----------|-----------------------------------------------------------------------|----|

|           | Ground 5: Obvious over Stubbs, in view of Moss, in further view of on | 68 |

|           | Claim 10                                                              |    |

| A.<br>B.  | Claim 10                                                              |    |

| -         |                                                                       |    |

| C.        | Claim 12                                                              | /1 |

| XV.       | PTAB Discretion Should Not Preclude Institution                       | 72 |

| <b>A.</b> | Board Should Not Exercise Discretion Under 35 U.S.C. § 314(a)         | 72 |

| B.        | Board Should Not Exercise Discretion Under 35 U.S.C. § 325(d)         | 73 |

| XVI.      | Conclusion                                                            | 74 |

# **TABLE OF AUTHORITIES**

# Page(s)

#### Cases

| <i>Apple, Inc. v. Fintiv, Inc,</i><br>IPR2020-00019, Paper 11 (PTAB March 20, 2020)72, 73                    |

|--------------------------------------------------------------------------------------------------------------|

| Edwards Lifesciences Corp. v. Boston Scientific SciMed, Inc.,<br>IPR2017-01295, Paper 9 (PTAB Oct. 25, 2017) |

| <i>HP Inc. v. Slingshot Printing LLC</i> ,<br>IPR2020-01084, Paper 13 (PTAB Jan. 14, 2021)72                 |

| Micron Tech., Inc. v. Godo Kaisha IPR Bridge 1,<br>IPR2020-01007, Paper 15 (PTAB Dec. 7, 2020)72             |

#### **Statutes**

| 11 |

|----|

|    |

|    |

| 73 |

|    |

### **Other Authorities**

| 37 C.F.R. § 42.8      | 2 |

|-----------------------|---|

| 37 C.F.R. § 42.10(b)  | 3 |

| 37 C.F.R. § 42.15(a)  | 4 |

| 37 C.F.R. § 42.103    | 4 |

| 37 C.F.R. § 42.104(a) | 4 |

### PETITIONER'S EXHIBIT LIST

| EX. # | Brief Description                                                                                                                                    |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1001  | U.S. Pat. No. 9,111,608 B2, entitled "STROBE OFFSET CONTROL CIRCUIT", to Best, et al. (the "'608 Patent").                                           |  |  |

| 1002  | Prosecution History of U.S. Pat. No. 9,111,608 B2.                                                                                                   |  |  |

| 1003  | Declaration of R. Jacob Baker, Ph.D., P.E., Regarding U.S. Patent No. 11,640,359.                                                                    |  |  |

| 1004  | U.S. Pat. No. 6,434,081, entitled "CALIBRATION TECHNIQUE FOR MEMORY DEVICES", to Johnson, et al. ("Johnson").                                        |  |  |

| 1005  | U.S. Pub. No. 2003/0099135 A1, entitled "PER-BIT SET-UP AND<br>HOLD TIME ADJUSTMENT FOR DOUBLE-DATA RATE<br>SYNCHRONOUS DRAM," to Stubbs ("Stubbs"). |  |  |

| 1006  | U.S. Pat. No. 6,646,929 B1, entitled "METHODS AND STRUCTURE<br>FOR READ DATA SYNCHRONIZATION WITH MINIMAL<br>LATENTCY," to Moss et al. ("Moss").     |  |  |

| 1007  | U.S. Pub. No. 2003/0179611 A1, entitled "METHOD AND DEVICE<br>FOR CONTROLLING DATA LATCH TIME", to Liou ("Liou")                                     |  |  |

# **Claims Appendix**

| #                                                                                                                                                                                                                            | Limitation Text                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1[pre]                                                                                                                                                                                                                       | An integrated circuit (IC) memory controller comprising:                                                                                                                                                                                                                                                                              |  |  |  |  |

| 1[a]                                                                                                                                                                                                                         | a first pin to receive a first data signal; a first adjustable delay element                                                                                                                                                                                                                                                          |  |  |  |  |

| 1[b]                                                                                                                                                                                                                         | a second pin to receive a second data signal; a second adjustable delay<br>element to delay the received second data signal and generate a second<br>delayed data signal;                                                                                                                                                             |  |  |  |  |

| 1[c]                                                                                                                                                                                                                         | a pin to receive a strobe signal;                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 1[d]                                                                                                                                                                                                                         | a first sampling circuit to sample the first delayed data signal based on<br>the strobe signal; and                                                                                                                                                                                                                                   |  |  |  |  |

| 1[e]                                                                                                                                                                                                                         | a second sampling circuit to sample the second delayed data signal based on the received strobe signal.                                                                                                                                                                                                                               |  |  |  |  |

| 2 The IC memory controller according to claim 1, further comprising<br>2 storage to store each of first and second delay values corresponding<br>the delays imparted to the first and second data signals.                   |                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 4 The IC memory controller according to claim 1, wherein the first<br>4 second data signals are delayed to compensate for timing offset<br>between the received first and second data signals.                               |                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 5                                                                                                                                                                                                                            | The IC memory controller according to claim 4, further comprising: a first timing signal delay element associated with the first pin; and a second timing signal delay element associated with the second pin; wherein each of the first and second timing signal delay elements impart first and second delays to the strobe signal. |  |  |  |  |

| 6                                                                                                                                                                                                                            | The IC memory controller according to claim 1, wherein: each of the first and second delay elements comprise locked-loop circuits having plural serially connected delay elements.                                                                                                                                                    |  |  |  |  |

| 7 The IC memory controller according to claim 6, wherein the first<br>value is used to select delay elements of the first delay circuit and<br>second delay value is used to select delay elements of the second<br>circuit. |                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 8                                                                                                                                                                                                                            | The IC memory controller according to claim 1, further comprising a calibration strobe delay element to impart a calibrated delay to the strobe signal.                                                                                                                                                                               |  |  |  |  |

| 9 The IC memory controller according to claim 1, further comprises of the first a second delay values.                                                                                                                       |                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 10[pre]                                                                                                                                                                                                                                                                                                                                    | A method of operation in an IC memory controller, the method comprising:                                                                                                            |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 10[a]                                                                                                                                                                                                                                                                                                                                      | [a] receiving first and second data signals from a memory device at respective first and second pins;                                                                               |  |  |  |

| <ul> <li>aligning the received first and second data signals with a strobe signation the aligning comprising imparting a first delay to the first data signal the first delay corresponding to a first delay value, imparting a second delay to the second data signal, the second delay corresponding to a second delay value.</li> </ul> |                                                                                                                                                                                     |  |  |  |

| The method according to claim 10, further comprising: in a ca<br>11 mode, determining the first and second delay values; and storin<br>first and second delay values.                                                                                                                                                                      |                                                                                                                                                                                     |  |  |  |

| 12                                                                                                                                                                                                                                                                                                                                         | The method according to claim 11, wherein: during the receiving mode,<br>the imparting the first and second delays includes retrieving the stored<br>first and second delay values. |  |  |  |

| 13                                                                                                                                                                                                                                                                                                                                         | The method according to claim 12, wherein: the first and second data signals are delayed by the first and second delay values.                                                      |  |  |  |

| The method according to claim 11, further comprising: during<br>calibration mode, calibrating a timing signal delay value corres<br>to a delay for application to the strobe signal.                                                                                                                                                       |                                                                                                                                                                                     |  |  |  |

| 15 The method according to claim 14, further comprising: during the calibration mode, storing the calibrated timing delay value.                                                                                                                                                                                                           |                                                                                                                                                                                     |  |  |  |

#### I. Introduction

U.S. Patent 9,111,608 (the "'608 Patent") is invalid. The '608 Patent purports to claim systems and methods for calibrating a memory controller for use with double data rate dynamic random access memory (DDR DRAM). The '608 Patent claims that there was a need "for per-pin (data bit) strobe-offset control and timing calibration to minimize . . . timing offsets for each [data] pin individually." (EX1001, at 2:21-25). But per-pin calibration was already well-known in the art as of the August 20, 2004 priority date. Indeed, numerous prior art references, including those described in this Petition, illustrate per-pin calibration techniques, which they recognize as prior art methods with problems that they aim to overcome.

Further, the claims of the '608 Patent were issued without any substantive rejections by the USPTO, suggesting that the claims were not fully vetted during prosecution. This is apparent in the structure of the claims themselves, which merely claim performing calibration of two pins individually, with no limitations describing how such calibration occurs. Nor are any novel or non-obvious calibration methods specifically claimed. The dependent claims merely add obviously inherent elements of any practical application of a memory controller in DDR DRAM memory. In view of the '608 Patent's attempts to lay claim merely to the concept of per-pin calibration – a technique well known in the art – the Board should hold each challenged claim invalid.

# II. Mandatory Notices under 37 C.F.R. § 42.8A. Real Party in Interest

Petitioner Silicon Motion Inc. is the real party-in-interest. In the litigation identified below, Patent Owner added infringement claims against Silicon Motion Technology Corporation on July 26, 2024. Patent Owner has further alleged that Silicon Motion, Inc. a California corporation ("SM-US"), is an agent or alter ego of Petitioner, which Petitioner disputes. Petitioner's immediate parent company is Silicon Motion Technology (Hong Kong) Limited ("SMHK"). Solely out of an abundance of caution, Petitioner identifies these three related entities as real parties-in-interest, but Petitioner maintains that these entities do not satisfy the legal criteria for being real parties-in-interest. Neither SM-US nor SMHK have been sued by Patent Owner.

#### **B.** Related Matters

The following judicial or administrative matters may be affected by a decision in this proceeding:

- *K.Mizra LLC v. Silicon Motion Inc.*, No. 2:24-cv-00101 (E.D. Tex. Feb. 15, 2024) ("District Court Litigation").

- U.S. Patent Application 18/094,895, which claims priority to the application issued as the '608 Patent.

### C. Designation of Lead and Back-Up Counsel

Petitioner appoints the following as lead and backup counsel:

| LEAD COUNSEL                   | BACK-UP COUNSEL                   |

|--------------------------------|-----------------------------------|

| Jeffrey Johnson                | Parker Hancock                    |

| BAKER BOTTS L.L.P.             | BAKER BOTTS L.L.P.                |

| 910 Louisiana Street           | 910 Louisiana Street              |

| Houston, TX 77002              | Houston, TX 77002                 |

| Phone: (713) 229-1222          | Phone: (713) 229-11196            |

| Fax: (713) 229-7922            | Fax: (713) 229-2896               |

| Jeffrey.Johnson@bakerbotts.com | Parker.Hancock@bakerbotts.com     |

| USPTO Reg. No. 53,078          | USPTO Reg. No. 73,667             |

|                                |                                   |

|                                | Robert Benson                     |

|                                | (Pro hac vice forthcoming)        |

|                                | BAKER BOTTS L.L.P.                |

|                                | 101 California Street, Suite 3200 |

|                                | San Francisco, CA 94111           |

|                                | Phone: (415) 291-6285             |

|                                | Fax: (415) 291-6385               |

|                                | Robert.Benson@bakerbotts.com      |

|                                | Ŭ Ŭ                               |

### **D.** Service Information

Petitioners consent to electronic service at DLSiliconIPR608@bakerbotts.com. A Power of Attorney is filed concurrently herewith under 37 C.F.R. § 42.10(b).

#### E. Payment of Fees – 37 C.F.R. § 42.103

Silicon Motion authorizes the USPTO to charge Deposit Account No. 02-0384 for the fee set forth in 37 C.F.R. § 42.15(a) for this Petition and further authorizes payment for any additional fees to be charged to this deposit account.

# **III.** Petitioner Meets Standing and Eligibility Requirements for *Inter Partes* Review.

Petitioner certifies under 37 C.F.R. § 42.104(a) that the '608 Patent "is available for *inter partes* review and that the Petitioner is not barred or estopped from requesting an *inter partes* review challenging the patent claims on the grounds identified in the petition." Patent Owner sued Petitioner and other real parties in interest less than one year ago, on February 15, 2024.

#### **IV.** Background

The '608 Patent is directed to the field of double-data rate dynamic random access memory (DDR DRAM). (EX1001, EX1003, ¶30). DDR DRAM systems are memory devices used in computer systems as a form of high-speed read/write volatile memory. (EX1003, ¶30). The "double data rate" refers to the fact that DDR DRAM systems can read and write data on both the rising and falling edges of a system clock signal, and thus can transfer data at double the system clock speed. (EX1003, ¶30). In read-and-write operations, DDR DRAM systems use a "data clock" or "strobe signal," sometimes referred to as DQS or DCLK, to indicate when data on various pins should be read. . (EX1003, ¶30).

A known problem with such systems is that propagation delay caused by the physical path between the data and the strobe signal can cause a misalignment between the data present on a specific pin and the strobe signal. (EX1003, ¶30). Thus, it was known in the art to insert delay elements between the strobe signal and/or the data pin and to calibrate these delay elements to ensure the strobe signal data signals are aligned. (EX1003, ¶32).

Adjustable delay elements, such as delay-locked loop (DLL) devices, were also well-known at the time of the alleged invention of the '608 patent. (EX1003, ¶31). DLL devices contain a chain of serially connected delay elements that introduce controllable delays into an output signal, each delay element creating a delayed version of the input signal. (EX1003, ¶31). The device also includes a phase detector that compares the phase difference between a reference signal and the delayed output signal, producing an error signal. (EX1003, ¶31). It was well-known at the time of the invention of the '608 Patent that DLLs could be used as delay elements to solve the problem of misaligned data and strobe signals caused by propagation delay. (EX1003, ¶31).

Further, at the time of the alleged invention, it was well-known that calibration of data paths in a memory controller could be performed on a per-bit, half-byte (4 bits), per-byte (8 bits), or per-word (16 bits) basis. (EX1003, ¶34).

#### V. Summary of the '608 Patent

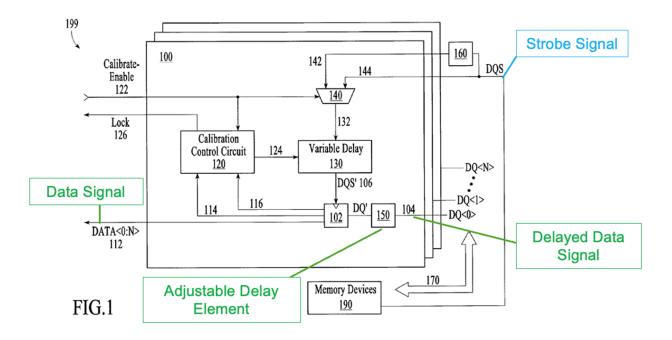

The '608 Patent is directed to alleged improvements in memory controllers using delay elements to ensure alignment between data and strobe signals. (EX1001, at 3:16-34, EX1003, ¶38). The '608 Patent purports to solve problems related to propagation delay by providing systems and methods for automatically calibrating the strobe delay on a per-bit basis, rather than on a per-byte basis. (Id.) Figure 1 illustrates an embodiment:

(EX1001, Fig 1 (annotated excerpt)).

The issued claims of the '608 Patent recite only a few components. (EX1003, ¶¶38-40). Independent Claim 1 recites two data pathways, each comprising a pin to receive a data signal, an adjustable delay element to delay the data signal, and a sampling circuit that samples the delayed data signal. (EX1003, ¶38). Claim 1 also

recites a pin to receive a strobe signal, and the sampling circuits of the two data pathways sample the delayed data signal based on that strobe signal. (EX1003, ¶¶38-40). Independent claim 10 and dependent claim 9 recite aligning two data pathways, each pathway including a data pin, and aligning them by imparting a delay to each data line. (EX1003, ¶41).

The remaining claims likewise recite only generic components or merely describe the purpose of elements already disclosed. (EX1003, ¶42). Dependent claims 2, 11, and 12 merely recite storage and retrieval of delay values for the first and second pins. (EX1003, ¶43). Dependent Claim 4 merely recites the purpose of the claimed invention, namely, that the delays applied to the first and second pins are to "compensate for timing offset between the received first and second data signals." (EX1003, ¶44). Claim 5 merely recites that each data pin likewise has a "timing signal delay element" associated with that pin to delay the strobe signal provided to each. (EX1003, ¶45). Claims 6 and 7 merely recite the use of a well-known delay-locked loop device as the delay devices in each of the data paths. (EX1003, ¶46). Claims 8, 14, and 15 recite the use of a "calibrated delay" applied to a data strobe signal during calibration. (EX1003, ¶47).

Finally, claim 13 (which is indefinite) recites delaying the data signals by a delay value. (EX1003, ¶56). Claim 13 is indefinite because its antecedent claim 10 recites that the actual delay imparted to the data signal "correspond[s] to" the actual

delay value. (Id.). This would make sense to a POSITA, because such delay values are likely control signals or voltages applied to the delay element. (Id.). However, Claim 13 recites delaying the signals "by" the "first and second delay values." Such a claim makes no sense, because delays are measured in seconds, whereas the delay values are voltages or signals. (Id.). Nonetheless, if it is assumed that Claim 13 were rewritten to recite that the data signals are "delayed by a delay corresponding to the first and second delay values," the claim is still invalid as it merely recites the basic functioning of the device claimed in Claim 10. (Id.).

#### A. Effective Filing Date and Date of Invention

The '608 Patent claims priority through a chain of continuation applications back to Application No. 10/923,421, filed on August 20, 2004. EX1001, cover. Solely for the purposes of this IPR, Petitioner assumes, but does not concede, an effective filing date of August 20, 2004 for the '608 Patent. Pre-AIA 35 U.S.C. §§ 102 and 103 apply.

#### **B.** Prosecution History of the '608 Patent

The application, which was issued as the '608 Patent, was filed on March 31, 2014. (EX1002, 140). In a Preliminary Amendment filed on May 1, 2014, the Applicant amended the claims to strip out numerous substantive limitations. (EX1002, 59-63). The application, with the amended claims, was allowed on April

16, 2015, without receiving any substantive rejections from the Examiner. (EX1002, 17-23).

#### C. Level or Ordinary Skill in the Art

A POSITA, as of August 20, 2004, would have at least a Bachelor's degree in Electrical Engineering, Computer Engineering, or a related field, and 2-3 years of experience in memory system design. (EX1003, ¶ 26-29). Alternatively, a POSITA could have a Master's degree in one of those fields and 1-2 years of relevant experience. (EX1003, ¶26-29).

#### VI. Claim Construction

The Board construes claims under the same construction standard as civil actions in federal district court. Petitioner asserts that no construction is necessary for any terms for the purposes of this Petition as the challenged claims are invalid under any reasonable construction.

Nonetheless, and to avoid any unnecessary disputes, Petitioner proposes that the term "pin" carry its plain and ordinary meaning as would be understood by a person of ordinary skill, which is simply a "signal path." (EX1003, ¶¶52-55). This understanding is consistent with how that term is used in the '908 Patent, which refers to "pin-to-pin offsets in the DRAM," by which it simply refers to data traveling on a signal path. (EX1004, at 1:63-66, EX1003, ¶¶52-55). Further, Claim 13 is indefinite, and no reasonable construction can save that claim from indefiniteness. (EX1003, ¶¶ 56-57). Claim 13 recites that "the first and second data signals are delayed by the first and second delay values." (EX1003, ¶¶ 56-67). But this does not make sense, as would have been appreciated by a POSITA. (EX1003, ¶¶ 56-67). In digital systems, delay values are typically represented as control signals or voltages that are applied to delay elements (EX1003, ¶¶ 56-67). But delays are measured in terms of seconds or fractions thereof. (EX1003, ¶¶ 56-67). These control signals or voltages instruct the delay elements on how much delay to introduce, but they are not the delays themselves, which are measured in seconds. (EX1003, ¶¶ 56-67).

Even if it were assumed that Claim 13 was rewritten to recite that the data signals are "delayed by a delay corresponding to the first and second delay values," the claim is still invalid as it merely recites the basic functioning of the device claimed in Claim 10, and thus adds no further limitation to that claim. (EX1003, ¶ 57). Nonetheless, solely for the purposes of this Petition, Petitioner assumes that Claim 13 is so rewritten.

#### VII. Relief Requested

#### A. Proposed Grounds

#### a. Ground 1

Claims 1-2, 4-7, and 9-15 are invalid under 35 U.S.C. § 103 over Johnson (EX1004) in view of Moss (EX1006).

#### b. Ground 2

Claim 8 is invalid under 35 U.S.C. § 103 over Johnson (EX1004), in view of Moss (EX1006), in further view of Liou (EX1007).

#### c. Ground 3

Claims 1-2, 4-7, and 9-15 are invalid under 35 U.S.C. § 103 over Stubbs (EX1005), in view of Moss (EX1006).

#### d. Ground 4

Claim 8 is invalid under 35 U.S.C § 103 over Stubbs (EX1005), in view of Moss (EX1006), in further view of Liou (EX1007).

#### e. Ground 5

Claims 10-12 are invalid under 35 U.S.C. § 103 over Stubbs (EX1005), in view of Moss (EX1006), in further view of Johnson (EX1004).

#### **B.** Qualifying Prior Art

The references relied upon in the grounds above qualify as prior:

| Prior Art Reference                                               | Filing Date   | Publication /<br>Issue Date | Applicable<br>Section of 35<br>U.S.C. § 102 |

|-------------------------------------------------------------------|---------------|-----------------------------|---------------------------------------------|

| U.S. Patent 6,434,081 to<br>Johnson et al. ("Johnson",<br>EX1004) | May 12, 2000  | Aug. 13, 2002               | (b) and (e)                                 |

| U.S. Pub. 2003/0099135 to<br>Stubbs ("Stubbs", EX1005)            | Nov. 26, 2001 | May 29, 2003                | (b) and (e)                                 |

| U.S. Patent 6,646,929 to Moss<br>et al. ("Moss", EX1006) | Dec. 5, 2001  | Nov. 11, 2003  | (b) and (e) |

|----------------------------------------------------------|---------------|----------------|-------------|

| U.S. Pub. 2003/0179611 to<br>Liou ("Liou", EX1007)       | Dec. 26, 2002 | Sept. 25, 2003 | (e)         |

#### VIII. The Prior Art

#### A. Summary of Johnson

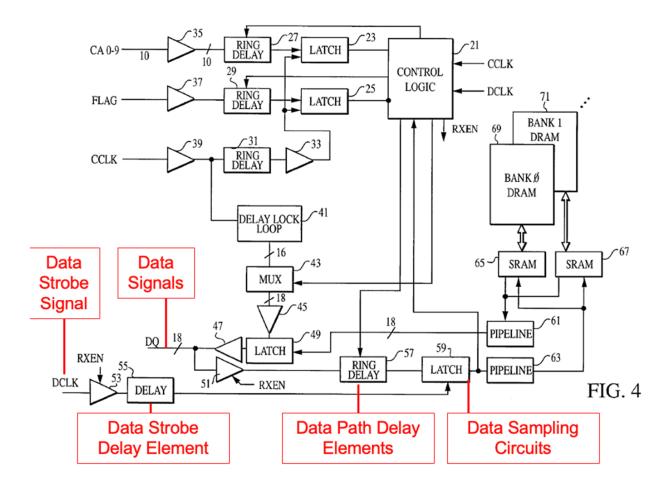

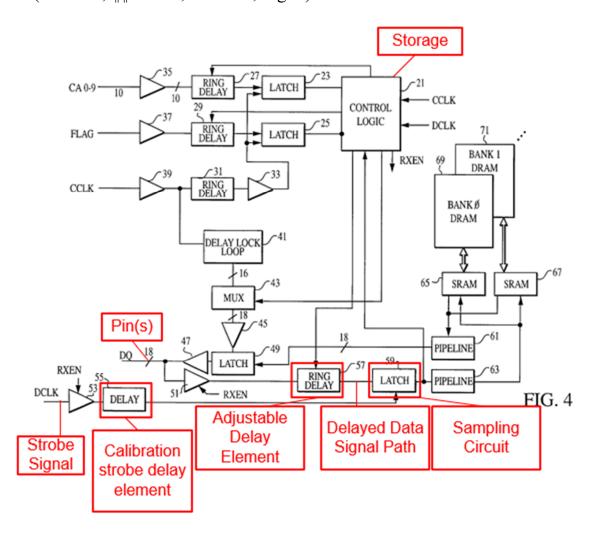

U.S. Patent 6,434,081, entitled "Calibration Technique for Memory Devices," to Johnson et al. ("Johnson")(EX1004) discloses systems and methods for calibrating data paths in a DDR DRAM memory device. (EX1003, ¶58; EX1004, Abstract, 1:11-2:2). Johnson discloses an improvement in existing calibration methods that ensures the synchronization of per-bit calibration across various data pins. (EX1004, ¶58; EX1004, at 2:3-14). That is, Johnson recognizes the existence of per-bit calibration techniques and solves a problem that can be created in such systems. Fig. 4 illustrates the system described in Johnson:

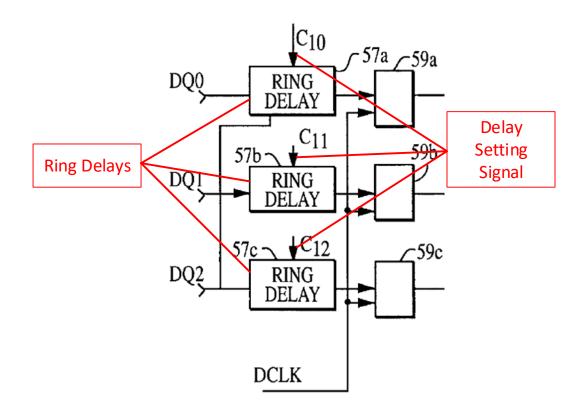

(EX1004, ¶59; EX1004, Fig. 4 (annotated excerpt)). Johnson describes that "[d]ata which is to be input into memory banks 69, 71" passes "through ring delays 57 on each path of the data bus, into latches 59." (EX1004, ¶¶60-62; EX1004, 4:12-19).

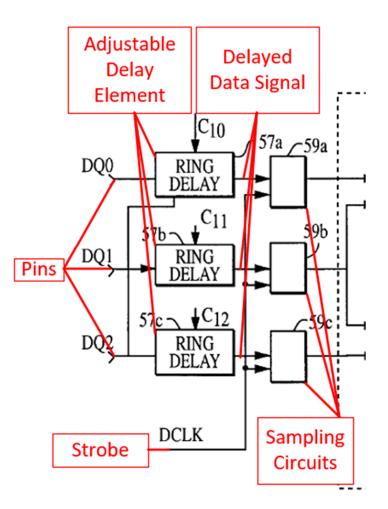

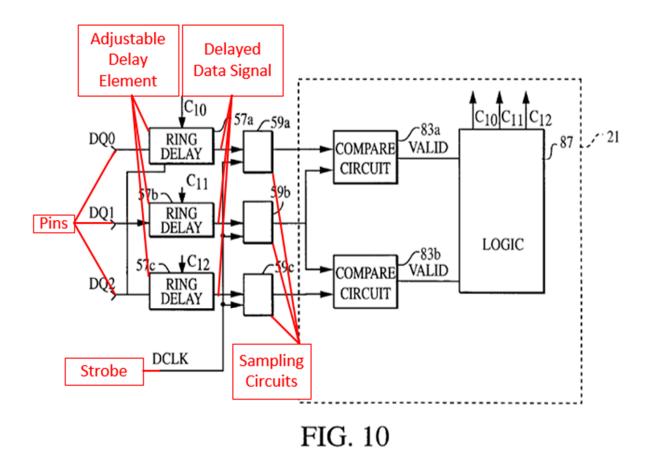

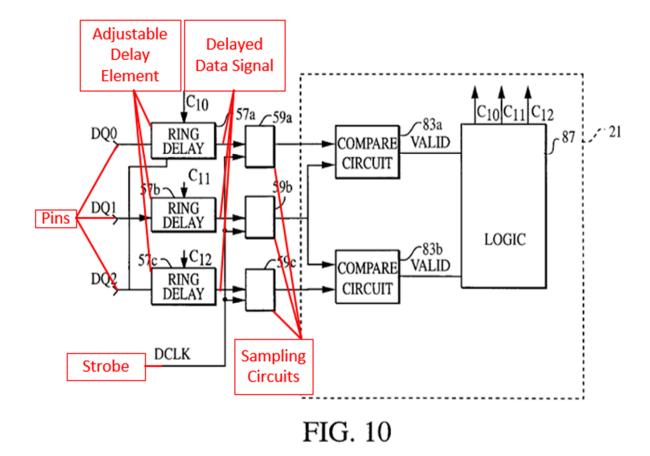

Johnson further discusses improvements to the per-bit calibration system shown in Fig. 4. (EX1003, ¶63). An example embodiment is shown in Fig. 10:

(EX1004, at Fig. 10 (annotated excerpt)). Pins DQ0, DQ1, and DQ2 represent three pins in a data bus. (EX1003, ¶¶64-66; EX1004, at 7:35-36). Ring delay elements 57a-c are adjustable delay circuits that delay the data received at pins DQ0, DQ1, and DQ2 by a delay controlled by control signals C10, C11, and C12. (EX1003, ¶¶64-66; EX1004, 3:49-67, 7:30-35). Latches 59a-c are used to sample the delayed data received from the ring delay elements 57a-c in response to the data strobe signal DCLK. (EX1003, ¶¶64-66; EX1004, at 4:12-26). The control logic circuit 21 is responsible for determining appropriate control signals C10, C11, and C12 to enable

the memory device to properly read data lines DQ0, DQ1, and DQ2. (EX1003, ¶¶67-71; EX1004, 7:25-60). The control logic circuit stores delay values corresponding to the delays that result in the successful alignment of the data signals. (EX1003, ¶¶67-71; EX1004, 5:32-6:1, 7:45-61). During operation, the stored delay values are retrieved and used to delay the data signals. (EX1003, ¶¶67-71; EX1004, 5:32-6:1, 7:45-61).

#### **B.** Summary of Stubbs

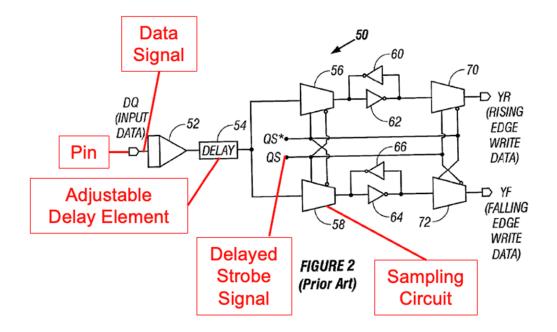

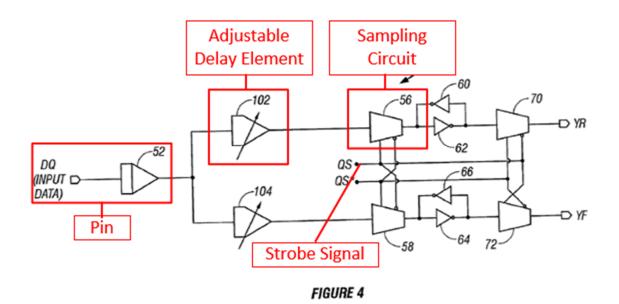

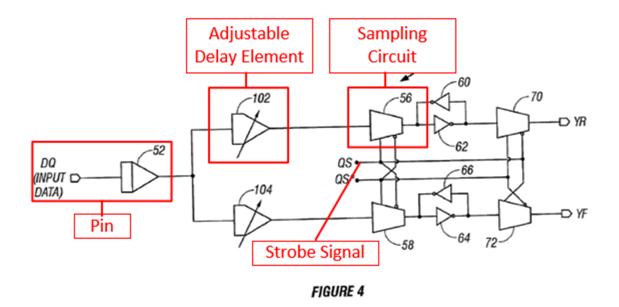

Stubbs (EX1005) discloses a memory controller for a DDR DRAM device. (EX1003, ¶72; EX1005, Abstract). Stubbs explains that a known problem is that different devices can have different propagation delays, causing misalignment between a data strobe and a data read/write operation. (EX1003, ¶72; EX1005, [0006], [0013-0015]). To solve this problem, Stubbs describes using delay-locked loop ("DLL") circuits to account for differences in propagation delay. (EX1003, ¶73; EX1005, [0010-0013]). Stubbs describes as prior art a system applying DLL circuits to both a data strobe and a data signal, as shown in Fig. 2:

(EX1005, Fig. 2 (annotated excerpt)). The "pin" is the data line DQ data input line. (EX1003, ¶73; EX1005, [0033]). Delay element 54 is a variable delay element applied to the data signal. (EX1003, ¶73; EX1005, [0033]). The data strobe signal (QS/QS\*) and the delayed data signal are provided to pass gate 58, which are sampling devices that "function to selectively allow the data appearing at their respective inputs to be presented at their respective outputs under the control of the data strobe (clock) signal QS/QS\*." (EX1003, ¶73; EX1005, [0034]). Stubbs further discloses that the data strobe signal (QS/QS\*) can be produced using a DLL circuit and is, thus, itself a delayed strobe signal. (EX1003, ¶73; EX1005, [0035]).

Stubbs explains that this prior art method of using DDL circuits on a per-bit basis to adjust the delay in reading data can cause problems if the propagation delays on the rising edge and falling edge are different. (EX1003, ¶74; EX1005, [0041-

0045]). Stubbs, therefore, discloses an improved memory controller device that provides two adjustable delay elements for each pin, one for the rising edge and the other for the falling edge of the clock signal. (EX1003, ¶75; EX1005, Abstract, [0018]). The delays are separately adjustable for data present during the rising edge of the data strobe signal and for data present during the falling edge of the data strobe signal, allowing the setup and hold window for write data to be optimized on a per-bit basis rather than a per-cycle basis. (EX1003, ¶75; EX1005, Abstract, [0018]). Fig. 4 is illustrative.

(EX1005, Fig. 4 (annotated)). Stubbs discloses various embodiments of the write path circuitry. In one embodiment shown in Figure 4, the write path circuitry includes an input buffer 52 that receives the input data signal, with the output of the input buffer coupled to first and second adjustable delay elements 102 and 104.

(EX1003, ¶76; EX1005, [0047]). The delayed data signal output from delay element 102 is applied to the input of a first pass gate 56, while the delayed data signal output from delay element 104 is applied to the input of a second pass gate 58. (EX1003, ¶76; EX1005, [0047]). The pass gates 56 and 58 are controlled by the data strobe signal to pass the delayed data signals at the appropriate time. (EX1003, ¶76; EX1005, [0047-0048]).

#### C. Summary of Moss

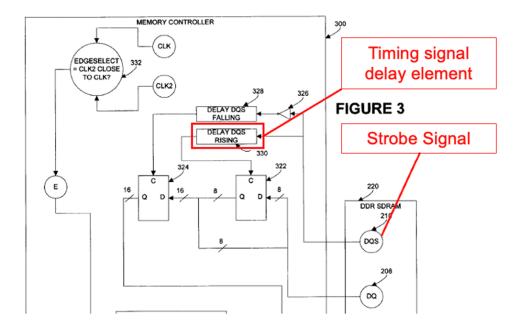

Moss (EX1006) discloses a memory controller for use with DDR DRAM devices to compensate for timing differences between the memory controller's clock signal (CLK) and a strobe signal (DQS) from the memory devices. (EX1003, ¶77; EX1006, Abstract, 4:17-36, 5:34-47, Fig. 3). The memory controller includes programmable delay lines (306, 328, 330) that delay the CLK and DQS signals to align the timing of the signals for capturing read data (DQ). (EX1003, ¶77; EX1006, 5:52-6:25).

(EX1006, Fig. 3 (annotated excerpt)). The delay values for the programmable delay lines are predetermined during a calibration phase based on an analysis of the design or through automated measurements. (EX1003, ¶78; EX1006, 6:52-65). These delay values are then used during normal operation to adjust the timing of the CLK and DQS signals to compensate for propagation delays and align the read data capture. (EX1003, ¶79; EX1006, 5:55-6:3, 6:26-36, 7:55-8:4). By delaying the CLK and DQS signals using the calibrated delay values, the memory controller can capture the read data using the delayed clock signal (CLK2) in alignment with the delayed DQS signal. (EX1003, ¶80; EX1006, 2:18-42, 3:1-8, 6:48-58).

#### **D.** Summary of Liou

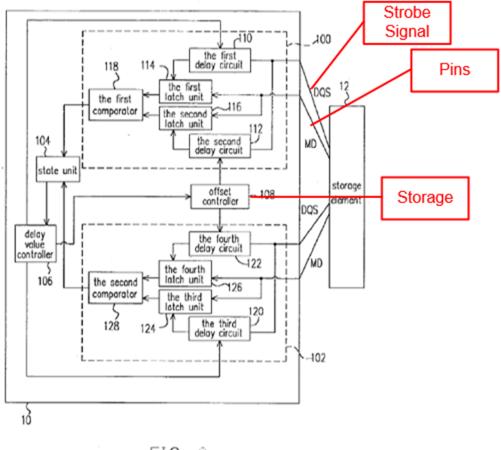

Liou (EX1007) discloses a device and method for controlling data latch timing in a memory system. (EX1003, ¶81; EX1007, Abstract, [1003]). The device includes a control chip that couples to a storage element, receives a data strobe signal (DQS) and memory data signal (MD), and delays DQS to latch the MD signal. (EX1003, **\$\$1**, **\$\$1**, **\$\$21007**, [0018], **\$\$1**, **\$\$2**, **\$\$1**, **\$\$1**, **\$\$0**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$0**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**, **\$1**,

FIG. 2

(EX1007, Fig. 2 (annotated)). A delay value controller provides the controlled delay value, which can be initially set by the BIOS during system initialization. (EX1003, ¶84; EX1007, [0021]). The delay value controller adjusts the controlled delay value based on the comparison results to compensate for timing offsets caused by temperature and voltage variations. (EX1003, ¶85; EX1007, [0025-0031], Claims 8-10, 17-18). In this way, Liou discloses a broad, adjustable memory interface that can ensure accurate data capture despite variable operating conditions. (EX1003, ¶87; EX1007, [0007], [0011-0012], [0028-0030]).

#### IX. Motivations to Combine

A POSITA would have been motivated to combine each of the asserted combinations to arrive at the challenged claims. (EX1003; ¶88. Each of Johnson, Stubbs, Moss, and Liou relate to memory controllers for use in DDR DRAM devices and, more specifically, to systems and methods for overcoming issues associated with propagation delays that can cause misalignment between strobe signals and data signals. (EX1003, ¶88; EX1004, 2:44-54; EX1005, [0006-0007]; EX1006, 4:37-64, EX1007, [0005-0007]). Thus, all the references asserted here are analogous art because they are in the same field of endeavor, specifically, memory controllers and components thereof for DDR DRAM devices. (EX1003, ¶88).

#### A. Motivation to Combine Johnson and Moss

A POSITA would have been motivated to combine Johnson and Moss. (EX1003, ¶¶89-93). As discussed above, both Johnson and Moss are in the same field of endeavor. (EX1003, ¶¶89-93). A POSITA in possession of Johnson would look to Moss for further disclosure on systems and methods for delaying the data strobe (DQS) signal to produce an improved memory controller. (EX1003, ¶¶89-93). In particular, Johnson already discloses the concept of adding a delay element to the data strobe signal. (EX1004, Fig. 4, element 55). (EX1003, ¶¶89-93). To provide enhanced flexibility, a POSITA in possession of Johnson would look to Moss to incorporate a plurality of delay elements to the data strobe signal. (EX1003, ¶¶89-

93). Moss discloses applying a delay element to the data strobe signal DQS 210 using delay element 330. (EX1006, Fig. 3). (EX1003, ¶¶89-93). Moss further discloses that the size of the data path – i.e. the number of data pins in each data path – is a design choice well within the knowledge and ability of a POSITA, and expressly recites examples of 4, 8, and 16-bit wide data paths. (EX1003, ¶¶89-93; EX1006, 6:47-48).

#### **B.** Motivation to Combine Johnson-Moss in further view of Liou

As discussed above, a POSITA would have been motivated to combine Johnson and Moss to arrive at a memory controller with multiple delay elements, one for each data path. (EX1003, ¶¶94-96). A POSITA would have been further motivated to combine Johnson-Moss with Liou. (EX1003, ¶¶94-96). Liou, like Johnson and Moss, discloses a memory controller for DRAM memory. (EX1003, ¶¶94-96). EX1007, at Abstract, [0005]). Liou provides further disclosure regarding the use of delay elements on the data strobe signal. (EX1003, ¶¶94-96). A POSITA in possession of Johnson-Moss for further disclosure and details regarding the use of delay elements on the data strobe signal. (EX1003, ¶¶94-96).

#### C. Motivation to Combine Stubbs with Moss

A POSITA would have been motivated to combine Stubbs with Moss. (EX1003, ¶¶97-100). As discussed above, both Stubbs and Moss are in the same field of endeavor. (EX1003, ¶¶97-100). A POSITA in possession of Stubbs would

look to Moss for additional details disclosing how to provide a delayed data strobe signal. (EX1003, ¶¶97-100; EX1006, [0035]). Moss provides additional details on delaying a data strobe signal using a delay element. (EX1003, ¶¶97-100; EX1006, Fig. 3, 6:47-48). Further, Moss further discloses that the size of the data path – i.e., the number of data pins in each data path – is a design choice well within the knowledge and ability of a POSITA and expressly recites examples of 4, 8, and 16-bit wide data paths. (EX1003, ¶¶97-100; EX1006, 6:47-48). Thus, a POSITA in possession of Stubbs and Moss would realize that delay elements on the data strobe line could be further modified to provide a delay element for each bit. (EX1003, ¶¶97-100).

#### D. Motivation to Combine Stubbs-Moss in further view of Liou

A POSITA would have been motivated to combine Stubbs and Moss to arrive at a memory controller with multiple delay elements, one for each data path. (*See supra*, § IX.C). A POSITA would have been further motivated to combine Stubbs-Moss with Liou. (EX1003, ¶¶100-103). Liou, like Stubbs and Moss, discloses a memory controller for DRAM memory. (EX1003, ¶¶100-103; EX1007, at Abstract, [0005]). Liou provides further disclosure, as discussed below, regarding the use of delay elements on the data strobe signal. (EX1003, ¶¶100-103). A POSITA in possession of Johnson-Moss for further disclosure and details regarding the use of delay elements on the data strobe signal. (EX1003, ¶¶100-103).

#### E. Motivation to Combine Stubbs-Moss in further view of Johnson

As discussed above, a POSITA would have been motivated to combine Stubbs and Moss to arrive at a memory controller with multiple delay elements, one for each data path. (*See supra*, § IX.C; EX1003, ¶¶104-108). A POSITA would further be motivated to combine Stubbs-Moss with Johnson to provide a specific calibration method for use with the physical systems provided in Stubbs and Moss. (EX1003, ¶¶104-108). The calibration technique and associated control circuitry of Johnson could be used directly with the Stubbs-Moss combination to arrive at the claimed methods. (EX1003, ¶¶104-108). This would have been a simple substitution of components, replacing the delay circuity of Johnson with the systems described in Stubbs-Moss. (EX1003, ¶¶104-108).

#### X. Ground 1: Obvious over Johnson, in view of Moss

#### A. Claim 1

# a. Element 1[pre]: "An integrated circuit (IC) memory controller comprising"

If the preamble is limiting, Johnson discloses this limitation. (EX1003, ¶110). Johnson describes an "integrated memory circuit." (EX1003, ¶110; EX1004, Claim 67). Moss also discloses this limitation. Moss implements a memory controller as an integrated circuit, allowing for efficient signal routing and timing control within a single chip. (EX1003, ¶111; EX1006, Fig. 3).

# b. Element 1[a]: "a first pin to receive a first data signal; a first adjustable delay element to delay the received first data signal and generate a first delayed data signal;"

Johnson discloses limitation 1[a]. Johnson's memory device includes multiple data paths for receiving data signals, each with an associated adjustable delay element. (EX1003, ¶112-14; EX1004, Fig. 4).

(EX1004, Fig. 4 (annotated)). Specifically, Johnson shows a data path DQ that includes a pin to receive an incoming data signal and a ring delay 57 to delay that received data signal. (EX1003, ¶¶112-14; EX1004, Fig. 4, 7:25-60). The ring delay

57 is an adjustable delay element that can impart different amounts of delay to the received data signal, generating a delayed version which is then provided to latch 59. (EX1003, ¶¶112-14; EX1004, Fig. 4, 4:13-18, 7:25-60).

The adjustable nature of the delay element allows the memory device to calibrate the timing of data signals relative to a clock signal, compensating for timing variations and ensuring proper sampling of the data signal. (EX1003, ¶¶112-14; EX1004, 1:38-43, 4:38-43, 7:54-59). Thus, Johnson discloses both a first pin to receive a first data signal and a first adjustable delay element to delay the received first data signal and generate a first delayed data signal as recited in limitation 1[a].

Even if Johnson did not disclose this feature, Moss also discloses limitation 1[a]. Moss describes a memory controller that receives data signals, including data signal DQ, from a memory component via pins. (EX1003; ¶¶115-17; EX1006, Fig. 3, 5:51-55, 6:28-36). The controller includes delay line 330, an adjustable delay element that delays the data strobe signal DQS controlling the sampling of the data signal DQ, effectively delaying the received data signal and generating a delayed version. (EX1003; ¶¶115-17; EX1006, Fig. 3, 6:16-63). Thus, Moss discloses both a first pin to receive a first data signal and a first adjustable delay element to delay the received first data signal and generate a first delayed data signal as recited in limitation 1[a].

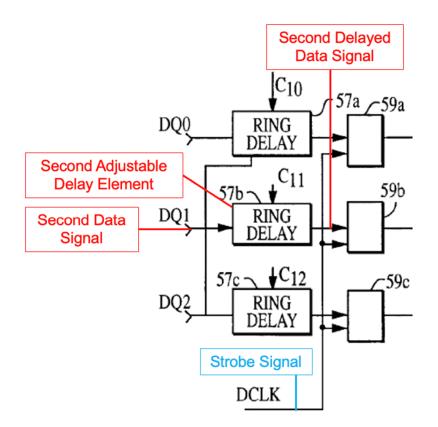

#### c. Element 1[b]: "a second pin to receive a second data signal; a second adjustable delay element to delay the received second data signal and generate a second delayed data signal;"

Johnson discloses this limitation. (EX1003, ¶119). As described above with reference to Element 1[a], Johnson discloses a "first pin to receive a first data signal" (signal DQ0), a "first adjustable delay element" (ring delay 57a), that generates a "first delayed data signal." (input to latch 59a). In the same manner, Johnson also discloses a "second pin to receive a second data signal" (signal DQ1), a "second adjustable delay element" (ring delay 57b) that generates a "second data signal" (input to latch 59b). (EX1003; ¶199; *See, e.g.* EX1004, 4:36-52, 7:24-60)

(EX1004, Fig. Even if Johnson did not disclose this feature, Moss does. (EX1003; ¶120). Moss's memory controller includes circuitry to receive and process multiple data signals from memory components via a data bus DQ, which comprises multiple data pins. (EX1003, ¶120; EX1006, 1:15-40, 5:25-28, Fig. 3). The controller's delay elements, such as delay line 330, delay the received data signals, effectively generating delayed versions of these signals. (EX1003, ¶120; EX1006, 6:16-23, 6:28-36).

A POSITA would have been motivated to combine Johnson's multiple data pins with adjustable delays and Moss's multi-pin data bus with delay elements, as both address timing control for multiple data signals in memory systems. (EX1003; ¶121).

#### d. Element 1[c]: "a pin to receive a strobe signal;"

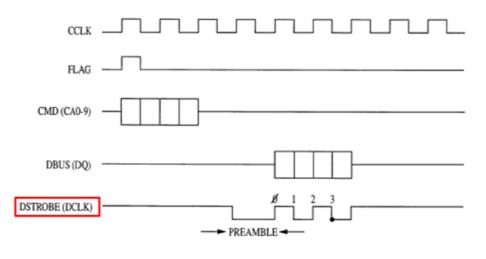

Johnson discloses a pin to receive a strobe signal DCLK, which is used to clock data into and out of the memory device. (EX1003, ¶¶122-23; EX1004, Fig. 4, 4:24-5:7). This DCLK strobe signal serves the same purpose as the strobe signal in the challenged patent, timing the sampling of data signals. (EX1003, ¶¶122-23, EX1004, 4:24-5:7, Fig. 5).

FIG. 5

#### (EX1004, Fig. 5 (annotated)).

Even if Johnson did not disclose this feature, Moss does. (EX1003, ¶¶124-25). Moss discloses a memory controller with a pin to receive a strobe signal DQS from an associated memory component, which is applied to delay lines within the controller. (EX1003, ¶¶124-25; EX1006, 5:48-60, 6:16-22, Fig. 3). A POSITA would have been motivated to combine Johnson's pin for receiving data signals with Moss's adjustable delay elements for data signal timing, as both address timing control in memory systems to improve data transfer efficiency. (EX1003, ¶126).

### e. Element 1[d]: "a first sampling circuit to sample the first delayed data signal based on the strobe signal; and"

Johnson discloses this limitation. (EX1003, ¶¶127-28). Referring to Figure 10, the latch 59a serves as a "first sampling circuit to sample the first delayed data signal based on the strobe signal." (EX1003, ¶¶127-28; EX1004, 4:12-26). As shown

in Figure 10, the latch 59a receives two critical inputs: (1) the "first delayed data signal" from ring delay 57a, and (2) the "strobe signal" DCLK.

Johnson states that "DCLK passes through gated buffer 53, delay circuit 55 and is used to control latch 59 to latch in incoming data on the data bus DQ." (EX1003, ¶¶127-28; EX1004, 4:12-26). That is, the DCLK strobe signal directly controls the sampling operation of latch 59a. The use of the word "control" indicates that the latch's operation is fundamentally dependent on and driven by the DCLK signal. (EX1003, ¶¶127-28). Even if Johnson did not disclose this feature, Moss does. (EX1003, ¶¶127-28). Moss's memory controller interfaces with DDR SDRAM components via a data bus DQ comprising multiple data pins, receiving and processing multiple data signals. (EX1003, ¶¶127-28; EX1006, 1:9-14, 6:16-6:36, Fig. 3). The controller employs delay elements, such as delay line 330, to delay these received data signals, effectively generating delayed versions. (EX1006, 6:16-6:36).

A POSITA would have been motivated to combine Johnson's multiple data pins with adjustable delays and Moss's multi-pin data bus with delay elements, as both address timing control for multiple data signals in memory systems because it would enhance memory controller performance by improving timing control and signal integrity for multiple data signals. (EX1003, ¶130).

### f. Element 1[e]: "a second sampling circuit to sample the second delayed data signal based on the received strobe signal."

Johnson discloses this limitation. (EX1003, ¶¶131). As described above, Johnson discloses a "first sampling circuit" with respect to the data path originating from DQ0, through ring delay 57a and latch 59a. (*See* supra, § X.A.d). Similarly, Johnson discloses a "second sampling circuit to sample the second delayed data signal based on the strobe signal" with respect to the data path originating from DQ1, through ring delay 57b and latch 59b. (EX1003, ¶ 131).

(EX1004, Fig. 10 (annotated excerpt). Moss also discloses this feature. While Moss shows only one data signal path with register flip-flop 322 in Figure 3, a POSITA would have understood that memory interfaces have multiple data pins for data transfer. (EX1004, ¶132; EX1006, 1:25-31, 5:25-6:25). A POSITA would have been motivated to combine the teachings of Johnson and Moss to arrive at the claimed second sampling circuit because references address timing control in multi-pin memory systems, and the combination would yield predictable results in enhancing memory controller performance. (EX1003, ¶133).

B. Claim 2: "The IC memory controller according to claim 1, further comprising storage to store each of first and second delay values corresponding to the delays imparted to the first and second data signals."

Johnson discloses this claim. (EX1003, ¶134). In particular, it describes that control logic can step the ring delays 57a-b through possible delay values, and select a best delay value which is provided to ring delays 57a-b. (EX1003, ¶134; EX1004, 7:25-60). As Johnson describes, "the delay settings of the ring delays 57a, 57b, 57c may be set by logic 87 using signals C10, C11, C12, respectively." (EX1003, ¶134; EX1004, at 7:25-60).

(EX1004, Fig. 10 (annotated excerpt)). A POSITA would have understood that these delay values are necessarily stored in the control logic 21 for application to ring

delays 57, and thus Johnson inherently discloses this feature. (EX1003, ¶134; EX1004, Fig. 10)

Even if Johnson did not disclose this feature, Moss does. (EX1003, ¶135). Moss discloses a memory controller with delay lines that use predetermined, stored delay values to delay the data strobe signal for proper data sampling. (EX1003, ¶135; EX1006, Fig. 3, 6:16-26, 6:55-63).

A POSITA would have been motivated to combine Johnson's storage of delay values for multiple data paths with Moss's use of predetermined stored delays, as both address timing control in memory systems. (EX1003, ¶136).

#### C. Claim 4: "The IC memory controller according to claim 1, wherein the first and second data signals are delayed to compensate for timing offset between the received first and second data signals."

Johnson discloses this claim. (EX1003, ¶137). Specifically, Johnson is directed to a calibration system and method of calibrating data paths "to produce serial and parallel bit alignment on all data paths." (EX1003, ¶137; EX1004, at Abstract). The purpose of Johnson is to ensure that any delays between the data signals in various paths (including a first and second data signals) are aligned, thereby compensating for any time offsets. (EX1003, ¶137; EX1004, at 2:24-42).

Even if Johnson did not disclose this feature, Moss does. Moss's memory controller uses delay elements to align received data signals with a strobe signal, skewing the data strobe signal DQS to capture data at the center of DQS transitions. (EX1003, ¶138; EX1006, 3:9-15, Fig. 3, 6:24-27).

A POSITA would have been motivated to combine Johnson's use of delays for compensating timing differences across multiple data paths with Moss's technique of skewing the data strobe signal relative to the data signal, as both address timing control in memory systems. (EX1003, ¶139).

# D. Claim 5: "The IC memory controller according to claim 4, further comprising: a first timing signal delay element associated with the first pin; and a second timing signal delay element associated with the second pin; wherein each of the first and second timing signal delay elements impart first and second delays to the strobe signal."