### UNITED STATES PATENT AND TRADEMARK OFFICE

#### BEFORE THE PATENT TRIAL AND APPEAL BOARD

## ZF FRIEDRICHSHAFEN AG, ZF ACTIVE SAFETY AND ELECTRONICS US LLC, AND NISSAN MOTOR COMPANY, LTD., Petitioners

v.

FORAS TECHNOLOGIES LTD., Patent Owner

Patent No. 7,502,958 Filing Date: October 25, 2004 Issue Date: March 10, 2009 Title: SYSTEM AND METHOD FOR PROVIDING FIRMWARE RECOVERABLE LOCKSTEP PROTECTION

Inter Partes Review No.: IPR2024-00969

PETITION FOR *INTER PARTES* REVIEW UNDER 35 U.S.C. §§ 311-319 AND 37 C.F.R. § 42.100 *et seq.*

## **TABLE OF CONTENTS**

| EXH  | IBITSv                                                                                                                    |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| MAN  | NDATORY NOTICES viii                                                                                                      |  |  |

| I.   | INTRODUCTION AND RELIEF REQUESTED1                                                                                        |  |  |

| II.  | OVERVIEW1                                                                                                                 |  |  |

|      | A. Technical Background1                                                                                                  |  |  |

|      | 1. Lockstep/FRC Processors Were Known1                                                                                    |  |  |

|      | 2. Determining Whether Lockstep Is Recoverable Was Known4                                                                 |  |  |

|      | 3. Handling Recoverable or Non-Recoverable Errors Differently Was<br>Known                                                |  |  |

|      | 4. Using Firmware to Detect and Handle Processor Errors Was Known7                                                        |  |  |

|      | 5. Designating Spare Processors to Boot the System in the Event the<br>Current Boot Processor Suffers a Problem Was Known |  |  |

|      | B. Brief Description of the Alleged Invention9                                                                            |  |  |

|      | C. The Scope and Content of the Prior Art11                                                                               |  |  |

|      | 1. Bigbee (Ex. 1005)11                                                                                                    |  |  |

|      | 2. Nguyen (Ex. 1006)13                                                                                                    |  |  |

|      | 3. Suffin (Ex. 1020)16                                                                                                    |  |  |

|      | 4. Goodrum (Ex. 1021)                                                                                                     |  |  |

|      | 5. Safford (Ex. 1007)19                                                                                                   |  |  |

| III. | IDENTIFICATION OF CHALLENGE PURSUANT TO 37 C.F.R.<br>§ 42.104(b) AND STATEMENT OF THE RELIEF REQUESTED20                  |  |  |

|      | A. Level of Ordinary Skill in the Art21                                                                                   |  |  |

|      | B. How the Challenged Claims Are to Be Construed22                                                                        |  |  |

|      | 1. "Detection of Loss of Lockstep" and "Detecting Loss of Lockstep".22                                                    |  |  |

|      | 2. "Lockstep Is Recoverable" and "Loss of Lockstep Is Recoverable"23                                                      |  |  |

|      | <ol> <li>Optional Conditional Limitations in Method Claims Are Not Limiting 24</li> </ol>                                 |  |  |

| IV.  | GROUND A: CLAIMS 9-12 ARE OBVIOUS OVER BIGBEE-<br>NGUYEN-GOODRUM                                                          |  |  |

| A. Overview of the Bigbee-Nguyen Combination that Teaches Claim 124                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B. A POSITA Would Have Found It Obvious to Combine Bigbee and<br>Nguyen                                                                                                                                                                                                                                                                                |

| 1. A POSITA would have been motivated to implement Nguyen's determining whether lockstep is recoverable from the detected error in Bigbee                                                                                                                                                                                                              |

| 2. Reasonable Expectation of Success                                                                                                                                                                                                                                                                                                                   |

| C. Independent Claim 132                                                                                                                                                                                                                                                                                                                               |

| <ol> <li>Limitation [1A]: A method comprising: detecting loss of lockstep for a<br/>lockstep pair of processors</li></ol>                                                                                                                                                                                                                              |

| <ol> <li>Limitation [1B]: using firmware to trigger an operating system to idle<br/>the lockstep pair of processors, recover lockstep for the lockstep pair of<br/>processors, and trigger the operating system to recognize the lockstep<br/>pair of processors having recovered lockstep</li></ol>                                                   |

| 3. Limitation [1C]: responsive to said detecting loss of lockstep, using said firmware to determine if lockstep is recoverable for the lockstep pair of processors, wherein said using said firmware to determine if lockstep is recoverable further comprises determining if a lockstep mismatch has occurred between the lockstep pair of processors |

| D. Overview of Bigbee-Nguyen-Goodrum Combination                                                                                                                                                                                                                                                                                                       |

| E. Claim 9: The method of claim 1 further comprising: determining if said<br>lockstep pair of processors for which said loss of lockstep is detected<br>comprises a system boot processor                                                                                                                                                              |

| F. Claim 10: The method of claim 9 wherein if determined that said<br>lockstep pair of processors for which said loss of lockstep is detected<br>comprises a system boot processor, further comprising: swapping the<br>role of system boot processor to another processor in the system                                                               |

| G. Claim 11: The method of claim 10 further comprising: after said swapping, recovering the lockstep for the lockstep pair of processors46                                                                                                                                                                                                             |

| H. Claim 12: The method of claim 11 further comprising: after recovering<br>lockstep for the lockstep pair of processors, holding the recovered pair<br>of processors in idle as a spare for the processor to which the role of<br>system boot processor was swapped                                                                                   |

| GROUND B: CLAIMS 9-12 ARE OBVIOUS OVER BIGBEE-                                                                                                                                                                                                                                                                                                         |

| NGUYEN-SUFFIN48                                                                                                                                                                                                                                                                                                                                        |

V.

|     | A. Overview of Bigbee-Nguyen-Suffin Combination                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|     | B. Claim 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                |

|     | C. Claim 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53                                |

|     | D. Claim 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54                                |

|     | E. Claim 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55                                |

| VI. | GROUND C: CLAIMS 23-25 AND 12 ARE OBVIOUS OVER<br>BIGBEE-NGUYEN-SUFFIN-SAFFORD                                                                                                                                                                                                                                                                                                                                                                                                     | 56                                |

|     | A. Overview of Bigbee-Nguyen-Suffin-Safford Combination                                                                                                                                                                                                                                                                                                                                                                                                                            | 56                                |

|     | B. Independent Claim 23                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58                                |

|     | 1. Limitation [23A]: A method comprising: establishing, in a mult processor system, a hot spare processor for a system boot processor                                                                                                                                                                                                                                                                                                                                              |                                   |

|     | 2. Limitation [23B]: detecting loss of lockstep for a lockstep pair processors in said multi-processor system                                                                                                                                                                                                                                                                                                                                                                      |                                   |

|     | 3. Limitation [23C]: determining if said lockstep pair of processors which the loss of lockstep is detected is the system boot processor                                                                                                                                                                                                                                                                                                                                           |                                   |

|     | 4. Limitation [23D]: if determined that said lockstep pair of processors which the loss of lockstep is the system boot processor, copying a star of the system boot processor to the hot spare processor                                                                                                                                                                                                                                                                           | ate                               |

|     | 5. Limitation [23E]: if determined that said lockstep pair of processors which the loss of lockstep is not the system boot processor, the triggering an operating system to a) idle the lockstep pair of processor b) attempt to recover lockstep between the lockstep pair of processor and c) if lockstep is successfully recovered between the lockstep p of processors, trigger said operating system to recognize the processor as being available for receiving instructions | ien<br>ors,<br>ors,<br>air<br>ors |

|     | C. Claim 24: The method of claim 23 wherein if determined that said<br>lockstep pair of processors for which the loss of lockstep is the system<br>boot processor further comprising: attempting to recover lockstep<br>between the lockstep pair of processors after copying the state of the<br>system boot processor to the hot spare processor                                                                                                                                 | 62                                |

|     | D. Claim 25: The method of claim 24 wherein if determined that said<br>lockstep pair of processors for which the loss of lockstep is the system<br>boot processor further comprising: if lockstep is successfully<br>recovered between the lockstep pair of processors, establishing the                                                                                                                                                                                           |                                   |

| CLA   | IM LISTING APPENDIX                                                                   | 80 |

|-------|---------------------------------------------------------------------------------------|----|

| XI.   | CONCLUSION                                                                            | 77 |

| X.    | GROUNDS FOR STANDING & FEE PAYMENT                                                    | 77 |

|       | B. Unified Patent's <i>Ex Parte</i> Reexamination Is Not Cumulative of this Petition  |    |

|       | A. The Present Grounds Were Not Considered During Prosecution                         | 74 |

| IX.   | 325(D) DISCRETION DOES NOT APPLY                                                      | 74 |

|       | B. General Plastic Discretionary Denial Is Unwarranted                                |    |

|       | A. Fintiv Discretionary Denial Is Unwarranted                                         | 71 |

| VIII. | 314(A) DISCRETION DOES NOT APPLY                                                      | 71 |

|       | D. Claim 12                                                                           | 70 |

|       | C. Claim 25                                                                           | 69 |

|       | B. Claim 24                                                                           | 68 |

|       | 5. Limitation [23E]                                                                   | 67 |

|       | 4. Limitation [23D]                                                                   | 67 |

|       | 3. Limitation [23C]                                                                   |    |

|       | 2. Limitation [23B]                                                                   | 66 |

|       | 1. Limitation [23A]                                                                   |    |

|       | A. Independent Claim 23                                                               | 66 |

| VII.  | GROUND D: CLAIMS 23-25 AND 12 ARE OBVIOUS OVER<br>BIGBEE-NGUYEN-GOODRUM-SAFFORD       | 65 |

|       | E. Claim 12                                                                           | 65 |

|       | lockstep pair of processors for which lockstep was recovered as a hot spare processor |    |

## **EXHIBITS**

| Ex. 1001: | U.S. Patent No. 7,502,958 to Michaelis et al. ("the '958 Patent")                                                                              |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1002: | Declaration of Dr. Jacob Baker                                                                                                                 |

| Ex. 1003: | Curriculum Vitae of Dr. Jacob Baker                                                                                                            |

| Ex. 1004: | Prosecution History of the '958 Patent                                                                                                         |

| Ex. 1005: | U.S. Patent Application Publication No. US 2003/0126498A1 to<br>Bigbee et al., filed January 2, 2002, published July 3, 2003<br>("Bigbee")     |

| Ex. 1006: | U.S. Patent Application Publication No. US 2004/0123201 Al to<br>Nguyen et al., filed December 19, 2002, published June 24, 2004<br>("Nguyen") |

| Ex. 1007: | U.S. Patent Application Publication No. US 2004/0006722 Al to Safford, filed July 3, 2002, published Jan. 8, 2004 ("Safford")                  |

| Ex. 1008: | U.S. Patent No. 7,085,959 B2 to Safford, filed July 3, 2002, published August 1, 2006 ("Safford-959")                                          |

| Ex. 1009: | U.S. Patent No. 7,296,181 B2 to Safford, filed April 6, 2004, published November 13, 2007 ("Safford-181")                                      |

| Ex. 1010: | U.S. Patent Application Publication No. US 2002/0144177 Al to Kondo et al., filed January 31, 2002, published October 3, 2002 ("Kondo")        |

| Ex. 1011: | U.S. Patent No. 6,516,429 B1 to Bossen et al., filed November 4, 1999, published February 4, 2003 ("Bossen")                                   |

| Ex. 1012: | U.S. Patent No. 6,158,015 to Klein, filed March 30, 1998, published December 5, 2000 ("Klein")                                                 |

| Ex. 1013: | U.S. Patent Application Publication No. US 2005/017216 A1 to Fox et al., filed January 21, 2004, published August 4, 2005 ("Fox")              |

| Ex. 1014: | U.S. Patent No. 7,404,105 B2 to Arai, filed August 16, 2004, published July 22, 2008 ("Arai")                                                  |

| Ex. 1015: | U.S. Patent No. 6,675,324 B2 to Marisetty et al., filed September 27, 1999, published January 6, 2004 ("Marisetty")                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1016: | U.S. Patent Application Publication No. US 2003/0074601 A1 to<br>Schultz et al., filed September 28, 2001, published April 17, 2003<br>("Schultz")                        |

| Ex. 1017: | U.S. Patent Application Publication No. 2003/0126142 A1 to Tu et al., filed December 31, 2001, published July 3, 2003 ("Tu")                                              |

| Ex. 1018: | U.S. Patent No. 5,915,082 to Marshall et al., filed June 7, 1996, published June 22, 1999 ("Marshall")                                                                    |

| Ex. 1019: | Reserved                                                                                                                                                                  |

| Ex. 1020: | PCT Patent Application WO 01/80007 A2 to Suffin, filed April 12, 2001, published Oct. 25, 2001 ("Suffin")                                                                 |

| Ex. 1021: | U.S. Patent No. 5,627,962 to Goodrum et al., filed Dec. 30, 1994, published May 6, 1997 ("Goodrum")                                                                       |

| Ex. 1022: | Advanced Configuration and Power Interface Specification,<br>Revision 2.0, July 27, 2000 ("ACPI 2.0")                                                                     |

| Ex. 1023: | Reserved                                                                                                                                                                  |

| Ex. 1024: | Reserved                                                                                                                                                                  |

| Ex. 1025: | Prosecution History of U.S. Patent No. 7,356,733                                                                                                                          |

| Ex. 1026: | Request for Ex Parte Reexamination of the '958 Patent, Control No. 90/019,245 (Sept. 1, 2023)                                                                             |

| Ex. 1027: | Order granting stay in Foras Technologies Ltd. v. Nissan Motor<br>Company, Ltd. and ZF Friedrichshafen AG, Case No. 1-23-cv-<br>00640 (W.D. Tex)                          |

| Ex. 1028: | Infringement contention cover pleading for ZF in Foras<br>Technologies Ltd. v. Nissan Motor Company, Ltd. and ZF<br>Friedrichshafen AG, Case No. 1-23-cv-00640 (W.D. Tex) |

| Ex. 1029: | Infringement contention cover pleading for Nissan in Foras<br>Technologies Ltd. v. Nissan Motor Company, Ltd. and ZF<br>Friedrichshafen AG, Case No. 1-23-cv-00640 (W.D. Tex) |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. 1030: | U.S. Patent No. 5,790,850 to Natu, filed September 30, 1996, published August 4, 1998 ("Natu")                                                                                |

## **MANDATORY NOTICES**

## **Real Parties in Interest**

The real parties-in-interest for this petition are ZF Friedrichshafen AG, ZF North America, Inc., ZF Active Safety and Electronics US LLC, Nissan North America, Inc., and Nissan Motor Company, Ltd.

No unnamed entity is funding, controlling, or directing this Petition for *inter partes* review of the '958 Patent, or otherwise has an opportunity to control or direct this Petition or Petitioners' participation in any resulting IPR.

## **Related Matters**

To Petitioners' knowledge, the '958 Patent is involved in the following:

| Name                                                                | Number        | Court    | Filed         |

|---------------------------------------------------------------------|---------------|----------|---------------|

| ZF Friedrichshafen AG et al.<br>v. Foras Technologies Ltd.          | IPR2024-00727 | USPTO    | Apr. 19, 2024 |

| HL Klemove Corporation v.<br>Foras Technologies Ltd.                | IPR2024-00813 | USPTO    | Apr. 19, 2024 |

| Valeo SE et al. v. Foras<br>Technologies Ltd.                       | IPR2024-00823 | USPTO    | Apr. 18, 2024 |

| Bayerische Motoren Werke<br>AG et al. v. Foras<br>Technologies Ltd. | 1-24-cv-00363 | E.D. Va. | Mar. 6, 2024  |

| BMW of North America, LLC<br>et al. v. Foras Technologies<br>Ltd.   | IPR2023-01373 | USPTO    | Sept. 8, 2023 |

| Name                                                                                     | Number                    | Court     | Filed         |

|------------------------------------------------------------------------------------------|---------------------------|-----------|---------------|

| Foras Technologies Limited v.<br>Volkswagen AG et al.                                    | 2-23-cv-00314             | E.D. Tex. | Jun. 28, 2023 |

| Foras Technologies Limited v.<br>Nissan Motor Company, Ltd.<br>and ZF Friedrichshafen AG | 1-23-cv-00640             | W.D. Tex. | Jun. 6, 2023  |

| Foras Technologies Ltd. v.<br>Bayerische Motoren Werke AG et<br>al.                      | 6-23-cv-00386             | W.D. Tex. | May 19, 2023  |

| <i>Ex Parte Reexamination</i> filed by Unified Patents                                   | Control No.<br>90/019,245 | USPTO     | Sept. 1, 2023 |

This petition is the first *inter partes* review petition to challenge claims 9-12 and 23-25 of the '958 Patent. In IPR2023-01373, unrelated third parties BMW and Bosch challenged claims 1-8 and 13-22 of the '958 Patent. That petition was instituted on March 20, 2024, and Petitioners herein (ZF Friedrichshafen AG, ZF Active Safety and Electronics US LLC, and Nissan Motor Company, Ltd.) filed a copycat petition as IPR2024-00727 and moved to join IPR2023-01373 within the one-month window for doing so. Claims 9-12 depend from claim 1, and this Petition relies on the same prior art (Bigbee-Nguyen) as was used against claim 1 in IPR2023-01373, but uses additional art, such as Goodrum and Suffin, for additional claim elements found in claims 9-12, and for certain claim elements found in claims 23-25.

## Lead & Back-Up Counsel

Petitioner designates counsel listed below and consents to electronic service.

A power of attorney for counsel is being filed with this Petition.

| Lead Counsel                                                                       | Back-Up Counsel                                                                                                                   |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| John R. Hutchins (Reg. No. 43,686)<br>jhutchins@bannerwitcoff.com                  | Paul T. Qualey (Reg. No. 45,027)<br>pqualey@bannerwitcoff.com                                                                     |

| BANNER & WITCOFF, LTD.<br>1100 13th Street, NW, Suite 1200<br>Washington, DC 20005 | Wesley W. Jones (Reg. No. 56,552)<br>wjones@bannerwitcoff.com                                                                     |

| Tel: (202) 824-3000<br>Fax: (202) 824-3001                                         | BANNER & WITCOFF, LTD.<br>1100 13th Street, NW, Suite 1200<br>Washington, DC 20005<br>Tel: (202) 824-3000<br>Earry (202) 824 2001 |

|                                                                                    | Fax: (202) 824-3001<br>Binal J. Patel (Reg. No. 42,065)<br>bpatel@bannerwitcoff.com                                               |

|                                                                                    | BANNER & WITCOFF, LTD.<br>71 South Wacker Drive, Suite 3600<br>Chicago, IL 60606<br>Tel: (312) 463-5000<br>Fax: (312) 463-5001    |

## **Service Information**

Please address all correspondence to counsel at the addresses shown above. Petitioner further consents to electronic service by email at the following address if sent to each of the emails indicated above, as well to: ZFIPRService@bannerwitcoff.com.

#### I. INTRODUCTION AND RELIEF REQUESTED

ZF Friedrichshafen AG, ZF Active Safety and Electronics US LLC, and Nissan Motor Company, Ltd. ("Petitioners") hereby petition for *inter partes* review under 35 U.S.C. §§ 311-319 and 37 C.F.R. § 42.100 *et seq.* and cancellation of claims 9-12 and 23-25 of U.S. Patent No. 7,502,958 ("the '958 Patent"). This petition is supported by the Declaration of Dr. Jacob Baker, Exhibit 1002.

Claims 9-12 and 23-25 of the '958 Patent are directed to obvious combinations of simple concepts, long known in the art: detecting and correcting loss of lockstep in processors, and identifying and using a spare processor to boot the system in the event a problem (such as loss of lockstep) occurs with respect to the boot processor. More particularly, references such as Bigbee, Nguyen, and Safford teach how to detect and correct a loss of lockstep, as claimed in the '958 Patent. References such as Goodrum and Suffin teach that problems with a boot processor can be ameliorated by designating a spare processor to be the boot processor. In combination they render claims 9-12 and 23-25 obvious.

#### **II. OVERVIEW**

#### A. Technical Background

#### 1. Lockstep/FRC Processors Were Known

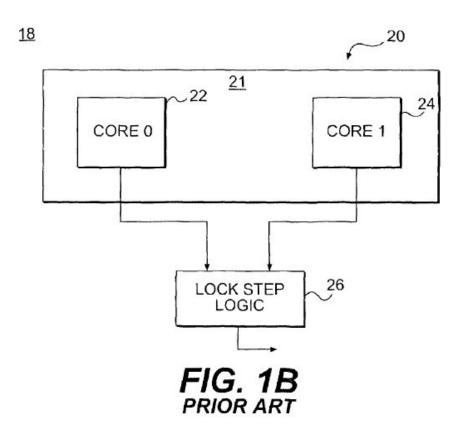

Before the '958 Patent, it was typical to improve the fault tolerance of a computer system using lockstep processing. For example, two processors 22 and 24 (or two processor units or two processor cores) are paired together to execute the

same instructions on identical data in parallel and their outputs are compared by, e.g., lockstep logic 26. Safford, [0003]; *see also* Bigbee, [0033]; Nguyen, [0006]; Kondo, [0004]; Ex. 1001, 2:13-19. A discrepancy between the outputs is a loss of lockstep. Safford, [0004]; Ex. 1002, ¶58.

Safford, Fig. 1B.

Lockstep processors are also said to operate in "functional redundancy check" (FRC) mode, because they execute redundant instructions in parallel. Safford-181, 1:67-2:3; Ex. 1002, ¶59.

If the same outputs are produced, no error is detected. If the comparison indicates a mismatch, it is assumed that at least one processor has an error, such as a data cache error or a soft error.<sup>1</sup> Safford, [0003], [0016]; Nguyen, [0008]. A loss of lockstep, if not promptly corrected, may cause the computer system to crash. That is, a failure of one of the pair of processors may halt the entire computer system, even if the other processor does not encounter an error. Safford [0003]; Ex. 1002, ¶60.

It was known that an error detected in an individual processor of a pair of lockstep processors signals an impending mismatch error. Safford, [0015]-[0017] (error detected in an single processor core of a lockstep processor signals an *impending* loss of lockstep); Kondo, [0101] (detecting an error in the processor provides *early warning* of a divergence), [0103], [0106]; Nguyen, [0008] (soft errors in FRC-enabled processors are likely to be manifested as FRC errors since they take the execution cores out of lockstep), [0022]; Ex. 1002, ¶¶61-62.

<sup>1</sup> A "soft error" results when, for example, a high-energy particle switches the state of a memory element causing a parity or other error. Nguyen, [0004]; Kondo, [0006]. Soft errors are generally correctable by rewriting the affected memory location. Socalled "hard" errors, in contrast, indicate failure of a hardware element.

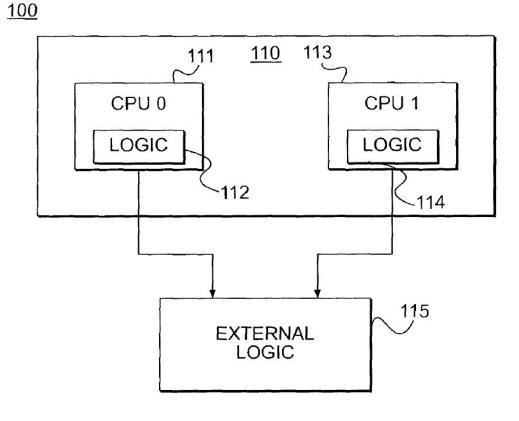

#### 2. Determining Whether Lockstep Is Recoverable Was Known

It was known that lockstep is recoverable from certain errors, such as soft errors, but not others, such as some lockstep mismatch errors. For example, lockstep is recoverable from an error detected in an individual processor before a mismatch error is detected and signaled. As shown below, a pair of lockstep processors 111 and 113 can include error detection and signaling logic 112 and 114, respectively, to signal an impending loss of lockstep. Safford, [0017]; Ex. 1002, ¶¶63-64.

FIG. 2

Safford, Fig. 2.

It was known that detecting and handling such errors before signaling a mismatch error improves processor or system availability. Safford, [0017]; Nguyen, [0046] (detecting an error in the processor core before triggering an FRC reset allows recovery from the error); Kondo, [0100]; Ex. 1002, ¶65.

It was also known that lockstep is non-recoverable from a mismatch error in various situations, for example, a hard error that caused the mismatch (e.g., hardware failure). Bigbee, [0033]; Bossen, 1:35-40 (no recovery is possible for hard errors). Also, lockstep is not recoverable if the processor or FRC logic does not know which processor core was responsible for the mismatch error. Nguyen, [0023]; Safford-181, 6:53-56. As another example, lockstep is not recoverable if the mismatch error is triggered before detection of the error in the individual processor. Nguyen, [0022] (triggering a non-recoverable FRC error before the underlying parity error in the processors is detected). And lockstep is not recoverable if the mismatch error is detected in the absence of detecting an error in the individual processor. Marshall, 2:17-34. Such mismatch error typically would indicate a high risk of corrupt data or incorrect results about to propagate through the system. Kondo, [0089], [0102]; Ex. 1002, ¶¶66-67.

#### 3. Handling Recoverable or Non-Recoverable Errors Differently Was Known

It was known that once an error was detected in FRC processors, the appropriate responsive action depends on whether the error was non-recoverable or recoverable, in order to reduce the impact of errors on the system. Ex. 1002, ¶68.

When a non-recoverable error occurs, there is risk of corrupt data or results propagating through the system. An appropriate responsive action would have been immediately resetting or rebooting the system to return the system to a safe state or shut down the processor. Nguyen, [0007] (FRC errors are detectable but not recoverable; the FRC error handling routine typically resets the system, which is time consuming and reduces system availability); Marshall, 2:3-6 (the only recovery action responsive to an output mismatch is to reset the system); Kondo, [0039], [0190]; Schultz, [0030]; Marisetty, 5:21-28; Ex. 1002, ¶69.

Also, a mismatch error can be non-recoverable because it indicates a non-recoverable hardware failure of the processor (Bigbee, [0033]), for which an appropriate action would have been replacing it with another processor. Klein, 1:19-66 (hot swapping a failed CPU while the system is running); Fox, Abstract, [0005]-[0014]; Arai, 1:39-45, 2:23-41; Ex. 1002, ¶70.

With respect to recoverable errors, in contrast, various recovery routines have been used to reduce the impact of such errors on the system, such as those disclosed in Bigbee, Nguyen, Kondo, and Safford. Kondo, [0191]; Ex. 1002, ¶71. Treating an otherwise recoverable error as non-recoverable would reduce system availability. Recovery of lockstep from a recoverable error can be implemented with a lower latency as compared to the reset or repair/replacement processes for handling a non-recoverable error. Nguyen, [0022]-[0023], [0040]; Ex. 1002, ¶72.

Conversely, treating a non-recoverable error as a recoverable error would reduce system reliability. For example, it would create risks of having corrupt data or results propagating through the system. Kondo, [0101] (the longer time that passes from error or divergence detection without remedial action, the more serious the impact); Marisetty, 2:38-52; Ex. 1002, ¶73.

# 4. Using Firmware to Detect and Handle Processor Errors Was Known

It was known that firmware can be used for detecting lockstep errors. Bigbee, [0034] (FRC logic 308 may be implemented as executable firmware); Safford-181, 15:60-64; Ex. 1002, ¶74.

It was also common to use firmware for handling processor errors. Nguyen, [0045] (using PAL or SAL layers of BIOS—firmware—for implementing error recovery mechanisms); Marisetty, 5:48-8:64, Figs. 1-2; Schultz, [0017]-[0018], Figs. 1-3; Bigbee, [0017]-[0025]; Ex. 1002, ¶75.

### 5. Designating Spare Processors to Boot the System in the Event the Current Boot Processor Suffers a Problem Was Known

It was known to designate a particular processor as the boot processor in a multi-processor system. Natu, 1:5-9, 2:20-36; Goodrum, 2:15-31, 2:40-43, 6:1-3, 6:49-51, 8:60-61; Suffin, 12:3-18, 13:16-20. The designated boot processor is responsible for turning on and testing the other processors or otherwise initializing the system. Goodrum, 2:15-31; Natu, 2:20-36. If a designated boot processor does not function properly, then the overall system may become incapacitated. Goodrum, 2:15-31; Natu, 2:20-50; Ex. 1002, ¶76.

It was therefore known to designate a backup processor to take over boot processor functions should the designated boot processor fail in order to improve the reliability of the multi-processor system. Goodrum, 1:17-20, 2:15-31, 3:7-31, 8:60-64, 9:39-50; Suffin, 2:18-3:11, 13:20-14:2, Fig. 4A; Natu, 1:5-9, 2:20-50, 2:57-3:13. It also beneficially enables the system to diagnose errors with the failed boot processor. Absent a backup boot processor, a reset of the system is typically necessary, which clears the operational status of the system, including operational status information associated with the failed boot processor, hindering diagnosis. Suffin, 1:1-5, 1:12-3:3, 16:9-17:11; Ex. 1002,  $\P77$ .

Use of a backup boot processor also enables an operational state of a functional processor to be copied over to the failed boot processor for recovery. Suffin, 1:1-5, 1:12-3:3, 16:9-17:11. It likewise was known that the operational state

of a failed processor may be copied over to a backup processor to facilitate recovery. Safford, [0006], [0018], [0021], Fig. 4; Ex. 1002, ¶78.

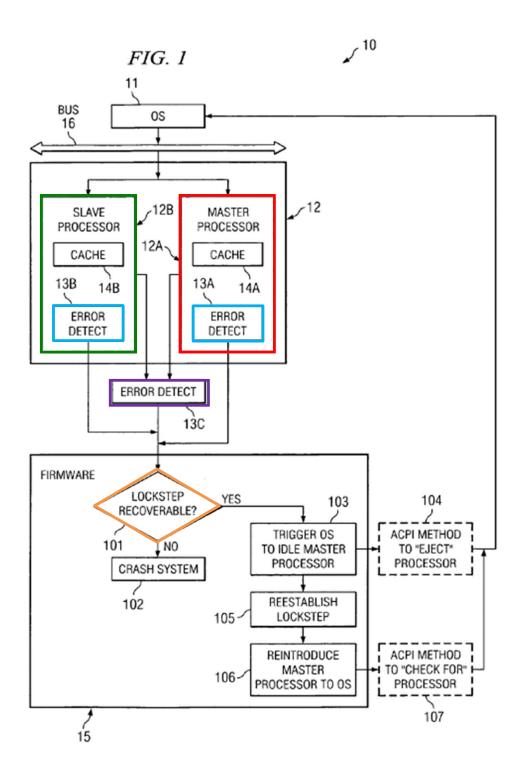

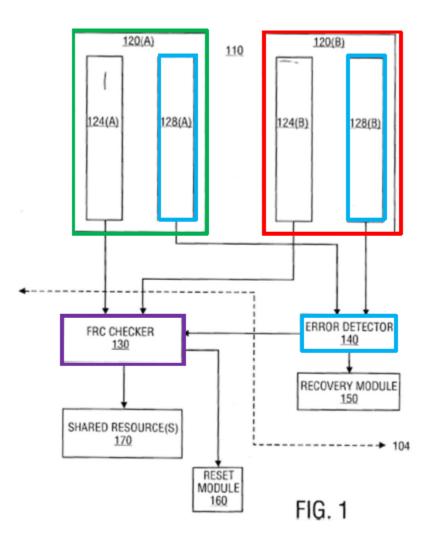

#### **B.** Brief Description of the Alleged Invention

The '958 Patent claims priority to October 25, 2004. Ex. 1001, p. 1. It discloses a system and method for detecting loss of lockstep (LOL) between pairs of processors and LOL recovery. Ex. 1001, 3:51-59, Figs. 1-6. The system includes a lockstep processor pair, including a master processor and a slave processor, each with error detect logic to detect errors present in the respective processor. Id., 4:14-46, Fig. 1 (reproduced below). The system also includes error detect logic to detect a lockstep mismatch between the master and slave processors. Id., 4:46-55. The specification describes detecting LOL as including at least one of (1) detecting mismatch of the output of the paired processors ("lockstep mismatch error"); and (2) detecting an error in either of the processors that may eventually propagate to a lockstep mismatch error. Id., 2:26-59, 4:36-67. The specification also refers to detecting an error in either of the processors before detecting a lockstep mismatch as a detection of a "precursor to lockstep mismatch." Id., 4:60-67; Ex. 1002, ¶79.

Ex. 1001, Fig. 1 (annotated).

Once the system detects LOL, it uses firmware to determine whether

lockstep is recoverable (or whether the detected LOL is a recoverable LOL); if recoverable, the system's firmware cooperates with the operating system ("OS") via standard OS methods to recover the lockstep. *Id.*, 5:49-6:1, Fig. 1 (step 101). If the OS is Advanced Configuration and Power Interface (ACPI) compatible, its firmware uses ACPI methods to cooperate with the OS to idle the processors, recover lockstep of the processors, and reintroduce the processors to the OS. *Id.*, 6:9-7:21, Fig. 1 (steps 103-107); Ex. 1002, ¶80.

In the event the loss of lockstep is in the boot processor, the system will transfer the role of boot processor to a "hot spare" processor. Ex. 1001, 9:15-29, 10:7-12, 10:26-31, Fig. 3. Loss of lockstep is then recovered in the processor that was the boot processor, and that processor becomes the new hot spare processor. *Id.*; Ex. 1002, ¶80.

## C. The Scope and Content of the Prior Art

#### 1. Bigbee (Ex. 1005)

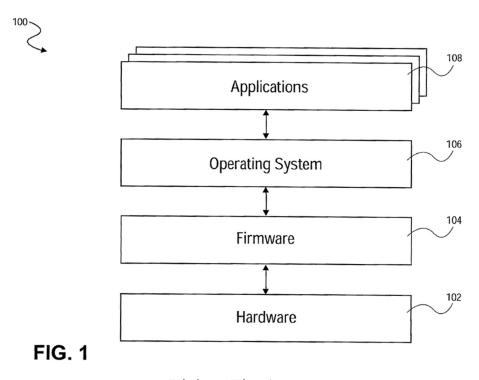

Bigbee discloses a data processing system including hardware 102, firmware 104, and an operating system 106. Bigbee, [0014]-[0025], Fig. 1.

Bigbee, Fig. 1.

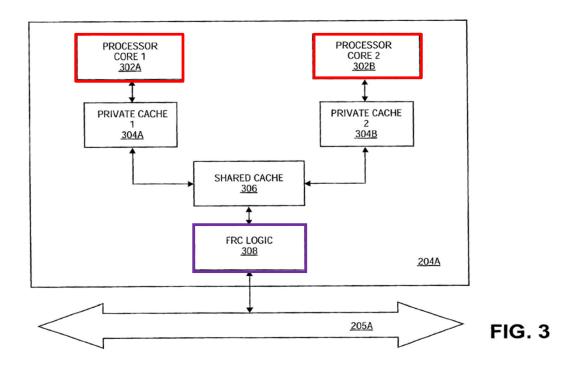

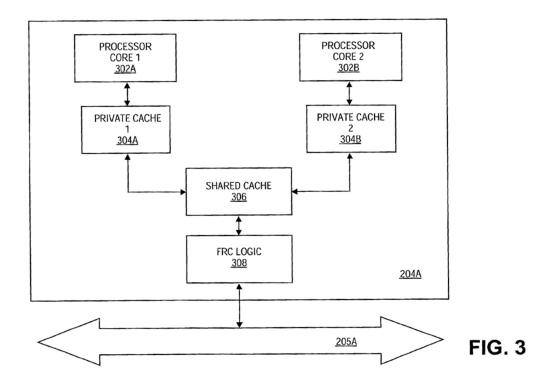

Hardware 102 includes two or more processor packages, each processor package including two processor cores operating in lockstep functional redundancy check (FRC) mode as a single logical processor from the point of view of operating system 106.<sup>2</sup> *Id.*, [0019], [0032]-[0033], Fig. 3 (reproduced below). The two processor cores concurrently execute identical instructions on identical data and each processor generates results. *Id.*, [0002], [0033]. An FRC logic 308 monitors and detects inconsistencies in the results of the two processor cores that indicate an FRC

<sup>&</sup>lt;sup>2</sup> FRC mode is synonymous with operating in lockstep.

mismatch error, which may be the result of an alpha particle impacting on one or both processor cores. *Id.*, [0033].

Bigbee, Fig. 3 (annotated).

The FRC logic also detects an error within each of the processor cores and generates a system machine check to cause the firmware and the operating system to perform an error recovery routine that recovers the FRC operation ("lockstep") of the cores. *Id.*, [0035]-[0037], Figs. 4A-4B; Ex. 1002, ¶¶83-85.

#### 2. Nguyen (Ex. 1006)

Nguyen likewise discloses a processor including two cores 120A and 120B that operate in an FRC mode ("lockstep"), an FRC checker 130 that compares results from the two cores, and an error detector 140 that detects errors in the respective

cores. Nguyen, Abstract, [0006], [0020]-[0022], [0039], [0045], Fig. 1. One of the two cores "may be designated as the master core and the other as the slave core." *Id.*, [0047]; Ex. 1002, ¶¶86-90.

Nguyen, Fig. 1 (annotated).

Nguyen discloses determining if lockstep is recoverable from a detected error that takes the two cores out of lockstep, such as a soft error or a mismatch error, and mechanisms for handling the detected error based on the determination. *Id.*, [0005], [0007]-[0008], [0022]-[0025], [0040]-[0041], [0056]-[0058].

*First*, Nguyen discloses lockstep is not recoverable from an FRC error detected by FRC checker 130. *Id.*, [0007], [0022], [0040]. If FRC checker 130 signals an FRC error after detecting a mismatch error before error detector 140 detects the underlying soft error, this FRC error is non-recoverable mismatch error and a reset module 160 resets the system. *Id.*, [0022].

*Second*, Nguyen discloses lockstep is recoverable from a soft error detected before detecting a mismatch error. *Id.*, [0005], [0022]-[0024], [0046]. If error detector 140 detects a soft error in either processor core (e.g., result from alpha particle collision) before FRC checker 130 detects an FRC error indicating mismatch, error detector 140 disables FRC checker 130 and recovery module 150 implements a recovery routine to restore the cores and FRC mode ("lockstep"). *Id.*

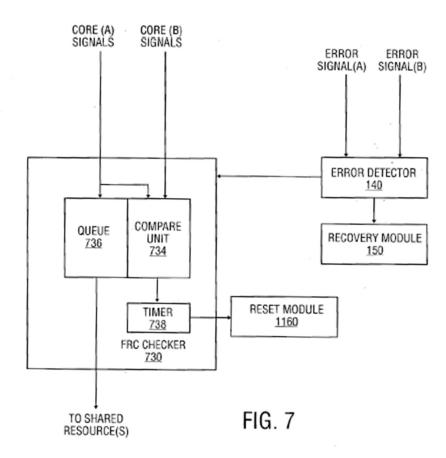

*Third*, Nguyen discloses lockstep is recoverable from a mismatch error detected before an FRC error is triggered. *Id.*, [0056]-[0058]. As shown below, Nguyen's FRC checker includes a compare unit 734 and a timer unit 738. *Id.* Compare unit 734 compares the data from both cores and sets a status flag to indicate if the comparison yields a match. *Id.* If the data does not match, compare unit 734 sets the status flag to indicate the mismatch and triggers timer unit 738 to begin a countdown interval. *Id.* If error detector 140 receives an error flag before the timeout interval expires, it disables FRC checker 730 and triggers recovery module 150. *Id.* But if the timeout interval does expire, the FRC checker signals a non-recoverable

FRC error and triggers reset module 160 to reset the system. *Id.*, [0022], [0056]-[0058].

Nguyen, Fig. 7.

Nguyen's process for determining if lockstep is recoverable from an error in a lockstep processor pair was known in the prior art. *See e.g.*, Tu (Ex. 1017), [0041]-[0043], Fig. 5.

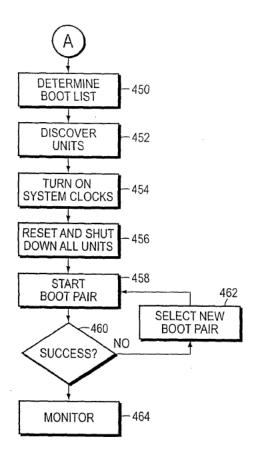

#### 3. Suffin (Ex. 1020)

Suffin, like Bigbee and Nguyen, discloses a computer system having multiple redundant CPUs and associated controllers, operating in lockstep. Suffin, 6:1-7:14,

Fig. 2. When a failure occurs in a processor, such as from a loss of lockstep (*Id.*, 7:12-14), Suffin discusses using an ordered list of processors (a "boot list") to determine which processor to use as a boot processor. *Id.*, 2:5-4:5, 11:3-9, 11:23-12:18, 13:1-7, 13:16-14:10, Fig. 4A. If a boot using a first processor is unsuccessful, the system selects the next processor on the list to be the boot processor. *Id.* When recovering from a system failure, if a processor is suspended or not operating, that processor likewise is skipped on the boot list, so that the next processor on the list is used for rebooting. *Id.*, 16:20-17:11, 13:1-7. Further, the state of the processor that failed may be copied for analysis. *Id.*; Ex. 1002, ¶¶94-96.

The swapping of the role of boot processor from one processor to another is shown, for instance, in Figure 4A, below.

FIG. 4A

Suffin, Fig. 4A.

The system determines the boot list in step 450, then determines which processors on the boot list are available (skipping those that are not) in step 452, then uses the first available processor on the list to boot in step 458, and if that is not successful selects another processor as the boot processor in step 462. *Id.*, 11:23-12:18, 13:1-14:6, 14:15-15:3, 16:9-17:11, claims 21, 30, Fig. 4A.

#### 4. **Goodrum (Ex. 1021)**

Goodrum, like Suffin, discloses a multiple processor system and methods for switching the role of boot processor to another processor in the event of a failure of the boot processor. For example, "a hot spare boot circuit ... automatically reassigns the power up responsibilities to an operational second processor should the primary processor fail." Goodrum, 3:10-13; 8:60-64; 9:39-50; 18:34-49, claims 1, 4, 7, 10, Fig. 2; Ex. 1002, ¶97.

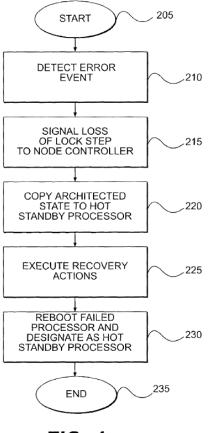

#### 5. Safford (Ex. 1007)

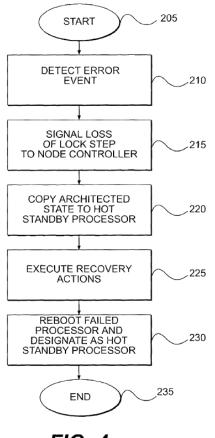

Safford, like Bigbee and Suffin, relates to a multi-processor system with processors operating in lockstep. Safford, Abstract, [0001], [0006]-[0007], [0015]-[0016], [0018]-[0021], claim 1, Figs. 2-4. In order to "enhance recovery from loss of lockstep," Safford copies the state of one or more of the processors in a processor pair for which a loss of lockstep has been detected to a spare processing unit, which becomes an active processor unit in the computer system. *Id.*, [0006]-[0007], [0021]. This process is shown, for instance, in Figure 4, step 220:

FIG. 4

Safford, Fig. 4, [0021].

Once the processor with the loss of lockstep is idled and lockstep is recovered, then

that processor (whose state was copied to the standby processor) becomes the new

hot standby processor, as seen in step 230. Id.; Ex. 1002, ¶¶98-99.

## III. IDENTIFICATION OF CHALLENGE PURSUANT TO 37 C.F.R. § 42.104(B) AND STATEMENT OF THE RELIEF REQUESTED

Petitioner requests *inter partes* review of claims 9-12 and 23-25 on these grounds:

| Ground | Prior Art <sup>3</sup>                                                       | Claims<br>Challenged |

|--------|------------------------------------------------------------------------------|----------------------|

| А      | Obvious under 35 U.S.C. § 103 over<br>Bigbee, Nguyen, and Goodrum            | 9-12                 |

| В      | Obvious under 35 U.S.C. § 103 over<br>Bigbee, Nguyen, and Suffin             | 9-12                 |

| С      | Obvious under 35 U.S.C. § 103 over<br>Bigbee, Nguyen, Suffin and Safford     | 23-25, 12            |

| D      | Obvious under 35 U.S.C. § 103 over<br>Bigbee, Nguyen, Goodrum and<br>Safford | 23-25, 12            |

This petition does not present grounds or substantially the same arguments presented during prosecution.

## A. Level of Ordinary Skill in the Art

A person of ordinary skill in the art ("POSITA") would have at least a bachelor's degree in Computer Science, Computer Engineering, or equivalent, and at least two years of prior work experience with computer architecture design, including fault tolerant computer architecture design, as of the earliest priority date of the '958 Patent—October 25, 2004. Ex. 1002, ¶¶101-104. Additional education could substitute for professional experience and vice versa. *Id.*

<sup>&</sup>lt;sup>3</sup> All references to 35 U.S.C. § 102 and § 103 refer to pre-AIA statutes.

#### **B.** How the Challenged Claims Are to Be Construed

The Board construes claims per *Phillips v. AWH Corp.*, 415 F.3d 1303 (Fed. Cir. 2005) (en banc). Under *Phillips*, claims terms are given their ordinary and customary meaning as understood by a POSITA in the context of the specification. *Id.*, 1312-13.

Aside from the terms addressed below, all terms are given this ordinary and customary meaning. Ex. 1002, ¶¶105-113.

# 1. "Detection of Loss of Lockstep" and "Detecting Loss of Lockstep"

For this IPR, the terms "detection of loss of lockstep" and "detecting loss of lockstep" should be construed to include both mismatch errors and errors that may eventually result in mismatch errors constituting a "precursor to lockstep mismatch"—including at least one of (1) detecting a lockstep mismatch error; and (2) detecting an error that may eventually cause a lockstep mismatch error. Ex. 1001, 4:56-67.

The specification provides detecting these two types of errors as examples of detection of LOL. *See e.g.*, Ex. 1001, 2:26-59, 4:37-67. It states that "[1]ockstep mismatch is one way of detecting a LOL." Ex. 1001, 4:56-57. It also states that "[b]ecause the detection of LOL … may occur before an actual lockstep mismatch occurs, the detection of LOL … may be referred to as a detection of a 'precursor to lockstep mismatch." Ex. 1001, 4:60-64. Both lockstep mismatch and precursors to

lockstep mismatch are detection of loss of lockstep in the specification of the '958 Patent because, as the specification explains, 1) mismatch errors indicate that lockstep is already lost and 2) precursors to lockstep mismatch indicate that the "error may eventually propagate to a lockstep mismatch error." Ex. 1001, 4:56-67.

This is consistent with the dependent claims, which expressly define detecting loss of lockstep as either of the two options. Ex. 1001, claims 1, 4-8. Claim 4, for example, further defines "detecting loss of lockstep" as comprising "detecting corrupt data ... *that would lead to a lockstep mismatch*." Similarly, claim 5 defines "detecting loss of lockstep" as comprising "*detecting a precursor to lockstep mismatch*." Both claims 4 and 5 expressly require that a precursor to lockstep mismatch is included in the definition of "detecting loss of lockstep." Claim 6 further defines "detecting loss of lockstep" as "detecting lockstep mismatch between the lockstep pair of processors," expressly requiring that lockstep mismatch is included.

The term must be interpreted as broad enough to encompass both dependent claim definitions—including at least one of (1) detecting a lockstep mismatch error; and (2) detecting an error that may eventually cause a lockstep mismatch error.

## 2. "Lockstep Is Recoverable" and "Loss of Lockstep Is Recoverable"

The terms "lockstep is recoverable" and "loss of lockstep is recoverable" should be construed as "lockstep is recoverable from the detected loss of lockstep"

"whether the detected LOL is a recoverable LOL." *See e.g.*, Ex. 1001, 5:56-6:1.

# 3. Optional Conditional Limitations in Method Claims Are Not Limiting

Limitations [23D], [23E], and claims 10-12, 24, and 25 are optional conditional limitations that need not be performed in order to perform the claimed method and, thus, are not limiting. *See Ex Parte Schulhauser*, Appeal No. 2013-007847 (P.T.A.B. Apr. 28, 2016), pp. 8-10; *Marvell Semiconductor, Inc. v. Uniloc 2017 LLC*, IPR2019-01350, Paper 24, pp. 36-39 (P.T.A.B. Feb. 1, 2021).

## IV. GROUND A: CLAIMS 9-12 ARE OBVIOUS OVER BIGBEE-NGUYEN-GOODRUM

Claims 9-12 depend from claim 1 (directly or through other claims). As explained below, the elements of claim 1 are taught by the combination of Bigbee-Nguyen. The additional elements of claims 9-12 are taught by Goodrum and/or Bigbee, rendering these claims obvious in light of Bigbee-Nguyen-Goodrum. Below is an overview of the Bigbee-Nguyen combination that teaches the elements of claim 1. Ex. 1002, ¶¶114-115.

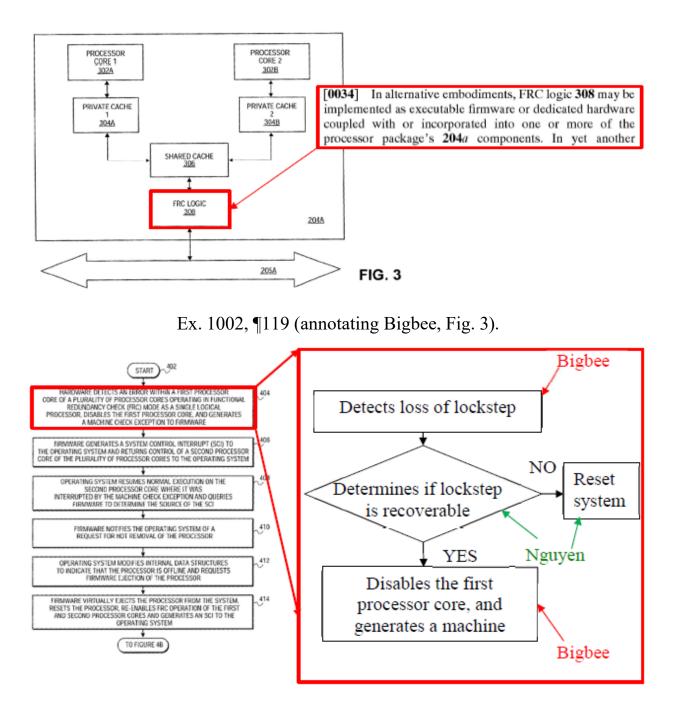

# A. Overview of the Bigbee-Nguyen Combination that Teaches Claim 1

Bigbee discloses all limitations of claim 1 except "determin[ing] if lockstep is recoverable." Nguyen discloses a method of determining if the lockstep of the processor pair is recoverable or non-recoverable. Bigbee's firmware performing Nguyen's determining if the lockstep is recoverable or non-recoverable renders claim 1 obvious. Ex. 1002, ¶¶116-117.

Applying the combination of Bigbee and Nguyen to the core components of claim 1, each limitation is expressly disclosed in the combination Ex. 1002, ¶118:

| Core Claim                                                                                         | Prior Art Reference                                                          |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Requirement                                                                                        |                                                                              |

| 1) Detecting loss of<br>lockstep between a pair of<br>lockstep processors                          | Bigbee                                                                       |

| 2) With firmware,<br>determining if lockstep is<br>recoverable                                     | Bigbee (with firmware)<br>Nguyen (determining if<br>lockstep is recoverable) |

| 3) With firmware,<br>determining if lockstep<br>mismatch has occurred                              | Bigbee                                                                       |

| 4) Triggering an operating<br>system to idle the<br>processors                                     | Bigbee                                                                       |

| 5) Attempting to recover<br>lockstep                                                               | Bigbee                                                                       |

| 6) If recovered, trigger<br>the operating system to<br>recognize the processors<br>to be available | Bigbee                                                                       |

The combined system, when implementing Nguyen's express disclosure of determining whether loss of lockstep is recoverable, in Bigbee's firmware (FRC Logic) responsive to Bigbee's detection of loss of lockstep would be as follows:

Ex. 1002, ¶119 (annotating and modifying Bigbee, Fig. 4A).

### B. A POSITA Would Have Found It Obvious to Combine Bigbee and Nguyen

A POSITA would have found it obvious to implement Nguyen's determination of whether the detected error causing the loss of lockstep is recoverable by Bigbee's firmware FRC logic to create a system that can handle both recoverable and non-recoverable lockstep errors. Ex. 1002, ¶120-126.

# 1. A POSITA would have been motivated to implement Nguyen's determining whether lockstep is recoverable from the detected error in Bigbee

A POSITA would have been motivated to implement Nguyen's determination of whether the detected error causing the loss of lockstep is recoverable by Bigbee's firmware FRC logic to appropriately handle the detected error. Because different responsive actions should be taken to handle each of non-recoverable and recoverable errors, determining whether the error is recoverable or non-recoverable is critical to reduce the impact of errors on the system. See Ex. 1002, ¶¶127, 63-73; Marisetty, 4:43-5:63, 7:24-27 (after detection of an error, the processor determines the severity of the error and takes action depending on the severity); Kondo, [0100] (determining whether an error is a) fatal to the processor or b) a correctable error that will produce a divergence but will not compromise data integrity); Schultz, [0027], [0154] (firmware SAL reports the appropriate error severity as being fatal or recoverable); [0021] (errors detected are classified according to the error type and severity).

Dr. Baker explained (Ex. 1002, ¶¶68-73, 128) that non-recoverable errors cause a risk of data corruption or propagating an incorrect result if the system is not immediately rebooted or reset to return to a safe state. Dr. Baker further explained (Ex. 1002, ¶¶68-73, 129) that recoverable errors can be recovered using known recovery routines that reduce the impact on the system. A POSITA would have understood the importance of handling recoverable errors differently from non-recoverable errors. Ex. 1002, ¶¶128-129.

Handling recoverable errors differently from non-recoverable errors also prevents loss of system availability. Ex. 1002, ¶129 (citing Nguyen, [0007]-[0008], [0022]-[0023], [0040]). Nguyen teaches that treating a recoverable error as a non-recoverable error would reduce system availability, i.e., increase system downtime. Nguyen, [0007]-[0008], [0022]-[0023], [0040]. Recovery of lockstep from a recoverable error can be implemented with lower latency compared to the reset or repair/replacement processes for handling a non-recoverable error. *Id*.

Handling non-recoverable errors differently from recoverable errors also prevents reduction in system reliability. Ex. 1002, ¶130. For example, handling nonrecoverable errors as recoverable creates risks of having corrupt data or incorrect results propagating through the system. *Id.* (citing Kondo, [0101], [0103] (a nonrecoverable error involves the risk of data corruption); Marisetty, 2:38-52; Safford, [0003]. Reducing system availability or reliability by handling errors incorrectly either restarting the entire system when an error can be recovered or attempting to recover a non-recoverable error and causing error propagation—would have been undesirable for fault-tolerant multiprocessor systems, particularly for systems that need to have high reliability and availability, such as server systems (Bigbee, [0030]-[0031]), resources in a network (Kondo, [0191]), electronic fund transfer systems or airline traffic control systems (Klein, 1:19-24). Ex. 1002, ¶131.

Accordingly, a POSITA would have understood that fault tolerant systems would distinguish between recoverable and non-recoverable errors by first determining whether an error is recoverable and then responding accordingly based on that determination. Ex. 1002, ¶132.

A POSITA, who would have had knowledge of handling recoverable and nonrecoverable errors detected in FRC processors, would have been motivated to use Bigbee's FRC logic to determine whether lockstep is recoverable and take the appropriate action responsive to the recoverability of the error, thereby reducing the impact of the error and improving system reliability and availability. Ex. 1002, ¶133.

#### 2. Reasonable Expectation of Success

A POSITA would have understood how to implement Nguyen's determining whether a detected error is recoverable or non-recoverable using Bigbee's firmware FRC logic with a reasonable expectation of success because implementing logical steps in firmware was known in the art. Ex. 1002, ¶134 (citing Bigbee, [0034], Safford-181, 15:60-64 (lockstep logic may be implemented in firmware)).

A POSITA would have expected success in implementing Nguyen's determining step in Bigbee's firmware because Bigbee's system is compliant with well-known industry standards—its operating system is ACPI-compliant, and its firmware includes ACPI BIOS code and a processor abstraction level (PAL) that provides an abstraction of implementation-specific processor features. Ex. 1002, ¶135; Bigbee, [0016]-[0018].

A POSITA would have known how to use ACPI Source Language (ASL) to program Bigbee's firmware code to implement Nguyen's determining step using ordinary computer programming skill because using such firmware, such as the PAL or SAL layer of ACPI BIOS, for implementing error diagnosis and recovery routines was well known, involving only ordinary skill and common knowledge. Ex. 1002, ¶136 (citing Schultz, [0027], [0154] (firmware SAL reports the appropriate error severity as being fatal or recoverable); Nguyen, [0045] (using PAL or SAL layers of BIOS for implementing error recovery mechanisms); Marisetty, 5:48-8:64 (teaching using firmware including PAL and SAL to execute error handling routines), Figs. 1-2; Schultz, Figs. 1-3, [0017]-[0018] (teaching using firmware including PAL and SAL for correcting an error that is not correctable directly by hardware)). Implementing Nguyen's determining step in firmware was also known to be one of only three available alternatives—firmware, hardware, or combination—all of which would have been obvious to try, and any of which would be a suitable option. Ex. 1002, ¶137; *Intel Corp. v. PACT XPP Schweiz AG*, 61 F.4th 1373, 1380-81 (Fed. Cir. 2023).

The benefits of implementing Nguyen's determination in firmware would have been understood by a POSITA, because firmware is flexible and so can be modified after production, updated, and supported relatively quickly and inexpensively. Hardware, on the other hand, is inflexible. As noted by Dr. Baker, once manufactured, hardware cannot be easily modified, and any modification or revision is often expensive because it requires remanufacture of new components. Ex. 1002, ¶138.

Therefore, implementing Nguyen's determining step in Bigbee's firmware would have been both desirable and readily achievable by a POSITA. Ex. 1002, ¶¶134-138, 74-75.

#### C. Independent Claim 1

## 1. Limitation [1A]: A method comprising: detecting loss of lockstep for a lockstep pair of processors <sup>4</sup>

Bigbee teaches element [1A]. Bigbee's FRC logic detects loss of lockstep between the pair of lockstep processor cores and further discloses implementing the FRC logic by executable firmware. Ex. 1002, ¶¶139-140; Bigbee, [0019], [0034].

As shown below, Bigbee discloses a processor package including two processor cores, each with a private cache, which are coupled to a shared cache. Bigbee, Fig. 3, [0032]. The two processor cores function as a single logical processor and operate in an FRC mode ("lockstep pair of processors"), executing identical instructions on identical data to generate results for storage in associated private cache and/or shared cache. Bigbee, [0033]. Bigbee discloses "detecting loss of lockstep for a lockstep pair of processors" because FRC logic detects both inconsistencies in the generated results that indicate an FRC mismatch error and errors within the processor cores of a processor package that cause a break in the lockstep between the cores, disabling FRC mode operation. Bigbee, [0019], [0033]; Ex. 1002, ¶141.

<sup>&</sup>lt;sup>4</sup> These limitations appear and are labelled in the Claims Listing Appendix.

Bigbee further discloses implementing its FRC logic by executable firmware, as was known in the art. Bigbee, [0034]; Ex. 1002, ¶141 (citing Safford-181, 15:60-64).

Bigbee, Fig. 3.

2. Limitation [1B]: using firmware to trigger an operating system to idle the lockstep pair of processors, recover lockstep for the lockstep pair of processors, and trigger the operating system to recognize the lockstep pair of processors having recovered lockstep

Bigbee in view of Nguyen renders obvious [1B]. Ex. 1002, ¶¶142-147.

As explained above, a POSITA would have incorporated Nguyen's determining if the lockstep is recoverable into Bigbee to take an appropriate action responsive to the severity of the error detected in the lockstep processor pair.

Sections IV.A-B, *supra*. Bigbee in view of Nguyen further discloses that, responsive to determining if lockstep is recoverable from the detected error, the firmware triggers the operating system to idle the processors and recover lockstep between the pair of processors. Ex. 1002, ¶143.

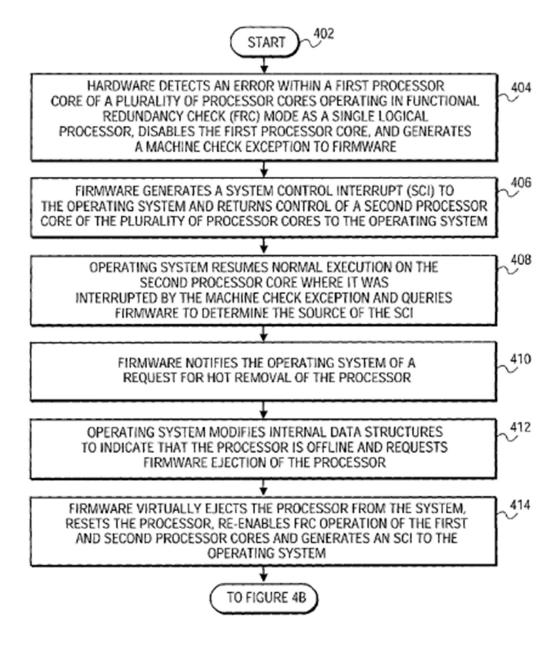

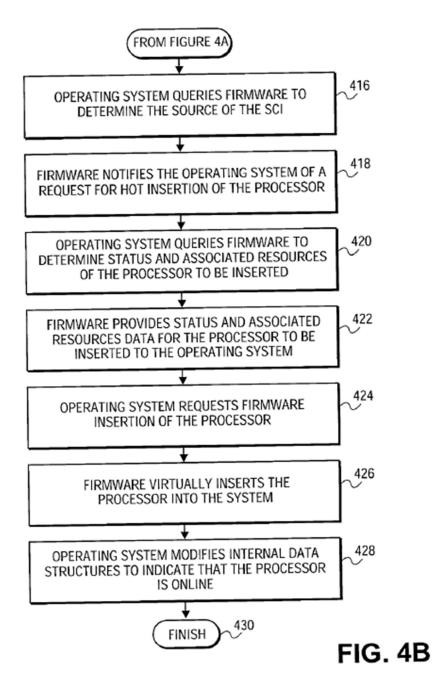

*First*, Bigbee discloses "using firmware to trigger an operating system to idle the lockstep pair of processors." Ex. 1002, ¶144. As shown in Figure 4A below, Bigbee discloses that firmware (e.g., SAL program code) generates a system control interrupt (SCI) to the operating system. Bigbee, [0035], Fig. 4A (block 406). In response to the SCI, the operating system queries firmware (ACPI BIOS) to determine the source of the SCI; firmware responds to the query by notifying the operating system of a request for processor hot removal (e.g., by a ACPI Notify command).<sup>5</sup> Bigbee, [0036], Fig. 4A (blocks 408-410) ("trigger an operating system"). The operating system then modifies its internal data structures to indicate that the processor is offline and requests firmware ejection of the processor (e.g., by executing an \_EJ<sub>X</sub> control method ("to idle the lockstep pair of processors"). Bigbee, [0036]-[0037], Fig. 4A (block 412); Ex. 1022, p. 162.

<sup>&</sup>lt;sup>5</sup> The term "processor" used in Bigbee's error recovering routine refers to the single logical processor that includes the pair of processor cores operating in lockstep. Ex. 1002, ¶144, n.4 (citing Bigbee, [0032], [0035]-[0038]).

FIG. 4A

Bigbee, Fig. 4A.

*Second*, Bigbee discloses "using firmware to … recover lockstep for the lockstep pair of processors." Ex. 1002, ¶145. In response to the operating system's ejection request, Bigbee's firmware virtually ejects the processor from

the system, resets the processor, re-enables FRC operation of the processor cores ("recover lockstep for the lockstep pair of processors") and generates an SCI to the operating system. *Id.*; Bigbee, [0037], Fig. 4A (block 414).

The '958 Patent similarly discloses idling the processors, by having the firmware use an ACPI method to "eject" the processors, thereby triggering the operating system to idle the master processor, resets the processor pair, and recover lockstep. Ex. 1001, 6:9-17, 6:40-42, 6:55-57; Ex. 1002, ¶146.

Bigbee discloses that its firmware generates an SCI to the operating system after recovering lockstep between the pair of processors. Bigbee, [0037], Fig. 4A (block 414). The operating system queries firmware (e.g., ACPI BIOS) to determine the source of the SCI, and the firmware responds to the query by notifying the operating system of a request for processor hot insertion ("trigger the operating system"). Bigbee, [0037], Fig. 4B (block 416-418). The firmware also provides the operating system with status and resource data of the processor to be inserted via one or more ACPI methods (e.g., STA, MAT, and CRS). Bigbee, [0037], Fig. 4B (block 422). The operating system then requests insertion of the processor by calling an ACPI method (e.g., PS0), which the firmware virtually executes to insert the processor into the system. Bigbee, [0037], Fig. 4B (block 424-426). Once the processor has been inserted, the operating system modifies its internal data structures to indicate that the processor is online and available ("recognize the lockstep pair of processors having recovered lockstep"). Bigbee, [0037], Fig. 4B (e.g., block 428);

Ex. 1002, ¶147.

Bigbee, Fig. 4B.

The '958 Patent similarly discloses that the firmware provides the operating system with status of the processors using an ACPI method (e.g., \_STA), and uses

an ACPI method to trigger the operating system to recognize the processors as available and as having recovered lockstep. Ex. 1001, 6:55-7:12; Ex. 1002, ¶148.

> 3. Limitation [1C]: responsive to said detecting loss of lockstep, using said firmware to determine if lockstep is recoverable for the lockstep pair of processors, wherein said using said firmware to determine if lockstep is recoverable further comprises determining if a lockstep mismatch has occurred between the lockstep pair of processors.

Bigbee-Nguyen renders obvious element [1C]. As explained for element [1A], Bigbee detects a loss of lockstep using firmware. Section IV.C.1. Nguyen discloses determining if lockstep is recoverable from lockstep errors, as was also known in the art. Ex. 1002, ¶¶150-151. Nguyen discloses responsive to the detection of loss of lockstep, the FRC checker and error detector operating together determine whether lockstep is recoverable from the detected error. Nguyen, [0022]-[0025], [0030], [0037], [0039]-[0041], [0046], [0056]-[0057]; Ex. 1002, ¶¶149-156.

Nguyen's FRC checker and error detector determine lockstep is recoverable from the detected error in two instances and non-recoverable from the detected error in one instance. Ex. 1002, ¶¶152. *First*, Nguyen's FRC checker and error detector determine a mismatch error that cannot be traced to a processor containing an underlying soft error is not recoverable. Nguyen, [0007], [0023]. *Second*, Nguyen's FRC checker and error detector determine that lockstep is recoverable from a soft error detector before detecting a mismatch error. Nguyen, [0005], [0022]-[0024], [0046]. *Third*, Nguyen's FRC checker and error detector determine

lockstep is recoverable from a mismatch error if an error in the processors is detected within a timeout interval from the detection of the mismatch error. Nguyen, [0023], [0030]; Ex. 1002, ¶152-153; Section II.C.2.

Nguyen further discloses "determining if a lockstep mismatch has occurred" because Nguyen determines if the lockstep is recoverable after detecting a mismatch error. Ex. 1002, ¶154-155. For example, in Nguyen's determining if lockstep is recoverable: (1) Nguyen's FRC checker's compare unit compares the data from both cores, and it sets a status flag to indicate whether the data matches or mismatches ("determining if a lockstep mismatch has occurred"); and (2) determining if Nguyen's error detector detects an error in the processors before (recoverable) or after (non-recoverable) the timeout interval of the timer unit expires. Ex. 1002, ¶155; Nguyen, [0056]-[0057]; Section II.C.2.

As explained in Section IV.B, a POSITA would have been motivated to incorporate Nguyen's determination of if lockstep is recoverable in Bigbee's FRC logic to increase system fault tolerance and availability and would have had a reasonable expectation of success in doing so. Ex. 1002, ¶156.

#### D. Overview of Bigbee-Nguyen-Goodrum Combination

Claims 9-12 all depend from claim 1. The elements of claim 1 are taught by Bigbee-Nguyen. Section IV.C. The additional elements of claims 9-12 are taught

by Goodrum and/or Bigbee, rendering these claims obvious in light of Bigbee-Nguyen-Goodrum. Ex. 1002, ¶157.

Goodrum recognizes that a fault-tolerant scheme is desirable to ensure that a multiprocessor system continues to function despite the occurrence of a failure in a processor. Goodrum, 2:15-31. Goodrum further recognizes the criticality of a boot processor in a multiprocessor system. Goodrum, 1:17-20, 2:15-31. Typically one processor in a multiprocessor system is assigned the role of boot processor, which is responsible for initializing the system and turning on the remaining processors. Goodrum, 2:15-31, 9:39-50. If the boot processor fails during startup, then it may not turn on the other processors, leaving the system incapacitated. Goodrum, 2:15-31; Ex. 1002, ¶158.

To provide a fault-tolerant system, Goodrum describes a hot spare boot circuit that detects a failure of a designated boot processor and reassigns the role of boot processor to a backup processor. Goodrum, Abstract, 1:17-20, 2:15-64, 3:7-31, 5:66-6:3, 6:28-57, 8:11-16, 8:60-64, 9:39-63, 17:7-16, 18:34-49, Fig. 2. Goodrum distinguishes the boot processor from the backup processor using first and second identifier values, respectively. Goodrum, 8:14-16, 17:7-19. In response to detecting a failure, the hot spare circuit disables the boot processor, modifies the identifier value of the backup processor to designate the backup processor as the new boot

processor, and then causes the new boot processor to complete system power on operations. Goodrum, 3:7-31, 9:39-63, 18:34-49; Ex. 1002, ¶159.

A POSITA would have understood the benefits to the Bigbee-Nguyen system of applying Goodrum's teaching to identify and switch to a backup processor for a failed boot processor. In particular, based on the teachings of Goodrum and Bigbee-Nguyen, a POSITA would have understood the desirability of detecting an error associated with a boot processor and the ability to identify a replacement backup processor both at startup and after startup. While Goodrum focuses on detecting boot processor errors during startup, Bigbee-Nguyen describes continuously monitoring its processors, and idling and restarting a processor for which a loss of lockstep is detected. After startup, if a failed boot processor is not switched to a backup processor, then the system may attempt to power up using the failed boot processor which Goodrum explains would leave the system incapacitated. Further, a POSITA would have understood that it would be beneficial for a recovered processor to then be used as a backup processor for the new boot processor, based on Goodrum's teaching regarding the benefits of maintaining a backup boot processor. Ex. 1002, ¶160.

Accordingly, a POSITA would have been motivated to modify Bigbee-Nguyen's response to a detected loss of lockstep error to include determining if the error was experienced by a boot processor (based on Goodrum's teachings of using identifiers to distinguish a boot processor from other processors), to reassign the role of boot processor to a backup processor (as further taught by Goodrum), and once lockstep is recovered (as is still taught by Bigbee and Nguyen) to use the original boot processor as a backup processor for the new boot processor (based on the teachings of Goodrum to provide a spare processor). By doing so, a POSITA would have understood that the reliability and availability of the Bigbee-Nguyen system would be improved, by ensuring that a boot processor is always available to power up the system in response to a system reset and/or to help recover lockstep or reset the processor for which a loss of lockstep was detected. Ex. 1002, ¶161. The addition of Goodrum does not remove the functionality of Bigbee-Nguyen that reads on claim 1, as described above.