#### UNITED STATES PATENT AND TRADEMARK OFFICE

#### BEFORE THE PATENT TRIAL AND APPEAL BOARD

KIOXIA AMERICA, INC. and KIOXIA CORPORATION,

Petitioners,

v.

BiTMICRO LLC,

Patent Owner.

Case No.: IPR2023-00743 U.S. Patent No. 6,496,939

\_\_\_\_\_

# PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 6,496,939

### **TABLE OF CONTENTS**

| I.    | INTR                     | NTRODUCTION1                                                                                                                                                                                             |  |  |

|-------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| II.   | GRO                      | OUNDS FOR STANDING1                                                                                                                                                                                      |  |  |

| III.  | FEES                     | EES1                                                                                                                                                                                                     |  |  |

| IV.   | PRECISE RELIEF REQUESTED |                                                                                                                                                                                                          |  |  |

|       | A.                       | Prior Art2                                                                                                                                                                                               |  |  |

|       |                          | 1. Horning2                                                                                                                                                                                              |  |  |

|       |                          | 2. Germer2                                                                                                                                                                                               |  |  |

|       |                          | 3. Bruder2                                                                                                                                                                                               |  |  |

|       |                          | 4. Weber                                                                                                                                                                                                 |  |  |

|       |                          | 5. Stokes                                                                                                                                                                                                |  |  |

| V.    | IPR C                    | ROUNDS                                                                                                                                                                                                   |  |  |

| VI.   | THE '939 PATENT          |                                                                                                                                                                                                          |  |  |

|       | A.                       | Overview of the '939 Patent                                                                                                                                                                              |  |  |

|       | B.                       | Prosecution History7                                                                                                                                                                                     |  |  |

| VII.  | LEVE                     | EL OF ORDINARY SKILL IN THE ART                                                                                                                                                                          |  |  |

| VIII. | CLAIM CONSTRUCTION       |                                                                                                                                                                                                          |  |  |

|       | A.                       | Claims 1 and 10: "predetermined level"9                                                                                                                                                                  |  |  |

|       | B.                       | Claims 1, 2, 6, 10, 11, and 15: "computing<br>engine"/"computer engine"                                                                                                                                  |  |  |

|       | C.                       | Claim 10: "means for activating a plurality of super<br>capacitors to supply power to the computing engine based<br>upon power being removed from the computer system"                                   |  |  |

|       | D.                       | Claim 10: "means for reconfiguring the data in the computing engine"                                                                                                                                     |  |  |

|       | E.                       | Claim 10: "means for deactivating the plurality of super<br>capacitors to cut off power to the computing engine based<br>upon the plurality of super capacitors discharging to a<br>predetermined level" |  |  |

|     | F.  | Claim 12: "means for allowing all data to be transferred<br>from the at least one volatile memory to the at least one<br>non-volatile memory" |

|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

|     | G.  | Claim 6: "reversing the flow of current between the computing engine and the plurality of super capacitors"                                   |

|     | H.  | Claim 15: "means for reversing the flow of current<br>between the computing engine and the plurality of super<br>capacitors"                  |

|     | I.  | Claim 15: "means for discharging current from the plurality of super capacitors to the computing engine"                                      |

| IX. | OVE | RVIEW OF THE PRIOR ART16                                                                                                                      |

|     | A.  | Bruder Discloses Systems and Methods for Storing Data in<br>a Computer System When Power Is Lost16                                            |

|     | В.  | Weber Discloses a Transfer Memory Backup System To<br>Safeguard Data When Power Is Lost17                                                     |

|     | C.  | Germer Discloses an Electronic Register That Preserves<br>Data When Power Is Lost                                                             |

|     | D.  | Horning Discloses A Data Protection System That Uses<br>Reserve Power To Maintain Data in Volatile Memory                                     |

|     | E.  | Stokes Discloses a Super Capacitor-Based Backup Power<br>System for a Nonvolatile Realtime Clock Calendar Module19                            |

| Х.  |     | CHALLENGED CLAIMS ARE UNPATENTABLE AND<br>ULD BE CANCELLED19                                                                                  |

|     | A.  | Ground 1: Claims 1-3 Are Rendered Obvious by Horning<br>in View of Stokes                                                                     |

|     |     | 1. Claim 1 Is Rendered Obvious by Horning in View of Stokes                                                                                   |

|     |     | 2. Claim 2 Is Rendered Obvious by Horning in View of Stokes                                                                                   |

|     |     | 3. Claim 3 Is Rendered Obvious by Horning in View of Stokes                                                                                   |

|     | В.  | Ground 2: Claims 1-3 Are Rendered Obvious by Germer in<br>View of Horning Further in View of Stokes27                                         |

|     |     |                                                                                                                                               |

|    | 1.                                                                                                                          | Claim 1 Is Rendered Obvious by Germer in View of<br>Horning Further in View of Stokes               |  |

|----|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

|    | 2.                                                                                                                          | Claim 2 Is Rendered Obvious by Germer in View of<br>Horning Further in View of Stokes               |  |

|    | 3.                                                                                                                          | Claim 3 Is Rendered Obvious by Germer in View of<br>Horning Further in View of Stokes               |  |

| C. | C. Ground 3: Each of the Challenged Claims Is Rendered<br>Obvious by Bruder in View of Horning Further in View of<br>Stokes |                                                                                                     |  |

|    | 1.                                                                                                                          | Claim 1 Is Rendered Obvious by Bruder in View of<br>Horning Further in View of Stokes               |  |

|    | 2.                                                                                                                          | Claim 2 Is Rendered Obvious by Bruder in View of<br>Horning Further in View of Stokes               |  |

|    | 3.                                                                                                                          | Claim 3 Is Rendered Obvious by Bruder in View of<br>Horning Further in View of Stokes               |  |

|    | 4.                                                                                                                          | Claim 6 Is Rendered Obvious by Bruder in View of<br>Horning Further in View of Stokes               |  |

|    | 5.                                                                                                                          | Claim 10 Is Rendered Obvious by Bruder in View of<br>Horning Further in View of Stokes              |  |

|    | 6.                                                                                                                          | Claim 11 Is Rendered Obvious by Bruder in View of<br>Horning Further in View of Stokes              |  |

|    | 7.                                                                                                                          | Claim 12 Is Rendered Obvious by Bruder in View of<br>Horning Further in View of Stokes              |  |

|    | 8.                                                                                                                          | Claim 15 Is Rendered Obvious by Bruder in View of<br>Horning Further in View of Stokes              |  |

| D. |                                                                                                                             | nd 4: Claims 1-3 and 6 Are Rendered Obvious by<br>er in View of Horning Further in View of Stokes62 |  |

|    | 1.                                                                                                                          | Claim 1 Is Rendered Obvious By Weber in View of<br>Horning Further in View of Stokes                |  |

|    | 2.                                                                                                                          | Claim 2 Is Rendered Obvious By Weber in View of<br>Horning Further in View of Stokes                |  |

|    | 3.                                                                                                                          | Claim 3 Is Rendered Obvious by Weber in View of<br>Horning Further in View of Stokes                |  |

|       |      | 4. Claim 6 Is Rendered Obvious by Weber in View of<br>Horning Further in View of Stokes | .72 |

|-------|------|-----------------------------------------------------------------------------------------|-----|

| XI.   | INST | ITUTION SHOULD NOT BE DISCRETIONARILY DENIED                                            | .74 |

|       | A.   | The Board Should Not Exercise Its Discretion Under 35 U.S.C. § 314(a)                   | .74 |

|       | B.   | The Board Should Not Exercise Its Discretion under 35 U.S.C. § 325(d)                   | .75 |

| XII.  | MAN  | DATORY NOTICES                                                                          | .76 |

|       | A.   | Real Parties in Interest—37 C.F.R. § 42.8(b)(1)                                         | .76 |

|       | В.   | Related Matters—37 C.F.R. § 42.8(b)(2)                                                  | .76 |

|       | C.   | Lead and Back-Up Counsel—37 C.F.R. § 42.8(b)(3)                                         | .76 |

|       | D.   | Service Information—37 C.F.R. § 42.8(b)(4)                                              | .77 |

| XIII. | CON  | CLUSION                                                                                 | .77 |

### **TABLE OF AUTHORITIES**

| Page(s)                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------|

| Cases                                                                                                                    |

| Advanced Bionics, LLC v. MED-EL Elektromedizinische Geräte<br>GmbH,<br>IPR2019-01469, Paper 6 (PTAB Feb. 13, 2020)75, 76 |

| 1112019 01109, 1 upor 0 (1 1111) 1 co. 13, 2020)                                                                         |

| <i>BiTMICRO LLC v. Intel Corp.</i> ,<br>Case No. 5:23-cv-00625 (N.D. Cal.)                                               |

| <i>BiTMICRO LLC v. KIOXIA Am. Inc., et al.,</i><br>Case NO. 6:22-cv-00331 (W.D. Tex. 2022)76                             |

| <i>KCJ Corp. V. Kinetic Concepts, Inc.</i> ,<br>223 F.3d 1351 (Fed. Cir. 2000)                                           |

| Nidec Motor Corp. v. Zhongshan Broad Ocean Motor Co.,<br>868 F.3d 1013 (Fed. Cir. 2017)7                                 |

| <i>Phillips v. AWH Corp.</i> ,<br>415 F.3d 1303 (Fed. Cir. 2005)7                                                        |

| Sotera Wireless, Inc., v. Masimo Corp.<br>IPR2020-01019, Paper 12 (PTAB Dec. 1, 2020)                                    |

| Target Corp. v. Proxicom Wireless, LLC,IPR2020- 009048                                                                   |

| The Data Co. Techs., Inc. v. Bright Data Ltd.,<br>IPR2022-00135, Paper 12 (PTAB June 1, 2022)                            |

| Western Digital Corp. v. Spex Techs., Inc.,<br>IPR2018-00084, Paper 14 (PTAB., April 25, 2018)                           |

| <i>Williamson v. Citrix Online, LLC</i> ,<br>792 F.3d 1339 (Fed. Cir. 2015)                                              |

#### Statutes

| 35 U.S.C. § 102(b)                                                         | 2, 3           |

|----------------------------------------------------------------------------|----------------|

| 35 U.S.C. § 103                                                            |                |

| 35 U.S.C. § 103(a)                                                         | 2              |

| 35 U.S.C. § 112                                                            | 8              |

| 35 U.S.C. § 311                                                            | 2              |

| 35 U.S.C. § 314(a)                                                         | 74, 75         |

| 35 U.S.C. § 325(d)                                                         | 75             |

|                                                                            |                |

| Regulations                                                                |                |

| <b>Regulations</b><br>37 C.F.R. § 42.8(b)(1)                               | 76             |

|                                                                            |                |

| 37 C.F.R. § 42.8(b)(1)                                                     | 76             |

| 37 C.F.R. § 42.8(b)(1)<br>37 C.F.R. § 42.8(b)(2)                           | 76<br>76       |

| 37 C.F.R. § 42.8(b)(1)<br>37 C.F.R. § 42.8(b)(2)<br>37 C.F.R. § 42.8(b)(3) | 76<br>76<br>77 |

### LIST OF EXHIBITS

| Ex. No. | Description                                                                                                                                                                     |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1001    | U.S. Patent No. 6,496,939 ("the '939 patent")                                                                                                                                   |  |

| 1002    | Excerpts of the File History for U.S. Patent No. 6,496,939                                                                                                                      |  |

| 1003    | Declaration of Dr. R. Jacob Baker                                                                                                                                               |  |

| 1004    | Curriculum Vitae of Dr. R. Jacob Baker                                                                                                                                          |  |

| 1005    | U.S. Patent No. 4,559,616 ("Bruder"). Bruder issued on December 17, 1985. Thus, Bruder is prior art under pre-AIA 35 U.S.C. § 102(b).                                           |  |

| 1006    | U.S. Patent No. 5,596,708 ("Weber"). Weber issued on January 21, 1997. Thus, Weber is prior art under pre-AIA 35 U.S.C. § 102(b).                                               |  |

| 1007    | U.S. Patent No. 4,591,782 ("Germer"). Germer issued on May 27, 1986. Thus, Germer is prior art under 35 U.S.C. § 102(b).                                                        |  |

| 1008    | U.S. Patent No. 5,414,861 ("Horning"). Horning issued on May 9, 1995. Thus, Horning is prior art under 35 U.S.C. § 102(b).                                                      |  |

| 1009    | Claim Construction Order and Memorandum in Support Thereof,<br><i>BiTMICRO LLC v. KIOXIA Am., Inc.</i> , Case No. 6:22-cv-00331-<br>ADA, Dkt. No. 54 (W.D. Tex. Feb. 16, 2023). |  |

| 1010    | U.S. Patent No. 3,980,935 ("Worst"). Worst issued on September 14, 1976. Thus, Worst is prior art under 35 U.S.C. § 102(b).                                                     |  |

| 1011    | U.S. Patent No. 4,306,299 ("Check"). Check issued on December 15, 1981. Thus, Check is prior art under 35 U.S.C. § 102(b).                                                      |  |

| 1012    | U.S. Patent No. 4,431,134 ("Hendricks"). Hendricks issued on<br>February 14, 1984. Thus, Hendricks is prior art under<br>35 U.S.C. § 102(b).                                    |  |

| 1013    | U.S. Patent No. 4,701,858 ("Stokes"). Stokes issued on October 20, 1987. Thus, Stokes is prior art under 35 U.S.C. § 102(b).                                                    |  |

| Ex. No. | Description                                                                                                                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------|

| 1014    | U.S. Patent No. 4,453,117 ("Elms"). Elms issued on June 5, 1984.<br>Thus, Elms is prior art under 35 U.S.C. § 102(b).              |

| 1015    | U.S. Patent No. 4,412,284 ("Kerforne"). Kerforne issued on October 25, 1983. Thus, Kerforne is prior art under 35 U.S.C. § 102(b). |

| 1016    | U.S. Patent No. 3,562,555 ("Ahrons"). Ahrons issued on February 9, 1971. Thus, Ahrons is prior art under to 35 U.S.C. § 102(b).    |

| 1017    | U.S. Patent No. 4,636,963 ("Nakajima"). Nakajima issued on January 13, 1987. Thus, Nakajima is prior art under 35 U.S.C. § 102(b). |

| Claim element | Claim 1                                                                                                                                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Claim 1 Pre] | A method for controlling data in a computer system when<br>the computer system loses power, the computer system<br>comprising a computing engine, comprising the steps of:                |

| [Claim 1a]    | (a) activating a plurality of super capacitors to supply power<br>to the computing engine based upon power being removed<br>from the computer system;                                     |

| [Claim 1b]    | (b) reconfiguring the data in the computing engine; and                                                                                                                                   |

| [Claim 1c]    | (c) deactivating the plurality of super capacitors to cut off<br>power to the computing engine based upon the plurality of<br>super capacitors discharging to a predetermined level.      |

| Claim element | Claim 2                                                                                                                                                                                   |

| [Claim 2a]    | The method of claim 1 wherein the computing engine<br>comprises a least one volatile memory and at least one non-<br>volatile memory.                                                     |

| Claim element | Claim 3                                                                                                                                                                                   |

| [Claim 3a]    | The method of claim 2 wherein the reconfiguring step (b) further comprises:                                                                                                               |

| [Claim 3b]    | (b1) allowing all data to be transferred from the at least one volatile memory to the at least one non-volatile memory.                                                                   |

| Claim element | Claim 6                                                                                                                                                                                   |

| [Claim 6 a]   | The method of claim 3 wherein the activating step (a) further<br>comprises: (a1) reversing the flow of current between the<br>computing engine and the plurality of super capacitors; and |

| [Claim 6b]    | (a2) discharging current from the plurality of super capacitors to the computing engine.                                                                                                  |

| Claim element | Claim 10                                                                                                                                                                                  |

### Challenged Claims of U.S. Patent No. 6,496,939

| [Claim 10 Pre] | A system for controlling data in a computer system when the computer system loses power, the computer system comprising a computer engine, comprising:                                     |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Claim 10a]    | means for activating a plurality of super capacitors to supply<br>power to the computing engine based upon power being<br>removed from the computer system;                                |

| [Claim 10b]    | means for reconfiguring the data in the computing engine;<br>and                                                                                                                           |

| [Claim 10c]    | means for deactivating the plurality of super capacitors to cut<br>off power to the computing engine based upon the plurality<br>of super capacitors discharging to a predetermined level. |

| Claim element  | Claim 11                                                                                                                                                                                   |

| [Claim 11]     | The system of claim 10 wherein the computing engine comprises a least one volatile memory and at least one non-volatile memory.                                                            |

| Claim element  | Claim 12                                                                                                                                                                                   |

| [Claim 12 Pre] | The system of claim 11 wherein the reconfiguring means further comprises:                                                                                                                  |

| [Claim 12a]    | means for allowing all data to be transferred from the at least<br>one volatile memory to the at least one non-volatile memory.                                                            |

| Claim element  | Claim 15                                                                                                                                                                                   |

| [Claim 15 Pre] | The system of claim 12 wherein the activating means further comprises:                                                                                                                     |

| [Claim 15a]    | means for reversing the flow of current between the computing engine and the plurality of super capacitors; and                                                                            |

| [Claim 15b]    | means for discharging current from the plurality of super capacitors to the computing engine.                                                                                              |

#### I. INTRODUCTION

KIOXIA Corporation and KIOXIA America, Inc. ("Petitioners") petition for institution of inter partes review ("IPR") of claims 1-3, 6, 10-12, and 15 ("challenged claims") of U.S. Patent No. 6,496,939 ("the '939 patent"). Ex-1001.

#### II. GROUNDS FOR STANDING

Petitioners certify that the '939 patent is available for review under 35 U.S.C. § 311(c) and that Petitioners are not estopped from requesting *inter partes* review of the challenged claims on the grounds identified in this Petition.<sup>1</sup>

#### III. FEES

The Commissioner is hereby authorized to charge or credit the fee specified by 37 C.F.R. § 42.15(a), and any other additional fees, to Bracewell LLP Deposit Account No. 50-0259.

<sup>&</sup>lt;sup>1</sup> The '939 patent expired on September 21, 2019. The Board has jurisdiction over expired patents through *inter partes* review. *See, e.g., See, e.g., Sony Corp. v. Iancu*, 924 F.3d 1235, 1239–41 (Fed. Cir. 2019) (articulating the importance of the Board's review of expired patents because expired patents can be asserted for past infringement); *see also, e.g., Wasica Fin. GmbH v. Cont'l Auto. Sys., Inc.*, 853 F.3d 1272, 1279 (Fed. Cir. 2017) (noting that "[t]he Board construes claims of an expired patent in accordance with *Phillips*").

#### **IV. PRECISE RELIEF REQUESTED**

Petitioners request review of the challenged claims under 35 U.S.C. § 311 and cancellation of the challenged claims under pre-AIA 35 U.S.C. § 103(a) in view of the prior art and grounds described herein.

#### A. Prior Art

#### 1. Horning

Petitioners rely on U.S. Patent No. 5,414,861 ("Horning"). Ex-1008. Cornwell was issued on May 9, 1995, more than a year before the alleged priority date for the '939 patent, and qualifies as a prior art printed publication under at least pre-AIA 35 U.S.C. § 102(b).

#### 2. Germer

Petitioners also rely on U.S. Patent No. 4,591,782 ("Germer"). Ex-1007. Germer was issued on May 27, 1986, more than a year before the alleged priority date for the '939 patent, and qualifies as a prior art printed publication under at least pre-AIA 35 U.S.C. § 102(b).

#### 3. Bruder

Petitioners also rely on U.S. Patent No. 4,559,616 ("Bruder"). Ex-1005. Bruder was issued on December 17, 1985, more than a year before the alleged priority date for the '939 patent, and qualifies as a prior art printed publication under

2

at least pre-AIA 35 U.S.C. § 102(b).

#### 4. Weber

Petitioners rely on U.S. Patent No. 5,596,708 ("Weber"). Ex-1006. Weber was issued on January 21, 1997, more than a year before the alleged priority date for the '939 patent, and qualifies as a prior art printed publication under at least pre-AIA 35 U.S.C. § 102(b).

#### 5. Stokes

Petitioners rely on U.S. Patent No. 4,701,858 ("Stokes"). Ex-1013. Stokes was issued on October 20, 1987, more than a year before the alleged priority date for the '939 patent, and qualifies as a prior art printed publication under at least pre-AIA 35 U.S.C. § 102(b).

#### V. IPR GROUNDS

| Ground | Claims                | Statutory Basis                                                                      |

|--------|-----------------------|--------------------------------------------------------------------------------------|

| 1      | 1-3                   | Horning in view of Stokes under pre-AIA 35 U.S.C. § 103                              |

| 2      | 1-3                   | Germer in view of Horning further in view of Stokes<br>under pre-AIA 35 U.S.C. § 103 |

| 3      | 1-3, 6, 10-<br>12, 15 | Bruder in view of Horning further in view of Stokes<br>under pre-AIA 35 U.S.C. § 103 |

| 4      | 1-3, 6                | Weber in view of Horning further in view of Stokes<br>under pre-AIA 35 U.S.C. § 103  |

#### VI. THE '939 PATENT

#### A. Overview of the '939 Patent

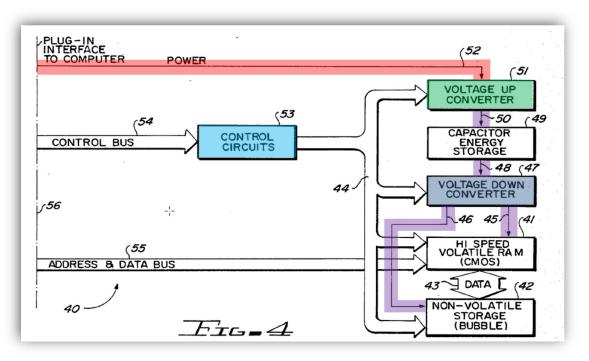

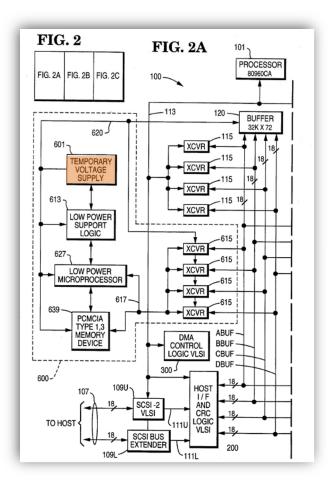

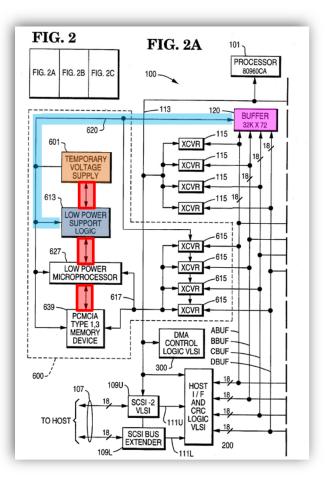

The '939 patent describes well known systems and methods for controlling data in a computer system upon power loss. Ex-1001 at 1:8-11. Computer systems typically comprise volatile "cache" memory, which is erased when power is removed, and non-volatile memory, which preserves data when power is removed. *Id.* at 1:15-33. Because volatile cache memory operates much faster than non-volatile memory, data is typically written to cache memory before being transferred to non-volatile memory. *Id.* The '939 patent explains that sudden loss of external power leaves insufficient time to transfer all newly written data from volatile cache memory to non-volatile memory, which risks data loss. *Id.* at 1:34-39. Accordingly, the '939 patent identifies an alleged need to ensure transfer of newly written data in the volatile memory to non-volatile memory in the event of a sudden power loss. *Id.* at 2:13-16.

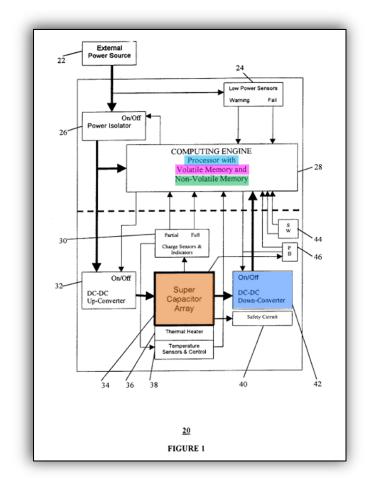

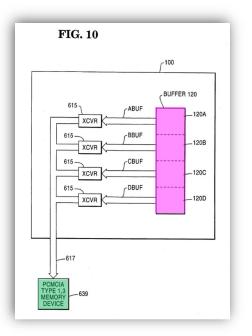

The '939 patent purports to address this perceived need by using a "computing engine," comprising a processor, volatile memory, and non-volatile memory, *id.* at 3:33-36; Figure 1, and an array of "super capacitors" as a "short term power source" for the computing engine, *id.* at 2:27-31; 3:3-5. Upon a sudden loss of external power, the super-capacitors are purportedly "activated" to maintain internal power to the system. *Id.* at 5:8-11. Using the stored charge on the super-capacitors, data

in volatile memory can be transferred to non-volatile memory. *Id.* at 5:33-36. Once the super-capacitors have discharged "to a predetermined level," the supercapacitors are purportedly "deactivated" to cut off power to the computer system. *Id.* at 5:39-43; 5:48-52; 6:49-53. According to the specification, the super-capacitors are activated and deactivated by a "down-converter," which converts the high voltage stored on the super-capacitors to a lower voltage that can be utilized by the computing engine. *Id.* at 5:8-29; 5:39-43; 6:11-31; 6:40-44.

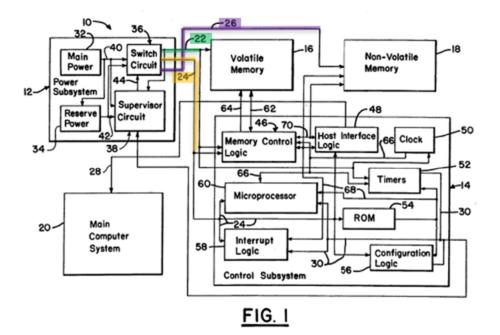

Figure 1 of the '939 patent, annotated below, illustrates this system, including the computing engine, which comprises a **processor**, **volatile memory**, and **non-volatile memory**, as well as a **super-capacitor array** and voltage **down-converter**.

However, systems comprising the disclosed "computing engine," supercapacitors, and voltage down-converters were well known before the priority date of the '939 patent. Likewise, reconfiguring data using energy stored in capacitors to facilitate data transfer from volatile to non-volatile memory upon a sudden loss of power was equally well known before the applicable priority date. As explained below, Horning, Stokes, Bruder, Weber, and Germer all disclose such systems. Accordingly, nothing about the claims of the '939 patent would have been novel or non-obvious to a person of ordinary skill in the art ("POSITA") at the time the application for the '939 patent was filed. Ex-1003, ¶ 31.

#### **B. Prosecution History**

The application underlying the '939 patent was filed on September 21, 1999. In response to a rejection asserting that the applied-for claims were anticipated or rendered obvious by the prior art, the applicant made a number of substantive amendments to the claims. Importantly, neither Horner, Stokes, Germer, Bruder, nor Weber were before the Examiner during prosecution; however, as discussed below, these references disclose the particular claim elements on which the Examiner based the Notice of Allowance. *See* Ex-1003, ¶¶ 32-38.

#### VII. LEVEL OF ORDINARY SKILL IN THE ART

As of the priority date, a POSITA would have had at least a Bachelor's degree in electrical or computer engineering, or a similar field, and at least two years of work experience in the computer memory or data storage industry. Ex-1003, ¶¶ 64-67. A POSITA could have substituted less formal education with additional relevant work experience, and vice versa. *Id*.

#### **VIII. CLAIM CONSTRUCTION**

Claim terms should be construed according to the *Phillips* standard. *See Phillips v. AWH Corp.*, 415 F.3d 1303 (Fed. Cir. 2005); *see also* 37 C.F.R. § 42.100(b). The Board need only construe terms to the extent necessary to resolve a controversy. *See Nidec Motor Corp. v. Zhongshan Broad Ocean Motor*

7

#### Co., 868 F.3d 1013, 1017 (Fed. Cir. 2017).

A patent claim that uses the term "means for" invokes a rebuttable presumption that the term is a means-plus-function term that should be construed pursuant to 35 U.S.C. § 112. *Williamson v. Citrix Online, LLC*, 792 F.3d 1339, 1348 (Fed. Cir. 2015). Construing a means-plus-function term is a two-step process. *Id.* at 1351. First, the claimed function must be identified. *Id.* Second, the structure disclosed in the specification for performing the claimed function must be determined. *Id.*

For purposes of this proceeding only, Petitioners submit constructions for the below terms.<sup>2</sup> Petitioners do not believe that construction of any other term is

<sup>2</sup> While Petitioner proposes these constructions for purposes of this proceeding, Petitioner reserves its right to revise or amend these constructions in any other action or forum. *Western Digital Corp. v. Spex Techs., Inc.,* IPR2018-00084, Paper 14 at 11 (PTAB., April 25, 2018) ("37 C.F.R. § 104(b)(3) does not require [a p]etitioner to express its subjective agreement regarding correctness of its proffered claim constructions or to take ownership of those constructions"). Petitioner also reserves the right to challenge the validity of the challenged claims under 35 U.S.C. § 112 in another other action or forum. *See Target Corp. v. Proxicom Wireless, LLC,* IPR2020- 00904, Paper 11 at 12-13 (PTAB Nov. 10, 2020) (instituting IPR despite

necessary.

#### A. Claims 1 and 10: "predetermined level"

The district court construed the term "predetermined level" as having a plain and ordinary meaning, which Petitioners adopt for the purposes of this Petition. *See* Ex-1009.

## B. Claims 1, 2, 6, 10, 11, and 15: "computing engine"/"computer engine"

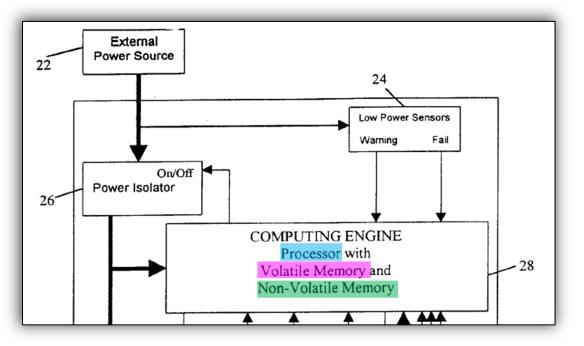

Independent claim 1 and dependent claims 2 and 6 recite a "computing engine." Ex-1001, claim 1, 2, 6. Claims 10, 11, and 15 contain similar recitations in meanplus-function format."<sup>3</sup> "Computing engine" should be construed as comprising a processor or similar structure for directing the transfer and storage of data in memory, volatile memory, and non-volatile memory. The specification explicitly states that the computing engine "contain[s] the processor, volatile and non-volatile memory." *Id.* at 3:33-36. Annotated Figure 1, shown below, further illustrates the computing

indefiniteness arguments in parallel lawsuit, explaining that this kind of "alternative pleading before a district court is common practice, especially where it concerns issues outside the scope of inter partes review").

<sup>&</sup>lt;sup>3</sup> The preamble of claim 10 recites a "computer engine," but the individual elements of claim 10 recite a "computing engine."

engine as containing a processor, volatile memory, and non-volatile memory:

Moreover, a POSITA would have understood that the processor is a structure that controls the memory and sends signals and instructions to direct the transfer and storage of data in the volatile and non-volatile memory. Ex-1003, ¶ 73. Accordingly, based on the description in the specification, together with the knowledge of a POSITA, "computing engine" should be construed as comprising a processor or similar structure for directing the transfer and storage of data in memory, volatile memory, and non-volatile memory. Id.

#### C. Claim 10: "means for activating a plurality of super capacitors to supply power to the computing engine based upon power being removed from the computer system"

This term should be construed as a means-plus-function term, with a recited function of "activating a plurality of super capacitors to supply power to the

computing engine based upon power being removed from the computer system." The corresponding structure should be construed as a "down-converter and upconverter, and equivalents thereof, together with associated circuit components."

While the district court did not directly construe "means for activating," in connection with claim 15, the court construed "means for reversing the flow of current between the computing engine and the plurality of super capacitors." Ex-1009 at 26, 47. Per claim 15, the "activating means . . . comprises: means for reversing the flow of current . . . ." Accordingly, because the "means for activating" as construed by the court includes the "means for reversing," Petitioners adopt the court's construction of "means for reversing" for the "means for activating" claim element, which is a "down-converter 42 and up-converter 42<sup>4</sup> in Figure 1 (and corresponding text), and equivalents thereof." *Id.* Therefore, Petitioners propose that the structure for the "means for activating" includes the structure identified by the district court with respect to the "means for reversing," as well as associated circuit components.

11

<sup>&</sup>lt;sup>4</sup> The court's recitation of an "up-converter 42" appears to be an error, as the '939 patent does not disclose an up-cover with this numerical designation. Instead, the '939 patent discloses an "up-converter 32." Ex-1001 at 3:39-41 (emphasis added); Figure 1.

### D. Claim 10: "means for reconfiguring the data in the computing engine"

This term should be construed as a means-plus-function term, with a recited function of "reconfiguring the data in the computing engine." The corresponding structure should be construed as a "processor or equivalent structure that directs the transfer and storage of data in memory."

As explained above, the '939 patent states that the computing engine comprises a processor, volatile memory, and non-volatile memory. Ex-1001 at 3:33-36; Figure 1; *supra* § VIII.B. A POSITA would understand that the processor is the structure that controls the volatile and non-volatile memory in the computing engine by sending signals and instructions to direct the transfer and storage of data in the volatile and non-volatile memory. *See, e.g.*, Ex-1001 at 5:33-36; 6:35-37; *supra* § VIII.B; Ex-1003, ¶¶ 78-82. Thus, Petitioners applies the foregoing function and structure for this term.

# E. Claim 10: "means for deactivating the plurality of super capacitors to cut off power to the computing engine based upon the plurality of super capacitors discharging to a predetermined level"

The district court construed this term as a means-plus-function term with the recited function as "deactivating the plurality of super capacitors to cut off power to the computing engine based upon the plurality of super capacitors discharging to a predetermined level" and the corresponding structure as a "down-converter 42 in

Figure 1 (and corresponding text) and equivalents thereof, and switches, transistors, gates, *etc.* that are generally known in the art." Ex-1009 at 18-20, 46. Petitioners apply this construction for purposes of this Petition.

# F. Claim 12: "means for allowing all data to be transferred from the at least one volatile memory to the at least one non-volatile memory"

This term should be construed as a means-plus-function term, with a recited function of "allowing all data to be transferred from the at least one volatile memory to the at least one non-volatile memory." The corresponding structure should be construed as a "processor or equivalent structure that directs the transfer and storage of data in memory and is configured to transfer all data from volatile to non-volatile memory."

As stated in the claim language, dependent claim 12 further limits the "means for reconfiguring" claim element. The structure corresponding to the "means for reconfiguring" claim element is a "processor or equivalent structure that directs the transfer and storage of data in memory." *See supra* § VIII.D. Claim 12 illustrates that this structure must further be configured such to allow "all data to be transferred from the at least one volatile memory to the at least one non-volatile memory." For the purposes of this Petition, Petitioner thus applies the foregoing function and structure for this term.

#### G. Claim 6: "reversing the flow of current between the computing

#### engine and the plurality of super capacitors"

Claim 6 recites "reversing the flow of current between the computing engine and the plurality of super capacitors." The district court construed this term as having a plain and ordinary meaning. Ex-1009 at 23-24, 46. For the purposes of this Petition, Petitioners apply the court's construction.

### H. Claim 15: "means for reversing the flow of current between the computing engine and the plurality of super capacitors"

The district court construed this term as a means-plus-function term, with the recited function of "reversing the flow of current between the computing engine and the plurality of super capacitors" and the following corresponding structure: "down-converter 42 and up-converter 42 in Figure 1 (and corresponding text), and equivalents thereof." Ex-1009 at 26, 47. Petitioners apply the court's construction for purposes of this Petition.

# I. Claim 15: "means for discharging current from the plurality of super capacitors to the computing engine"

This term should be construed as a means-plus-function term, with a recited function of "discharging current from the plurality of super capacitors to the computing engine." The corresponding structure should be construed as a "voltage down-converter or equivalent structure that converts a high voltage signal to a lower voltage signal and is configured to discharge current from the capacitors to the

computing engine."

As stated in the claim language, dependent claim 15 further limits the "means for activating the plurality of super-capacitors" claim element. As explained above, Petitioners construe the "means for activating" element as including a "downconverter 42 and up-converter 42 in Figure 1 (and corresponding text), and equivalents thereof." The portion of this structure corresponding to "discharging current from the plurality of super capacitors to the computing engine" is a downconverter configured to discharge current from the plurality of super-capacitors to the computing engine.

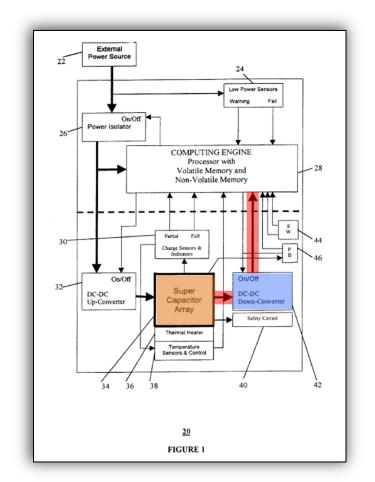

This is confirmed by the specification, which states that, once the downconverter has been activated and current has been reversed, "[t]he super capacitors then begin to *slowly discharge current* to the computer system *through the downconverter*." Ex-1001 at 5:26-28 (emphasis added); 6:28-31; Figures 3 & 5 (current discharged "to the computer system through the down converter"). Annotated Figure 1, shown below, further illustrates that **current** from the **capacitors** is discharged through the **down-converter** to the computing engine:

For the purposes of this Petition, Petitioners thus apply the foregoing

function and structure for this term.

#### IX. OVERVIEW OF THE PRIOR ART

#### A. Bruder Discloses Systems and Methods for Storing Data in a Computer System When Power Is Lost

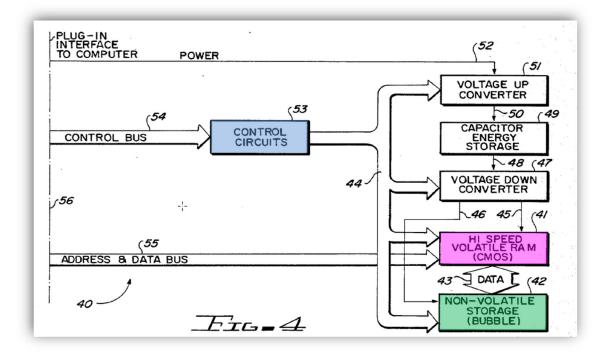

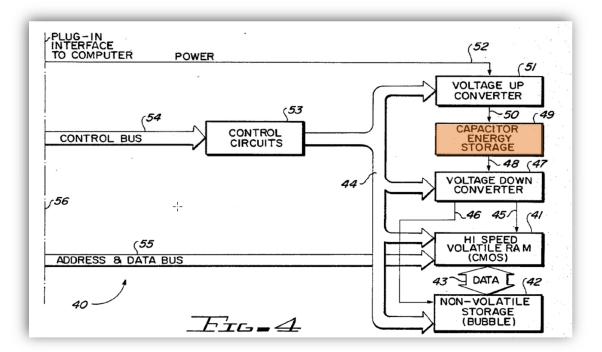

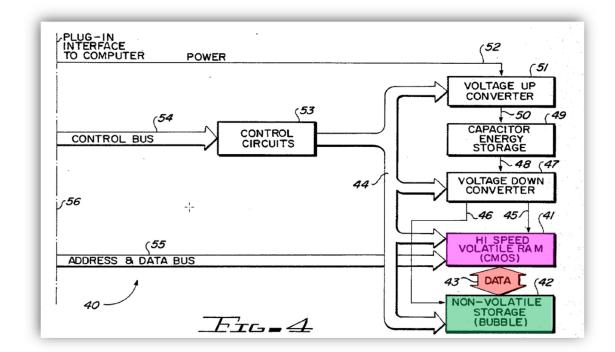

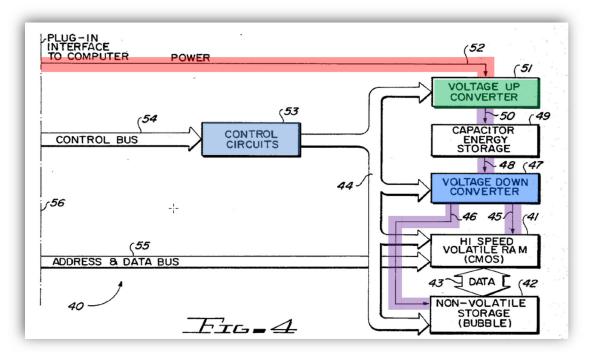

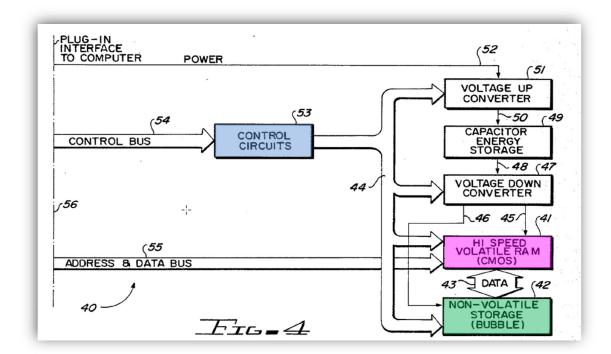

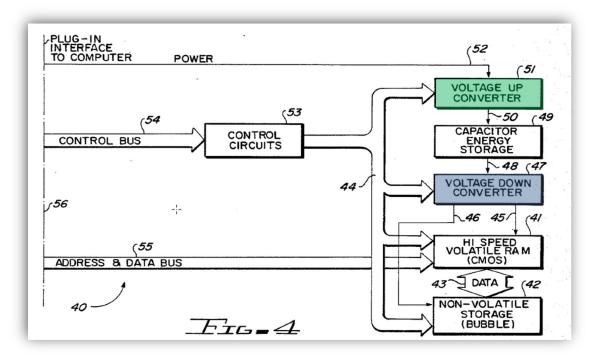

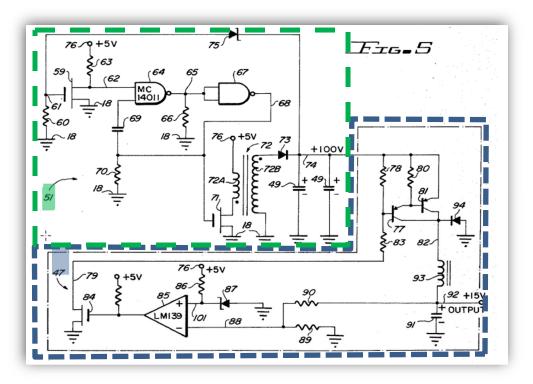

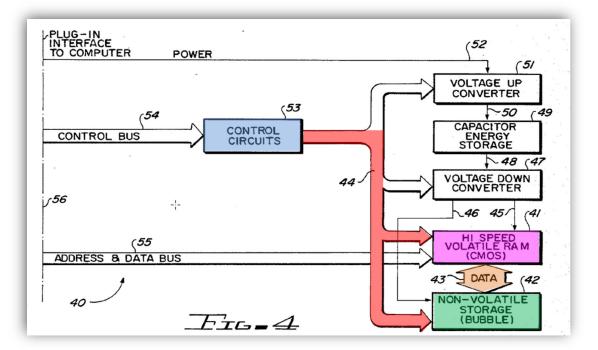

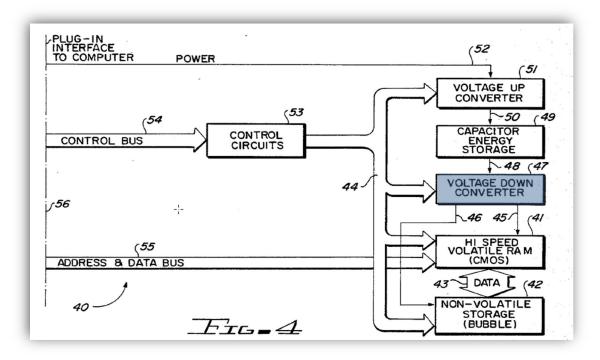

Bruder discloses a method and system for securely storing data when power is interrupted. This system includes volatile CMOS RAM and non-volatile "bubble memory." Ex-1005 at 7:52-60. While the volatile memory is used by the computer during normal operations, the entire contents of the volatile memory can be "rapidly transfer[red]" to the non-volatile memory upon a power failure. *Id.* The power needed to facilitate this data transfer is supplied by a bank of storage capacitors containing sufficient energy to allow the transfer of data from volatile to non-volatile memory. *Id.* at 7:60-66. Power from these capacitors is routed through a "voltage down converter," which maintains the proper operating voltage for each of the system's components. *Id.* at 8:2-10. Bruder also teaches that control circuitry directs the transfer of data from volatile to non-volatile memory. *Id.* at 8:37-45.

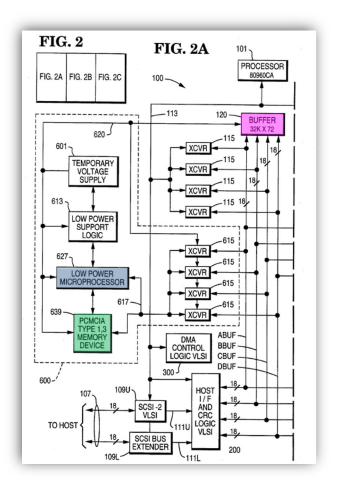

#### B. Weber Discloses a Transfer Memory Backup System To Safeguard Data When Power Is Lost

Weber discloses a "transfer memory backup system" for use with a computer data storage system. Ex-1006 at 3:51-57. This transfer memory backup system comprises volatile memory in the form of a transfer buffer, together with non-volatile PCMCIA flash card memory. *Id.* at Abstract; 3:38-43; 4:16-20; 5:13-20. The system also includes a low-power microprocessor, which controls data transfer from volatile to non-volatile memory in the event that external power is interrupted. *Id.* at 4:13-16; 6:65–7:8; 7:22-36. The system also comprises a temporary voltage source, which may include a "high capacitance gold capacitor," to power the transfer of data upon a power interruption. *Id.* at Abstract; 4:5-10; 6:65–7:8; 7:17-21.

#### C. Germer Discloses an Electronic Register That Preserves Data When Power Is Lost

Germer discloses an electronic register that preserves data upon a power

outage. Ex-1007 at 2:27-30. This system includes volatile random access memory and non-volatile memory, a processor, and capacitors to store power. *Id.* at Abstract; 5:39-57. In the event of a power outage, the capacitors provide energy—through a regulator that converts a high-voltage signal to a low-voltage regulated signal appropriate for the electronic components—to power the transfer of data from volatile to non-volatile memory. *Id.* at 5:64-6:10. Using this power, the processor directs and controls the transfer of data from volatile memory to non-volatile memory. *Id.* at 5:49-57.

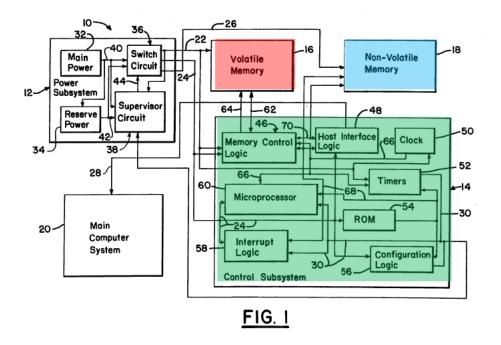

#### D. Horning Discloses A Data Protection System That Uses Reserve Power To Maintain Data in Volatile Memory

Horning describes an intelligent data protection system that includes a power subsystem for providing backup power to a volatile memory that is preferably a solid state disk drive (SSD). Ex-1008 at 5:51-60. The backup power is supplied by a power subsystem that includes a reserve power supply maintained at an energy level sufficient to power the data transfer process between the volatile memory and a non-volatile memory. *See id.* at 8:9-24; 9:5-27. A control subsystem manages backup power and the data transfer process. *See id.* at 9:20-27. After the data transfer process is completed, power is removed from the memory arrays and the data protection system is deactivated. *Id.* Horning describes the power supply and reserve power supply for the data protection system as having "sufficient capacity"

to power the control subsystem, non-volatile memory, and volatile memory, and can be any circuit "well known in the art" recognized as suitable by persons having ordinary skill in the art. *See id.* at 12:1-11.

#### E. Stokes Discloses a Super Capacitor-Based Backup Power System for a Nonvolatile Realtime Clock Calendar Module

Stokes discloses a "super capacitor" in the form of a "Double Layer Capacitor (DLC)" to maintain power to non-volatile memory in the event of power loss. Ex-1013 at 2:57-3:27. These super capacitors offer the advantage of reduced physical volume and cost per farad of capacitance. *Id.* at 3:7-10. Stokes explains that super capacitors are also quickly rechargeable, upon restoration of the primary power source. *See id.* at 4:28-32.

## X. THE CHALLENGED CLAIMS ARE UNPATENTABLE AND SHOULD BE CANCELLED

## A. Ground 1: Claims 1-3 Are Rendered Obvious by Horning in View of Stokes

Horning in view of Stokes teaches, and therefore renders obvious, claims 1-3 of the '939 patent. As explained in the attached declaration of Dr. R. Jacob Baker, Horning and Stokes are in the same field, teach analogous solutions to the same issues, and have the same purpose of improving a backup power supply for data preservation systems. Ex-1003, ¶¶ 116-122. Accordingly, a POSITA would have been motivated to incorporate Stokes' super-capacitors, which enable additional

power to be stored in a more compact form, into Horning's reserve power supply to provide the benefit of a more compact and efficient reserve power supply. *Id*.

This motivation is plain from the references themselves. Ex-1003, ¶¶ 117-118. Horning identifies the problems with the then-current state of battery size and rapid exhaustion, Ex-1008 at 2:13-25, and states that the reserve power supply may comprise "other energy storage devices" besides batteries, id. at 11:60-64. Horning further notes that "persons having ordinary skill in the art could easily provide a suitable . . . *reserve power supply* [] with sufficient capacity to power the control subsystem [], volatile memory array [], and non-volatile memory array [], depending on the configuration of the computer system." Id. at 12:1-9 (emphasis added). Similarly, Stokes not only teaches the drawbacks of batteries (similar to Horning), but also teaches the benefits of super-capacitors, noting their "significance" because they can be "packaged in one cubic inch, a two order of magnitude reduction in volume of prior technology," and used to "sustain" operation of electronic devices and memory during power outages. Ex-1013 at 3:7-15. The benefits provided by Stokes thus directly align with Horning's purpose. Accordingly, a POSITA would have been motivated to combine these references to leverage the benefits of Stokes' super-capacitors and avoid the drawbacks of batteries in Horning's data protection system. Ex-1003, ¶ 119.

A POSITA also would have had every expectation of success in incorporating

super-capacitors into Horning's data protection system, as Stokes demonstrates that super-capacitors were already well-known for use in reserve power systems for preserving data in volatile memory when external power is lost. Ex-1013 at 2:57-3:61; Ex-1003, ¶ 121. Likewise, given the smaller form factor but otherwise interchangeable capability of super-capacitors, a POSITA would have understood that no significant changes would have been required to use a super-capacitor in place of another type of reserve power supply. Ex-1003, ¶ 120.

As a result, it would have been obvious to a POSITA to combine Horning with Stokes to improve the functionality of the system. *See* Ex-1003, ¶ 118.

#### 1. Claim 1 Is Rendered Obvious by Horning in View of Stokes

a. [Claim 1 Pre]: "A method for controlling data in a computer system when the computer system loses power, the computer system comprising a computing engine, comprising the steps of:"

To the extent the preamble is limiting, Horning discloses this claim element through the disclosure of data protection systems and methods that use different levels of reserve power to preserve data in volatile memory in the event of a power failure. *See* Ex. 1008, Abstract ("The data protection system also includes data transfer apparatus to transfer data from the volatile memory into a non-volatile memory upon command from the control apparatus."); *id.* at 5:1-8 (describing a method of intelligent data protection).

In particular, Horning discloses a control subsystem (including a memory control logic, a host interface logic, and a microprocessor), a volatile memory, and a non-volatile memory. *Id.* at Figure 1; 5:51-6:60; Abstract. In the event of power loss, the control subsystem will transfer the data from the volatile memory array to the non-volatile memory array. *Id.* at 9:20-28. Horning's control subsystem is thus a "processor or similar structure for directing the transfer and storage of data in memory" under Petitioners' proposed construction. Ex-1003, ¶ 125.

Annotated Figure 1 of Horning, shown below, illustrates the control subsystem, volatile memory, and non-volatile memory.

*Id.*, ¶ 126.

b. [Claim 1a]: "activating a plurality of super capacitors to supply power to the computing engine based upon

#### power being removed from the computer system;"

Horning in view of Stokes renders this claim element obvious. Horning discloses a power subsystem that includes main power and reserve power components. Ex-1008, Figure 1; 6:9-37. Upon interruption of power to the main power supply component, the reserve power supply is connected to maintain power to the memory arrays and prevent data loss. *See id.* at 6:27-37; 8:25-33; Abstract. As a result, Horning discloses activating a reserve power to supply to supply power upon the main power being removed from the computer system. Ex-1003, ¶ 131.

Horning describes an embodiment in which the reserve power supply comprises batteries, *see, e.g., id.* at 13:16-25, but also states that "persons having ordinary skill in the art could easily provide a suitable main power supply [] and reserve power supply [] with sufficient capacity to power the control subsystem [], volatile memory array [], and non-volatile memory array [], depending on the configuration of the computer system." *Id.* at 12:1-9; 11:60-63 (stating that the reserve power supply may comprise "other energy storage devices"). Ex-1003, ¶ 129.

Stokes teaches a circuit module that utilizes a super-capacitor to maintain power to a nonvolatile memory in the event of power loss. *See* Ex-1013 at Abstract; 2:57-3:27. In particular, Stokes discloses a "super capacitor" in the form of a "Double Layer Capacitor (DLC)." *Id*. Stokes explains that super-capacitors offer the advantage of reduced physical volume and cost per farad of capacitance. *Id.* at 3:7-10. Super-capacitors are also quickly rechargeable upon restoration of the primary power source. *See id.* at 4:28-32. Stokes also discloses that multiple DLCs—i.e., a plurality of DLCs—can be used to power a nonvolatile memory. *See id.* at 3:15-24. Ex-1003, ¶ 130.

As explained above, it would have been obvious to a POSITA to combine Horning with Stokes, including using a plurality of super-capacitors as described by Stokes in the power subsystem of Horning in order to benefit from the stated advantages. *Supra* § X.A. Ex-1003, ¶ 116-122, 131.

### c. [Claim 1b]: "reconfiguring the data in the computing engine;"

Horning discloses that, in the event of prolonged external power loss, the data stored in the volatile memory array is transferred to the non-volatile memory array. Ex-1008 at Abstract; 7:19-23; 9:20-24; 11:9-17. This transfer of data from volatile to non-volatile memory is an example of "reconfiguring data" in the computing engine. Ex-1003, ¶¶ 132-133.

d. [Claim 1c]: "deactivating the plurality of super capacitors to cut off power to the computing engine based upon the plurality of super capacitors discharging to a predetermined level."

Horning in view of Stokes renders this claim element obvious. Horning describes user programmable power control sequences that can be tailored to accommodate a wide variety of capacities of reserve power supplies. *See* Ex-1008 at 7:60-8:8. Horning also discloses conserving reserve power by discharging the reserve power supply only to the point where there is enough energy to accomplish the data transfer task. *Id.* at 8:13-17. At that point, once all data has been transferred from volatile to non-volatile memory, Horning teaches that power is cut off to the computing engine by a circuit that "*removes power* from the primary, secondary, and tertiary power conductors 22, 24, and 26, respectively, thereby *deactivating the entire data protection system 10*."<sup>5</sup> *Id.* at 9:20-27 (emphasis added); 7:23-27. Horning thus teaches deactivating a reserve power supply to cut off power to the computing engine upon the reserve power system discharging to a predetermined level—i.e., a level where there is only enough energy left for the data transfer. Ex-1003, ¶¶ 134-137.

Annotated Figure 1 from Horning illustrates that conductors 22, 24, and 26 are the only lines that supply power to the control subsystem. Thus, when power is removed from conductors 22, 24, and 26, power is removed from the entire system.

<sup>&</sup>lt;sup>5</sup> The reserve power supply is part of, and thus is deactivated with, "data protection system 10." Ex-1008, Figure 1.

*Id.*, ¶ 135.

As discussed above, it would have been obvious to a POSITA to combine Horning and Stokes, and to include a plurality of super capacitors as taught by Stokes in the power subsystem of Horning. *Supra* § X.A.; Ex-1003, ¶¶ 116-122, 128-131. As a result, it also would have been obvious to discharge the super-capacitors to a predetermined level at which there is enough charge to complete the data transfer task, and then disconnect those super-capacitors upon completion of data transfer, as taught by Horning. Ex-1003, ¶ 136.

#### 2. Claim 2 Is Rendered Obvious by Horning in View of Stokes

a. [Claim 2 pre]: "The method of claim 1 wherein the computing engine comprises a least one volatile memory and at least one non-volatile memory."

26

Horning in view of Stokes renders obvious the method of claim 1 for the reasons discussed above. *Supra* § X.A.1. Horning and Stokes also render obvious the method of claim 2, as Horning discloses that the computing engine comprises both a volatile memory and non-volatile memory. *See supra* §§ X.A.1.a., X.A.1.c; Ex-1003, ¶¶ 124-127, 132-133.

#### 3. Claim 3 Is Rendered Obvious by Horning in View of Stokes

a. [Claim 3]: "The method of claim 2 wherein the reconfiguring step (b) further comprises: (b1) allowing all data to be transferred from the at least one volatile memory to the at least one non-volatile memory."

Horning in view of Stokes renders obvious the method of claim 2 for the reasons discussed above, *supra* § X.A.2, and also render obvious the method of claim 3.

Horning discloses that the data transfer task allows for all the data from the volatile memory array to be transferred to the non-volatile memory array. Ex-1008 at 7:30-34. Horning further confirms that the power is not removed from the data protection system until after "*all the data* [has] been transferred." *Id.* at 9:23-27 (emphasis added); Ex-1003, ¶¶ 142-144.

# **B.** Ground 2: Claims 1-3 Are Rendered Obvious by Germer in View of Horning Further in View of Stokes

Germer in view of Horning further in view of Stokes teaches, and therefore

renders obvious, claims 1-3 of the '939 patent. As Dr. Baker explains, a POSITA would have been motivated to combine the power supply and power monitor for the electric meter disclosed in Germer with the intelligent data protection system disclosed in Horning. Ex-1003, ¶¶ 145-151. A POSITA also would have been motivated to combine Horning's functionality for deactivating a reserve power supply to cut off power, with Germer's data protection system, to provide optimal utilization and management of Germer's reserve power supply. *Id.* Furthermore, a POSITA would have been motivated to combine the super capacitors described by Stokes into the combination of Germer and Horning in order to provide low cost-per-farad of capacitance with a reduced physical volume that is also quickly rechargeable. *Id.*, ¶¶ 145, 149, 150.

Germer and Horning are in the same field, teach analogous solutions to the same issues, and have the same purpose of improving data protection and preservation systems. Ex-1003, ¶ 148. Thus, a POSITA would have been motivated to combine these references, which is apparent from the reference themselves. *Id.* Germer teaches that, once reserve power has dropped below the level where the processor can properly function, a reset signal is produced and a switching transistor "*cut off*" is maintained. Ex-1007 at 6:25-31; 9:3-6; claim 1; Ex-1003, ¶ 148. Likewise, Horning teaches that power is cut off to the computing engine by a circuit that "*removes power* from the primary, secondary, and tertiary power conductors 22,

24, and 26, respectively, thereby *deactivating the entire data protection system 10.*" Ex-1007 at 9:20-27 (emphasis added); 7:23-27. Accordingly, the power optimization benefits taught by Horning directly align with Germer's purpose. As a result, a POSITA would have been motivated to combine Germer's data protection system with Horning's teaching of deactivating and cutting off power from a reserve power system, as this would have allowed Germer's data protection system to leverage the benefits of Horning's power optimization and utilization scheme. Ex-1003, ¶ 148.

A POSITA also would have had an expectation of success in incorporating Horning's functionality for deactivating the reserve power supply to cut off power into Germer's data protection system. Ex-1003, ¶ 150. As Germer teaches, a processor would need to be reset once power falls below a predetermined level, and Horning demonstrates the benefits of deactivating a capacitor to cut off power at such a level. *Id.*, ¶ 149. Accordingly, a POSITA would have understood that incorporating Horning's teaching of deactivation into Germer's data preservation system would have been straightforward and yielded expected results. *Id.* Similarly, A POSITA would have understood that substituting a plurality of Stokes' super capacitors into the combination of Germer and Horning would be a simple substitution and yield the expected results of higher capacitance at a reduced physical volume. *Id.*

- 1. Claim 1 Is Rendered Obvious by Germer in View of Horning Further in View of Stokes

- a. [Claim 1 Pre]: "A method for controlling data in a computer system when the computer system loses power, the computer system comprising a computing engine, comprising the steps of:"

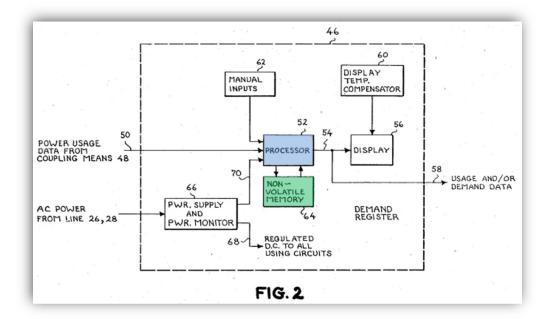

To the extent the preamble is limiting, Germer discloses this claim element. Germer is directed to an electronic register that saves data when a computer system loses power, together with methods for using the same. Ex-1007 at 2:18-4; 2:66-3:16; claim 15. In particular, Germer discloses a computing engine that comprises a processor, which contains volatile random access memory, and non-volatile memory. Id. at Abstract; 2:55-60; 3:7-13; 5:6-9; 5:12-15; 5:64-6:3. In the event of a power outage, the processor controls the transfer of data from the volatile memory to the non-volatile memory. Id. at 5:50-57. Germer's processor is thus a "processor or similar structure for directing the transfer and storage of data in memory" under Petitioners' proposed construction. Ex-1003, ¶ 153. As a result, Germer discloses "a processor or similar structure for directing the transfer and storage of data in memory, volatile memory, and non-volatile memory" pursuant to Petitioner's construction. Id.

Annotated Figure 2 of Germer, shown below, illustrates Germer's **processor**, which comprises volatile memory, as well as **non-volatile memory**:

*Id.*, ¶ 154.

#### b. [Claim 1a]: "activating a plurality of super capacitors to supply power to the computing engine based upon power being removed from the computer system;"

Germer renders this claim element obvious in view of Stokes. Germer discloses an "unregulated supply and emergency storage" component, which comprises a capacitor for storing power. Ex-1007 at Abstract; 2:30-34; 7:41-55. Germer further claims an electronic register that "includes a capacitor having a capacitance." *Id.* at claim 3. The use of the indefinite article "a" in a patent claim means "one or more."<sup>6</sup> As a result, by claiming "a capacitor," Germer discloses

<sup>&</sup>lt;sup>6</sup> *KCJ Corp. V. Kinetic Concepts, Inc.*, 223 F.3d 1351, 1356 (Fed. Cir. 2000) ("This court has repeatedly emphasized that an indefinite article 'a' or 'an' in patent

"one or more"—i.e., a plurality—of capacitors. Ex-1003, ¶ 156.

Germer also discloses that, in the event of a power outage, the capacitor is activated to "maintain power to critical circuits" for long enough "to permit transfer of billing data and programmed constants from the volatile random access memory . . . to safe storage in non-volatile memory." *Id.* at 5:64-6:3; 6:18-31. Germer thus teaches activating the capacitors to supply power to the computing engine based upon power being removed from the computer system. Ex-1003, ¶ 157.

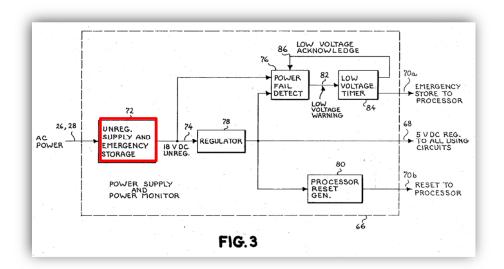

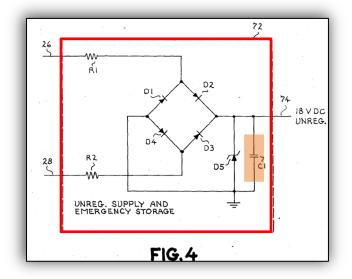

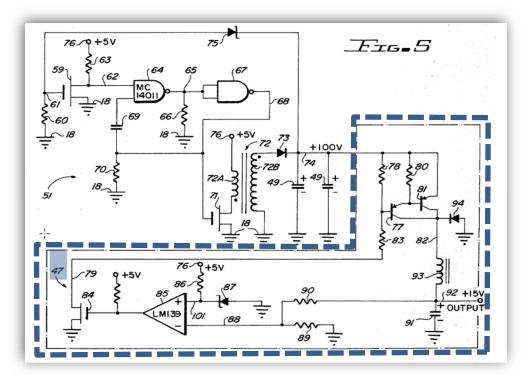

A diagram illustrating the unregulated supply and emergency storage structure is provided in annotated Figure 3, below:

A more detailed diagram of the unregulated supply and emergency storage

parlance carries the meaning of 'one or more' in open-ended claims containing the transitional phrase 'comprising.'").

component, illustrating a capacitor, is shown in annotated Figure 4, below:

Ex-1003, ¶¶ 158-159.

Although Germer does not refer to the capacitors as "super capacitors," use of super-capacitors in Germer's invention would have been obvious in view of Stokes. Ex-1003, ¶ 160.<sup>7</sup> As discussed above, super-capacitors would have been well-known to a POSITA at the time that that '939 patent was filed, and were also known to provide more capacitance in a smaller form factor. *Supra* § IX.E; Ex-1003,

<sup>&</sup>lt;sup>7</sup> The '939 patent does not define what a super-capacitor, nor does it differentiate a super-capacitor from a "capacitor." Instead, the specification, simply states that "with the advent of low cost super-capacitors available in values of over 10 Farads, large amounts of energy can be affordably stored in a very small space." Ex-1001 at 3:7-10.

¶¶ 114-115, 160. Moreover, as also discussed above, a POSITA would have known that super-capacitors could be used electronic systems and circuits. Ex-1003, ¶¶ 114-115, 160. Thus, using Stokes' "super-capacitor" in place of a "capacitor" would have been obvious to a POSITA, particularly in view of Stokes' teachings and given Germer's disclosure that the capacitors need to have sufficient capacity to power the computing engine, and ensure the complete transfer of data to non-volatile memory, in the event of power loss. *See, e.g.*, IX.E *supra* (discussing characteristics of super capacitors); Ex-1003, ¶¶ 114-115, 160.

### c. [Claim 1b]: "reconfiguring the data in the computing engine;"

Germer discloses that data in the computing engine is reconfigured by transferring the data "from the volatile random access memory in processor 52 to safe storage in non-volatile memory 64" upon a power interruption. Ex-1008 at 5:64-6:3; 5:49-57; 2:59-62; Claim 15; Ex-1003, ¶ 162.

d. [Claim 1c]: "deactivating the plurality of super capacitors to cut off power to the computing engine based upon the plurality of super capacitors discharging to a predetermined level."

Germer in view of Horning further in view of Stokes renders this claim element obvious. Germer discloses a number of thresholds, including a specific threshold (e.g., a "third threshold") at which the processor "is no longer able to reliably maintain its operating conditions" and a reset signal is generated. Ex-1007 at 6:25-31. Germer explains that when the regulated voltage 68 (i.e., the output of regulator circuit seen in Fig. 5) powering the processor decreases "from its nominal value of 5 volts to a threshold value of about 3.9 volts," a reset to processor signal is generated. *Id.* at 9:9-13; Ex-1003, ¶ 164.

Horning also discloses a system and method of data protection that includes discharging a reserve power supply to a predetermined level at which it can supply enough power to the computing engine so that it can transfer all the data from the volatile memory array to the non-volatile memory array. *Supra* § X.A.1; Ex-1008 at 8:13-17. Horning teaches that cutting off power from the reserve power supply at that level allows the user to obtain "optimum utilization of the reserve power supply regardless of the capacity of the reserve power supply." *Id.* at 8:6-8; 8:19-24. Horning also discloses that, after all data has been transferred from volatile to non-volatile memory, power is cut off to the computing engine by a circuit that "*removes power* from the primary, secondary, and tertiary power conductors . . . thereby *deactivating the entire data protection system 10*."<sup>8</sup> *Id.* at 9:20-27 (emphasis added); Ex-1003, ¶ 165.

As discussed above, it would have been obvious to a POSITA to include the

<sup>&</sup>lt;sup>8</sup> The reserve power supply is part of, and thus is deactivated with, "data protection system 10." Ex-1008, Figure 1.

teachings of Horning, including Horning's functionality for deactivating the reserve power system, in the system and method of Germer in order to achieve the stated optimum utilization of the reserve power capacitor. *Supra* § X.B.1.b; Ex-1003, ¶¶ 164-165. As discussed above, it would have been obvious to a POSITA to replace Germer's capacitors with Stokes' super capacitors in order to supply sufficient reserve power from a reduced physical volume. *See supra* § X.B.1.b; Ex-1003, ¶¶ 164-165.

#### 2. Claim 2 Is Rendered Obvious by Germer in View of Horning Further in View of Stokes

# a. [Claim 2 pre]: "The method of claim 1 wherein the computing engine comprises a least one volatile memory and at least one non-volatile memory."

Germer in view of Horning further in view of Stokes renders obvious the method of claim 1 for the reasons discussed above. *Supra* § X.B.1. Germer and Horning in view of Stokes also render obvious the method of claim 2, as Germer discloses that the computing engine comprises both a volatile memory and non-volatile memory. *See supra* §§ X.B.1.a, X.B.1.c; Ex-1003, ¶¶ 167-169.

#### 3. Claim 3 Is Rendered Obvious by Germer in View of Horning Further in View of Stokes

a. [Claim 3]: "The method of claim 2 wherein the reconfiguring step (b) further comprises: (b1) allowing all data to be transferred from the at least one volatile memory to the at least one non-volatile memory."

Germer in view of Horning further in view of Stokes renders obvious the method of claim 2 for the reasons discussed above, *supra* § X.B.2, and also renders obvious the method of claim 3.

Germer discloses that data in the computing engine is reconfigured by transferring the data "from the volatile random access memory in processor 52 to safe storage in non-volatile memory 64." Ex-1007 at 5:64-6:3; 5:49-57; 2:59-62. Germer further confirms that the power thresholds for deactivation of the capacitors are set to ensure "that *all data* is safely stored in non-volatile memory." *Id.* at 6:28-31 (emphasis added); Ex-1003, ¶¶ 172-173.

#### C. Ground 3: Each of the Challenged Claims Is Rendered Obvious by Bruder in View of Horning Further in View of Stokes

Bruder in view of Horning further in view of Stokes teaches, and therefore makes obvious, claims 1-3, 6, 10-12, and 15 of the '939 patent. As Dr. Baker explains, a POSITA would have been motivated to combine Horning's functionality for deactivating a reserve power supply to cut off power with Bruder's data protection system to provide optimal utilization and management of Bruder's reserve power supply. Ex-1003, ¶¶ 174-180.

Bruder and Horning are in the same field, teach analogous solutions to the same issues, and have the purpose of improving data protection and preservation systems. Ex-1003, ¶ 175-177. Thus, a POSITA would have been motivated to

37

combine these references. Id. Bruder teaches that reserve power from capacitors should only be supplied for "long enough to allow this transfer of data [from volatile to non-volatile memory] to be accomplished." Ex-1005 at 7:64-66; Ex-1003, ¶ 175-177. Likewise, Horning teaches optimizing power utilization in a reserve power system using a circuit that "removes power from the primary, secondary, and tertiary power conductors ... thereby *deactivating the entire data protection system* 10." Ex-1008 at 9:20-27 (emphasis added); 7:23-27. As a result, a POSITA would have been motivated to combine Bruder's data protection system with Horning's teaching of deactivating and cutting off power from a reserve power system because this would have allowed Bruder's data protection system to leverage the benefits of Horning's power optimization and utilization scheme. Ex-1003, ¶¶ 176-177. Furthermore, a POSITA would have been motivated to combine the super capacitors described by Stokes into the combination of Bruder and Horning in order to provide low cost-per-farad of capacitance with a reduced physical volume that is also quickly rechargeable. Ex-1003, ¶ 177.

A POSITA also would have had an expectation of success in incorporating Horning's functionality for deactivating the reserve power supply to cut off power into Bruder's data preservation system. Ex-1003, ¶ 179. As Bruder teaches, power should only be supplied temporarily to ensure that data is transferred to non-volatile memory, and Horning demonstrates the benefits of deactivating a capacitor to cut

off power at that same level. *Id.* Accordingly, a POSITA would have understood that incorporating Horning's teaching of deactivation into Bruder's data preservation system would have been straightforward and yielded expected results. *Id.* Likewise, a POSITA would have understood that substituting a plurality of Stokes' super capacitors into the combination of Germer and Horning would be a simple substitution and yield the expected results of higher capacitance at a reduced physical volume. *Id.*, ¶ 178.

#### 1. Claim 1 Is Rendered Obvious by Bruder in View of Horning Further in View of Stokes

a. [Claim 1 Pre]: "A method for controlling data in a computer system when the computer system loses power, the computer system comprising a computing engine, comprising the steps of:"

To the extent the preamble is limiting, Bruder teaches this claim element. Bruder is directed to systems and methods for retaining data in a computer system when external power is interrupted. Ex-1005 at 1:8-13; Abstract. Bruder discloses a computing engine that comprises both volatile memory (e.g., CMOS RAM) and non-volatile memory (e.g., bubble memory). *Id.* at Abstract; 2:32-42; 7:52-60; Fig. 4. Bruder also teaches control circuits, which control "data transfer between CMOS Ram 41 and bubble memory 42 during a power interruption." *Id.* at 8:37-45. The "control circuits" comprise a "processor or similar structure for directing the transfer and storage of data in memory" under the Petitioners' proposed construction of

computing engine. Ex-1003, ¶ 182.

Bruder's **control circuits**, **volatile memory**, and **nonvolatile memory**, which comprise the claimed "computing engine," are illustrated in annotated Figure 4, below:

*Id.*, ¶ 183.

#### b. [Claim 1a]: "activating a plurality of super capacitors to supply power to the computing engine based upon power being removed from the computer system;"

Bruder renders this claim element obvious in view of Stokes. Bruder discloses a capacitor bank (i.e., a "plurality of capacitors") that stores and "supplies enough energy to maintain the voltage supply lines" to the memory and other circuitry when external power is interrupted. Ex-1005 at 7:60-66; Abstract; 2:35-38; 8:2-7; Fig. 4;

Ex-1003, ¶ 185.

Bruder also teaches activating the capacitors when external power is removed from the computer system. Bruder states that, when external power to the computing system is interrupted, "low power control circuitry actuates a voltage down converter circuit that produces a regulated output voltage" from the capacitor bank "to temporarily power the control circuitry." *Id.* at Abstract; 8:2-10; 2:35-38; Ex-1003, ¶ 186.

The **capacitor bank** is illustrated in annotated Figure 4, below.