# UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

KIOXIA AMERICA, INC and KIOXIA CORPORATION,

Petitioners,

v.

BiTMICRO LLC,

Patent Owner.

Case No.: IPR2023-00741 U.S. Patent No. 9,135,190

\_\_\_\_\_

# PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 9,135,190

# **TABLE OF CONTENTS**

| I.    | INTRODUCTION1                                                                                              |                                                                                   |  |

|-------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

| II.   | GROUNDS FOR STANDING1                                                                                      |                                                                                   |  |

| III.  | FEES1                                                                                                      |                                                                                   |  |

| IV.   | PRECISE RELIEF REQUESTED1                                                                                  |                                                                                   |  |

|       | A.                                                                                                         | Prior Art2                                                                        |  |

|       |                                                                                                            | 1. Cornwell2                                                                      |  |

|       |                                                                                                            | 2. Ware                                                                           |  |

|       | B.                                                                                                         | IPR Grounds                                                                       |  |

| V.    | THE                                                                                                        | '190 PATENT                                                                       |  |

|       | A.                                                                                                         | Overview of the '190 Patent                                                       |  |

|       | B.                                                                                                         | Prosecution History of the '190 Patent                                            |  |

| VI.   | LEVE                                                                                                       | EL OF ORDINARY SKILL IN THE ART4                                                  |  |

| VII.  | CLAIM CONSTRUCTION                                                                                         |                                                                                   |  |

|       | A.                                                                                                         | Claim 45: "means for performing a memory transaction"                             |  |

|       | В.                                                                                                         | Claim 45: "interface controller means for processing memory transaction requests" |  |

|       | C.                                                                                                         | Claim 45: "means for addressing a first memory location"7                         |  |

| VIII. | OVE                                                                                                        | RVIEW OF THE PRIOR ART9                                                           |  |

|       | A.                                                                                                         | Cornwell                                                                          |  |

|       | B.                                                                                                         | Ware11                                                                            |  |

| IX.   |                                                                                                            | CHALLENGED CLAIMS ARE UNPATENTABLE AND<br>ULD BE CANCELLED13                      |  |

|       | A. Ground 1: Each of the Challenged Claims is Rendered Obvious by Cornwell in View of a POSITA's Knowledge |                                                                                   |  |

|       |                                                                                                            | 1. Claim 1 is Obvious in View of Cornwell and a POSITA's Knowledge                |  |

|       |                                                                                                            | 2. Claim 5 is Obvious in View of Cornwell and a POSITA's                          |  |

|    |     | Knowledge                                                                                      | 28 |

|----|-----|------------------------------------------------------------------------------------------------|----|

|    | 3.  | Claim 6 is Obvious in View of Cornwell and a POSITA's Knowledge                                | 28 |

|    | 4.  | Claim 29 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 28 |

|    | 5.  | Claim 36                                                                                       | 30 |

|    | 6.  | Claim 37                                                                                       | 30 |

|    | 7.  | Claim 45 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 30 |

|    | 8.  | Claim 51 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 39 |

|    | 9.  | Claim 52 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 39 |

|    | 10. | Claim 59 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 39 |

|    | 11. | Claim 71 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 45 |

|    | 12. | Claim 76 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 45 |

|    | 13. | Claim 80 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 45 |

|    | 14. | Claim 84 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 51 |

|    | 15. | Claim 85 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 51 |

|    | 16. | Claim 98 is Obvious in View of Cornwell and a POSITA's Knowledge                               | 51 |

| В. |     | nd 2: Each of the Challenged Claims is Rendered Obvious<br>are in View of a POSITA's Knowledge | 53 |

|    | 1.  | Claim 1 is Obvious in View of Ware and a POSITA's Knowledge                                    | 53 |

|    | 2.  | Claim 5 is Obvious in View of Ware and a POSITA's                                              |    |

X.

|      |       | Knowledge74                                                         |

|------|-------|---------------------------------------------------------------------|

|      | 3.    | Claim 6 is Obvious in View of Ware and a POSITA's<br>Knowledge      |

|      | 4.    | Claim 29 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 5.    | Claim 36 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 6.    | Claim 37 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 7.    | Claim 45 is Obvious in View of Cornwell and a<br>POSITA's Knowledge |

|      | 8.    | Claim 51 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 9.    | Claim 52 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 10.   | Claim 59 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 11.   | Claim 71 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 12.   | Claim 76 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 13.   | Claim 80 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 14.   | Claim 84 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 15.   | Claim 85 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

|      | 16.   | Claim 98 is Obvious in View of Ware and a POSITA's<br>Knowledge     |

| INST | ITUTI | ON SHOULD NOT BE DISCRETIONARILY DENIED101                          |

| A.   |       | Coard Should Not Exercise Its Discretion Under 35 U.S.C.<br>(a)101  |

|      | B.  | The Board Should Not Exercise Its Discretion under 35 U.S.C. |     |

|------|-----|--------------------------------------------------------------|-----|

|      |     | § 325(d)                                                     | 101 |

| XI.  | MAN | DATORY NOTICES                                               | 102 |

|      | A.  | Real Parties in Interest—37 C.F.R. § 42.8(b)(1)              | 102 |

|      | B.  | Related Matters—37 C.F.R. § 42.8(b)(2)                       | 103 |

|      | C.  | Lead and Back-Up Counsel—37 C.F.R. § 42.8(b)(3)              | 103 |

|      | D.  | Service Information—37 C.F.R. § 42.8(b)(4)                   | 104 |

| XII. | CON | CLUSION                                                      | 104 |

# **TABLE OF AUTHORITIES**

| Pa                                                                                                                           | age(s) |

|------------------------------------------------------------------------------------------------------------------------------|--------|

| Cases                                                                                                                        |        |

| Advanced Bionics, LLC v. MED-EL Elektromedizinische Geräte<br>GmbH,                                                          | 100    |

| IPR2019-01469, Paper 6 (PTAB Feb. 13, 2020)                                                                                  | 102    |

| BiTMICRO LLC v. Intel Corp.,<br>Case No. 5:23-cv-00625 (N.D. Cal.)                                                           | 103    |

| <i>BiTMICRO LLC v. KIOXIA Am. Inc., et al.,</i><br>Case NO. 6:22-cv-00331 (W.D. Tex. 2022)                                   | 103    |

| Certain Solid State Storage Drives, Stacked Electronics Components,<br>and Products Containing Same,<br>Inv. No. 337-TA-1097 | 103    |

| Nidec Motor Corp. v. Zhongshan Broad Ocean Motor Co.,<br>868 F.3d 1013 (Fed. Cir. 2017)                                      | 5      |

| Phillips v. AWH Corp.,<br>415 F.3d 1303 (Fed. Cir. 2005)                                                                     | 5      |

| Samsung Semiconductor, Inc. et al v. BiTMICRO, LLC et al.,<br>Case No. 3:18-cv-03502 (N.D. Cal.)                             | 103    |

| SK Hynix Inc., et al. v. BiTMICRO, LLC,<br>Case No. 3:18-cv-03505 (N.D. Cal.)                                                | 103    |

| Sotera Wireless, Inc., v. Masimo Corp.<br>IPR2020-01019, Paper 12 (PTAB Dec. 1, 2020)                                        | 101    |

| Target Corp. v. Proxicom Wireless, LLC,<br>IPR2020-00904, Paper 11 (PTAB Nov. 10, 2020)                                      | 6      |

| <i>The Data Co. Techs., Inc. v. Bright Data Ltd.,</i><br>IPR2022-00135, Paper 12 (PTAB June 1, 2022)                         | 100    |

|                                                                                                                              | 2, 102 |

| Vestern Digital Corp. v. Spex Techs., Inc.,<br>IPR2018-00084, Paper 14 (PTAB April 25, 2018)6 | 5 |

|-----------------------------------------------------------------------------------------------|---|

| <i>Villiamson v. Citrix Online, LLC,</i><br>792 F.3d 1339 (Fed. Cir. 2015)5, 8                | 3 |

| tatutes                                                                                       |   |

| 5 U.S.C. § 102(b)                                                                             | 2 |

| 5 U.S.C. § 103(a)                                                                             | 2 |

| 5 U.S.C. § 112                                                                                | 5 |

| 5 U.S.C. § 311                                                                                | 1 |

| 5 U.S.C. § 311(c)                                                                             | 1 |

| 5 U.S.C. § 314(a)101                                                                          | 1 |

| 5 U.S.C. § 325(d)                                                                             | 1 |

| Regulations                                                                                   |   |

| 7 C.F.R. § 42.8(b)(1)102                                                                      | 2 |

| 7 C.F.R. § 42.8(b)(2)103                                                                      | 3 |

| 7 C.F.R. § 42.8(b)(3)103                                                                      | 3 |

| 7 C.F.R. § 42.8(b)(4)104                                                                      | 1 |

| 7 C.F.R. § 42.15(a)                                                                           | 1 |

| 7 C.F.R. § 42.100(b)                                                                          | 5 |

| 7 C.F.R. § 104(b)(3)                                                                          | 5 |

# LIST OF EXHIBITS

| Ex. No. | Description                                                                                                                                                                     |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1001    | U.S. Patent No. 9,135,190                                                                                                                                                       |

| 1002    | Excerpts of the File History for U.S. Patent No. 9,135,190                                                                                                                      |

| 1003    | Declaration of Dr. R. Jacob Baker                                                                                                                                               |

| 1004    | Curriculum Vitae of Dr. R. Jacob Baker                                                                                                                                          |

| 1005    | U.S. App. Pub. No. 2007/0180186 ("Cornwell")                                                                                                                                    |

| 1006    | U.S. Patent No. 7,269,708 ("Ware")                                                                                                                                              |

| 1007    | Claim Construction Order and Memorandum in Support Thereof,<br><i>BiTMICRO LLC v. KIOXIA Am., Inc.</i> , Case No. 6:22-cv-00331-<br>ADA, Dkt. No. 54 (W.D. Tex. Feb. 16, 2023). |

| 1008    | Reserved                                                                                                                                                                        |

| 1009    | Reserved                                                                                                                                                                        |

| 1010    | U.S. Patent App. Pub. No. 2005/0108500 ("Kishida")                                                                                                                              |

| 1011    | Brent Keeth et al., DRAM Circuit Design (Mohamed E. El-Hawary<br>et al. Eds., IEEE Press 2008) ("Keeth")                                                                        |

| 1012    | Declaration of Ms. Sylvia Hall-Ellis regarding Public Accessibility<br>of Keeth                                                                                                 |

| Claim element | Claim 1                                                                                                                                                                                                                                                                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Claim 1Pre]  | A method of performing transactions on a set of memory<br>locations that includes a first memory location and a second<br>memory location, the method comprising:                                                                                                          |

| [Claim 1a]    | performing a memory transaction comprising addressing a first memory location in a first memory device in a memory store,                                                                                                                                                  |

| [Claim 1b]    | said first memory location and a second memory location<br>respectively associated with a first device profile and a<br>second device profile,                                                                                                                             |

| [Claim 1c]    | wherein said second memory location is in a second memory device in the memory store,                                                                                                                                                                                      |

| [Claim 1d]    | wherein a memory read transaction or a memory write<br>transaction is performed on at least one of the first memory<br>location or second memory location,                                                                                                                 |

| [Claim 1e]    | wherein data is transferred to the first memory location or<br>second memory location from a host for a memory write<br>transaction, wherein data is transferred from the first<br>memory location or second memory location to the host for a<br>memory read transaction; |

| [Claim 1f]    | wherein said first device profile is optimal for a data type<br>subject to the memory transaction, wherein said data type<br>comprises one of a random data type or a sequential data<br>type;                                                                             |

| [Claim 1g]    | said performing the memory transaction further comprising<br>identifying command details for causing the memory<br>transaction to be performed, wherein said command details<br>comprising the first memory device;                                                        |

| [Claim 1h]    | said first device profile representing a first set of attributes of<br>said first memory location, and said second device profile<br>representing a second set of attributes of said second<br>memory location, and a difference exists between said first                 |

# Challenged Claims of U.S. Patent No. 9,135,190

|               | and second device profiles;                                                                                                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Claim 1i]    | after identifying the command details, obtaining the first set of attributes;                                                                                                                                                                                                      |

| [Claim 1j]    | wherein each attribute in the first set of attributes and second<br>set of attributes is associated with a respective attribute<br>qualifier that qualifies a respective memory location;                                                                                          |

| [Claim 1k]    | wherein the memory store is directly coupled to at least one<br>memory bus and wherein the at least one memory bus is<br>directly coupled to a controller, and wherein the controller<br>performs the memory read transaction and memory write<br>transaction on the memory store; |

| [Claim 11]    | wherein the host is directly coupled to the controller by a communication path as the controller performs the memory read transaction or memory write transaction;                                                                                                                 |

| [Claim 1m]    | wherein the first device profile and second device profile are<br>each stored in the memory store;                                                                                                                                                                                 |

| [Claim 1n]    | and using attributes from said first and second device profiles; and                                                                                                                                                                                                               |

| [Claim 10]    | selecting a transfer size for the memory transaction, wherein<br>the transfer size is a function of a data size of the memory<br>transaction and the first set of attributes.                                                                                                      |

| Claim element | Claim 5                                                                                                                                                                                                                                                                            |

| [Claim 5]     | The method of claim 1, wherein said difference includes<br>different attribute qualifiers for at least one set of shared<br>attributes from said first and second device profiles.                                                                                                 |

| Claim element | Claim 6                                                                                                                                                                                                                                                                            |

| [Claim 6]     | The method of claim 5, wherein said different attribute qualifiers include different attribute values.                                                                                                                                                                             |

| Claim element | Claim 29                                                                                                                                                                                                                                                                           |

| [Claim 29Pre] | A non-transitory computer readable medium comprising<br>computer executable instructions adapted to cause a method<br>of performing memory transactions on a first memory<br>location and a second memory location, said method                                                    |

|               | comprising:                                                                                                                                                                                                                                                                               |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Claim 29a]   | performing a memory transaction comprising addressing a<br>first memory location, said first memory location and a<br>second memory location are respectively associated with a<br>first device profile and a second device profile;                                                      |

| [Claim 29b]   | wherein said first device profile is optimal for a data type<br>subject to the memory transaction, wherein said data type<br>comprises one of a random data type or a sequential data<br>type;                                                                                            |

| [Claim 29c]   | said performing the memory transaction further comprising<br>identifying command details for causing the memory<br>transaction to be performed, wherein said command details<br>comprising the first memory device;                                                                       |

| [Claim 29d]   | said first device profile representing a first set of attributes of<br>said first memory location, and said second device profile<br>representing a second set of attributes of said second<br>memory location, and a difference exists between said first<br>and second device profiles; |

| [Claim 29e]   | after identifying the command details, obtaining the first set of attributes;                                                                                                                                                                                                             |

| [Claim 29f]   | and using attributes from said first and second device profiles; and                                                                                                                                                                                                                      |

| [Claim 29g]   | selecting a transfer size for the memory transaction, wherein<br>the transfer size is a function of a data size of the memory<br>transaction and the first set of attributes.                                                                                                             |

| Claim element | Claim 36                                                                                                                                                                                                                                                                                  |

| [Claim 36]    | The computer readable medium of claim 29, wherein said<br>difference includes different attribute qualifiers for at least<br>one set of shared attributes from said first and second device<br>profiles.                                                                                  |

| Claim element | Claim 37                                                                                                                                                                                                                                                                                  |

| [Claim 37]    | The computer readable medium of claim 36, wherein said different attribute qualifiers include different attribute values.                                                                                                                                                                 |

| Claim element | Claim 45                                                                                                                                                                                                                                                                                  |

| [Claim 45Pre] | A memory controller for performing memory transactions, said memory controller comprising:                                                                                                                                                                                                |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Claim 45a]   | means for performing a memory transaction comprising a<br>means for addressing a first memory location, said first<br>memory location and a second memory location are<br>respectively associated with a first device profile and a<br>second device profile;                             |

| [Claim 45b]   | said means for addressing is directly coupled to the first<br>memory location and second memory location;                                                                                                                                                                                 |

| [Claim 45c]   | wherein said means for addressing includes an interface<br>controller means for processing memory transaction<br>requests;                                                                                                                                                                |

| [Claim 45d]   | said means for addressing is directly coupled to a host as said<br>means for addressing addresses the first memory location or<br>second memory location;                                                                                                                                 |

| [Claim 45e]   | wherein said first device profile is optimal for a data type<br>subject to the memory transaction, wherein said data type<br>comprises one of a random data type or a sequential data<br>type;                                                                                            |

| [Claim 45f]   | said performing the memory transaction further comprising<br>identifying command details for causing the memory<br>transaction to be performed, wherein said command details<br>comprising the first memory device;                                                                       |

| [Claim 45g]   | said first device profile representing a first set of attributes of<br>said first memory location, and said second device profile<br>representing a second set of attributes of said second<br>memory location, and a difference exists between said first<br>and second device profiles; |

| [Claim 45h]   | said means for addressing obtains the first set of attributes<br>after identifying the command details;                                                                                                                                                                                   |

| [Claim 45i]   | and said means for addressing uses attributes from said first<br>and second device profiles and selects a transfer size for the<br>memory transaction, wherein the transfer size is a function of<br>a data size of the memory transaction and the first set of<br>attributes.            |

| Claim element | Claim 51                                                                                                                                                                                                                                                                            |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Claim 51]    | The memory controller of claim 45, wherein said difference includes different attribute qualifiers for at least one set of shared attributes from said first and second device profiles.                                                                                            |

| Claim element | Claim 52                                                                                                                                                                                                                                                                            |

| [Claim 52]    | The memory controller of claim 51, wherein said different attribute qualifiers include different attribute values.                                                                                                                                                                  |

| Claim element | Claim 59                                                                                                                                                                                                                                                                            |

| [Claim 59Pre] | A memory controller comprising:                                                                                                                                                                                                                                                     |

| [Claim 59a]   | an interface controller coupled to a memory device interface<br>and an input/output (IO) device interface;                                                                                                                                                                          |

| [Claim 59b]   | a memory store;                                                                                                                                                                                                                                                                     |

| [Claim 59c]   | wherein the memory device interface is directly coupled to the memory store;                                                                                                                                                                                                        |

| [Claim 59d]   | said interface controller disposed to perform a memory<br>transaction by addressing a first memory location in the<br>memory store,                                                                                                                                                 |

| [Claim 59e]   | said first memory location and a second memory location<br>respectively associated with a first device profile and a<br>second device profile;                                                                                                                                      |

| [Claim 59f]   | wherein said first device profile is optimal for a data type<br>subject to the memory transaction, wherein said data type<br>comprises one of a random data type or a sequential data<br>type;                                                                                      |

| [Claim 59g]   | said interface controller identifies command details for<br>causing the memory transaction to be performed, wherein<br>said command details comprising the first memory device;                                                                                                     |

| [Claim 59h]   | said device profile representing a first set of attributes of said<br>first memory location, and said second device profile<br>representing a second set of attributes of said second<br>memory location, and a difference exists between said first<br>and second device profiles; |

| [Claim 59i]   | said interface controller obtaining the first set of attributes                                                                                                                                                                                                                     |

|               | after identifying the command details;                                                                                                                                                                                                                     |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [Claim 59j]   | and said addressing of said first memory location includes<br>using said attributes from said first device profile; and                                                                                                                                    |  |

| [Claim 59k]   | said addressing of said first memory location includes<br>selecting a transfer size for the memory transaction, wherein<br>the transfer size is a function of a data size of the memory<br>transaction and the first set of attributes.                    |  |

| Claim element | Claim 71                                                                                                                                                                                                                                                   |  |

| [Claim 71]    | The memory controller of claim 59, wherein said difference includes different attribute qualifiers for at least one set of shared attributes from said first and second device profiles.                                                                   |  |

| Claim element | Claim 76                                                                                                                                                                                                                                                   |  |

| [Claim 76]    | The memory controller of claim 71, wherein said different attribute qualifiers include different attribute values.                                                                                                                                         |  |

| Claim element | Claim 80                                                                                                                                                                                                                                                   |  |

| [Claim 80Pre] | An electronic storage device, comprising:                                                                                                                                                                                                                  |  |

| [Claim 80a]   | a memory controller directly coupled to and disposed to<br>address a first memory location and a second memory<br>location which are respectively associated with a first device<br>profile and a second device profile;                                   |  |

| [Claim 80b]   | said memory controller directly coupled to a host as said<br>memory controller addresses the first memory location or<br>second memory location;                                                                                                           |  |

| [Claim 80c]   | wherein said first device profile is optimal for a data type<br>subject to a memory transaction, wherein said data type<br>comprises one of a random data type or a sequential data<br>type;                                                               |  |

| [Claim 80d]   | said memory controller identifies command details for<br>causing the memory transaction to be performed, wherein<br>said command details comprising the first memory device;                                                                               |  |

| [Claim 80e]   | said first device profile representing a first set of attributes of<br>said first memory location, and said second device profile<br>representing a second set of attributes of said second<br>memory location, and a difference exists between said first |  |

|               | and second device profiles;                                                                                                                                                                                              |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [Claim 80f]   | said memory controller obtaining the first set of attributes<br>after identifying the command details;                                                                                                                   |  |

| [Claim 80g]   | and said memory controller using attributes from said first<br>and second device profiles; and                                                                                                                           |  |

| [Claim 80h]   | said memory controller selecting a transfer size for the<br>memory transaction, wherein the transfer size is a function of<br>a data size of the memory transaction and the first set of<br>attributes.                  |  |

| Claim element | Claim 84                                                                                                                                                                                                                 |  |

| [Claim 84]    | The electronic storage device of claim 80, wherein said<br>difference includes different attribute qualifiers for at least<br>one set of shared attributes from said first and second device<br>profiles.                |  |

| Claim element | Claim 85                                                                                                                                                                                                                 |  |

| [Claim 85]    | The electronic storage device of claim 84, wherein said different attribute qualifiers include different attribute values.                                                                                               |  |

| Claim element | Claim 98                                                                                                                                                                                                                 |  |

| [Claim 98Pre] | An electronic storage device, comprising:                                                                                                                                                                                |  |

| [Claim 98a]   | a memory controller directly coupled to and disposed to<br>address a first memory location and a second memory<br>location which are respectively associated with a first device<br>profile and a second device profile; |  |

| [Claim 98b]   | wherein the memory controller is directly coupled to a host<br>as the memory controller addresses the first memory location<br>or the second memory location;                                                            |  |

| [Claim 98c]   | wherein said first device profile is optimal for a data type<br>subject to a memory transaction, wherein said data type<br>comprises one of a random data type or a sequential data<br>type;                             |  |

| [Claim 98d]   | said memory controller identifies command details for<br>causing the memory transaction to be performed, wherein<br>said command details comprising the first memory device;                                             |  |

| [Claim 98e] | the first device profile representing a first set of attributes of<br>the first memory location, and the second device profile<br>representing a second set of attributes of the second memory<br>location;     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Claim 98f] | said memory controller obtaining the first set of attributes<br>after identifying the command details;                                                                                                          |

| [Claim 98g] | and wherein said memory controller uses attributes from the first and second device profiles;                                                                                                                   |

| [Claim 98h] | wherein said memory controller selecting a transfer size for<br>the memory transaction, wherein the transfer size is a<br>function of a data size of the memory transaction and the<br>first set of attributes. |

# I. INTRODUCTION

KIOXIA Corporation and KIOXIA America, Inc. ("Petitioners") petition for institution of inter partes review ("IPR") of claims 1, 5-6, 29, 36-37, 45, 51-52, 59, 71, 76, 80, 84-85, 98 ("challenged claims") of U.S. Patent No. 9,135,190 ("the '190 patent"). Ex-1001.

#### II. GROUNDS FOR STANDING

Petitioners certify that the '190 patent is available for review under 35 U.S.C. § 311(c) and that Petitioners are not estopped from requesting *inter partes* review of the challenged claims on the grounds identified in this Petition.

#### III. FEES

The Commissioner is hereby authorized to charge or credit the fee specified by 37 C.F.R. § 42.15(a), and any other additional fees, to Bracewell LLP Deposit Account No. 50-0259.

### **IV. PRECISE RELIEF REQUESTED**

Petitioners request review of the challenged claims under 35 U.S.C. § 311 and cancellation of the challenged claims under pre-AIA 35 U.S.C. § 103(a) in view of the prior art and grounds described herein.

## A. Prior Art

# 1. Cornwell

Petitioners rely on U.S. App. Pub. No. 2007/0180186 ("Cornwell"). Ex-1005. Cornwell was published on August 2, 2007, more than a year before the alleged priority date for the '190 patent, and qualifies as a prior art printed publication under at least pre-AIA 35 U.S.C. § 102(b).

### 2. Ware

Petitioners also rely on U.S. Patent No. 7,269,708 ("Ware"). Ex-1006. Ware was issued on September 11, 2007, more than a year before the alleged priority date for the '190 patent, and qualifies as a prior art printed publication under at least pre-AIA 35 U.S.C. § 102(b).

| Ground | Claims                                                     | Statutory Basis                                                                       |

|--------|------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 1      | 1, 5-6, 29, 36-37, 45, 51-52, 59,<br>71, 76, 80, 84-85, 98 | Obviousness under pre-AIA §<br>103(a) in view of Cornwell and a<br>POSITA's knowledge |

| 2      | 1, 5-6, 29, 36-37, 45, 51-52, 59,<br>71, 76, 80, 84-85, 98 | Obviousness under pre-AIA §<br>103(a) in view of Ware and a<br>POSITA's knowledge     |

## **B.** IPR Grounds

#### V. THE '190 PATENT

#### A. Overview of the '190 Patent

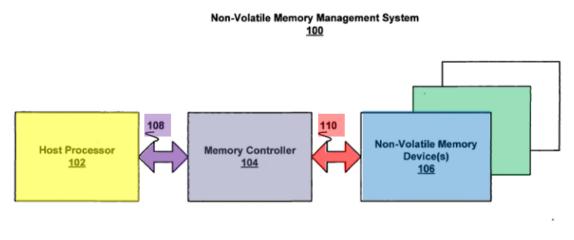

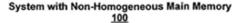

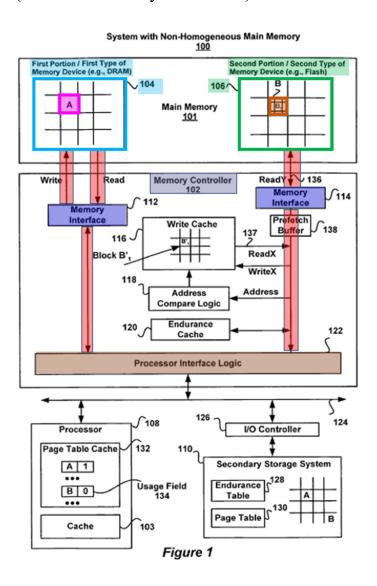

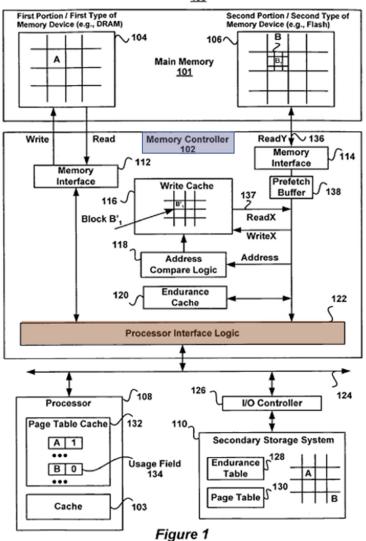

The '190 patent relates to solid-state storage devices utilizing multi-profile memory controllers, but does not purport to invent a new type of memory, multiprofile memory controller, or communication protocol for memory devices and controllers. Ex-1001, 1:17-19. Instead, the patent confirms that the memory devices discussed in the specification, such as Flash memory, SRAM, or DRAM, were wellknown at the time of filing. Id., 1:21-37, 4:47-5:20. The patent further discloses that multi-profile memory controllers for use with these memory devices were wellknown at the time of filing, having "been traditionally designed to operate with memory stores or modules that comprise of memory devices that use the same memory device characteristics," id., 1:21-24, and explains that the recited methods and systems can simply utilize known standards and protocols, such as the Open NAND Flash Interface Specification ("ONFI"), which is a "known device interface standard created by a consortium of technology companies." Id., 4:47-5:3.

Instead, the '190 patent purports to identify a need for a multi-profile memory controller that can operate with memory devices having different memory attributes, *id.* at 1:43-48, and describes a "multi-profile memory controller disposed to perform memory transactions using different device profiles," to address this purported need. *Id.*, 2:44-47. The'190 patent discloses a memory store, which may include multiple

memory locations, each of which is associated with at least one memory "attribute" or "characteristic of a memory location that is related to accessing or addressing the memory location." *Id.*, 2:63-3:15. According to the patent, a multi-profile memory controller can perform memory transactions using the different profiles for these memory devices, *id.* at 3:61-63, 2:44-47. The '190 patent alleges that information can then be mapped to a memory location that is associated with a device profile that is optimal for the type of data subject to the memory transaction request. *Id.*, 9:7-16.

#### B. Prosecution History of the '190 Patent

The application underlying the '190 patent was filed on September 4, 2010. In response to multiple rejections asserting that the applied-for claims were anticipated or rendered obvious by the prior art, the applicant made numerous substantive amendments to the claims. Ultimately, the Examiner issued a Notice of Allowance on June 22, 2015. Importantly, neither Cornwell nor Ware was before the Examiner during prosecution; however, as discussed below, both references disclose the particular claim elements on which the Examiner based the Notice of Allowance. *See* Ex-1003, ¶¶ 25-40.

#### VI. LEVEL OF ORDINARY SKILL IN THE ART

As of the priority date, a person of ordinary skill in the art ("POSITA") would have had at least a Bachelor's degree in electrical or computer engineering, or a similar field, and at least two years of work experience in the computer memory or

4

data storage industry. Ex-1003, ¶¶ 66-69. A POSITA could have substituted less formal education with additional relevant work experience, and vice versa. *Id.*

#### VII. CLAIM CONSTRUCTION

In an IPR, claim terms should be construed according to the *Phillips* standard. *See Phillips v. AWH Corp.*, 415 F.3d 1303 (Fed. Cir. 2005); *see also* 37 C.F.R. § 42.100(b). The Board need only construe terms to the extent necessary to resolve a controversy. *See Nidec Motor Corp. v. Zhongshan Broad Ocean Motor Co.*, 868 F.3d 1013, 1017 (Fed. Cir. 2017).

A patent claim that uses the term "means for" invokes a rebuttable presumption that the term is a means-plus-function term that should be construed pursuant to 35 U.S.C. § 112. *Williamson v. Citrix Online, LLC*, 792 F.3d 1339, 1348 (Fed. Cir. 2015). Construing a means-plus-function term is a two-step process. *Id.* at 1351. First, the claimed function must be identified. *Id.* Second, the structure disclosed in the specification for performing the claimed function must be determined. *Id.*

For purposes of this proceeding only, Petitioners submit constructions for the following terms.<sup>1</sup> Petitioners do not believe that construction of any other term is

<sup>&</sup>lt;sup>1</sup> While Petitioners propose these constructions for purposes of this proceeding, Petitioners reserve their right to revise or amend these constructions in any other

necessary.<sup>2</sup>

## A. Claim 45: "means for performing a memory transaction"

This term should be construed as a means-plus-function term, with a recited function of "performing a memory transaction." Further, the corresponding structure should be construed as a "multi-profile memory controller or similar structure configured to perform a memory transaction." This is confirmed by the specification, which states that the invention is directed to a "*multi-profile memory*

action or forum. *Western Digital Corp. v. Spex Techs., Inc.*, IPR2018-00084, Paper 14 at 11 (PTAB April 25, 2018) ("37 C.F.R. § 104(b)(3) does not require [a p]etitioner to express its subjective agreement regarding correctness of its proffered claim constructions or to take ownership of those constructions"). Petitioners also reserve the right to challenge the validity of the challenged claims under 35 U.S.C. § 112 in another other action or forum. *See Target Corp. v. Proxicom Wireless, LLC*, IPR2020-00904, Paper 11 at 12-13 (PTAB Nov. 10, 2020) (instituting IPR despite indefiniteness arguments in parallel lawsuit, explaining that this kind of "alternative pleading before a district court is common practice, especially where it concerns issues outside the scope of *inter partes* review").

<sup>2</sup> In the co-pending litigation, the Court held that the term "optimal" had a plain and ordinary meaning. Ex-1007 at 42-45.

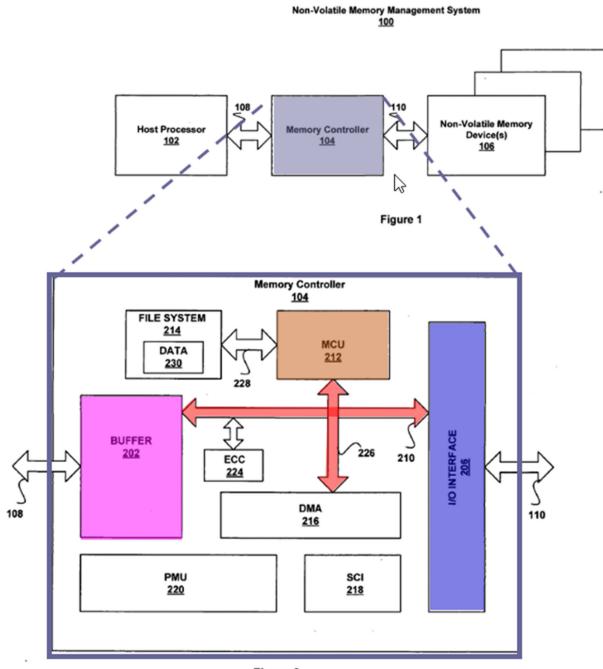

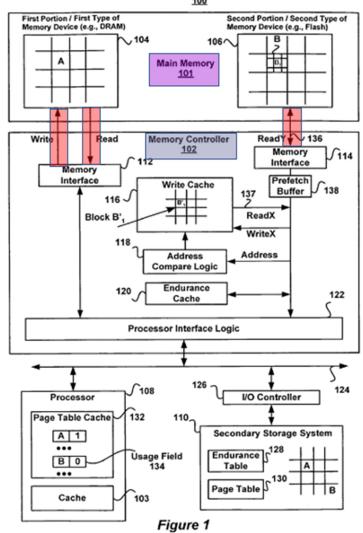

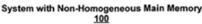

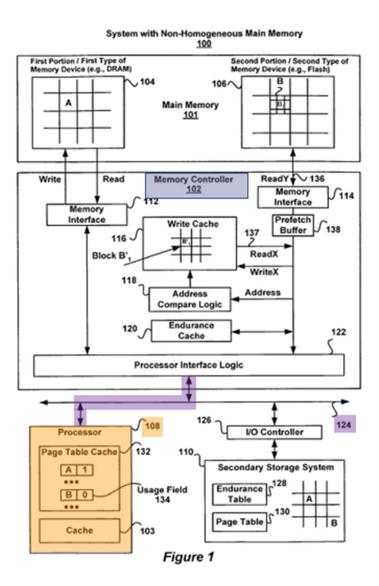

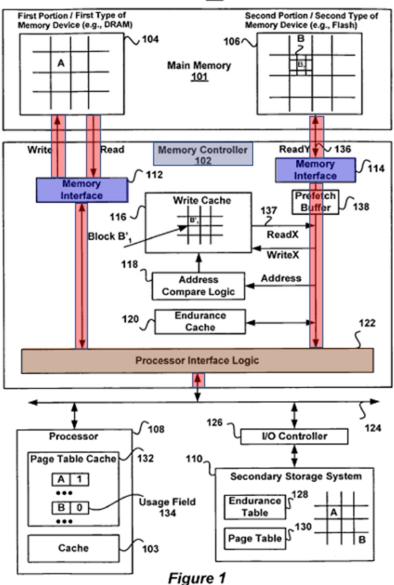

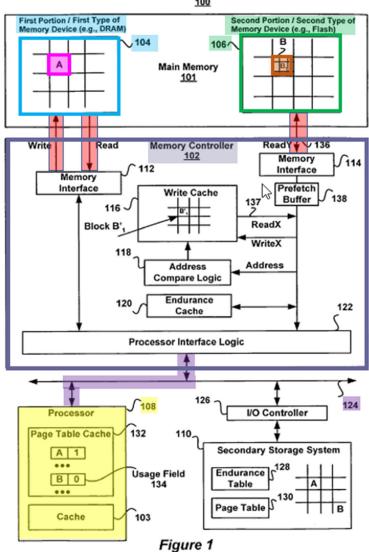

*controller* disposed to *perform a memory transaction*." Ex-1001 at 2:44-47 (emphasis added); 3:61-63; 7:50-53; Figure 1; Ex-1003, ¶¶ 71-75.

# B. Claim 45: "interface controller means for processing memory transaction requests"

This term should be construed as a means-plus-function term, with a recited function of "processing memory transaction requests." The corresponding structure should be construed as an "interface controller or similar structure configured to process memory transaction requests." This construction is established by the specification, which explains that the "*[i]nterface controller* 52 *processes memory transaction request[s]* 6 by interpreting the memory transaction request and performing a memory transaction on a memory location." Ex-1001 at 7:21-24; 5:21-42; Figure 1; Ex-1003, ¶¶ 76-80.

#### C. Claim 45: "means for addressing a first memory location"

This term should be construed as a means-plus-function term, with a recited function of "addressing a first memory location." The corresponding structure should be construed as a "a memory device interface, a host interface, an interface controller or similar structure configured to process memory transaction requests, and associated communication pathways."

This construction is confirmed by both claim 45 and the specification. For example, claim 45 recites four requirements for the "means for addressing"

7

structure:

- "means for performing a memory transaction"—i.e., the memory controller—"comprises" means for addressing, confirming that the means for addressing is a portion of the memory controller.

- 2. means for addressing "is directly coupled to the first memory location and second memory location," confirming that the means for addressing must include the memory device interface as that component is "directly coupled" to the memory. Ex-1001, Figure 1.

- 3. means for addressing is "directly coupled to a host as said means for addressing addresses the first memory location or second memory location," confirming that the means for addressing must include a host interface as that component is directly coupled to the host. *Id*.

- 4. means for addressing "includes an interface controller means for processing memory transaction requests." Thus, means for addressing must include an "interface controller or similar structure configured to process memory transaction requests" as explained above.

The specification of the '190 patent confirms this construction, describing these components and demonstrating that they involved in addressing a memory location. *Id.* at 5:21-42; Figure 1; Ex-1003, ¶¶ 81-86. Petitioner's construction should thus be adopted.

#### **VIII. OVERVIEW OF THE PRIOR ART**

#### A. Cornwell

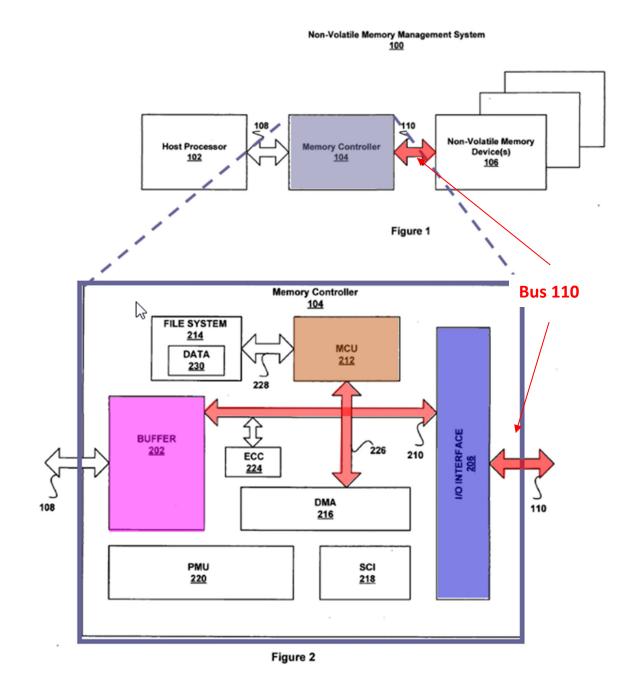

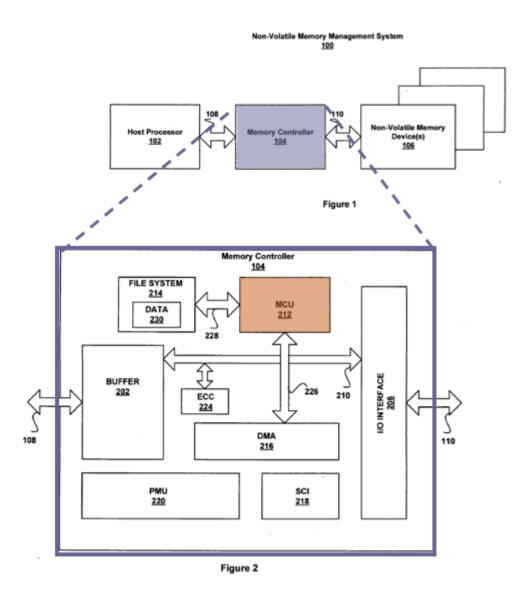

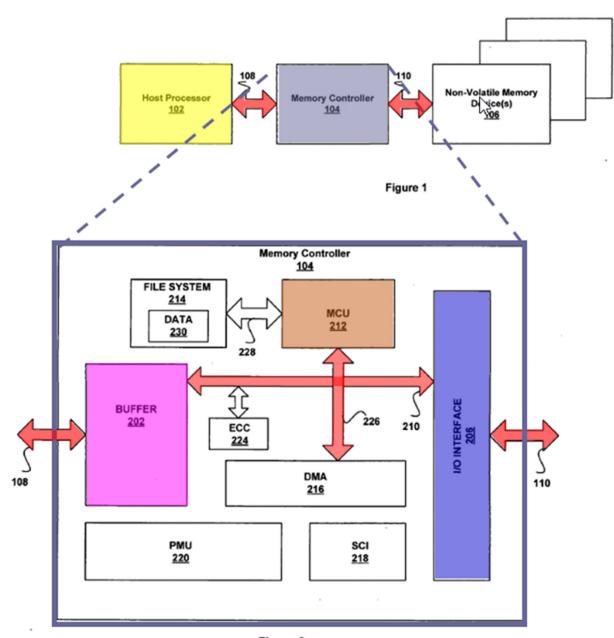

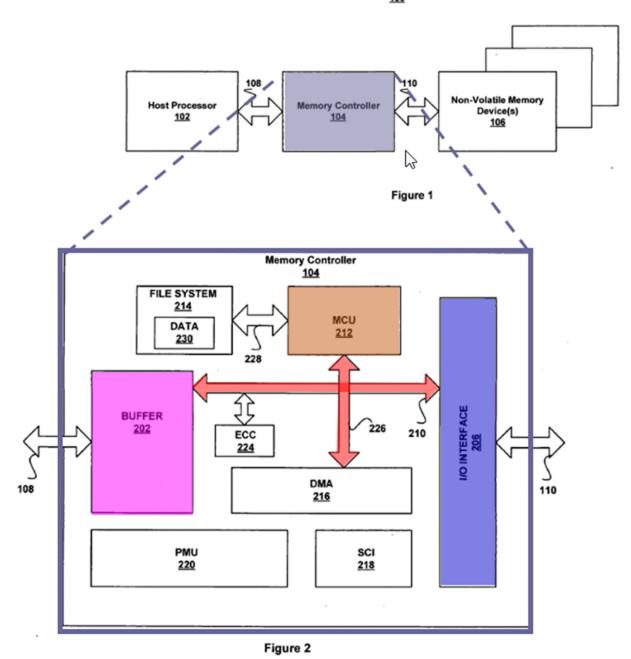

Cornwell teaches a memory management system comprising a memory controller that is coupled to—and utilizes device profiles for—multiple non-volatile memory devices. Ex-1005, ¶¶ [0007]-[0008]. These device profiles, also referred to as "device data," are used to identify each memory device and include a variety of information such as device serial number, device type, device density, device operating voltage, page size, spare area size, sequential access time, block size, bus width, bad block identification, and "any other information that is associated with attributes, properties or characteristics of the memory device." *Id.*, ¶ [0042].

Cornwell teaches that these attribute values may differ between the memory devices. For example, because the memory controller can support "single-level cell (SLC) and/or multi-level cell (MLC) flash media," Cornwell teaches that "syncing with memory devices 106 that include multi-level (MLC) technology can be performed at a different frequency than with memory devices 106 that include single-level cell technology (SLC)." *Id.*, ¶¶ [0019]; [0078]. Cornwell teaches that numerous other attribute values, such as device type and device density, may also vary between the memory devices. *Id.*, ¶ [0042].

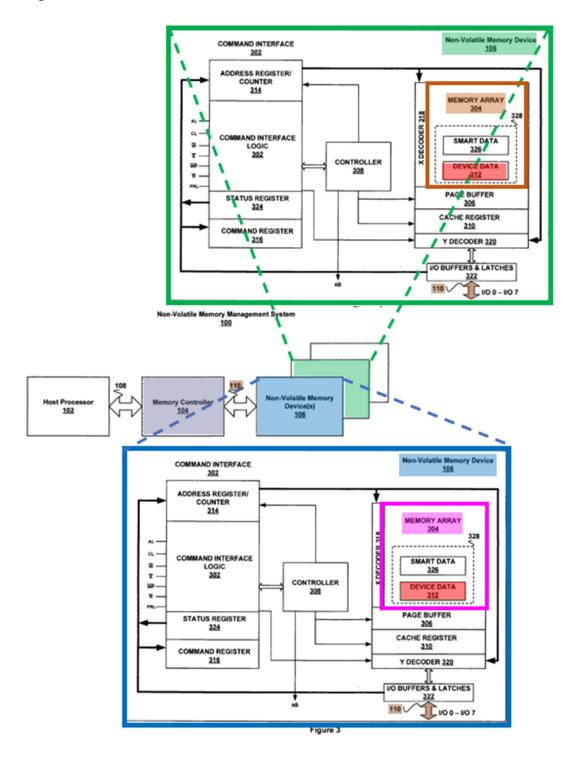

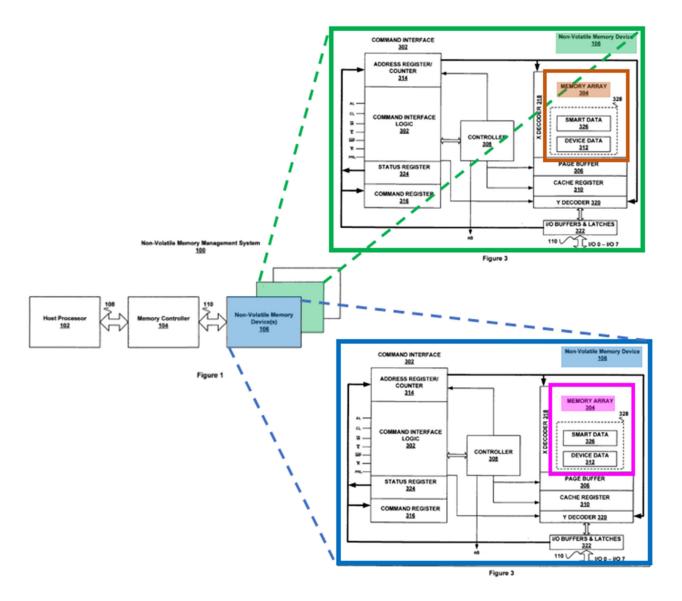

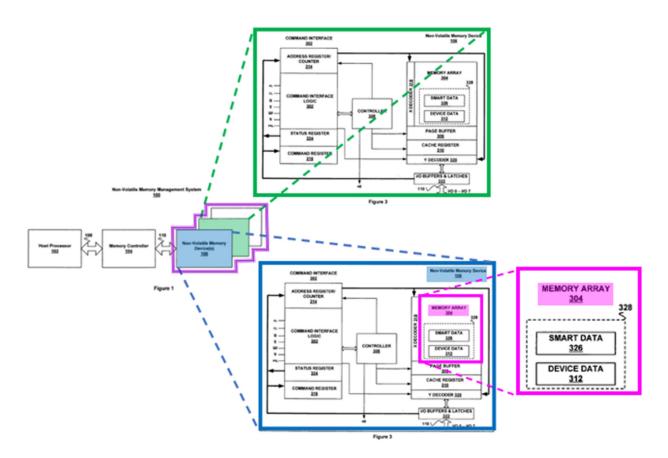

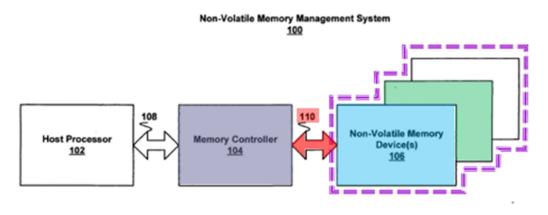

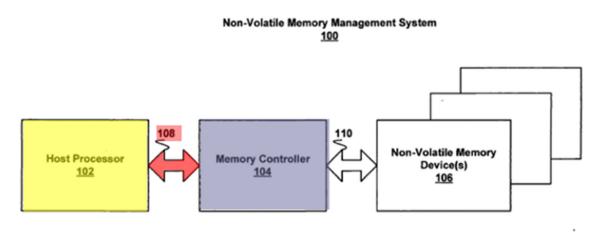

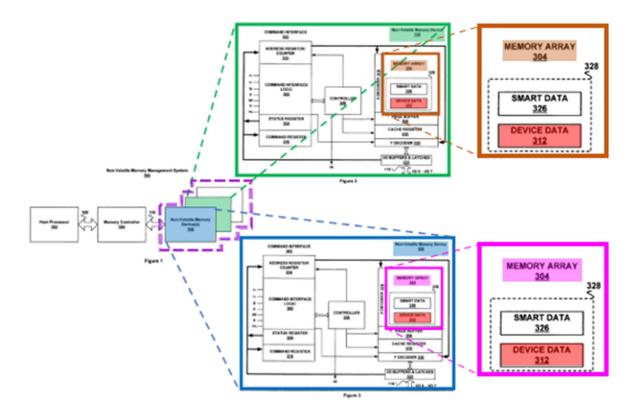

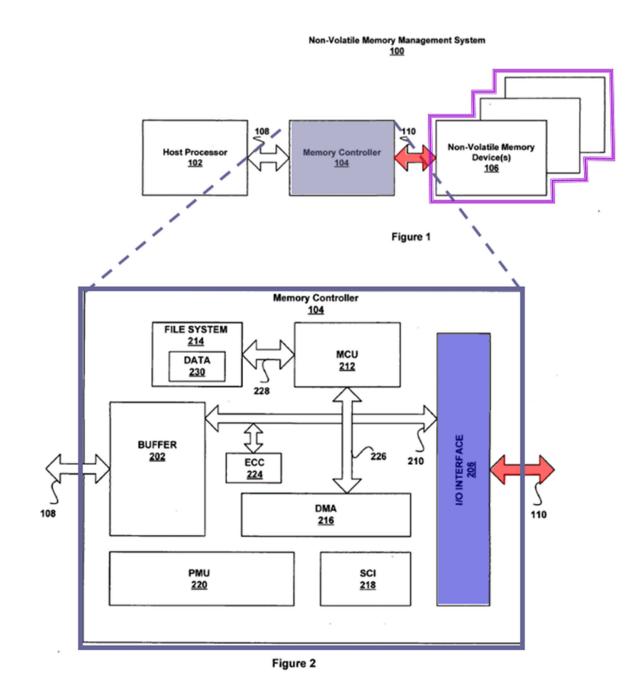

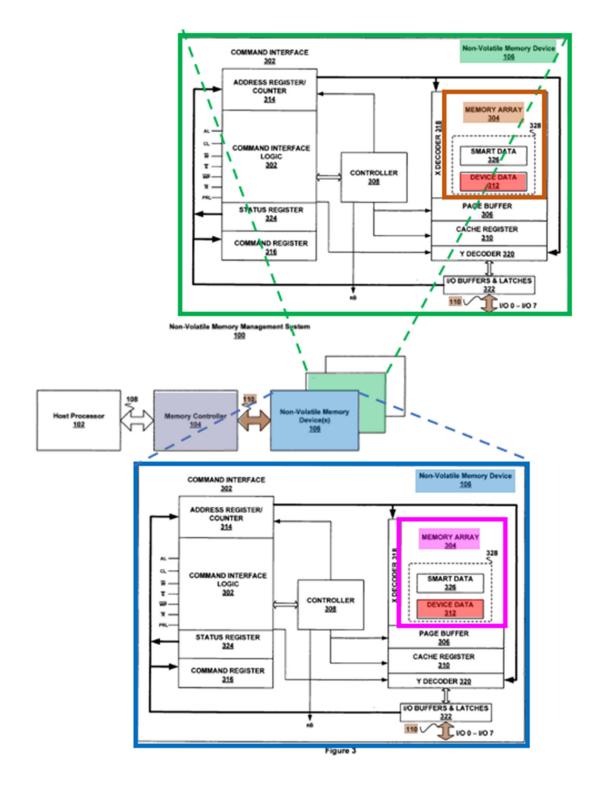

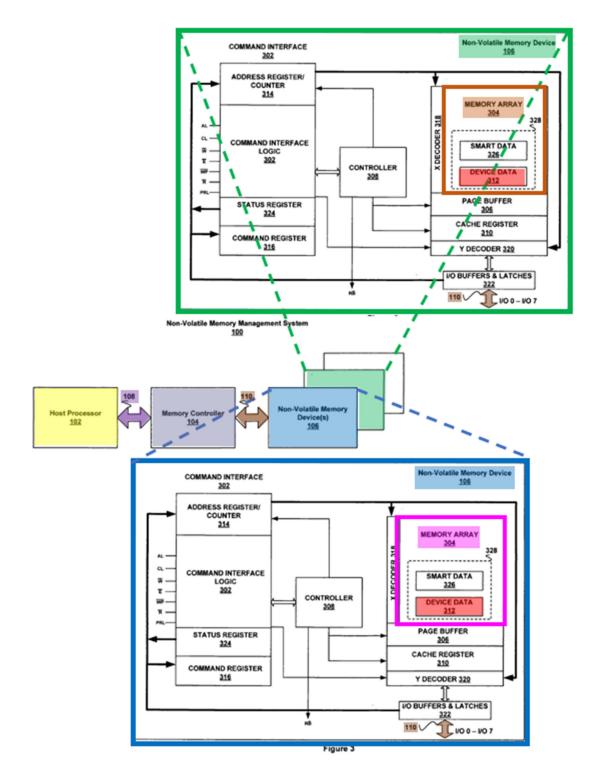

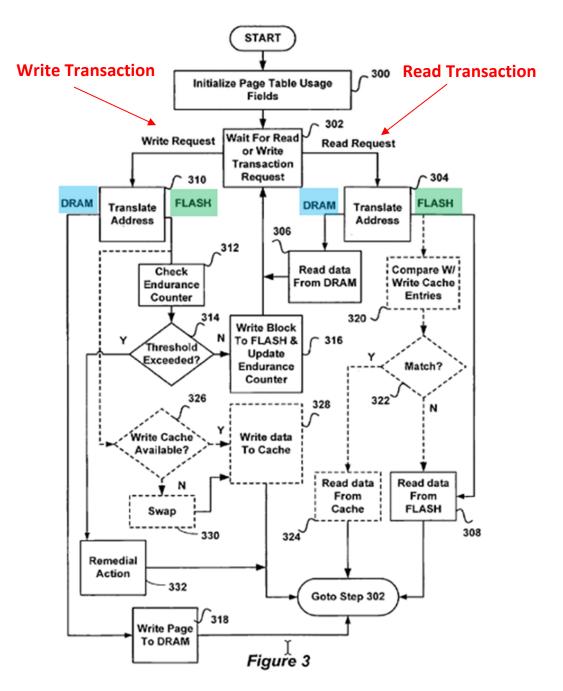

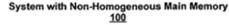

Annotated Figures 1 and 3 illustrate Cornwell's **memory controller** coupled to a **first memory device** and **second memory device**, each of which contain **device**

9

# data or profiles.

#### **B.** Ware

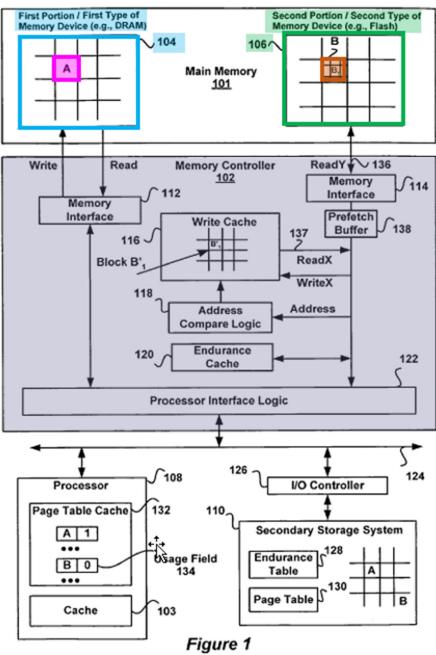

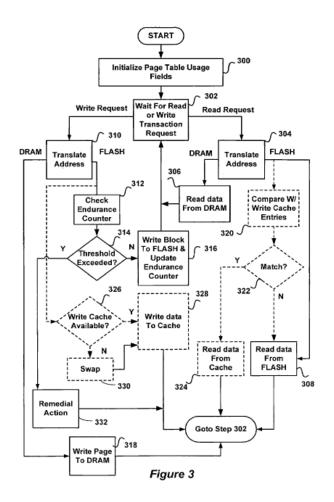

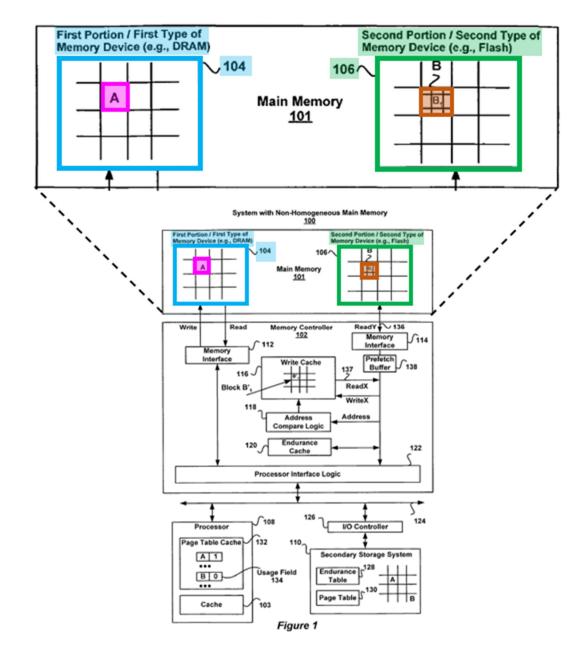

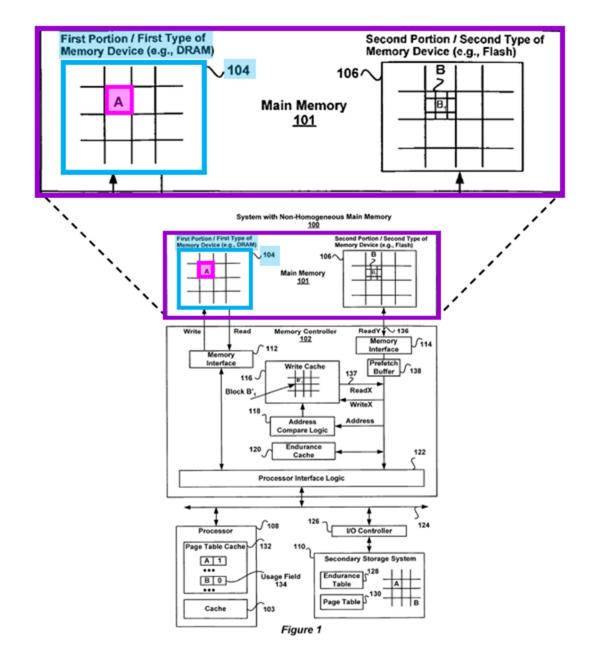

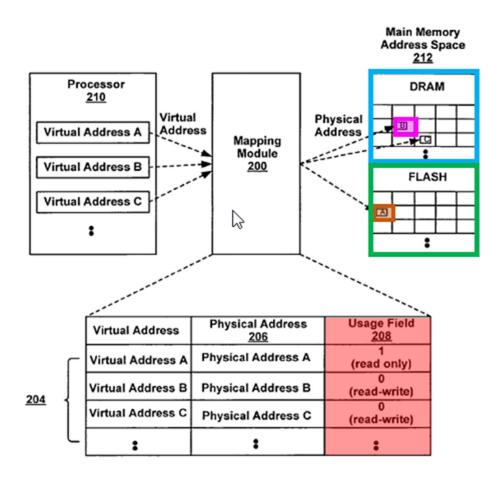

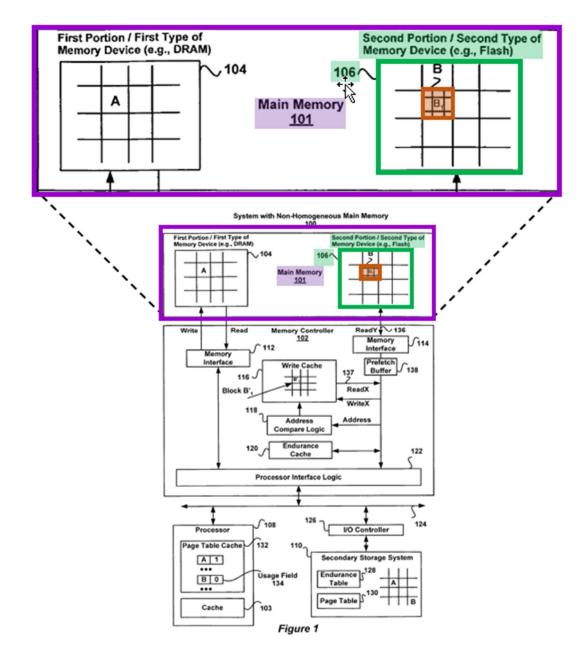

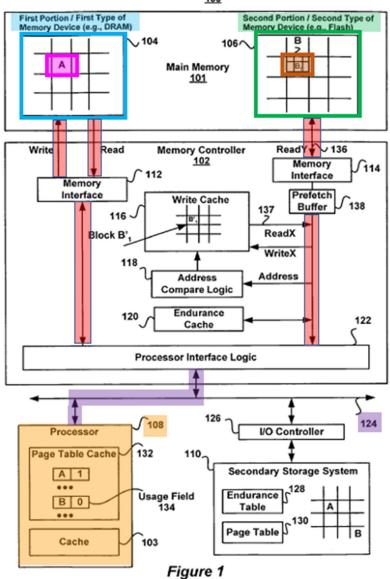

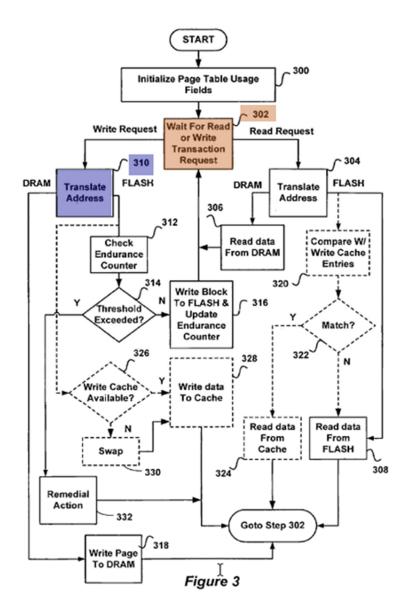

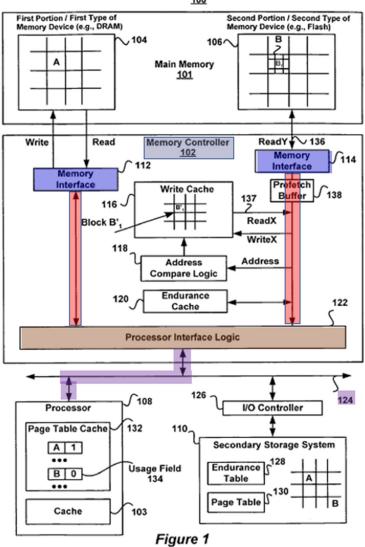

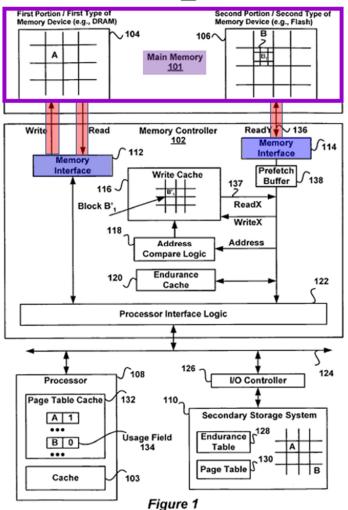

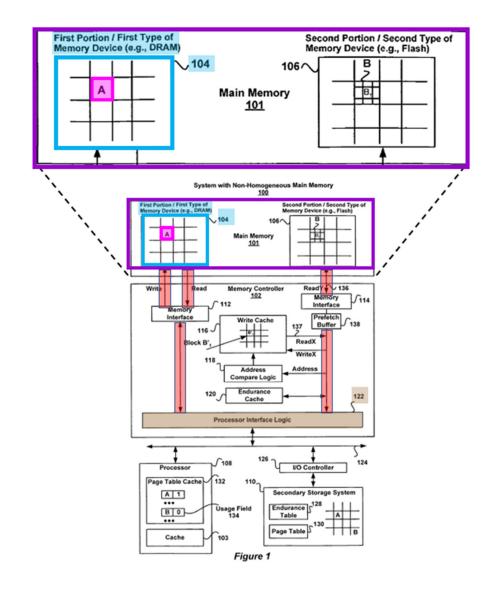

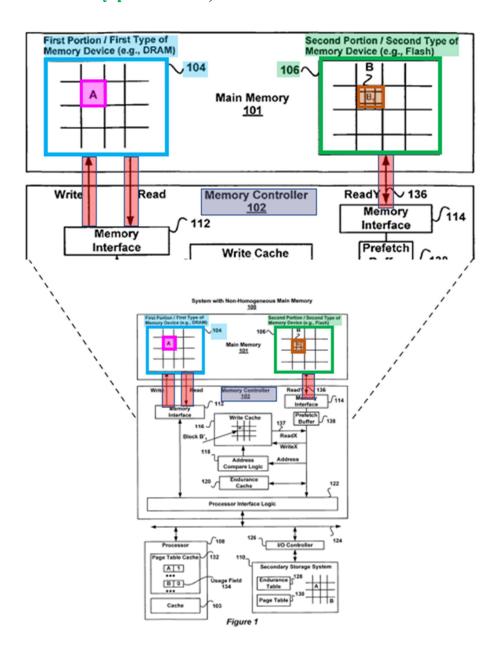

Ware teaches a memory controller for a "non-homogenous memory system" in which the main memory is comprised of two or more memory "portions" or device types, such as DRAM and Flash. Ex-1006 at 2:18-25; 3:57-4:11. Each of the memory devices has a device profile comprising sets of attributes, such as a write-to-read access time ratio, volatility, and endurance. *Id.* at 4:6-11.

Ware teaches that each of these memory devices have "different attributes." *Id.* at 2:21-26. For example, the write-to-read access time ratio differs substantially between DRAM and flash memory. *Id.* at 4:22-37. Similarly, the endurance attribute differs between memory devices. *Id.* at 2:41-48. Accordingly, the memory controller of Ware utilizes these different attributes to distribute data among the different memory devices "in a manner designed to provide fast access to the data and programs that are most frequently used." *Id.*, 3:64-67.

Annotated Figures 1 illustrates Wares memory controller coupled to a first memory device and second memory device.

System with Non-Homogeneous Main Memory <u>100</u>

# IX. THE CHALLENGED CLAIMS ARE UNPATENTABLE AND SHOULD BE CANCELLED

- A. Ground 1: Each of the Challenged Claims is Rendered Obvious by Cornwell in View of a POSITA's Knowledge

- 1. Claim 1 is Obvious in View of Cornwell and a POSITA's Knowledge

- a. [Claim 1Pre]

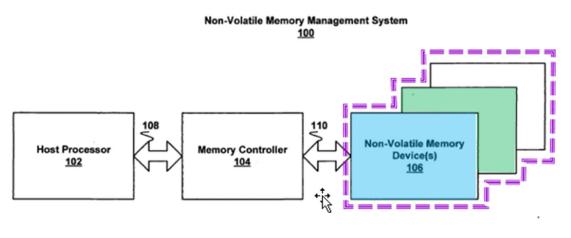

To the extent the preamble is limiting, Cornwell discloses this element by teaching "systems, methods and devices for managing non-volatile memory," as well as memory transactions in the form of "read or write requests . . . [that] are mapped to physical memory addresses that can span two or more memory devices." Ex-1005, ¶ [0006]; [0008]; [0024]; [0038]; [0040]; [0046]. Each of the "one or more non-volatile memory devices 106" can be "discrete chips, chipsets and or memory modules." *Id.*, [0018]; [0020]; Ex-1003, ¶ 98-102.

The first memory location in a first memory device 106 and second memory location in a second memory device 106 disclosed by Cornwell are shown in annotated Figures 1 and 3 below:

IPR2023-00741 Patent No. 9,135,190

Ex-1003, ¶ 100.

## b. [Claim 1a]

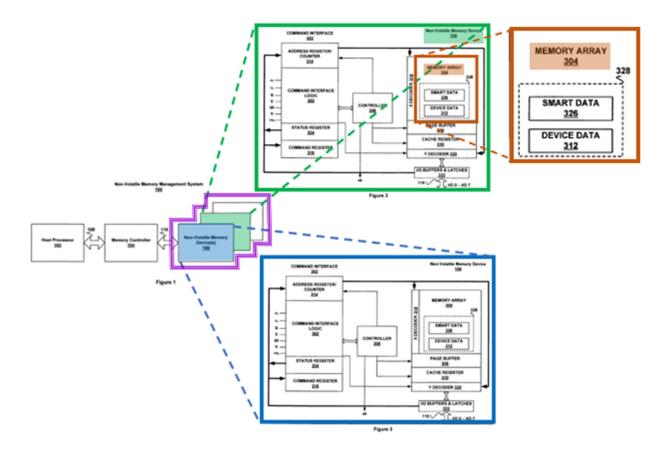

Cornwell discloses a memory store comprising "one or more non-volatile memory devices 106." Ex-1005, ¶¶ [0018]; [0020]; Ex-1003, ¶ 103. The **memory store**, which includes a **first memory device 106** and a **second memory device 106**, is illustrated in annotated Figure 1 below:

Ex-1003, ¶ 104.

Cornwell further discloses addressing a first memory location in a memory store, teaching that "the memory controller 104 recognizes control, *address*, and data signals transmitted . . . by the host processor 102" and "translates the control, *address* and data *signals into* memory *access requests on memory devices 106*." Ex-1005, ¶¶ [0021] (emphasis added); [0035]; [0037]. A POSITA would understand that the address for accessing data in Cornwell's memory device would include information addressing the location in the memory device where the data is located, including in

the first memory location in a first memory device 106 in the memory store, as

illustrated below:

*See* Ex-1003, ¶¶ 104-107.

## c. [Claim 1b]

Cornwell discloses that each memory device 106 includes a device profile in the form of "device data 312 [that] can be used to identify the memory device 106 and its manufacturer." Ex-1005, ¶ [0042]; Ex-1003, ¶ 108. The device profile (device data) "can include an electronic signature or serial number that includes a manufacturer code and/or device code," as well as attributes such as "device type (e.g., NAND, NOR, etc.), device density (e.g., 512 Mb, 1 Gb, 2 Gb, etc.), device operating voltage (e.g., 3.3 volts), page size (1 k, 2K, etc.), spare area size (e.g., 8, 16 bytes, etc.), sequential access time (e.g., 30, 50 nanoseconds, etc.), block size (e.g., 64 k, 128 k, etc.), bus width (e.g.,  $\times 8$ ,  $\times 16$ , etc.), bad block identification, and any other information that is associated with attributes, properties or characteristics of the memory device 106 (collectively, referred to herein as 'attributes')." Ex-1005,  $\P$  [0042]; Ex-1003,  $\P$  108-110.

# d. [Claim 1c]

As illustrated below in annotated Figures 1 and 3, the second memory location disclosed by Cornwell is in the second memory device in the memory store. *See also supra*, §§ IX.A.1.b, IX.A.1.c; Ex-1003, ¶¶ 111-112.

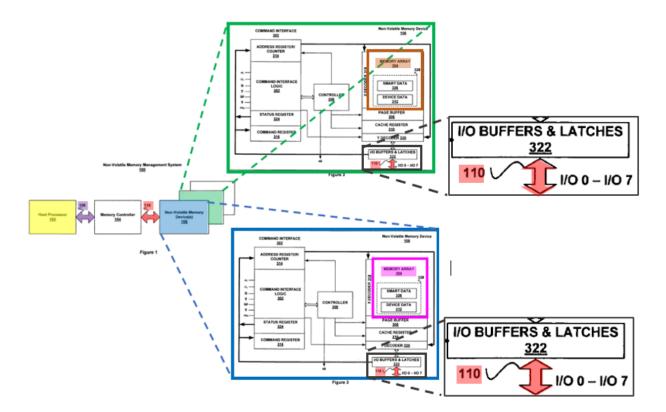

e. [Claim 1d]

Cornwell discloses that a memory read or write transaction is performed on at least one memory location, teaching that "[d]uring operation, one or more memory devices 106 receive signals from the memory controller 104 over Input/Output (I/O) bus 110, which enables the *memory devices 106 to perform* memory access requests (e.g., *read or write operations*)." Ex-1005, ¶¶ [0024] (emphasis added); [0031]; [0034]; [0039]; [0040]; Ex-1003, ¶¶ 113-114.

# f. [Claim 1e]

Cornwell discloses that data is transferred between the host and the first or

second memory locations, explaining that "*a host system performs reads and writes* to logical block addresses (LBAs) which are mapped or translated to *physical block addresses of flash memory*." Ex-1005, ¶¶ [0004] (emphasis added); [0007]; [0021]; [0029]; Ex-1003, ¶ 115. Annotated Figure 1, below, illustrates that data is transferred by **the host processor** over **bus 108** and **bus 110** to and from memory locations in the **first memory device** and the **second memory device**:

Figure 1

Annotated Figures 1 and 3 below further illustrate this process:

Ex-1003, ¶¶ 116-118.

# g. [Claim 1f]

The device profile disclosed by Cornwell "can be used to identify the memory device 106 and its manufacturer" and may be comprised of a variety of information. Ex-1005, ¶ [0042]; *supra* § VI.A.1.c; Ex-1003, ¶ 119. This information includes identifying the "device type (e.g., NAND, NOR, etc.)." Ex-1005, ¶ [0042]. A POSITA would have understood that NOR flash provides access to, and is therefore optimal for, a random data type. Ex-1003, ¶ 120. Likewise, a POSITA would have understood that NAND flash provides access to, and thus is optimal for, a sequential type. *Id*.

Cornwell also discloses that the device profile may comprise information regarding "block size (e.g., 64 k, 128 k, etc.)," Ex-1005, ¶ [0042], and teaches that a device profile can be optimized for a particular data type subject to the memory transactions through "block defining," wherein "[m]emory access efficiency can be improved by matching the average size of files to be stored in the flash media to the block size of the flash media." *Id.*, ¶¶ [0048]-[0050] (emphasis added). Cornwell further discloses that "[i]n some implementations a *random* [*data type*] *read command* may be issued first, followed by a page [*sequential data type*] read command." *Id.*, ¶ [0040] (emphasis added). By matching block size to file size, and teaching that files contain random or sequential data types, Cornwell teaches that a first device profile is optimal for a data type subject to the memory transaction. Ex-1003, ¶ 122.

Accordingly, because a POSITA would have understood from Cornwell that a device profile would be optimal for a data type subject to the transaction, this claim element is rendered obvious by Cornwell in view of a POSITA's knowledge. *Id.*, ¶¶ 119-123.

## h. [Claim 1g]

The memory device disclosed by Cornwell "includes a command interface 302, a memory array 304 and a controller 308." Ex-1005,  $\P$  [0034]. Cornwell further discloses a variety of commands that are "translated into signals which can be used

21

by a controller and decoding logic in the memory device 106 to access a memory array." *Id.*, ¶ [0027]. "For example, when the host processor 102 makes a read request, the 'Read Sectors' opcode (20 h) is transmitted to the memory controller 104, together with address and control signals for accessing the sector(s)." *Id.*, ¶¶ [0027]; [0035]; [0038]. A POSITA would thus understand that Cornwell discloses identifying command details for causing the memory transaction to be performed, wherein the command details comprise the first memory device. Ex-1003, ¶ 124.

Examples of commands, including read and write commands, are shown in Table 1:

| Examples of Standard ATA-6 Commands |                   |

|-------------------------------------|-------------------|

| Opcode                              | Command           |

| 10h                                 | Recalibrate       |

| 20h                                 | Read Sectors      |

| 30h                                 | Write Sectors     |

| <b>4</b> 0h                         | Read Verify       |

| B0h                                 | SMART             |

| C8h                                 | Read DMA          |

| CAh                                 | Write DMA         |

| EOh                                 | Standby Immediate |

| E2h                                 | Standby           |

| E7h                                 | Flush Cache       |

| ECh                                 | Identify          |

| EFh                                 | Set Features      |

TABLE I

Ex-1005, ¶ [0026]; Ex-1003, ¶¶ 125-127.

# i. [Claim 1h]

Cornwell discloses that each device profile (device data 312) includes a variety of information "associated with *attributes*, *properties or characteristics* of

the memory device 106 (*collectively, referred to herein as 'attributes'*)." Ex-1005, ¶ [0042] (emphasis added); *supra* § IX.A.1.c. The memory profiles taught by Cornwell may also be different, including by having different densities for singlelayer cell or multi-layer cell technology. Ex-1005, ¶ [0078]; Ex-1003, ¶ 129. Similarly, Cornwell identifies many other potential differences in device attributes, including device type, device density, spare area, block size, bad block identification, etc. Ex-1005, ¶¶ [0042]; [0054]-[0056]; Ex-1003, ¶ 130.

Accordingly, because a POSITA would have understood from Cornwell that differences could exist between device profiles, this claim element is rendered obvious by Cornwell in view of a POSITA's knowledge. Ex-1003, ¶¶ 128-133.

### j. [Claim 1i]

Cornwell discloses that attributes comprising device data 312 can be obtained or "transmitted to the memory controller 104 via the I/O bus 110 *in response to a read command* issued by the memory controller." Ex-1005, ¶ [0043] (emphasis added). This teaching confirms that the attributes are obtained after the command details are identified. Ex-1003, ¶¶ 134-135.

## k. [Claim 1j]

Cornwell teaches that each of the attributes, as described above, is associated with a respective attribute qualifier. Ex-1005, ¶ [0042]; *supra*, § IX.A.1.i. For example, the "device type" attribute is associated with the qualifiers "NAND" or

23

"NOR," the "device density" attribute is associated with the qualifiers "512 Mb," "1Gb," and "2Gb," etc. Ex-1005, ¶ [0042]; Ex-1003 ¶ 136. Cornwell also discloses that the device profile (device data 312) comprising these qualifiers "can be used to identify the memory device 106 and its manufacturer," thereby qualifying each memory location. Ex-1005, ¶ [0042]; Ex-1003, ¶¶ 137-138.

## I. [Claim 1k]

Cornwell discloses that the memory store is directly coupled to at least one memory bus that is also coupled to a controller, noting "one or more memory devices 106 receive[s] signals *from the memory controller 104 over Input/Output (I/O) bus 110*, which enables the memory devices 106 to perform memory access requests (e.g., read or write operations)." Ex-1005, ¶¶ [0024] (emphasis added); [0042]. Annotated Figure 1 further illustrates that the memory store is directly coupled to **bus 110**, which is directly coupled to the **memory controller 104**:

## Ex-1003, ¶ 140.

Cornwell further discloses that the controller performs read and write transactions on the memory store, explaining that the memory devices "receive signals from the memory controller 104," which "enables the memory devices 106 to perform memory access requests (e.g., read or write operations)." Ex-1005, ¶¶ [0024]; [0029]; Ex-1003, ¶¶ 139-142.

## m. [Claim 11]

As shown in annotated Figure 1, Cornwell discloses that the **host processor** is directly coupled to the **memory controller 104** via **bus 108**, explaining that data requests "are transmitted to the memory controller 104 on the IDE/ATA *bus 108* by the host processor 102." Ex-1005, ¶¶ [0025] (emphasis added); [0021]; Ex-1003, ¶¶ 143-145:

Figure 1

## n. [Claim 1m]

Cornwell discloses that each device profile (device data 312) may be "stored in a spare area 328 of the memory array 304" and "can be used to identify the memory device 106 and its manufacturer." Ex-1005, [0042]; *supra* §§ IX.A.1.c, IX.A.1.i; Ex-1003, ¶¶ 146-148. Annotated Figures 1 and 3 illustrate that **device profiles** for both the **first memory location** (memory array 304) and the **second memory location** (memory array 304) are stored in the memory store:

Ex-1003, ¶ 147.

## o. [Claim 1n]

Cornwell teaches that attributes from each device profile are used, i.e., device data 312 is transmitted "*in response to a read command* issued by the by the

memory controller" and "*used by the memory controller 104 and/or host system* to perform various memory management tasks." Ex-1005, ¶¶ [0043] (emphasis added); [0042]; [0046], [0058]; Ex-1003, ¶¶ 149-150.

## p. [Claim 1o]

Cornwell teaches that "the controller 308, *programs the page* into the memory array  $304 \dots$ " Ex-1005, ¶ [0039] (emphasis added). Each page has a specific "page size (1k, 2k, etc.)." *Id.*, ¶¶ [0042]; [0048]; [0050]. Cornwell therefore teaches selecting a transfer size for the memory transaction. Ex-1003, ¶ 151.

Cornwell also discloses that page size is a function of device density, which may vary, and the IDE/ATA bus standard, which is used as the communication between the host and the command interface 302. Ex-1005, [0042]; *supra*, §§ IX.A.1.i-IX.A.1.k. Further, a POSITA would have understood that page size is the length of a row (i.e., the number of columns) in the memory, which varies with the device density, and that the data size information (e.g., the number of logical sectors to be transferred), which is referred by the controller for the communication between the controller and the memory store, is included in the ATA command from the host. Ex-1003, ¶¶ 151-152. Cornwell thus teaches that the transfer size is also a function of the first set of attributes, such as the device density. *Id.* Cornwell also teaches that the transfer size is selected by the controller. *Id.*, ¶¶ 153-155.

# 2. Claim 5 is Obvious in View of Cornwell and a POSITA's Knowledge

Cornwell teaches that the first and second device profiles (device data 312) have shared attributes. Ex-1005, ¶ [0042]; *supra*, §§ IX.A.1.k, IX.A.1.i. It would also have been obvious to a POSITA that these shared attributes could have different attribute qualifiers. *Supra*, § IX.A.1.k; Ex-1003, ¶ 158. For example, it would have been obvious to a POSITA, based on their knowledge in view of Cornwell, that the first memory location using NAND would have a "NAND" qualifier for the "device type" attribute, while a second memory location using NOR would have a "NOR" qualifier for the "device type" attribute. Ex-1005, ¶ [0042]; Ex-1003, ¶ 158.

# 3. Claim 6 is Obvious in View of Cornwell and a POSITA's Knowledge

It would have been obvious to a POSITA that the shared attributes disclosed by Cornwell could have different attribute qualifiers. *Supra*, §§ IX.A.1.i; Ex-1003, ¶ 162. Cornwell also discloses that each attribute qualifier has an attribute value, which can be different for different attribute qualifiers. *Supra*, §§ IX.A.1.i, IX.A.2. It therefore would have been obvious to a POSITA, based on their knowledge in view of Cornwell, to include different attribute values for different attribute qualifiers. Ex-1003, ¶¶ 162-164.

# 4. Claim 29 is Obvious in View of Cornwell and a POSITA's Knowledge

a. [Claim 29 pre]

To the extent the preamble is limiting, Cornwell discloses the recited method for the reasons discussed above with respect to element [1 pre]. *Supra*, § IX.A.1.a; Ex-1003, ¶ 166. Cornwell further discloses that "memory device information is stored on a *computer-readable medium* in the host system (e.g., memory, hard disk, CDROM, etc.)," which constitute non-transitory computer readable media. Ex-1005, ¶ [0047] (emphasis added). Further, "the host system can include pre-stored information for multiple memory devices that are known to be compatible with the host system and the memory controller." *Id*. Thus, the non-transitory computer readable medium comprises computer executable instructions adapted to cause a method of performing memory transactions on a first memory location and a second memory location. *Id.*, ¶¶ [0083]-[0084]; Ex-1003, ¶¶ 167-171.

### b. [Claim 29a]

The recited features of element [29a] are substantially identical to those of elements [1a] and [1b]. Cornwell discloses this element for the reasons discussed above. *Supra* §§ IX.A.1.b, IX.A.1.c; Ex-1003, ¶¶ 172-178.

### c. [Claim 29b]

Element [29b] is identical to element [1f] and is rendered obvious by Cornwell for the reasons discussed above. *Supra* § IX.A.1.g; Ex-1003, ¶¶ 179-184.

## d. [Claim 29c]

Element [29c] is identical to element [1g] and is disclosed by Cornwell for the

reasons discussed above. Supra § IX.A.1.h; Ex-1003, ¶¶ 185-188.

## e. [Claim 29d]

Element [29d] is identical to element [1h] and is rendered obvious for the reasons discussed above. *Supra* § IX.A.1.i; Ex-1003, ¶¶ 189-194.

# f. [Claim 29e]

Element [29e] is identical to element [1i] and is disclosed by Cornwell for the reasons discussed above. *Supra* § IX.A.1.j; Ex-1003, ¶¶ 195-196.

# g. [Claim 29f]

Element [29f] is identical to element [1n] and is disclosed by Cornwell for the reasons discussed above. *Supra* § IX.A.1.o; Ex-1003, ¶¶ 197-198.

# h. [Claim 29g]

Element [29g] is identical to element [10] and is disclosed by Cornwell for the reasons discussed above. *Supra* § IX.A.1.p; Ex-1003, ¶¶ 199-203.

## 5. Claim 36

Claim 36 is substantially identical to claim 5 and is rendered obvious for the reasons discussed above. *Supra* § IX.A.2; Ex-1003, ¶¶ 205-207.

## 6. Claim 37

Claim 37 is substantially identical to claim 6 and is rendered obvious for the reasons discussed above. *Supra* § IX.A.3; Ex-1003, ¶¶ 209-212.

# 7. Claim 45 is Obvious in View of Cornwell and a POSITA's

## Knowledge

## a. [Claim 45 pre]

To the extent the preamble is limiting, Cornwell discloses "[a] memory controller [that] is operatively coupled to the one or more non-volatile memory devices and configurable to access the one or more non-volatile memory devices." Ex-1005,  $\P$  [0007]; Ex-1003,  $\P\P$  214-215.

### b. [Claim 45a]

Cornwell discloses the first recited function of "performing a memory transaction" as well as a "memory controller" for performing that function pursuant to Petitioner's proposed construction. Specifically, Cornwell discloses "*[a] memory controller* [that] is operatively coupled to the one or more non-volatile memory devices and *configurable to access the one or more non-volatile memory devices*." Ex-1005, ¶¶ [0007] (emphasis added); [0021] (explaining that "memory controller 104 translates control, address and data signals into memory access requests on memory devices 106"); [0024]-[0025]; Ex-1003, ¶¶ 218-219.

Cornwell also discloses the second recited function of "addressing a first memory location." Cornwell explains that the memory controller "translates control, *address* and data signals into memory access requests on memory devices 106." *Id.* ¶¶ [0021]; [0035]. Cornwell also discloses Petitioner's proposed structure of "a memory device interface, a host interface, an interface controller, and associated

**communication pathways,**" *supra* § VII.C, as shown in annotated Figures 1 and 2:

Figure 2

## Ex-1003, ¶¶ 221-225.