# UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_\_

### BEFORE THE PATENT TRIAL AND APPEAL BOARD

\_\_\_\_\_

SAMSUNG ELECTRONICS CO., LTD., and SAMSUNG ELECTRONICS AMERICA, INC.,

Petitioner

V.

SONRAI MEMORY LTD.,

Patent Owner

U.S. PATENT NO. 7,159,766

Case IPR2022-TBD

PETITION FOR *INTER PARTES* REVIEW UNDER 35 U.S.C. § 312 AND 37 C.F.R. § 42.104

# TABLE OF CONTENTS

| I.   | INTE                                       | TRODUCTION1                                |    |  |  |

|------|--------------------------------------------|--------------------------------------------|----|--|--|

| II.  | OVERVIEW OF CHALLENGE AND RELIEF REQUESTED |                                            |    |  |  |

|      | A.                                         | Prior Art Patents and Printed Publications | 1  |  |  |

|      | B.                                         | Relief Requested                           | 2  |  |  |

| III. | OVE                                        | ERVIEW OF THE TECHNOLOGY                   | 3  |  |  |

|      | A.                                         | USB Architecture and Topology              | 3  |  |  |

|      | B.                                         | USB Cabling and Device Connections         | 4  |  |  |

| IV.  | U.S.                                       | U.S. PATENT NO. 7,159,7669                 |    |  |  |

|      | A.                                         | Claims                                     | 9  |  |  |

|      | B.                                         | Specification                              | 9  |  |  |

|      | C.                                         | Summary of the Prosecution History         | 12 |  |  |

|      | D.                                         | Person of Ordinary Skill in the Art        | 13 |  |  |

| V.   | CLA                                        | IM CONSTRUCTION                            | 13 |  |  |

| VI.  | OVE                                        | ERVIEW OF THE PRIOR ART                    | 14 |  |  |

|      | A.                                         | Cohen                                      | 14 |  |  |

|      | B.                                         | Maemura                                    | 17 |  |  |

|      | C.                                         | USB 2.0                                    | 19 |  |  |

|      | D.                                         | USB 1.0                                    | 19 |  |  |

|      | E.                                         | Tornai                                     | 20 |  |  |

| VII. | SPEC                                       | CIFIC GROUNDS FOR PETITION                 | 20 |  |  |

|      | A.                                         | Ground I                                   | 20 |  |  |

|      |                                            | 1. Claim 1                                 | 21 |  |  |

| 2.  | Claim 3: "The system of claim 1, wherein the device is a       |     |

|-----|----------------------------------------------------------------|-----|

|     | hub and the active state comprises a second device             |     |

|     | attached to the hub"                                           | 31  |

| 3.  | Claim 6: "The system of claim 1, wherein when the              |     |

|     | device is electrically disconnected from the host              |     |

|     | controller, the device does not cause bus activity"            | 31  |

| 4.  | Claim 8: "The system of claim 1, wherein if the                |     |

|     | processor is in a low power state, the processor exits the     |     |

|     | low power state if an electrical disconnect is                 |     |

|     | discontinued"                                                  | 31  |

| 5.  | Claim 10: "The system of claim 1, wherein the host             |     |

|     | controller provides a peripheral bus interface for the         |     |

|     | device"                                                        | 33  |

| 6.  | Claim 11: "The system of claim 1, wherein electrically         |     |

|     | disconnecting the device comprises electrically removing       |     |

|     | a pull up resistor from a D+ line"                             | 33  |

| 7.  | Claim 13: "The system of claim 1, wherein the device           |     |

| , - | being electrically disconnected from the host controller       |     |

|     | allows the processor to enter a low power state or remain      |     |

|     | in a low power state"                                          | 34  |

| 8.  | Claim 14                                                       | 34  |

| 9.  | Claim 16: "The method of claim 14, wherein the device          | 5 1 |

| •   | is a hub, and the active state comprises a second device       |     |

|     | coupled to the hub"                                            | 36  |

| 10. | Claim 21: "The method of claim 14, wherein if no               | 50  |

| 10. | devices are coupled to the host controller the host            |     |

|     | controller does not create bus activity"                       | 36  |

| 11. | Claim 25: "The method of claim 14, wherein the host            | 50  |

| 11. |                                                                |     |

|     | controller provides a peripheral bus interface for the device" | 36  |

| 12. | Claim 26: "The method of claim 14, wherein electrically        | 30  |

| 12. | ·                                                              |     |

|     | disconnecting the device comprises electrically removing       | 20  |

| 1.2 | a pull up resistor from a D+ line"                             |     |

| 13. | Claim 28                                                       |     |

| 14. | Claim 39                                                       |     |

| 15. | Claim 45                                                       | 37  |

| 16. | Claim 47: "The memory medium of claim 45, wherein              |     |

|     | the device is a hub, and the active state comprises a          |     |

|     | second device coupled to the hub"                              | 38  |

|    | 17.  | Claim 50: "The memory medium of claim 45, wherein if no devices are coupled to the host controller the host |    |

|----|------|-------------------------------------------------------------------------------------------------------------|----|

|    |      | controller does not create bus activity"                                                                    | 38 |

|    | 18.  | Claim 54: "The memory medium of claim 45, wherein                                                           |    |

|    |      | the host controller provides a peripheral bus interface for                                                 |    |

|    |      | the device"                                                                                                 | 38 |

|    | 19.  | Claim 55: "The memory medium of claim 45, wherein                                                           |    |

|    |      | electrically disconnecting the device comprises                                                             |    |

|    |      | electrically removing a pull up resistor from a D+ line"                                                    | 38 |

|    | 20.  | Claims 57 and 58                                                                                            |    |

| В. | Grou | ınd 2                                                                                                       | 39 |

|    |      |                                                                                                             |    |

|    | 1.   | Claims 5, 20, and 49                                                                                        |    |

|    | 2.   | Claim 60                                                                                                    |    |

|    | 3.   | Claims 4, 19, and 48                                                                                        | 42 |

| C. | Grou | and 3                                                                                                       | 42 |

|    |      |                                                                                                             |    |

|    | 1.   | Claim 1                                                                                                     | 43 |

|    | 1.   | Claim 6: "The system of claim 1, wherein when the                                                           |    |

|    |      | device is electrically disconnected from the host                                                           |    |

|    |      | controller, the device does not cause bus activity"                                                         | 49 |

|    | 2.   | Claim 8: "The system of claim 1, wherein if the                                                             |    |

|    |      | processor is in a low power state, the processor exits the                                                  |    |

|    |      | low power state if an electrical disconnect is                                                              |    |

|    |      | discontinued"                                                                                               | 50 |

|    | 3.   | Claim 10: "The system of claim 1, wherein the host                                                          |    |

|    |      | controller provides a peripheral bus interface for the                                                      |    |

|    |      | device"                                                                                                     | 51 |

|    | 4.   | Claim 11: "The system of claim 1, wherein electrically                                                      |    |

|    |      | disconnecting the device comprises electrically removing                                                    |    |

|    |      | a pull up resistor from a D+ line"                                                                          | 51 |

|    | 5.   | Claim 12: "The system of claim 1, wherein electrically                                                      |    |

|    |      | disconnecting the device comprises tri-stating a D+ line                                                    |    |

|    |      | and a D- line"                                                                                              | 52 |

|    | 6.   | Claim 13: "The system of claim 1, wherein the device                                                        |    |

|    |      | being electrically disconnected from the host controller                                                    |    |

|    |      | allows the processor to enter a low power state or remain                                                   |    |

|    |      | in a low power state"                                                                                       | 53 |

|    | 7.   | Claim 14                                                                                                    | 54 |

|       |      | 8.      | Claim 21: "The method of claim 14, wherein if no devices are coupled to the host controller the host        |    |

|-------|------|---------|-------------------------------------------------------------------------------------------------------------|----|

|       |      | 9.      | controller does not create bus activity"                                                                    |    |

|       |      | 10.     | device"                                                                                                     | 33 |

|       |      | 11.     | a pull up resistor from a D+ line"                                                                          | 55 |

|       |      | 12.     | and a D- line"                                                                                              |    |

|       |      | 13.     | Claim 50: "The memory medium of claim 45, wherein if no devices are coupled to the host controller the host |    |

|       |      | 14.     | controller does not create bus activity"                                                                    | 56 |

|       |      | 15.     | the device"                                                                                                 | 56 |

|       |      | 16.     | electrically removing a pull up resistor from a D+ line"                                                    | 56 |

|       |      |         | a D+ line and a D- line"                                                                                    |    |

|       |      | 17.     | Claims 57 and 58                                                                                            | 57 |

| VIII. | SECO | ONDA    | RY CONSIDERATIONS                                                                                           | 57 |

| IX.   | PTAE | B DISC  | CRETION SHOULD NOT PRECLUDE INSTITUTION                                                                     | 58 |

|       | A.   | Institu | ution Is Appropriate Under 35 U.S.C. §325(d)                                                                | 58 |

|       | B.   | Institu | ution Is Appropriate Under Fintiv                                                                           | 60 |

| X.    | MAN  | DATO    | ORY NOTICES                                                                                                 | 63 |

|       | A.   | Real    | Party-In-Interest                                                                                           | 63 |

|       | B.   | Relate  | ed Matters                                                                                                  | 63 |

|       | C.   | Coun    | sel Information                                                                                             | 64 |

|       | D.  | Service Information | .64 |

|-------|-----|---------------------|-----|

| XI.   | PAY | MENT OF FEES        | .64 |

| XII.  | CER | ΓΙFICATION          | .65 |

| XIII. | CON | CLUSION             | .65 |

## **TABLE OF AUTHORITIES**

|                                                                                                                             | Page(s)    |

|-----------------------------------------------------------------------------------------------------------------------------|------------|

| Cases                                                                                                                       |            |

| Advanced Bionics, LLC v. MED-EL Elektromedizinische Geräte GmbH,<br>Case IPR2019-01469, Paper 6 (P.T.A.B. Feb. 13, 2020)    | 58         |

| Apple Inc. v. Fintiv, Inc., IPR2020-00019, Paper 11 (P.T.A.B. Mar. 20, 2020)                                                | 60, 63     |

| Becton, Dickinson, & Co. v. B. Braun Melsungen AG, IPR2017-01586, Paper 8 (P.T.A.B. Dec. 15, 2017)                          | 58         |

| Bowtech, Inc. v. MCP IP, LLC,<br>IPR2019-00383, Paper 14 (P.T.A.B. Aug. 6, 2019)                                            | 59         |

| In re Huai-Hung Kao,<br>639 F.3d 1057 (Fed. Cir. 2011)                                                                      | 57         |

| MED-EL Elektromedizinische Geräte Ges.m.b.h. v. Advanced Bionics AG, IPR2021-00044, 2021 WL 1287684 (P.T.A.B. Apr. 6, 2021) | 62         |

| Ormco Corp. v. Align Tech., Inc.,<br>463 F.3d 1299 (Fed. Cir. 2006)                                                         | 57         |

| Philip Morris Prods., S.A. v. Rai Strategic Holdings, Inc., IPR2020-00919, Paper 9 (P.T.A.B. Nov. 16, 2020)                 | 63         |

| Phillips v. AWH Corp.,<br>415 F.3d 1303 (Fed. Cir. 2005)                                                                    | 13         |

| Samsung Elecs. Co., Ltd. v. BitMicro, LLC,<br>IPR2018-01410, Paper 14 (P.T.A.B. Jan. 23, 2019)                              | 60         |

| Samsung Elecs. Co., Ltd. v. Dynamics, Inc.,<br>No. IPR2020-00504, 2020 WL 6050685 (P.T.A.B. Oct. 13, 2020)                  | 60, 61, 63 |

| Tech. Gen. Corp. v. Genentech, Inc.,<br>80 F.3d 1553 (Fed. Cir. 1996)                                                       | 61         |

| Thryv, Inc v. Click-To-Call Techs., LP,<br>140 S. Ct. 1367 (2020)                                                           | 60         |

| Wyers v. Master Lock Co.,<br>616 F.3d 1231 (Fed. Cir. 2010)                                                                 | 57         |

| Other Authorities         |    |

|---------------------------|----|

| 37 C.F.R. § 42.100 (2018) | 13 |

# LIST OF EXHIBITS

| Exhibit No. | Description                                                                                                                                 |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1001        | U.S. Pat. No. 7,159,766 (the "'766 Patent")                                                                                                 |  |  |

| 1002        | File History of U.S. Pat. No. 7,159,766                                                                                                     |  |  |

| 1003        | Declaration of Declaration of R. Jacob Baker Ph.D., P.E. in Support of Petition for <i>Inter Partes</i> Review of U.S. Patent No. 7,159,766 |  |  |

| 1004        | Curriculum Vitae of Declaration of R. Jacob Baker Ph.D., P.E.                                                                               |  |  |

| 1005        | U.S. Pat. App. Pub. No. 2002/0138776 ("Cohen")                                                                                              |  |  |

| 1006        | U.S. Pat. No. 6,076,119 ("Maemura")                                                                                                         |  |  |

| 1007        | Universal Serial Bus Specification, Revision 2.0 ("USB 2.0")                                                                                |  |  |

| 1008        | U.S. Pat. No. 5,408,668 ("Tornai")                                                                                                          |  |  |

| 1009        | Declaration of Jeffrey L. Ravencraft                                                                                                        |  |  |

| 1010        | Notice of Institution of Investigation No. 337-TA-1280                                                                                      |  |  |

| 1011        | Respondents' Invalidity Contentions, 337-TA-1280                                                                                            |  |  |

| 1012        | Complainant's Motion for Partial Termination, 337-TA-1280                                                                                   |  |  |

| 1013        | Order No. 7: Setting Procedural Schedule, 337-TA-1280                                                                                       |  |  |

| 1014        | Order No. 5: Initial Determination Setting The Target Date At Seventeen Months, 337-TA-1280                                                 |  |  |

| 1015        | Order No. 6: Regarding Procedural Schedule, 337-TA-1280                                                                                     |  |  |

| 1016        | Universal Serial Bus Specification, Revision 1.0 ("USB 1.0")                                                                                |  |  |

| 1017        | Universal Serial Bus Specification, Revision 1.1 ("USB 1.1")                                                                                |  |  |

| 1018        | Declaration of Paul E. Berg                                                                                                                 |  |  |

| 1019        | Stipulation                                                                                                                                 |  |  |

| 1020        | U.S. Pat. No. 7,159,766 Claim Listing                                                                                                       |  |  |

Samsung Electronics Co., Ltd. and Samsung Electronics America, Inc. (collectively, "Samsung" or "Petitioner") request *inter partes* review of Claims 1, 3-6, 8, 10-14, 16, 19-21, 25-28, 39, 45, 47-50, 54-58, 60 ("Challenged Claims") of U.S. Patent No. 7,159,766 (the "'766 Patent") (Ex. 1001).

#### I. INTRODUCTION

The '766 Patent is directed to creating a disconnect condition under the USB standard when a USB device connected to a USB host controller becomes inactive. This disconnect, referred to in the '766 Patent as an "electrical disconnect," is created without unplugging or uncoupling the device from the host controller. Instead, an electrical state specified in the USB standard is created over the data lines between the device and the host controller that causes the host controller to make a determination that the device has been physically uncoupled from it when in fact it has not. The purported benefit of this scheme is that it results in power savings when the USB device is not active. As discussed below, however, this power-saving scheme was well-known in the prior art years before the January 20, 2004 priority date.

### II. OVERVIEW OF CHALLENGE AND RELIEF REQUESTED

Petitioner challenges the patentability of the Challenged Claims and requests that they be cancelled.

#### A. Prior Art Patents and Printed Publications

Petitioner's challenge is based on the following prior-art references:

- Cohen (Ex. 1005) U.S. Patent App. Pub. No. 2002/0138776 to Cohen *et al.*, published on September 26, 2002, is prior art under at least pre-AIA 35 U.S.C. § 102(a) and (b).

- Maemura (Ex. 1006) U.S. Patent No. 6,076,119 to Maemura *et al.*, issued on June 13, 2000, is prior art under at least pre-AIA 35 U.S.C. § 102(a) and (b).

- USB 2.0 (Ex. 1007) "Universal Serial Bus Specification," Revision 2.0 (2000), is prior art under at least pre-AIA 35 U.S.C. § 102(a) and (b).

- Tornai (Ex. 1008) U.S. Patent No. 5,408,668 to Tornai, issued on April 18, 1995, is prior art under at least pre-AIA 35 U.S.C. § 102(a) and (b).

- USB 1.0 (Ex. 1016) "Universal Serial Bus Specification," Revision 1.0 (1996), is prior art under at least pre-AIA 35 U.S.C. § 102(a) and (b).

### **B.** Relief Requested

Petitioner requests cancellation of the Challenged Claims as unpatentable under 35 U.S.C. § 103. The specific grounds of the challenge are set forth below, and are supported by the Declaration of R. Jacob Baker Ph.D., P.E. (Ex. 1003).

| Ground | Claims                                                                               | Proposed Statutory Rejection                                      |

|--------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Ι      | 1, 3, 6, 8, 10-11, 13-<br>14, 16, 21, 25-26, 28,<br>39, 45, 47, 50, 54-55,<br>57, 58 | Obvious under § 103 in view of Cohen and USB 2.0                  |

| II     | 4-5, 19, 20, 48-49, 60                                                               | Obvious under § 103 in view of Cohen, USB 2.0, and Tornai         |

| III    | 1, 6, 8, 10-14, 21, 25-<br>27, 45, 50, 54-58                                         | Obvious under § 103 in view of Maemura and USB 2.0 and/or USB 1.0 |

#### III. OVERVIEW OF THE TECHNOLOGY

The '766 Patent relates to the USB standard, and specifically to creating a USB disconnected state for purposes of power savings when a USB device connected to a host controller, such as a hub or peripheral device, becomes inactive. USB is a standardized, serial bus technology for connecting peripherals to computers. Ex. 1003 ¶39. The operative USB standard as of the 2004 priority date was the USB 2.0 standard, released in 2000. Ex. 1007, Cover.

# A. USB Architecture and Topology

The basic architecture of USB involves the connection of devices with a host, forming a USB system. Ex. 1007, 15-16; Ex. 1003 ¶39. A host refers to the computer system that manages the USB system, and the host communicates with the devices via an interface referred to as a host controller. Ex. 1007, 6; see also id., 15-84, 275-96. There is only one host controller in any USB system, which may be implemented in a combination of hardware, firmware, or software. *Id.* A hub that

is integrated within the host system and attached directly to the host controller is referred to as the "root hub." Ex. 1007, 8, 16.

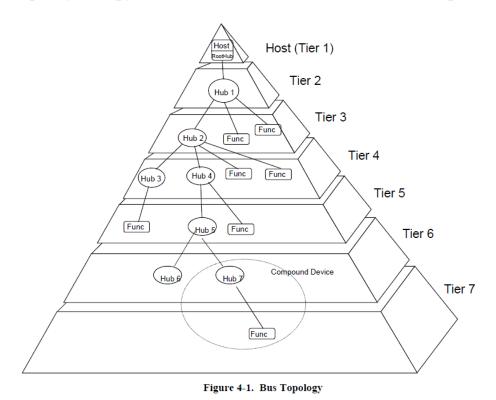

USB devices fall into two categories: hubs and functions. Ex. 1003 ¶40. Hubs provide attachment points to the USB bus, while functions are devices, such as a mouse or keyboard, that provide capabilities to the system. Ex. 1007, 4, 6, 17, 24. The USB topology is a pyramid, with the root hub and host at the top:

Ex. 1007, 16, Fig. 4-1. All devices connect to the host via the host controller directly or indirectly. Ex. 1007, 16, 29-30; Ex. 1003 ¶40.

# **B.** USB Cabling and Device Connections

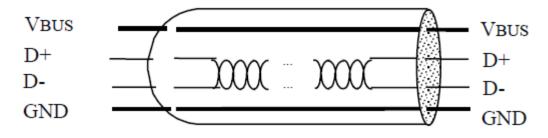

Per the USB standard operative years before the priority date, host controllers and devices are connected using a four-wire cable or connection:

Figure 4-2. USB Cable

Ex. 1007, 17-18, Fig. 4-2. D+ and D- are a pair of differential data lines, while  $V_{BUS}$  and GND are used to deliver power to USB devices. *Id.*; Ex. 1003 ¶41.

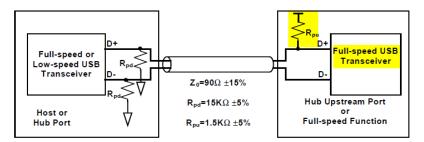

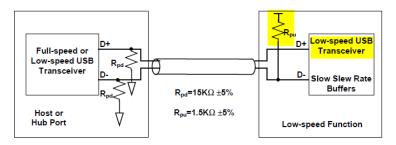

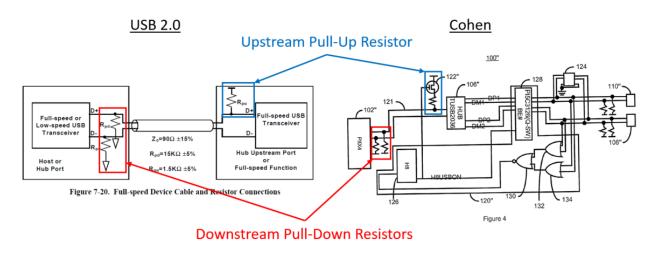

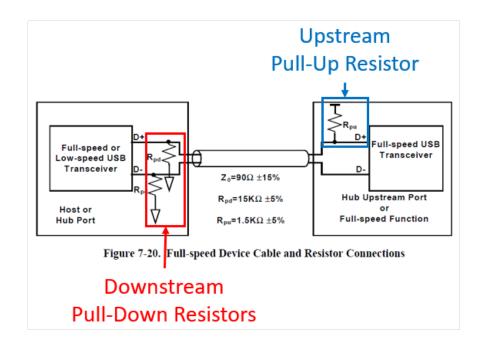

USB 2.0 permits USB devices to operate at three speeds: low-speed, full-speed, and high-speed. Ex. 1007, 1, 12, 17; Ex. 1003 ¶42. The manner in which a USB device connects to a USB host controller (or other upstream device) depends on the speed of the device. As shown in Figures 7-20 and 7-21 from USB 2.0, reproduced below, full-speed devices are terminated with a pull-up resistor, R<sub>pu</sub>, on the D+ line. Low-speed devices, on the other hand, are terminated with a pull-up resistor on the D- line. A "pull-up" resistor is a resistor connected to power that pulls the line into a high state, which USB 2.0 defines as greater than V<sub>IH</sub> (min) or 2.0 volts. Ex. 1007, 141, Table 7-7. Termination refers to "[p]assive components attached at the end of cables to prevent signals from being reflected or echoed." Ex. 1007, 9.

Figure 7-20. Full-speed Device Cable and Resistor Connections

Figure 7-21. Low-speed Device Cable and Resistor Connections

Ex. 1007, Figs. 7-20, 7-21 (annotated).

A host or other upstream USB device (left side of Figures 7-20 and 7-21) will assume a device is connected to it if either D+ or D- is pulled above a threshold value for a predetermined period of time, for example 2.0 volts for 2.5 µs. Ex. 1007, 149, Tables 7-7, 7-13; Ex. 1003 ¶43. Per the USB standard, a full-speed device will pull up this high voltage on the D+ line, while a low-speed device will pull up this high voltage on the D-. Ex. 1007, 141, Figs. 7-27, 7-28; Ex. 1003 ¶43. High-speed devices initially connect as full-speed devices, but then execute a specified low-level electrical protocol to transition to high-speed signaling. Ex. 1007, 151, 154; Ex. 1003 ¶43.

Assuming a successful connection, the host controller will monitor the voltage on the D+ and D- lines. Ex. 1007, 316. Per USB 2.0, if the host controller is not sending data to the device and the voltage drops below 0.8 volts on both D+ (full-speed) and D- (low-speed)—referred to in the USB standard as a "Single-ended 0," or SE0, state—for more than 2.5 μs, a "disconnect condition is indicated." Ex. 1007, 149, Tables 7-2, 7-7, 7-13; Ex. 1003 ¶44. In this condition, the host controller will assume that the device has been disconnected by unplugging or physically removing the connection to the device. *Id.* The USB 2.0 standard in Chapter 7 explains this as follows:

When no function is attached to the downstream facing port of a host or hub in low-/full-speed, the pull-down resistors present there will cause both D+ and D- to be pulled below the single-ended low threshold of the host or hub transceiver when that port is not being driven by the hub. This creates an SE0 state on the downstream facing port. A disconnect condition is indicated if the host or hub is not driving the data lines and an SE0 persists on a downstream facing port for more than TDDIS (see Figure 7-26). The specifications for TDDIS and TDCNN are defined in Table 7-13.

Ex. 1007, 149. Per the USB standard, the host controller handles these electrical interactions with the device on behalf of the host. *Id.*, 277.

A summary of the relationship between the D+ and D- levels on a USB connector and the port configurations discussed in this section is shown below:

| D+   | D-   | Port Configuration        |

|------|------|---------------------------|

| Low  | Low  | No device connected (SE0) |

| High | Low  | Full-Speed                |

| Low  | High | Low-Speed                 |

| High | High | Abnormal condition (SE1)  |

Ex. 1003 ¶45. These disconnect states are also specified in the USB 1.0 and 1.1 versions of the standard. Ex. 1016, 116; Ex. 1017, 134.

A disconnect of a high-speed device is determined "by sensing the doubling in differential signal amplitude across the D+ and D- lines that can occur when the device terminations are removed," *i.e.*, when the connecting cable is unplugged. Ex. 1007, 151; *see also id.*, 121, 140-41, Tables 7-1, 7-3; Ex. 1003 ¶46.

As discussed below, the '766 Patent creates a USB disconnect condition or state without unplugging any cables or physically removing a connection by manipulating the pull-up resistor and/or tri-state buffers to create a low voltage on the D+ and/or D- lines that they are connected to, for example, by removing the resistor or setting the buffers to a very high impedance, a well-known technique known as tri-stating. Ex. 1001, 6:5-11; Ex. 1003 ¶47. This effectively creates an open line condition at the host, which electrically mimics the unplugging of the cable from the USB device, and is interpreted by the host as such per the USB standard. Ex. 1007, 121-23, 149, Tables 7-1, 7-3; *see also id.*, 119-94, 309-18; Ex. 1003 ¶47.

As also discussed below, however, this electrical disconnect technique was well-known in the art before the 2004 priority date, and is disclosed in the Cohen reference, among many others.

### IV. U.S. PATENT NO. 7,159,766

The '766 Patent issued on January 9, 2007, from U.S. Application No. 10/762,767 (Ex. 1002, "the '767 Application"), which was filed on January 20, 2004.

#### A. Claims

The '766 Patent has 82 claims. Claims 1, 3-6, 8, 10-14, 16, 19-21, 25-28, 39, 45, 47-50, 54-58, 60 are challenged herein, of which six are independent.

### B. Specification

The '766 Patent purports to disclose a power-savings scheme whereby a USB device that is not active is electrically disconnected without unplugging or otherwise physically uncoupling the device from the host controller. This is done by manipulating the D+ and D- lines in order to artificially create a disconnect condition as specified in USB 2.0, which would ordinarily be created by unplugging the USB cable.

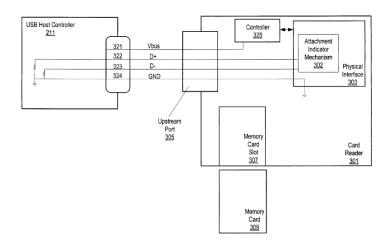

For example, Figure 3 of the '766 Patent reproduced below shows USB host controller 211 connected to USB card reader 301 by a standard USB cable having Vbus, D+, D-, and GND lines:

FIG. 3

Ex. 1001, Fig. 3.

As the '766 Patent explains, when memory card 309 is removed from the memory slot, the card reader becomes inactive because it is not performing any functions. According to the '766 Patent, because the card reader is now inactive, the electrical conditions on the data lines are manipulated in order create an electrical state that makes the host controller think that the card reader has been unplugged or physically disconnected when in fact it has not. The '766 Patent describes this process as follows:

In some embodiments, if no memory card 309 is inserted in the card reader 301 (i.e., the card reader 301 is not in an active state) or the card reader 301 is turned off, an algorithm (e.g., stored in firmware on the card reader 301) may be implemented in the card reader 301 to electrically disconnect the card reader 301 from the USB host controller 211. ... For full speed devices to electrically disconnect, the pull up resistor may be electrically removed (i.e., set to a high impedance or "tri-stated") from the D+ line. The USB host controller may interpret this as a disconnect. To electrically disconnect high speed

devices, the D+ and D- lines may both be tri-stated (set to a high impedance).

Ex. 1001, 5:60-6:11.

For full-speed USB devices, the '766 Patent teaches that electrically removing the pull-up resistor from the D+ line will be interpreted by the host controller as a physical disconnect, even though the host and device remain physically attached via the USB cable. Ex. 1001, 6:16-20; Ex. 1002, 80. As Dr. Baker explains, the host controller interprets this as a physical disconnect because electrically removing the D+ resistor has the effect of driving the D+ line low, creating an SE0 state. Ex. 1003 ¶51. This is precisely the disconnect state described in Section 7.1.7.3 of the USB 2.0 standard (and in section 7.1.4.1 of USB 1.0 and section 7.1.7.1 of USB 1.1), which a host controller is required to interpret as a physical disconnect. Ex. 1007, 141. For high-speed USB devices, the '766 Patent teaches to tri-state both the D+ and D- lines. Ex. 1001, 6:20-22. As Dr. Baker explains, this has the effect of creating an open line condition on the D+ and D- lines, which is what the USB 2.0 standard specifies for a disconnect condition in high-speed devices. Ex. 1003 ¶51.

Thus, the '766 Patent is doing nothing more than creating the disconnect states specified by the USB standard without physically disconnecting the device from the host controller, which the host controller interprets as a physical disconnect as required by the USB standard, even though the host and device are still physically connected. Ex. 1003 ¶52.

This interpretation by the host controller of a physical disconnect when none has occurred is captured in the claim element "wherein the device being electrically disconnected from the host controller causes an appearance to the host controller that the device is not coupled to the host controller." The only supporting disclosure in the '766 Patent is the reference to creating a USB disconnect state on the USB cable: "For full speed devices to electrically disconnect, the pull up resistor may be electrically removed (i.e., set to a high impedance or 'tri-stated') from the D+ line. *The USB host controller may interpret this as a disconnect.*" Ex. 1001, 6:16-20. There is no other supporting disclosure in the specification, and thus this element is merely recognizing the fact that a USB host controller will interpret an SE0 state as a physical disconnect, as specified in the USB standards.

# **C.** Summary of the Prosecution History

The application that led to the '766 Patent was filed on January 20, 2004. Ex. 1001, Cover; Ex. 1002, 201. The Applicant originally presented 59 claims. Ex. 1002, 201. Over the course of the prosecution, the Applicant amended many of the independent claims to overcome prior-art rejections. *Id.*, 47-58, 148-55. These amendments included the addition of limitations that recite "wherein the device being electrically disconnected from the host controller causes an appearance to the host controller that the device is not coupled to the host controller" and "wherein a sideband signal is used to signal the device to electrically reconnect after the device

has been electrically disconnected." *Id.* On October 6, 2006, the Examiner issued the Notice of Allowance. *Id.*, 20.

### D. Person of Ordinary Skill in the Art

As explained in Dr. Baker's declaration, a person of skill in the art as of January 20, 2004 (the earliest effective filing date of the '766 Patent) would have had at least a Bachelor's degree in Electrical Engineering, Computer Engineering, or an equivalent technical degree, and two or more years of experience with peripheral device interconnect technologies, such as USB. Additional education would compensate for less experience, and vice-versa. Ex. 1003 ¶37.

#### V. CLAIM CONSTRUCTION

Claim terms "shall be construed using the same claim construction standard that would be used to construe the claim in a civil action under 35 U.S.C. § 282(b)." 37 C.F.R. § 42.100(b) (2018); *Phillips v. AWH Corp.*, 415 F.3d 1303 (Fed. Cir. 2005) (en banc). Petitioner submits that the Board does not need to construe any claim term for purposes of evaluating the prior art in this Petition.<sup>1</sup>

While there are a number of claim-construction disputes in the pending ITC investigation, those issues are directed to Patent Owner's infringement allegations, and do not need to be addressed to resolve any of the invalidity issues presented here.

### VI. OVERVIEW OF THE PRIOR ART

#### A. Cohen

Cohen discloses a USB system in which a USB hub is connected to a host computer system. Ex. 1005, [0002], [0018], [0020]. If no devices are attached to the hub's downstream USB ports, such that the hub is inactive, then the hub is electrically disconnected from the host without physically disconnecting the hub from the host controller, just as described and claimed in the '766 Patent. *Id.*, Abstract, [0005], [0020]. But even though the host controller and hub are physically connected, the host controller believes they are not. *Id.* The benefit of this disconnection scheme is that it allows the host computer to enter a low power state when the hub is inactive, conserving power. *Id.*

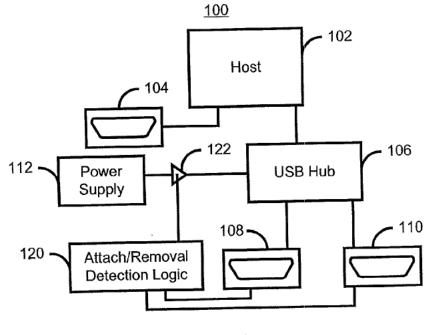

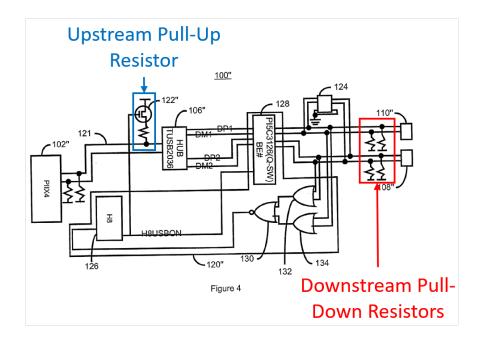

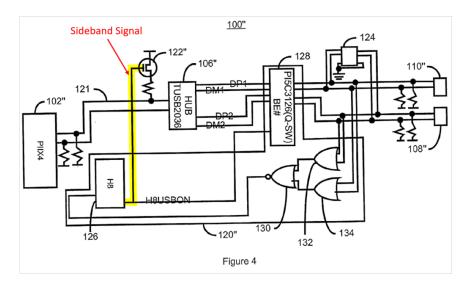

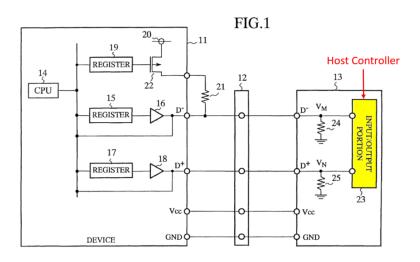

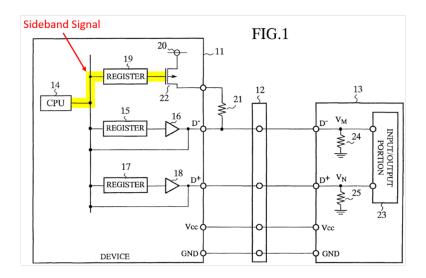

For example, Cohen discloses a USB system in Figure 2:

Figure 2

Ex. 1005, Fig. 2. The USB system includes host 102 connected to USB hub 106. The hub 106 includes ports 108 and 110 to which USB devices may connect. Ex. 1005, [0015]-[0016]. The hub also includes attach/removal detection logic 120, which detects when devices have been plugged into or unplugged from ports 108 and 110. *Id.* If devices have been removed from both ports, such that the hub has no function to perform and is therefore inactive, attach/removal detection logic 120 transmits a sideband signal (i.e., not over the USB bus) to the hub's connector 122, which disconnects hub 106 from its power supply. *Id.* As a result, the host 102 can no longer recognize that it is connected to hub 106, even though they are still connected by a USB cable. When a device is then connected to one of the ports, and the hub becomes active, attach/removal detection logic 120 signals the hub to reconnect the USB hub to power, which is then recognized by the USB host. Id., [0017].

Cohen discloses a second embodiment in Figures 3 and 4, with Figure 4 providing a detailed block diagram. Ex. 1005, [0020]. This embodiment is exactly the same disconnect scheme disclosed in the '766 Patent. As shown in Figure 4, USB hub 106" is connected to processor 102" inside a USB host via line 121. Because this is a USB system, a POSITA would understand that line 121 includes differential D+ and D- lines, per the USB standard. Ex. 1003 ¶55. A pull-up resistor is connected to one of the data lines in the hub, while pull-down resistors are

connected to the data lines in the host. *Id.*; Ex. 1005, Fig. 4. As the following side-by-side comparison shows, this architecture is exactly the same as that shown in the USB standard for a full-speed USB device or hub connected to a host, except for the presence of FET 122":

Ex. 1007, Fig. 7-20; Ex. 1005, Fig. 4 (annotated).

As Cohen explains, FET 122" allows the USB hub to be electrically disconnected from the host controller:

The connector 122" is a FET. Thus, the connector 122" is not a connector in the traditional sense of the word in that the connector 122" does not physically decouple the USB hub 106" from the processors 102". Instead, the connector 122" is a connector in the sense that it allows the USB hub 106" to be logically coupled or decoupled from the processor 102". When a USB device is connected to a USB connector 108" or 110", the attach/removal detection logic 120" provides a signal (H8USBON) that is on. When this signal is on, the FET 122" is turned on. Thus, the line 121 between the processors 102" and the USB hub 106" is driven high when a USB device is connected to one of the connectors 108" or 110". As a result, the USB hub 106" is connected to the processors 102" only when the USB connector 108" or 110" is in use. Thus, the processors 102" only recognize the USB hub 106" as a USB device when the USB connector 108" or 110" is

being used. At other times, the processors 102" behave as though the USB hub 106" is not present in the computer system 100".

Ex. 1005, [0020]. As Dr. Baker explains, this is exactly what the '766 Patent discloses when it states that, "[f]or full speed devices to electrically disconnect, the pull up resistor may be electrically removed (*i.e.*, set to a high impedance or "tristated") from the D+ line," and this is nothing more than creating an SE0 electrical state that the host controller interprets as a disconnect as required by the USB specification, even though the USB cable is still connected to the hub. Ex. 1003 ¶56. Cohen also discloses the use of a sideband signal, H8USBON, which signals the hub to reconnect to the USB host. Ex. 1005, [0020].

Cohen is not the only prior-art reference to make use of an artificially created USB disconnect state such as described and claimed in the '766 Patent. This technique was used in multiple other prior-art references including Maemura discussed below, demonstrating that it was well within the knowledge of a POSITA.

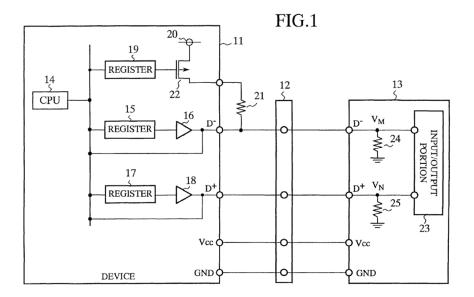

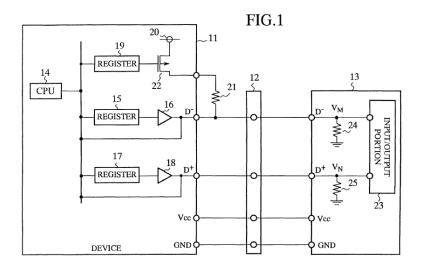

#### B. Maemura

Maemura discloses a USB system wherein "inoperative" devices are electrically disconnected from the USB host controller in order to save power. Ex. 1006, Abstract. Maemura explains that, in a conventional system, "even if the [USB peripheral] device 1 is inoperative in actuality, the host computer 5 must continue a communication processing like that carried out while the device 1 is operative as long as the device 1 is physically connected." *Id.*, 2:2-8. That is, even when a USB

peripheral device is not being used, its physical connection to the USB host controller causes power to be wasted by the processor of the host system.

To overcome this problem, Maemura discloses that, "when the [USB peripheral device 11 is physically connected to the host computer 13, but is actually inoperative," a switching circuit is used to disconnect the pull-up resistor on the D+ or D- line from its power source. *Id.*, 5:12-18, 7:64-67. As a result, the voltage on both of the data lines falls below a threshold voltage "V<sub>TH2</sub>" that the host controller uses to determine if a device has been physically disconnected (*id.*, 1:51-2:2, 5:19-25, Fig. 10B), creating the "SE0" condition that is defined as a disconnect in the USB standards. Ex. 1007, 149; Ex. 1003 ¶59. Per the USB standards, this causes the host controller to perceive the USB peripheral device as having been physically disconnected from it. *Id.* This in turn permits the processor in the host computer to enter a low power state. As a result, power is saved by reducing the processing load of the processor of the host system. Ex. 1006, 5:40-50.

Maemura's Figure 1, below, depicts peripheral device 11, USB connection 12, and host computer 13:

*Id.*, Fig. 1.

### C. USB 2.0

USB 2.0 was published on April 27, 2000 and is prior art under §102(b). Ex. 1007, Cover; Ex. 1009 ¶¶3-5. USB 2.0 sets forth various requirements of a USB system, including the bus attributes, protocol definition, types of transactions, bus management, and programming interface required to design and build systems and peripherals that are compliant with this standard. Ex. 1007, 1.

### D. USB 1.0

USB 1.0 was published on January 15, 1996 and is prior art under §102(b). Ex. 1016, Cover; Ex. 1018 ¶¶7-9. USB 1.0 is the original version of the USB standard.

#### E. Tornai

Tornai relates to power management in computer systems, and more specifically to removing power from inactive peripherals. Of particular relevance to certain dependent claims, Tornai discloses using a timer to make sure an inactive peripheral is truly inactive before disconnecting it from power. Ex. 1008, 3:19-35.

#### VII. SPECIFIC GROUNDS FOR PETITION

#### A. Ground I

Claims 1, 3, 6, 8, 10-11, 13-14, 16, 21, 25-26, 28, 39, 45, 47, 50, 54-55, and 57-58 are rendered obvious by Cohen, alone or in combination with the USB 2.0 standard.

A POSITA would have been motivated to combine the disclosures of Cohen with those of USB 2.0 because Cohen is specifically directed to a USB system (Ex. 1005, Abstract, [0001]-[0006]), and USB 2.0 was the operative version of the USB standard as of Cohen's 2001 filing date, and also the '766 Patent's January 2004 priority date. Ex. 1003 ¶64. Furthermore, a POSITA would have been motivated to look to USB 2.0 to better understand implementation details of the USB system described by Cohen, as it is an industry standard with which such a system would need to comply. *Id.* Moreover, a POSITA would have had a reasonable expectation of success in combining these complementary disclosures as doing so would have been well within the abilities of a POSITA and would have yielded predictable results without undue experimentation, given that Cohen discloses a USB system,

USB 2.0 discloses the requirements for such a system, and USB was a well-known and common standardized interconnect technology at the time. *Id*.

### 1. <u>Claim 1</u>

## a) 1[pre]: "A system, comprising:"

To the extent a limitation, Cohen discloses this preamble, as it discloses various examples of a USB "computer *system*" in Figures 1 through 4. Ex. 1005, [0007]-[0009], [0015], [0018], [0020], Figs. 2-4; Ex. 1003 ¶66.

### b) 1[a]: "a processor"

Cohen discloses a USB host that includes at least one processor: "A conventional computer system may include a host, a USB hub and multiple USB connectors integrated into a single unit. The host typically includes one or more integrated circuits, *including at least one processor*, that run an operating system ("OS") for the conventional computer system." Ex. 1005, [0012]. Cohen also discloses processors in the embodiments of Figures 2-4. *Id.*, [0017], [0019], [0020]; Ex. 1003 ¶67.

# c) 1[b]: "a host controller coupled to the processor"

Cohen renders this element obvious in view of USB 2.0. First, Cohen discloses a USB system, and a POSITA would understand and find obvious that Cohen's USB system contains a host controller. Ex. 1003 ¶68-69. For example, USB 2.0 explains that a USB system is *required* to have a host and a host controller, where the host is "[t]he host computer system where the USB Host Controller is

installed. This includes the host hardware platform (CPU, bus, etc.) and the operating system in use[,]" and the host controller is "[t]he host's USB interface." Ex. 1007, 6; see also id., 15-84, 275-96. USB 2.0 further explains that "[t]here is only one host in any USB system. The USB interface to the host computer system is referred to as the Host Controller." *Id.*, 16.

Second, a POSITA would understand that the host controller in Cohen is coupled to the processor in the host computer, where the term "coupled" is defined in the '766 Patent as directly or indirectly connected (Ex. 1001, 4:14-15), since the host controller is the interface to the host computer, and the host computer is controlled by its processor(s). Ex. 1003 ¶¶70-71. Indeed, the entire purpose of Cohen is to control power to the processor(s) in the host computer by disconnecting inactive USB devices, and this information must be reported to the processor through the USB host controller. A POSITA would thus understand and find obvious that there is at least an indirect connection between the host controller and the processor(s) in the host computer. Ex. 1003 ¶¶70-71.

### d) 1[c]: "a device coupled to the host controller"

Cohen discloses this element or renders it obvious in view of USB 2.0. Ex. 1003 ¶72. First, Cohen discloses a device in the form of a USB hub connected to a host computer, as shown in Figures 2 (hub 106 connected to host 102), 3 (hub 106' connected to host 102'), and 4 (hub 106" connected to host processor 102"). Ex.

1005, [0007]-[0009], [0015], [0018], [0020], Figs. 2-4. And as explained with respect to element 1[b], a POSITA would understand and find obvious that the USB hub is coupled to a host controller because, per USB 2.0, "[t]he USB host interacts with USB devices through the Host Controller." Ex. 1007, 24; see also, e.g., id., 15-84, 275-96, Figs. 4-1, 5-1, 5-5, 5-7.

Additionally, while Cohen refers to elements 106, 106', and 106" as "the USB hub," a POSITA would recognize that other elements disclosed by Cohen are part of the same device as the hub. As Dr. Baker explains, USB 2.0 requires that hubs have both upstream and downstream ports. Ex. 1003 ¶73; Ex. 1007, 22-23, 297. While the upstream ports are not labeled with an element number in Cohen, a POSITA would recognize USB connectors 108, 110, 108', 110', 108", and 110" as the hub's downstream ports. *Id.*; Ex. 1005, [0016], [0018], [0020], Figs. 2-4. Additionally, Dr. Baker explains that USB 2.0 requires that hubs include pull-down resistors on the downstream ports and a pull-up resistor on the upstream port. Ex. 1003 ¶74; Ex. 1007, 123, 141, Figs. 7-20, 7-21. These resistors can be seen in Figure 7-20 from USB 2.0 and Cohen's Figure 4, both of which are annotated below:

Ex. 1007, Figs. 7-20 (annotated).

Ex. 1005, Fig. 4 (annotated). A POSITA would thus understand that all of these elements are part of the same device as the hub. Ex. 1003 ¶74. Dr. Baker further explains that, based on the circuit diagram in Figure 4, a POSITA would have also

have recognized that connector 122" to be part of the hub device because it is in between the pull-up resistor and the port through which the resistor connects to power. *Id*.

Additionally, to the extent Complainant argues that the upstream ports, downstream ports, pull-up and pull-down resistors, or connecters 122, 122', and 122" are located outside of the hub, that argument is incorrect and beside the point. As Dr. Baker explains, a POSITA would find it obvious that all of these elements can be included in the hub device. Ex. 1003 ¶75. Indeed, there are only two possible locations for this circuitry, inside the hub or outside the hub. And as Dr. Baker explains, it would have been obvious to include these elements inside the hub device because it would simplify the implementation and allow all of the necessary connections to be made to a single device, rather than require multiple components to be assembled and connected. *Id.* Such an implementation would also have been well within the skill of a POSITA, who would have had a reasonable expectation of success implementing such a design with undue experimentation given that it is merely a routine issue of packaging known components. *Id*.

e) 1[d]: "wherein the device is electrically disconnected from the host controller if the device is not in an active state"

Cohen discloses this element or renders it obvious in view of USB 2.0. Ex. 1003 ¶¶76-80. For example, Cohen's embodiment of Figures 3 and 4 utilizes the very same method of electrical disconnection described in the '766 Patent by

creating an SE0 state as specified in USB 2.0—electrically removing the pull-up resistor from the D+ line. *See* Ex. 1001, 6:5-9. As Dr. Baker explains, in this embodiment, when no USB devices are connected to ports 108" and 110" of hub 106" via USB line 121, the hub is inactive because it is not performing any functions (the hub serves an attachment point for other USB devices and is inactive when no devices are connected; this is an example of inactivity provided in the '766 specification). Ex. 1003 ¶77. Attach/removal detection logic 120" causes FET 122" to disconnect the attached pull-up resistor from power, resulting in the hub 106" being electrically disconnected from the host controller. *Id.* On the other hand, when a device is connected to one of the ports of hub 106", the hub is performing its connection function, and the resistor is connected to power and pulled high, connecting the hub to the host controller. *Id.* Cohen explains as follows:

When a USB device is connected to a USB connector 108" or 110", the attach/removal detection logic 120" provides a signal (H8USBON) that is on. When this signal is on, the FET 122" is turned on. Thus, the line 121 between the processors 102" and the USB hub 106" is driven high when a USB device is connected to one of the connectors 108" or 110". As a result, the USB hub 106" is connected to the processors 102" only when the USB connector 108" or 110" is in use. Thus, the processors 102" only recognize the USB hub 106" as a USB device when the USB connector 108" or 110" is being used. At other times, the processors 102" behave as though the USB hub 106" is not present in the computer system 100".

Ex. 1005, [0020]; see also id., [0018]-[0019]. Because Cohen's device is a USB hub and is disconnected by creating an SE0 state, a POSITA would understand that it is

a full-speed USB device with the pull-up resistor connected to the D+ line, because USB hubs cannot be low-speed which would have the pull-up resistor connected to D-. Ex. 1007, 139, 141, 297, 318, Figs. 7-20, 7-21; Ex. 1003 ¶ 108.

As Dr. Baker explains, this constitutes an electrical disconnection in USB because the hub and host controller cannot communicate over the bus given that the host controller does not know the hub is there, even though they remain physically connected. Ex. 1003 ¶78. As Dr. Baker further explains, this is simply a consequence of the disconnect states defined in Section 7.1.7.3 of USB 2.0, and is precisely what happens in the USB embodiments disclosed in the '766 Patent. *Id.* By electrically removing the pull-up resistor from the D+ line, such that it no longer drives the data line to a high voltage, the host controller is unable to recognize the attached device, and this is deemed an electrical disconnection by the '766 Patent. This embodiment is essentially identical to an embodiment disclosed in the '766 Patent where a hub is "not in an active state" if no devices are attached to it. *See, e.g.*, Ex. 1001, 2:60-65, 7:46-61, 9:7-36, Fig. 8, claims 3, 16, 47.

Similarly, in connection with its Figure 2 embodiment, Cohen discloses that hub 106 will be electrically disconnected from the host controller when no devices are attached to hub ports 108 and 110, *i.e.*, when hub 106 is inactive. Ex. 1005, [0016]-[0017]; Ex. 1003 ¶80.

f) 1[e]: "wherein the device being electrically disconnected from the host controller causes an appearance to the host controller that the device is not

#### coupled to the host controller"

Cohen discloses this element or renders it obvious in view of USB 2.0. As Dr. Baker explains, both Cohen and the '766 Patent artificially create a USB disconnect state defined in Section 7.1.7.3 of USB 2.0 by manipulating the state of the interface between the USB device—a hub in the case of Cohen—and the host controller to create an electrical state that the host controller interprets as the device being physically unplugged, but without physically uncoupling them from each other. Ex. 1003 ¶¶81-82. This appearance of physical de-coupling is not an inventive feature of the '766 Patent, but merely the consequence of electrically creating a USB disconnect state. In other words, as Dr. Baker explains, a USB host controller by definition interprets a disconnect state as a physical de-coupling, because that is what the USB standard requires of it. Id., ¶44; Ex. 1007, 149. This is confirmed by Cohen itself, which explains that in a USB disconnected state, the hub is considered not to be present in the system, even though it remains physically attached to the host: "Thus, the processors 102" only recognize the USB hub 106" as a USB device when the USB connector 108" or 110" is being used. At other times, the processors 102" behave as though the USB hub 106" is not present in the computer system 100"." Ex. 1005, [0020]; see also id., [0016]-[0017] (discussing hub being unrecognized in Figure 2 embodiment). Indeed, the only support in the

'766 specification for this element is the references to the USB disconnect states. Ex. 1001, 5:39-56, 6:5-11.

### g) 1[f]: "wherein a sideband signal is used to signal the device to electrically reconnect after the device has been electrically disconnected"

This element is disclosed or rendered obvious by Cohen. Cohen discloses a signal from the attach/removal detection logic—element 120, 120, or 120", depending on the embodiment—which causes the hub to electrically reconnect to the host controller when a USB device is connected to either of the USB hub's downstream facing ports. Ex. 1005, [0016], [0018], [0020], Figs. 2-4. This signal is referred to as an H8USBON signal. As Cohen explains, this signal is used to connect Cohen's hub to the host when a device is plugged into one of its ports:

When a USB device is connected to a USB connector 108" or 110", the attach/removal detection logic 120" provides a signal (H8USBON) that is on. When this signal is on, the FET 122" is turned on. Thus, the line 121 between the processors 102" and the USB hub 106" is driven high when a USB device is connected to one of the connectors 108" or 110". As a result, the USB hub 106" is connected to the processors 102" only when the USB connector 108" or 110" is in use."

Ex. 1005, [0020]; see also id., [0016]-[0019]. By driving the data line to a high voltage, Cohen's hub electrically reconnects to the host controller. A POSITA would also understand and find obvious based on this disclosure that a device could be connected to one of the downstream ports of Cohen's hub after the hub had been electrically disconnected, thus causing it to reconnect. Ex. 1003 ¶83. The output from the attach/removal detection logic signals Cohen's hub because it causes the

hub to electrically reconnect by causing it to raise the voltage on the D+ line via the pull-up resistor in the Figure 3 and 4 embodiment, or causes the hub to re-connect to power in the Figure 2 embodiment. As discussed in Section VII.A.1.d) above, connectors 122, 122′, and 122″ that receive this signal are part of the same device as the hub. It is also obvious to a POSITA to include them in the same device, for the reasons discussed in Section VII.A.1.d).

Further, as Dr. Baker explains, in all of the embodiments, the signal from the attach/removal detection logic is a "sideband signal" because it is transmitted over an electrical pathway that is separate from the USB connection between the host controller and the USB hub. Ex. 1003 ¶86; Ex. 1005, Figs. 2-4. This can be seen in Figure 4 of Cohen, where H8USBON is transmitted over a connection other than the USB connection 121 between the hub and host. *Id*.

Ex. 1005, Fig. 4 (annotated).

### 2. Claim 3: "The system of claim 1, wherein the device is a hub and the active state comprises a second device attached to the hub"

Claim 1 is obvious as discussed above and Cohen further discloses this element. As explained with regard to elements 1[c] and 1[d], Cohen discloses a USB hub that is "in an active state" when a device is attached to one of its downstream ports. Ex. 1005, Abstract, [0001], [0005], [0008]-[0010], [0012]-[0013], [0015]-[0020], Figs. 2-4; Ex. 1003 ¶101.

## 3. Claim 6: "The system of claim 1, wherein when the device is electrically disconnected from the host controller, the device does not cause bus activity"

Claim 1 is obvious as discussed above. Cohen further discloses this element or renders it obvious in view of USB 2.0. As explained with regard to elements 1[d] and 1[e], when Cohen's hub is electrically disconnected from the host controller, it does not cause bus activity because it is "logically decoupled" from and not recognized by the host, in which state it cannot communicate over the USB bus. Ex. 1005, Abstract, [0005], [0013], [0016]-[0020]; Ex. 1003 ¶102.

### 4. Claim 8: "The system of claim 1, wherein if the processor is in a low power state, the processor exits the low power state if an electrical disconnect is discontinued"

Claim 1 is obvious as discussed above. Cohen further discloses this element or renders it obvious in view of USB 2.0. Ex. 1003 ¶¶103-106. As Cohen describes and teaches, when a device is connected to one of Cohen's hub ports, the processor cannot be in a low power state. As discussed above, Cohen discloses discontinuing

an electrical connection by connecting the pull-up resistor on the data lines to connect to the pull-up power supply, electrically connecting the hub to the host controller. Ex. 1005, [0020]. From the perspective of the host controller, this is equivalent to connecting Cohen's hub to a USB port on the host computer, and would cause the processor in the host computer to exit a low power state. Ex. 1003 ¶104. Indeed, Cohen explains that "the processors 102" only recognize the USB hub 106" as a USB device when the USB connector 108" or 110" is being used." Ex. 1005, [0020]. A POSITA would understand that the processors in Cohen's system must exit the low power state in order to recognize the USB hub, and that when devices are plugged into Cohen's hub, the processor will not maintain a low power state. Ex. 1003 ¶105.

In addition, a POSITA would have recognized that, pursuant to USB 2.0, the connection of a device to a USB port may generate "a resume signal" that causes the processor in a host system to exit a low power state. Ex. 1007, 156, 280, 282; Ex. 1003 ¶106. As Dr. Baker describes, it would have been obvious to a POSITA to use such a resume signal with Cohen, because enabling device initiated wake-up signaling provides added convenience for users of USB systems. *Id.* A POSITA would have had reasonable success in implementing a resume signal with Cohen because this was a well-understood functionality common in USB systems and with which a POSITA would have been familiar. *Id.*; Ex. 1007, 156, 308.

### 5. Claim 10: "The system of claim 1, wherein the host controller provides a peripheral bus interface for the device"

Claim 1 is obvious as discussed above. Also as discussed with regard to element 1[b], a USB host controller is an interface to the host, and Cohen's hub connects to the host through the host controller via the USB bus. Ex. 1003 ¶107; Ex. 1007, 16; see also id., 15-84, 275-96.

## 6. Claim 11: "The system of claim 1, wherein electrically disconnecting the device comprises electrically removing a pull up resistor from a D+ line"

Claim 1 is obvious as discussed above. Cohen further discloses this element or renders it obvious in view of USB 2.0. Cohen discloses the use of FET 122" to electrically remove the pull-up resistor shown in Figure 4 from the D+ line. Ex. 1005, [0020], Fig. 4; Ex. 1003 ¶108. This is done by removing the connection between the resistor and power, which has the effect of rendering the resistor electrically disconnected, because it has no electrical influence on the D+ line. To the extent Patent Owner contends that Cohen does not explicitly refer to a D+ line, a POSITA would have found it obvious in view of USB 2.0. Ex. 1003 ¶108. Cable 121 is a USB cable (see Ex. 1005, [0012], [0020]) and, as discussed in the background section above, a POSITA would understand that a USB cable includes a D+ line. Ex. 1007, 17-18, Fig. 4-2. Further, in USB 2.0 (as in earlier versions), the upstream port of a hub *must* include a pull-up resistor on the D+ line, and not on the D- line. *Id.*, 139, 141, 297, 318, Figs. 7-20, 7-21; Ex. 1003 ¶108.

# 7. Claim 13: "The system of claim 1, wherein the device being electrically disconnected from the host controller allows the processor to enter a low power state or remain in a low power state"

Claim 1 is obvious as discussed above. Cohen further discloses this element or renders it obvious: "At other times, the processors 102" behave as though the USB hub 106" is not present in the computer system 100". Therefore, the processors 102" can enter a lowest power state when the USB connectors 108" and 110" are not in use." Ex. 1005, [0020]; see also id., [0003], [0017], [0019]. Furthermore, as Dr. Baker explains, allowing the processor to enter or remain in a low power state is not a separate inventive element or step described in the '766 Patent specification. Ex. 1003 ¶109. Rather, it is simply a consequence of causing an appearance to the host controller that the device is no longer coupled, as claimed in the independent claim. See Ex. 1001, 2:36-42.

#### 8. <u>Claim 14</u>

#### a) 14[pre]: "A method:"

As discussed with regard to claim 1, Cohen discloses a system and method for electrically disconnecting and reconnecting a USB hub to a USB host based on whether there are any devices attached to the host. *See, e.g.*, Ex. 1005, Title, Abstract, [0001], [0005]-[0006]; Ex. 1003 ¶87.

#### b) 14[a]: "detecting whether a device coupled to a host controller is in an

#### active state"

Cohen discloses detecting whether the USB hub device—which, as explained with respect to element 1[c], is coupled to a host controller—is an active state by determining whether there are any USB devices attached to its downstream ports. Ex. 1005, [0005]; *see also id.*, Abstract, [0013], [0016], [0018], [0020], Figs. 2-4; Ex. 1001, 9:7-36, Fig. 8, claims 3, 16, 47; Ex. 1003 ¶88.

- c) 14[b]: "if the device is not in an active state, electrically disconnecting the device from a host controller, wherein electrically disconnecting the device from the host controller causes an appearance to the host controller that the device is not coupled to the host controller"

- See element 1[d] above.

- d) 14[c]: "wherein electrically disconnecting the device from the host controller causes an appearance to the host controller that the device is not coupled to the host controller"

- See element 1[e] above.

- e) 14[d]: "if the device is in an active state, maintaining an electrical connection between the device and the host controller"

Cohen discloses that, if a device is attached to one of the USB hub's downstream ports, *i.e.*, the hub is in an active state, then the electrical connection between the hub and host controller will be maintained, *i.e.*, there will be no electrical disconnection. Ex. 1005, [0017]; *see also id.*, Abstract, [0005], [0013], [0016], [0018]-[0020]. As explained with respect to element 1[c], a POSITA would recognize and find obvious that Cohen's hub is coupled to the host through a USB host controller. Ex. 1003 ¶¶72, 91.

f) 14[e]: "electrically reconnecting the device using a sideband signal after the device has been electrically disconnected"

See element 1[f] above.

9. Claim 16: "The method of claim 14, wherein the device is a hub, and the active state comprises a second device coupled to the hub"

See claim 3.

10. Claim 21: "The method of claim 14, wherein if no devices are coupled to the host controller the host controller does not create bus activity"

Claim 14 is obvious as discussed above. In addition, a POSITA would have found the additional element of claim 21 obvious because, if there are no devices coupled to the host controller, there are no devices with which the host controller can communicate over the bus. Ex. 1003 ¶110.

11. Claim 25: "The method of claim 14, wherein the host controller provides a peripheral bus interface for the device"

See claim 10.

12. Claim 26: "The method of claim 14, wherein electrically disconnecting the device comprises electrically removing a pull up resistor from a D+ line"

See claim 11.

#### 13. <u>Claim 28</u>

Claim 28 is obvious over Cohen and USB 2.0. Ex. 1003 ¶¶93-95. Claim 28 is very similar to claim 1, and the analysis of claim 1 is incorporated herein by reference. Claim 28 specifically requires device detect logic and auto detach logic,

which are disclosed by Cohen in the form of attach/removal detection logic. Ex. 1005, Abstract, [0005], [0013], [0015]-[0020], Figs. 2-4. Cohen also discloses the additional hub requirement, as explained with regard to claim 3. *Id.*; *see also id.*, [0001], [0008]-[0010], [0012].

#### 14. Claim 39

Claim 39 is obvious. Ex. 1003 ¶96. Claim 39 is a method claim that tracks claim 14, except that it specifies the device as a hub, the active state as a device being connected to the hub, and the inactive state as no device connected to the hub. These elements are all disclosed by Cohen. Ex. 1005, Abstract, [0001], [0005], [0008]-[0010], [0012]-[0013], [0015]-[0020], Figs. 2-4.

#### 15. <u>Claim 45</u>

Claim 45 is a "computer accessible memory medium" claim whose elements are mirrored in method claim 14, and is obvious for the same reasons claim 14 is obvious. Ex. 1003 ¶97. In addition, to the extent the preamble is limiting, it would have been obvious to a POSITA that Cohen's invention could be implemented using processor executable program instructions stored in a computer accessible memory medium—which the '766 Patent broadly defines to include many different types of memory mediums and combinations of those mediums. Ex. 1001, 10:13-46. As Dr. Baker explains, it would have been obvious to a POSITA that the attach/removal detection logic could be implemented in processor executable program instructions,

for example firmware on Cohen's integrated circuits 126 and 128, which would be stored in a computer accessible memory medium. Ex. 1005, [0020]. Such processor executable implementations were common, well-known, and well within the capabilities of a POSITA. Ex. 1003 ¶98-99. Furthermore, such implementations had benefits in the form of simplicity and reconfigurability, as changes could be implemented without removing or replacing hardware. *Id*.

16. Claim 47: "The memory medium of claim 45, wherein the device is a hub, and the active state comprises a second device coupled to the hub"

See claim 3.

17. Claim 50: "The memory medium of claim 45, wherein if no devices are coupled to the host controller the host controller does not create bus activity"

See claim 21.

18. Claim 54: "The memory medium of claim 45, wherein the host controller provides a peripheral bus interface for the device"

See claim 10.

19. Claim 55: "The memory medium of claim 45, wherein electrically disconnecting the device comprises electrically removing a pull up resistor from a D+ line"

See claim 11.

#### 20. Claims 57 and 58

Claim 57 is the same as claim 1, minus the "causes an appearance" limitation, and dependent claim 58 includes that additional limitation. Both claims are obvious for the same reasons as claim 1. Ex. 1003 ¶¶ 100, 111.

#### B. Ground 2

Claims 4-5, 19, 20, 48-49, and 60 are rendered obvious by Cohen in combination with the USB 2.0 standard and Tornai.

#### 1. Claims 5, 20, and 49

Claim 5, 20, and 49 are all invalid as obvious over Cohen, USB 2.0, and Tornai. Ex. 1003 ¶¶117-119. These claims depend from claims 1, 14 and 45, respectively, which are obvious for the reasons explained in Ground 1. These claims all recite the additional element "wherein if the device is not in an active state, the device is electrically disconnected after a wait period, wherein if the device becomes active during the wait period, the device is not electrically disconnected." This element is obvious in view of Tornai.

Like Cohen, Tornai relates to power management in computer systems, and more specifically to removing power from an inactive peripheral device "when it is not needed in order to minimize the power consumed by the peripheral." Ex. 1008, Abstract. Tornai discloses the common-sense notion of using a timer to make sure an inactive peripheral is truly inactive before disconnecting it from power. As Tornai explains:

[P]rocessor 14 continues to process the various input signals received on input port 12 to determine whether any of the peripherals are no longer needed, and thus, should be deactivated. If processor 14 determines that a particular peripheral is no longer being used, it starts a timer having a selected time limit. After starting the timer, processor 14 monitors the input signals for input signal activity, and if signal activity is detected, the timer is reset and the peripheral remains on. However, if no input signal activity is detected before the expiration of the time limit, processor 14 generates and sends a deactivation signal to the connection circuit 16 to cause the circuit 16 to disconnect the appropriate peripheral from the power source. Hence, the apparatus 10 automatically and efficiently deactivates idle peripherals to prevent the unnecessary consumption of energy.

Ex. 1008, 3:19-35; see also id, Abstract, 2:22-39.

As Dr. Baker explains, a POSITA would be motivated to combine this teaching from Tornai with Cohen, as they disclose complementary methods of accomplishing the same goal. Ex. 1003 ¶¶113. First, a POSITA would have found it obvious to utilize the timers described by Tornai to ensure that Cohen's hub is actually inactive (*i.e.*, that a user has not removed the devices from the downstream ports and immediately replaced them with other devices) before it is electrically disconnected, so that the hub does not need to be unnecessarily re-enumerated (*i.e.*, identified and allocated resources by the host controller) seconds after it has been disconnected. *Id.*, ¶114.

Second, while Cohen describes a solution to the problem of power that is wasted when no devices are coupled to a hub, a POSITA would have recognized that just as much, if not more, power is wasted when completely inactive devices are

coupled to the hub. Ex. 1003 ¶115. A POSITA would have recognized that electrically disconnecting a hub from the host controller when there are no devices attached to its downstream ports *and* when devices attached to the downstream ports are inactive would enable the processor in the host to enter its lowest power state more often, which is Cohen's stated goal, saving even more power than Cohen's solution alone. *Id.*; Ex. 1005, [0003]-[0006]. In addition, a POSITA would have recognized the benefits of Tornai's timer feature, which prevents the disconnection of devices that are not actually inactive, minimizing disruptions to the system and the user. Ex. 1003 ¶113.

Further, a POSITA would have had a reasonable expectation of success in combining these complementary disclosures as doing so would have been well within the abilities of a POSITA—the trivial implementation of a timer—and would have yielded predictable results without undue experimentation. *Id.*, ¶116. As Dr. Baker explains, all of the necessary hardware is already provided by Cohen as the USB standard requires that hubs implement timers on their downstream facing ports, and Cohen's design includes circuitry to monitor the activity on the downstream data lines. *Id.* (citing Ex. 1007, 316; Ex. 1005, Fig. 4). A POSITA would only need to modify some programming to start the timers when the downstream data lines are in an idle state or disconnected (SE0) state, which would have been well within the capabilities of a POSITA. *Id.*

#### 2. <u>Claim 60</u>

Claim 60 depends from claim 57, which was shown to be obvious above. Claim 60 adds a limitation that requires "wherein the device is not in an active state if the device has not been used in a specified amount of time." This element is obvious for the same reasons as Claims 5, 20, and 49. Ex. 1003 ¶120-121.

#### 3. Claims 4, 19, and 48

Claims 4, 19, 48, and 60 are all invalid as obvious over Cohen, USB 2.0, and Tornai. Ex. 1003 ¶122. These claims depend from claims 1, 14 and 45, respectively, which are obvious for the reasons explained in Ground 1. These claims are similar to claim 60, and all require "wherein the device is not in an active state if the device has not been used in a second specified amount of time." In the parallel ITC investigation, Sonrai has taken the position that use of the word "second" in this limitation is a typographical error, because there is no "first" period of time specified in these claims or the claims from which they depend. Under this view, these claims are invalid as obvious for the same reasons as claim 60.

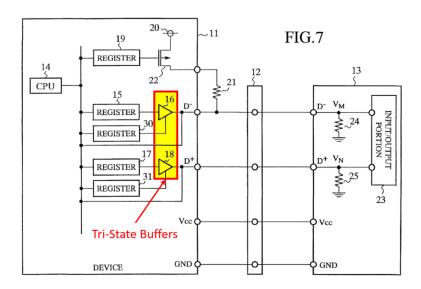

#### C. Ground 3

Claims 1, 6, 8, 10-14, 21, 25-27, 45, 50, and 54-58 are rendered obvious by Maemura in view of USB 2.0 and/or USB 1.0.

A POSITA would have found been motivated to combine the disclosures of Maemura with those of USB 2.0 and/or USB 1.0 because Maemura states explicitly that its invention operates "according to the USB (Universal Serial Bus Specification