### UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_

### BEFORE THE PATENT TRIAL AND APPEAL BOARD

SOLAREDGE TECHNOLOGIES LTD., Petitioner,

v.

KOOLBRIDGE SOLAR, INC., Patent Owner.

Patent No. 8,937,822 Filing Date: May 8, 2011 Issue Date: January 20, 2015

Title: SOLAR ENERGY CONVERSION AND UTILIZATION SYSTEM

Inter Partes Review No.: IPR2022-00008

PETITION 2 of 6 FOR *INTER PARTES* REVIEW UNDER 35 U.S.C. §§ 311-319 AND 37 C.F.R. § 42.100 et seq

## TABLE OF CONTENTS

| EXH  | IIBITS                                                        | •••••                              |                                                                                                                                      | iii |  |

|------|---------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| MA   | NDAT                                                          | ORY N                              | NOTICES                                                                                                                              | i   |  |

| I.   | INTF                                                          | INTRODUCTION & RELIEF REQUESTED1   |                                                                                                                                      |     |  |

| II.  | GRO                                                           | UNDS                               | FOR STANDING & FEE PAYMENT                                                                                                           | 2   |  |

| III. | OVERVIEW2                                                     |                                    |                                                                                                                                      |     |  |

|      | A.                                                            | Brief                              | Description of Alleged Invention                                                                                                     | 2   |  |

|      | B.                                                            | Prose                              | ecution History                                                                                                                      |     |  |

|      | C.                                                            | Scope and Content of the Prior Art |                                                                                                                                      | 6   |  |

|      |                                                               | 1.                                 | Japanese Patent Publication No. 2006-238630A ("Mori") (Ex. 1220, certified translation Ex. 1204)                                     | 6   |  |

|      |                                                               | 2.                                 | Tolbert, Multilevel Converters for Large Electric Drives, IEEE Trans. Ind. Apps., Vol 35, No. 1, Jan/Feb 1999 ("Tolbert") (Ex. 1244) | 8   |  |

|      |                                                               | 3.                                 | U.S. Pat. App. Pub. No. 2007/0278988 ("De") (Ex. 1218)                                                                               | .10 |  |

|      |                                                               | 4.                                 | U.S. Patent Application Publication No. 2008/0192519 ("Iwata") (Ex. 1207)                                                            | .11 |  |

|      |                                                               | 5.                                 | Japanese Pat. App. Pub. No. JP 11-122819 ("Fujimoto") (Ex. 1233, certified translation Ex. 1234)                                     | .13 |  |

|      |                                                               | 6.                                 | U.S. Patent No. 6,112,158 ("Bond") (Ex. 1235)                                                                                        | .14 |  |

|      |                                                               | 7.                                 | U.S. Patent Application Publication No. 2009/0086520 ("Nishimura") (Ex. 1208)                                                        | .15 |  |

| IV.  | IDENTIFICATION OF CHALLENGE PURSUANT TO 37 C.F.R. § 42.104(b) |                                    |                                                                                                                                      | .16 |  |

|      | A.                                                            | Leve                               | l of Ordinary Skill                                                                                                                  | .17 |  |

|      | B.                                                            | Clain                              | n Construction                                                                                                                       | .17 |  |

|      |                                                               | 1.                                 | "DC to AC converter" (Claim 1)                                                                                                       | 18  |  |

|      |                                                               | 2.                                 | "A switch[ing] controller" (Claims 2 and 5)                                                                                          | .19 |  |

|      |                                                               | 3.                                 | "AC ground leak detector" (Claim 4)                                                                                                  | .20 |  |

|      |                                                               | 4.                                 | "bidirectional DC-to-DC converter" (Claims 5, 13)                                                                                    | .20 |  |

|                  |        | 5.      | "common-mode filter" (Claim 6)                                                                        | 21                                              |

|------------------|--------|---------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| V.               | SPEC   | CIFIC ( | GROUNDS FOR UNPATENTABILITY                                                                           | 23                                              |

|                  | A.     |         | nds 1-3: Mori Anticipates, and Mori Alone or in View of ert Renders Obvious, Claims 1-3, 8-10, and 12 | 23                                              |

|                  |        | 1.      | Independent Claim 1                                                                                   | 23                                              |

|                  |        | 2.      | Independent Claim 8                                                                                   | 39                                              |

|                  |        | 3.      | Dependent Claim 2                                                                                     | 46                                              |

|                  |        | 4.      | Dependent Claims 3 and 9                                                                              | 51                                              |

|                  |        | 5.      | Dependent Claim 10                                                                                    | 52                                              |

|                  |        | 6.      | Dependent Claim 12                                                                                    | 53                                              |

|                  | B.     |         | nds 4, 5: Mori/Mori-Tolbert in view of De Renders Claims 6<br>0 Obvious                               | 59                                              |

|                  |        | 1.      | Dependent Claim 6                                                                                     | 59                                              |

|                  |        | 2.      | Dependent Claim 20                                                                                    | 63                                              |

|                  | C.     |         | nds 6, 7: Mori/Mori-Tolbert in View of Fujimoto Renders as 4 and 11 Obvious                           | 66                                              |

|                  |        | 1.      | Dependent Claims 4 and 11                                                                             | 66                                              |

|                  | D.     |         | nds 8, 9: Mori/Mori-Tolbert in View of Bond Renders Claim vious                                       | 71                                              |

|                  |        | 1.      | Dependent Claim 7                                                                                     | 71                                              |

|                  | E.     |         | nds 10, 11: Mori/Mori-Tolbert in View of Iwata and mura Renders Claims 5 and 13 Obvious               | Colbert in view of De Renders Claims 6       59 |

|                  |        | 1.      | Dependent Claim 5                                                                                     | 75                                              |

|                  |        | 2.      | Dependent Claim 13                                                                                    | 86                                              |

|                  | F.     | CON     | CLUSION                                                                                               | 88                                              |

| CERT             | ΓIFICA | ATION   | UNDER 37 CFR § 42.24(d)                                                                               | 89                                              |

| CERT             | ΓIFIC  | ATE O   | F SERVICE                                                                                             | 90                                              |

| $CI$ $\lambda I$ | MIT    | TING    | ADDENINIY                                                                                             | 01                                              |

### **EXHIBITS**

| Ex. 1201: | U.S. Patent No. 8,937,822 ("the '822 patent")                                                                                                                                                                                       |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ex. 1202: | Expert Declaration of Dr. R. Jacob Baker                                                                                                                                                                                            |  |  |

| Ex. 1203: | U.S. Patent No. 7,046,534 ("Schmidt")                                                                                                                                                                                               |  |  |

| Ex. 1204: | Certified translation of Japanese Patent Application Publication No. 2006-238630 ("Mori")                                                                                                                                           |  |  |

| Ex. 1205: | U.S. Patent No. 7,088,601 ("Tracy")                                                                                                                                                                                                 |  |  |

| Ex. 1206: | Reserved                                                                                                                                                                                                                            |  |  |

| Ex. 1207: | U.S. Patent Application Publication No. 2008/0192519 ("Iwata")                                                                                                                                                                      |  |  |

| Ex. 1208: | U.S. Patent Application Publication No. 2009/0086520 ("Nishimura")                                                                                                                                                                  |  |  |

| Ex. 1209: | Reserved                                                                                                                                                                                                                            |  |  |

| Ex. 1210: | K. H. Ahmed, S. J. Finney and B. W. Williams, <i>Passive Filter Design for Three-Phase Inverter Interfacing in Distributed Generation</i> , <i>Compatibility in Power Electronics</i> , CPE 2007, IEEE, pp. 1-9, 2007 ("Ahmed")     |  |  |

| Ex. 1211: | Reserved                                                                                                                                                                                                                            |  |  |

| Ex. 1212: | Mohan, N., Power Electronics: Converters Applications and Design (2nd Ed. John Wiley & Sons. Inc.) ("Mohan")                                                                                                                        |  |  |

| Ex. 1213: | U.S. Patent Application Pub. No. 2011/0255316 ("Burger")                                                                                                                                                                            |  |  |

| Ex. 1214: | Reserved                                                                                                                                                                                                                            |  |  |

| Ex. 1215: | Araújo, S. Highly Efficient Single-Phase Transformerless Inverters for Grid-Connected Photovoltaic Systems, IEEE Trans. on Industrial Elecs, vol. 57, no. 9 (Sept. 2010)                                                            |  |  |

| Ex. 1216: | Certified translation of Ex. 1246, Myrzik, J. Topologische Untersuchungen zur Anwendung von tief/-hochsetzenden Stellern für Wechselrichter, Dissertation zur Erlangung des Grades eines Doktor-Ingenieurs (Dr. ing.) im Fachgebiet |  |  |

|                | Elektrotechnik der Universität Gesamthochschule Kassel (2001, Kassel Univ. Press)                                                                                                                                   |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ex. 1217:      | Patel, H., Generalized Techniques of Harmonic Elimination and Voltage Control in Thyristor Inverters: Part I-Harmonic Elimination, IEEE Trans. on Industry Applications, Vol. 1A-9, No. 3 (May/June 1973) ("Patel") |  |  |

| Ex. 1218:      | U.S. Patent Application Publication No. 2007/0278988 ("De")                                                                                                                                                         |  |  |

| Ex. 1219:      | Mark W. Earley Ed., <i>National Electrical Code</i> ® <i>Handbook</i> , Eleventh Edition, 2008                                                                                                                      |  |  |

| Ex. 1220:      | Japanese Patent Application Publication No. 2006-238630 ("Mori")                                                                                                                                                    |  |  |

| Ex. 1221:      | Reserved                                                                                                                                                                                                            |  |  |

| Ex. 1222:      | Certified Prosecution History for the U.S. Patent No. 8,937,822                                                                                                                                                     |  |  |

| Ex. 1223:      | Declaration of James Mullins                                                                                                                                                                                        |  |  |

| Ex. 1224:      | U.S. Patent Application Publication No. 2009/0207543 ("Boniface")                                                                                                                                                   |  |  |

| Ex. 1225-1227: | Reserved                                                                                                                                                                                                            |  |  |

| Ex. 1228:      | U.S. Patent Application Publication No. 2008/0080106 ("Mirafzal")                                                                                                                                                   |  |  |

| Ex. 1229:      | Reserved                                                                                                                                                                                                            |  |  |

| Ex. 1230:      | Japanese Pat. App. Pub. No. P2004-7941A ("Suzuki")                                                                                                                                                                  |  |  |

| Ex. 1231:      | Certified Translation of Exhibit, 1230, Japanese Patent Application Publication No. P2004-7941A ("Suzuki")                                                                                                          |  |  |

| Ex. 1232:      | U.S. Patent No. 5,029,064 ("Ball")                                                                                                                                                                                  |  |  |

| Ex. 1233:      | Japanese Patent Application Publication No. JP 11-122819 ("Fujimoto")                                                                                                                                               |  |  |

| Ex. 1234:      | Certified Translation of Ex. 1233, Japanese Patent Application Publication No. JP 11-122819 ("Fujimoto")                                                                                                            |  |  |

Ex. 1235: U.S. Patent No. 6,112,158 ("Bond") Ex. 1236: Excerpts from the Modern Dictionary of Electronics, 6th Edition, 1992 Ex. 1237: U.S. Patent No. 8,643,985 ("West '985") Ex. 1238: U.S. Patent Application Publication No. 2010/0275823 ("Pahls") Ex. 1239: U.S. Patent No. 7,710,752 ("West '752") Ex. 1240: U.S. Patent No. 7,746,003 ("Verfuerth") Ex. 1241: J. G. Tracy and H. Pfitzer, "Achieving high efficiency in a double conversion transformerless UPS," 31st Annual Conference of IEEE Industrial Electronics Society, 2005. ("Tracy-IEEE 2005") Ex. 1242: McGraw-Hill Dictionary of Electrical and Electronic Engineering, 1984 Ex. 1243: Excerpts of IEEE: The Authoritative Dictionary of IEEE Standard Terms, Seventh Edition, IEEE Press 2000 Ex. 1244: Tolbert et al., Multilevel Converters for Large Electric Drives, IEEE Trans. Ind. Apps., Vol 35, No. 1, Jan/Feb 1999 ("Tolbert") Certified translation of Ex. 1255, Heribert Schmidt, Bruno Ex. 1245: Kiefer. Wechselwirkungen zwischen & Klaus Solarmodulen und Wechselrichtern, Fraunhofer Institute for Solar Power Systems, June 2007. ("Schmidt") Ex. 1246: Myrzik, J. Topologische Untersuchungen zur Anwendung von tief/-hochsetzenden Stellern für Wechselrichter. Dissertation zur Erlangung des Grades eines Doktor-Ingenieurs (Dr. ing.) im Fachgebiet Elektrotechnik der Universität Gesamthochschule Kassel (2001, Kassel Univ. Press) Ex. 1247: U.S. Patent No. 7,082,040 ("Raddi") Ex. 1248: U.S. Patent No. 4,320,449 ("Carroll") Ex. 1249: Reserved

U.S. Patent No. 5,285,372 ("Huynh")

Ex. 1250:

Ex. 1251: Certified translation of Ex. 1258, PCT Publication No. WO 2010/082265 ("Mori '265")

Ex. 1252: Keith H. Billings, Switchmode Power Supply Handbook, McGraw Hill, 1989

Ex. 1253: Marty Brown, *Power Supply Cookbook*, Butterworth-Heinemann, 1994

Ex. 1254: U.S. Department of Commerce. International Trade Administration, *Electric Current Abroad*, 1998 Edition, reprinted Feb. 2002. ("ECA 1998/2002")

Ex. 1255: Heribert Schmidt, Bruno Burger, & Klaus Kiefer. Wechselwirkungen zwischen Solarmodulen und Wechselrichtern. English translation: Interaction between Solar Modules and DC/AC Inverters, 2007

Ex. 1256: Math H. Bollen, Irene Gu, Signal Processing of Power Quality Disturbances, Wiley-IEEE Press, 2006

Ex. 1257: Symmetrical components, Wikipedia, <a href="https://en.wikipedia.org/wiki/Symmetrical\_components">https://en.wikipedia.org/wiki/Symmetrical\_components</a>, downloaded September 29, 2021

Ex. 1258: PCT Publication No. WO 2010/082265 ("Mori '265")

Ex. 1259-1263: Reserved

Ex. 1264: Ostbayerisches Technologie-Transfer-Institute. V., Power Electronics for Photovoltaics, OTTI International Seminar, June 7-8, 2010

Ex. 1265: Ostbayerisches Technologie-Transfer-Institute. V., Power Electronics for Photovoltaics, OTTI International Seminar, May 25-26, 2009

#### **MANDATORY NOTICES**

37 C.F.R. § 42.8(b)(1)&(2): Real Parties in Interest & Related Matters.

The real party-in-interest is Petitioner SolarEdge Technologies Ltd. No unnamed entity is funding, controlling, or directing this Petition, or otherwise has had an opportunity to control or direct this Petition or Petitioner's participation in any resulting IPR.

The '822 Patent has been asserted against SolarEdge in the District of Delaware in *Koolbridge Solar, Inc. v. SolarEdge Technologies, Inc.*, No. 1:20-cv-01374-MN (D. Del.). The earliest date of service on Petitioner was October 12, 2020. The Patent Owner, after having been notified of Petitioner's intent to file IPRs against the '822 Patent, voluntarily dismissed its lawsuit without prejudice.

The references relied upon herein were not cited during prosecution. No arguments presented in this Petition were raised during prosecution of the '822 patent.

37 C.F.R. § 42.8(b)(3)&(4): Lead & Back-Up Counsel, and Service Information. Petitioner designates counsel listed below. A power of attorney for counsel is being concurrently filed.

### **Lead Counsel**

Frederic M. Meeker (Reg. No. 35,282) fmeeker@bannerwitcoff.com

### First Back-Up Counsel

Michael S. Cuviello (Reg. No. 59,255) mcuviello@bannerwitcoff.com

Banner & Witcoff, Ltd., 1100 13<sup>th</sup> Street, NW, Suite 1200 Washington, DC 20005

Tel: 202-824-3000 Fax: 202-824-3001

### **Additional Back-Up Counsel**

Craig W. Kronenthal (Reg. No. 58,541) ckronenthal@bannerwitcoff.com

John R. Hutchins (Reg. No. 43,686) jhutchins@bannerwitcoff.com

Banner & Witcoff, Ltd., 1100 13<sup>th</sup> Street, NW, Suite 1200 Washington, DC 20005 Tel: 202-824-3000

Fax: 202-824-3001

Zachary L. Getzelman (Reg. No. 71,292) zgetzelman@bannerwitcoff.com

Banner and Witcoff, Ltd. 71 S. Wacker Dr., Suite 3600 Chicago, IL 60606 Tel: (312) 463-5000

The address and contact information for all designated counsel is: Banner & Witcoff, Ltd., 1100 13<sup>th</sup> Street, NW, Suite 1200, Washington, DC 20005; Tel: 202-824-3000; Fax: 202-824-3001. Please address all correspondence to counsel at this address shown above. Petitioner consents to electronic service by email at the following address and the above emails: SolarEdgeIPRService@bannerwitcoff.com.

### I. INTRODUCTION & RELIEF REQUESTED

U.S. Patent No. 8,937,822 (the "'822 patent") describes various configurations of well-known DC-AC inverters that convert direct current (DC) electrical power such as from a solar panel to alternating current (AC) electrical power using reversing switches arranged as: (1) a single-phase inverter with an Hbridge switch; (2) a single-phase inverter with multiple H-bridge switches in series; and (3) a three-phase inverter with half-bridge switches. Ex. 1202, ¶¶ 92-96. The '822 patent's claims add merely trivial requirements to these embodiments based on intrinsic properties of DC-AC inverters, such as common-mode AC waveforms appearing on the DC input lines, or well-known components like bi-directional DC-DC converters, switching controllers, a ground leak detector, and a common-mode filter. Mori (Japanese Patent Publication No. 2006-238630A), which is an example of a single-phase inverter with multiple H-bridge switches in series, alone and in combination with the additional secondary references in this petition, teaches these additional limitations. Claims 1-13 and 20 of the '822 patent are unpatentable and should be cancelled.

<sup>&</sup>lt;sup>1</sup> Other concurrently filed petitions use different base references teaching the other (*e.g.*, single-phase) inverter configurations.

### II. GROUNDS FOR STANDING & FEE PAYMENT

Petitioner certifies that the '822 patent is available for *inter partes* review, and that Petitioner is not barred or estopped from requesting *inter partes* review challenging claims 1-13 and 20 on the identified grounds. The undersigned authorizes the charge of any required fees to Deposit Account No. 19-0733.

#### III. OVERVIEW

### A. Brief Description of Alleged Invention

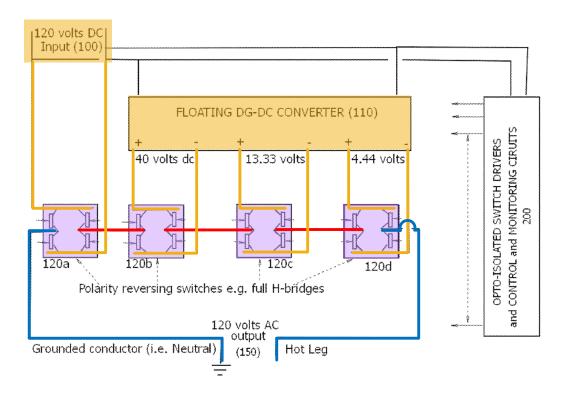

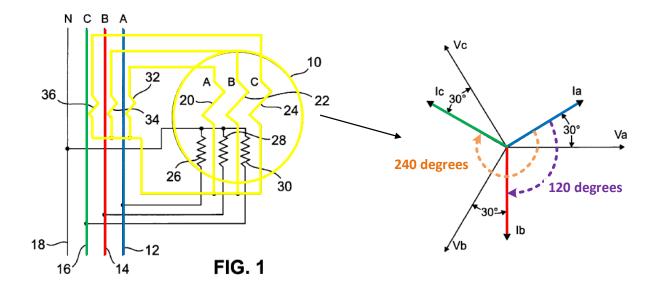

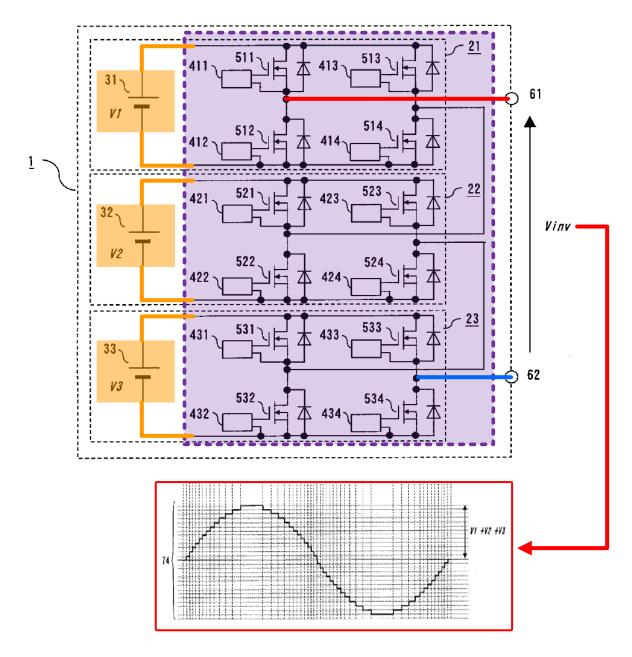

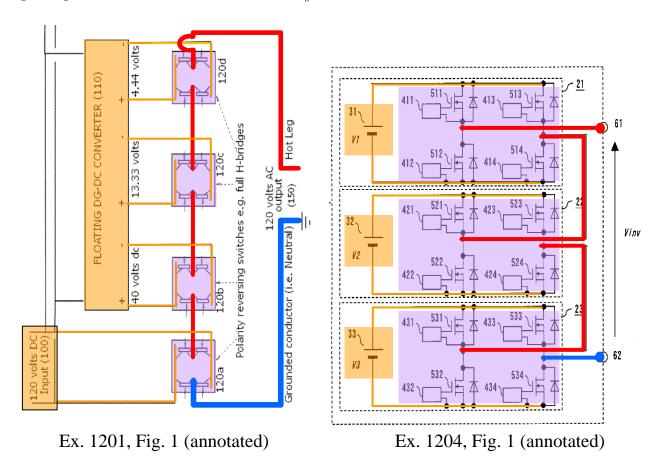

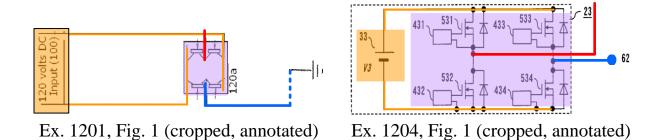

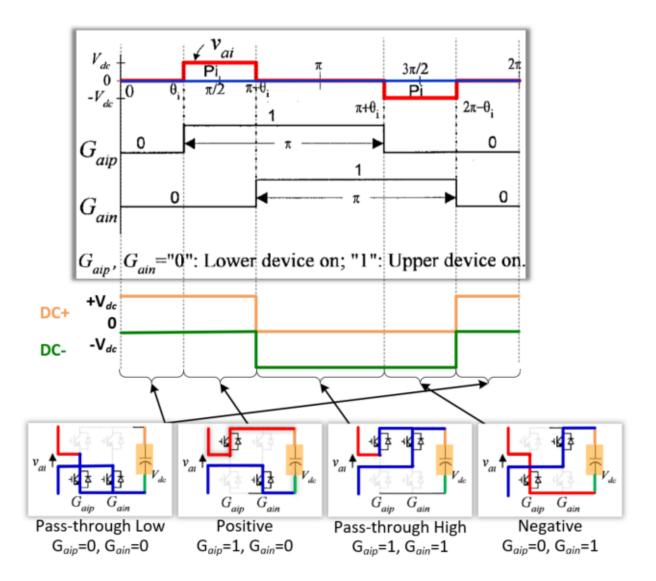

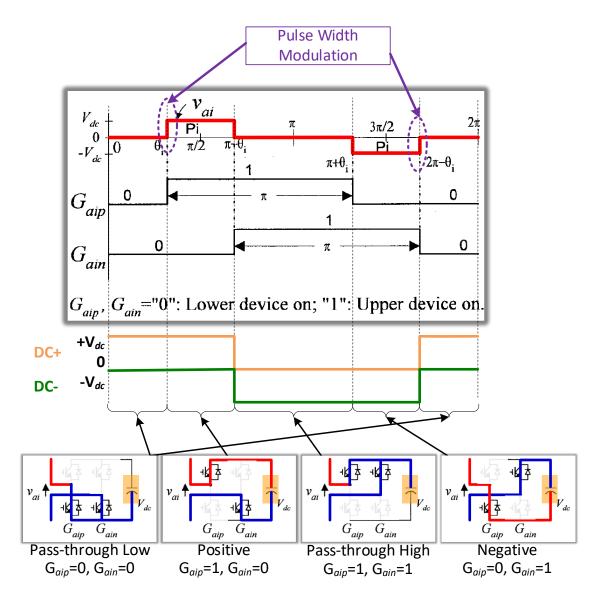

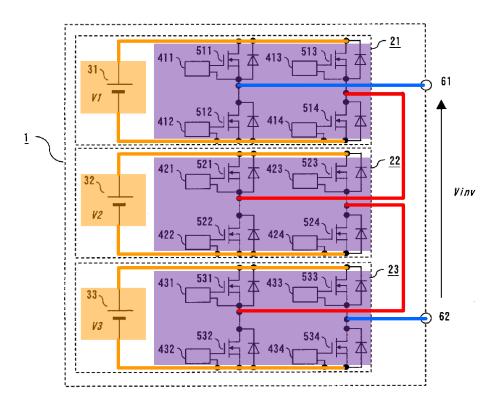

The '822 patent describes multiple well-known inverters, one of which is a single-phase, inverter using a plurality of H-bridges (**purple**), connected in series (**red**) to convert floating DC power sources (**orange**) to an AC output (**blue**):

Ex. 1201, Fig. 1 (annotated)

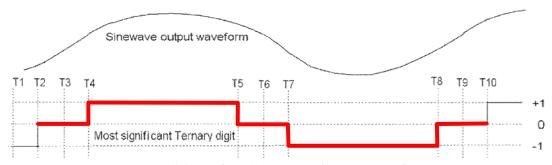

Id., Abstract, 3:17-36, 3:45-50, 3:53-57, 6:17-29, 6:49-59, 7:10-16, 7:39-43, 7:49-54; Ex. 1202, ¶¶ 61-65, 71-80. The floating DC-DC converter 110 converts the 120 volts DC input 100 to a plurality of floating DC voltages, each a successive power of 3 (i.e., 40V, 13.33V, 4.44V). Id., 6:46-52. The H-bridges output their voltage input multiplied respectively by four ternary digits (T4, T3, T2, T1), each having a value of +1, 0, or -1, thus producing a sum voltage as follows: 120v×T4+40v×T3+13.33v×T2+4.44v×T1. The ternary digits are controlled to produce a sequence of steps approximating a sinusoidal 60 Hz waveform:

Ex. 1201, Fig. 12 (annotated)

*Id.*, Abstract, 1:18-23, 3:61-4:10, 5:41-57, 7:39-43, 9:41-49, 9:60-64, 10:31-40; Ex. 1202, ¶¶ 67-70.

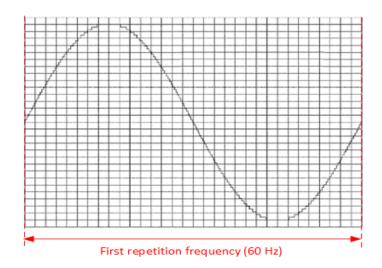

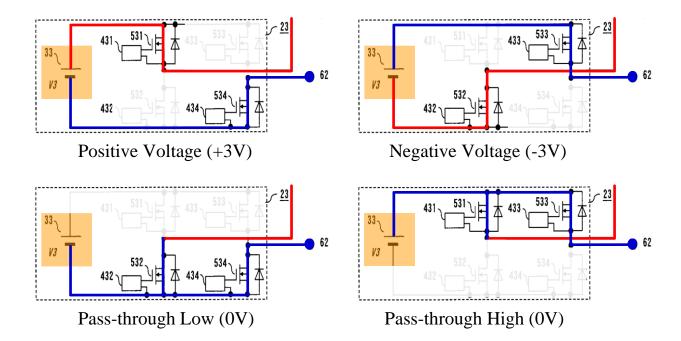

Each H-bridge switch connects a DC power source directly across the switch output (at terminals 163 and 164) with positive (+1) or negative (-1) polarity, or

bypasses the DC power source with either of two pass-through states (0) as shown below:

Ex. 1201, Fig. 3 (annotated)

*Id.*, 1:36-39, 6:42-57, 7:7-16, 7:49-8:3, 9:41-10:5, 10:15-18, 10:35-40, 11:9-16, 11:32-37; Ex. 1202, ¶ 66. The direct connection made by H-bridge 120a, with alternating polarity, to the AC output terminal causes a 60Hz common-mode voltage

square wave superimposed at "[e]ach DC input terminal" of the 120V DC supply. Ex. 1201, 4:46-50, 10:35-40, 10:55-57, 27:10-11.

### **B.** Prosecution History

The application that led to the '822 patent was filed May 8, 2011. Ex. 1222, p. 128. Claims 1 and 6 were rejected as obvious over U.S. Patent Nos. 7,082,040 (Raddi) and 4,320,449 (Carroll). *Id.* at 303-308. In response, the applicant amended claim 1 to recite "wherein the second repetition frequency is a multiple equal to the same said number N of said first repetition frequency," purportedly incorporating then-allowable claim 3 "to overcome the examiner's rejection of claim 1." *Id.*, p. 318-319. The applicant distinguished the amendment from claim 3: "Rather than specify N to be 1, 2 or 3[,] I have left it equal to the number of unique phases recited in claim 1." *Id.* The examiner allowed the claims based on the prior art allegedly lacking the feature "wherein the second repetition frequency is multiple equal to the same said number N of said first repetition frequency." *Id.*, p. 357-361. None of the prior art cited herein was cited during prosecution, and none is cumulative to the prior art relied upon by the examiner. Mori, the primary reference relied on herein, discloses an inverter with a floating DC supply voltage, which is fundamentally different from Raddi's AC-AC converter with an uninterrupted neutral from input to output that prevents the supply from floating, and fundamentally different from Carroll's cycloconverter connected to the outputs of an inverter for conditioning the

outputs for reactive loads. Ex. 1202, ¶¶ 81-91; Ex. 1201, cover; Ex. 1247, Abstract; Ex. 1248, 1:19-34, Fig. 1.

### C. Scope and Content of the Prior Art

1. Japanese Patent Publication No. 2006-238630A ("Mori") (Ex. 1220, certified translation Ex. 1204)

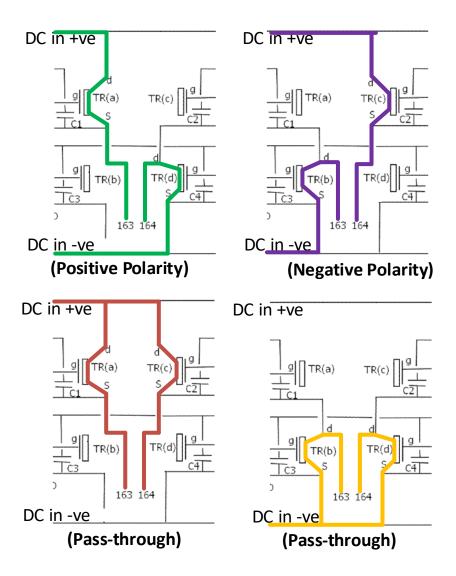

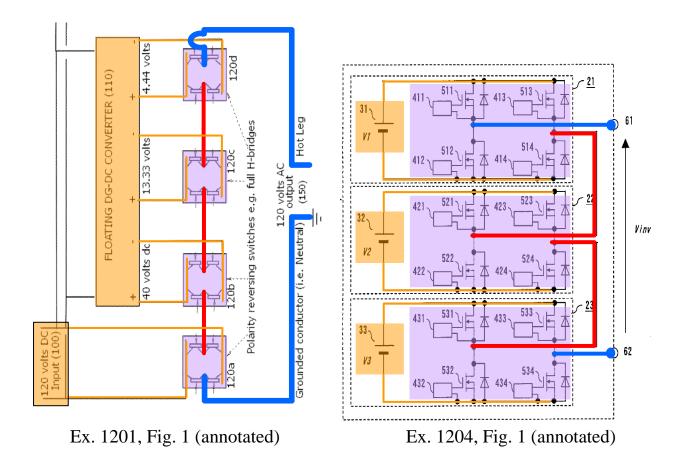

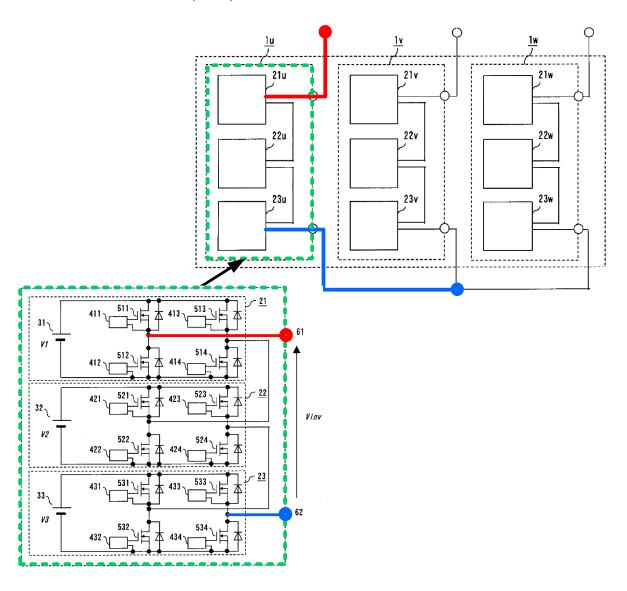

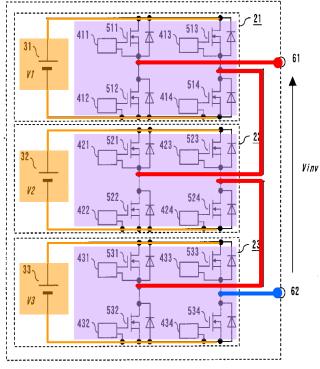

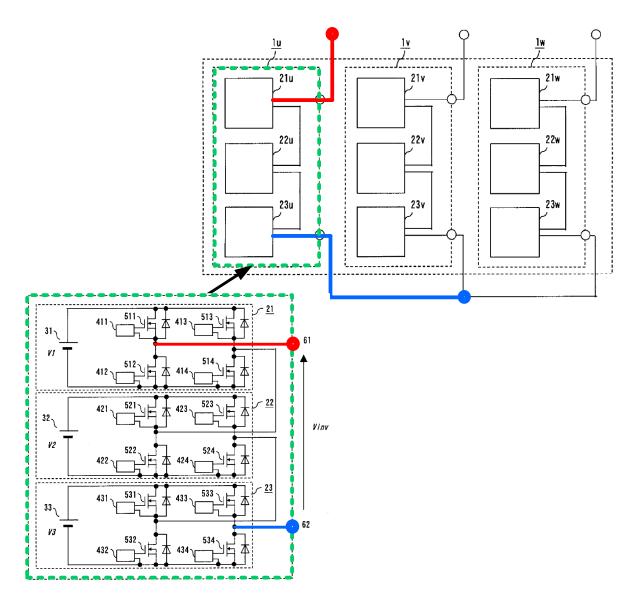

Mori is a Japanese Patent Publication that published on September 7, 2006, making it prior art under 35 U.S.C. § 102(b).<sup>2</sup> Ex. 1202, ¶ 203. As shown in the side-by-side figures below, Mori (right-side) discloses a near identical inverter to that of the '822 patent (left-side), including multiple H-bridges (21, 22, 23) (purple) respectively receiving multiple floating DC voltage sources (V1, V2, V3) (orange), each a successive power of 3 (1V, 3V, 9V), with the H-bridge outputs connected in series (red) to generate an AC output (Vinv) (blue) at a first repetition frequency. Ex. 1204, ¶¶ [0002]-[0012], [0015]-[0016], [0019]-[0021], [0034]; Ex. 1202, ¶¶ 204-206; compare Ex. 1204, ¶¶ [0009]-[0012], Fig. 1 with Ex. 1201, 6:16-9:40, Fig. 1. The switching structures differ only in the number of voltage sources/H-bridges (four in the '822 patent's Figure 1, and three in Mori's Figure 1). Ex. 1204, ¶ [0011]; Ex. 1201, 6:25-26.

<sup>&</sup>lt;sup>2</sup> Citations to 35 U.S.C. §§ 102 and 103 refer to the pre-AIA versions.

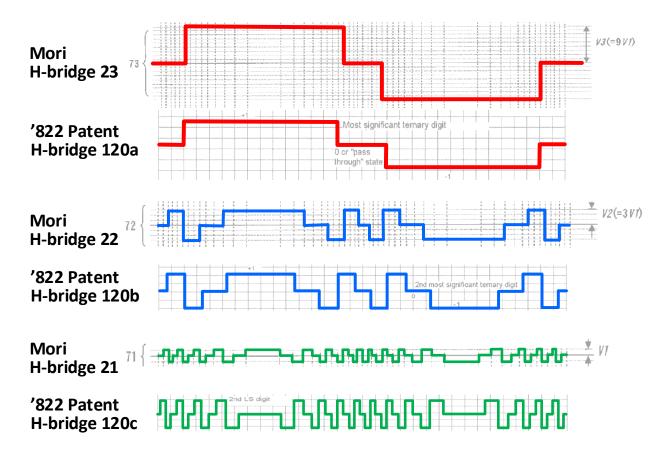

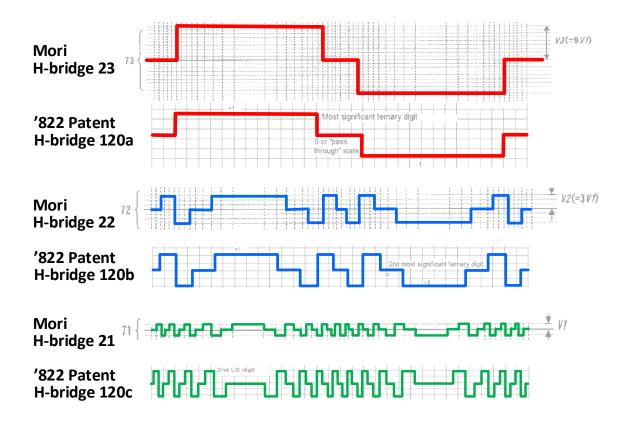

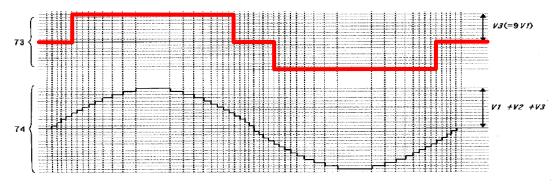

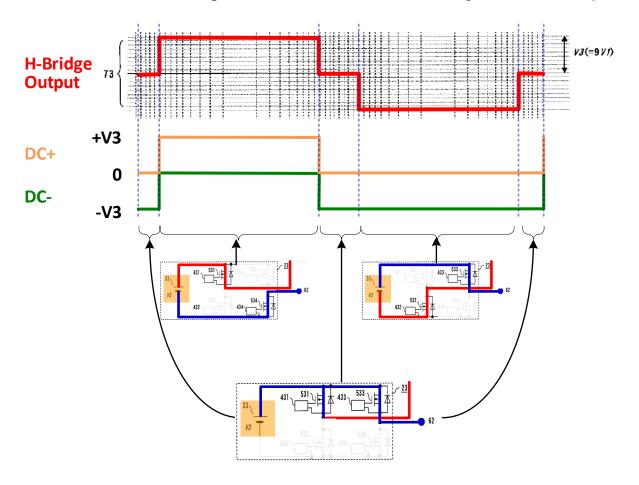

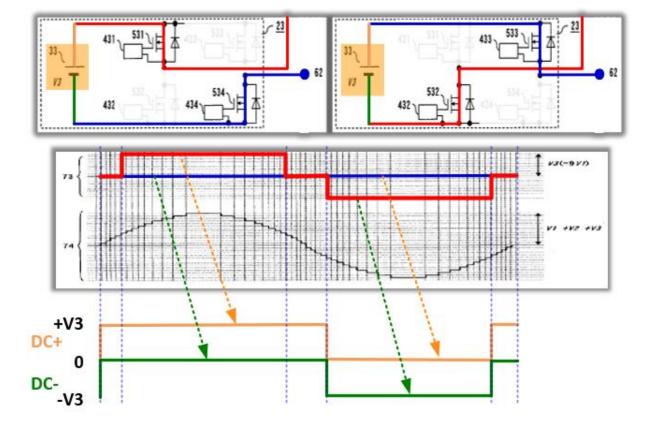

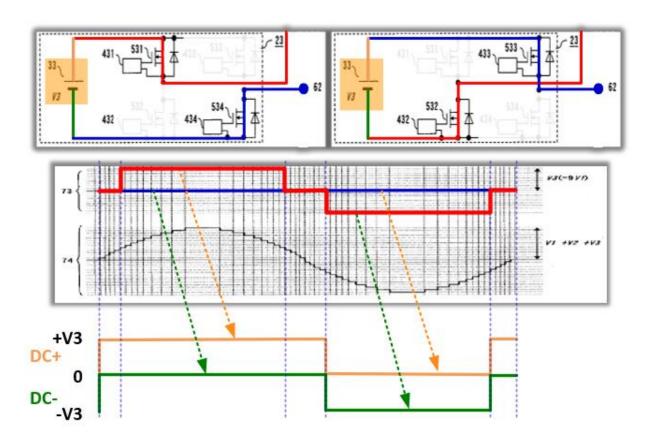

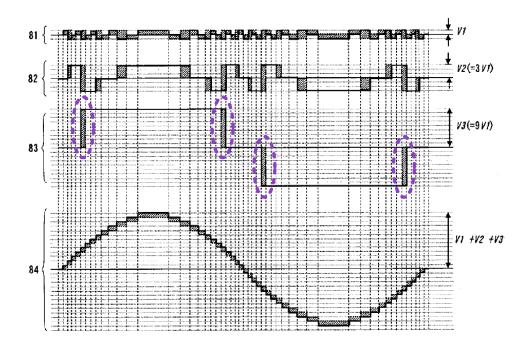

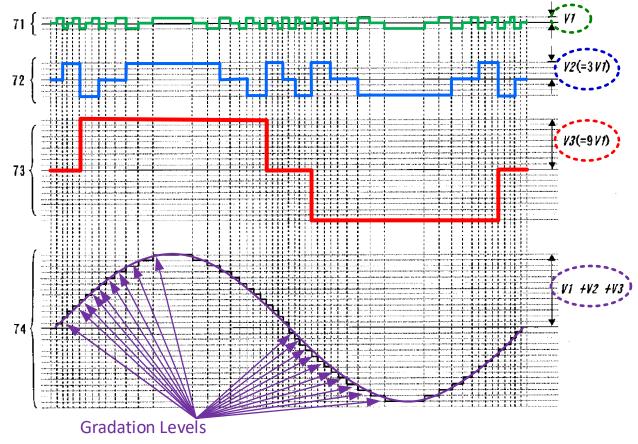

The switch timing of the two inverters is also the same, as shown in the annotated figures below, which juxtaposes the state switching (+1, 0, -1) of H-bridge 23, 22, and 21 from Figure 2 of Mori with that of H-bridges 120a, 120b, 120c of Figure 4 of the '822 patent, respectively. Ex. 1204, ¶¶ [0009]-[0012], Fig. 2; Ex. 1201, 9:51-11:45, Fig. 4; Ex. 1202, ¶¶ 207-209. As the '822 patent acknowledges, the switch timing of H-bridge 120a (illustrated below in red) causes a 60Hz common-mode voltage square wave superimposed on the terminals of the 120V DC supply. Ex. 1201, Abstract, 4:46-52, 10:35-57, 10:65-11:6, 35:54-58. Having an identical structure and timing to H-bridge 120a, Mori's H-bridge 23 necessarily

generates the same common-mode voltage on terminals of DC supply 33 (which outputs V3):

Ex. 1204, Fig. 2 (cropped, annotated); Ex. 1201, Fig. 4 (cropped, annotated) Id., ¶¶ [0002], [0004], [0009]-[0012]; Ex. 1202, ¶¶ 208-212.

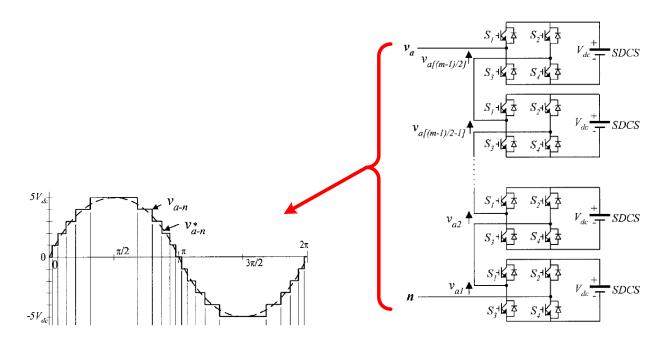

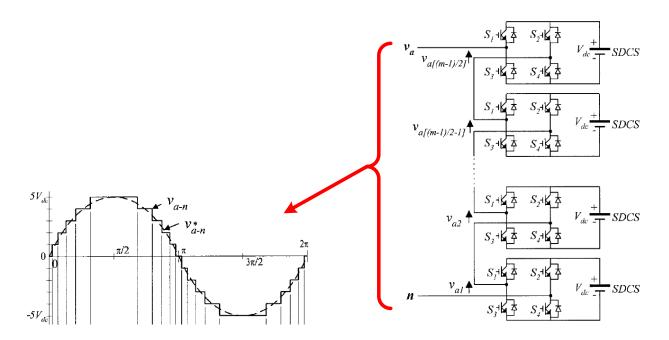

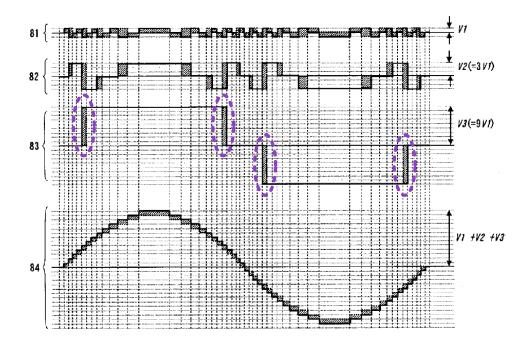

2. Tolbert, Multilevel Converters for Large Electric Drives, IEEE Trans. Ind. Apps., Vol 35, No. 1, Jan/Feb 1999 ("Tolbert") (Ex. 1244)

Tolbert was published in 1999, and is prior art under 35 U.S.C. § 102(b). Ex. 1223, ¶¶ 214-231 (Section III.J). Tolbert discloses an inverter having the same basic structure of Mori's inverter in which the outputs of multiple H-bridges are connected in series to generate an AC waveform.

Ex. 1244, Figs. 1, 2a (annotated)

*Id.*, pp. 37-38; Ex. 1202, ¶¶ 213-215.

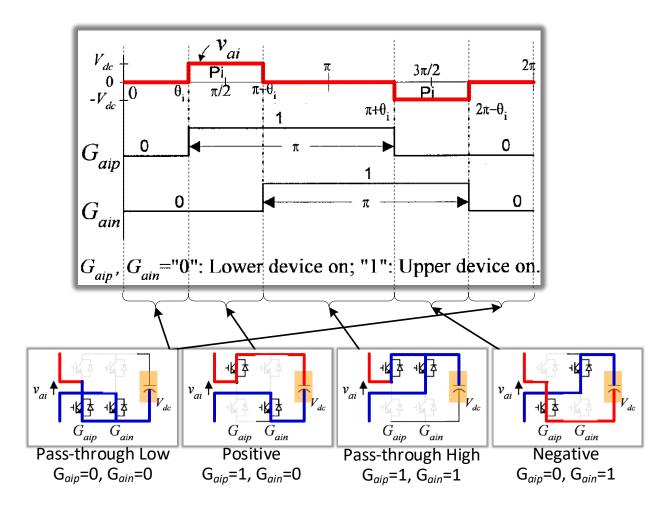

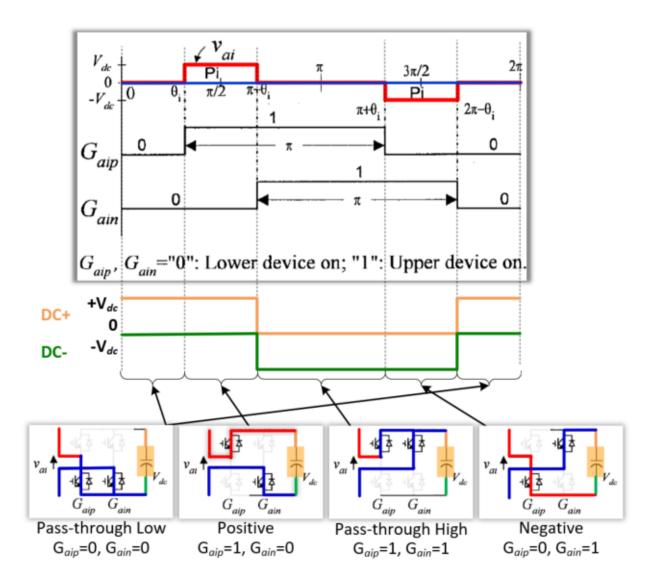

Each of Tolbert's H-bridges is controlled to output +V, 0, and -V (the same as Mori's H-bridge switch 33) according to 2 bits— $G_{aip}$ , which controls transistors S1, S3 (on the left) in opposite states, and  $G_{ain}$ , which controls transistors S2, S4 (on the right) in opposite states. Ex. 1202, ¶ 216; Ex. 1244, 37-38, Figs. 1, 2a. For each side of the H-bridge, a bit value of 1 turns on the top transistor and turns off the bottom transistor, and a bit value of 0 turns off the top transistor and turns on the bottom transistor. Ex. 1202, ¶ 216; Ex. 1244, Fig. 2b. These bits control the H-bridge sequentially into the pass-through low state, the positive state, the pass-through high state, and the negative state:

Ex. 1244, Fig. 2(b) (annotated)

*Id.*, pp. 37-38; Ex. 1202, ¶ 216. These are identical to the H-bridge states in the '822 patent. *See* Section III.A, *supra*; Ex. 1202, ¶ 217.

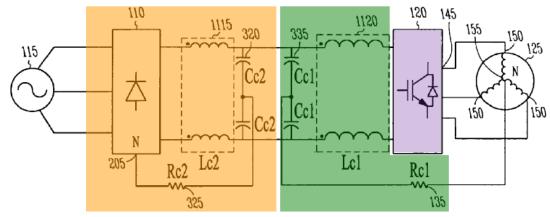

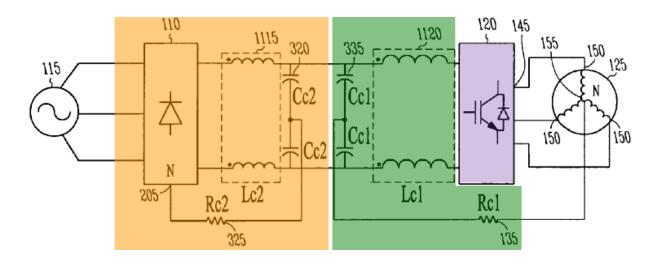

### 3. U.S. Pat. App. Pub. No. 2007/0278988 ("De") (Ex. 1218)

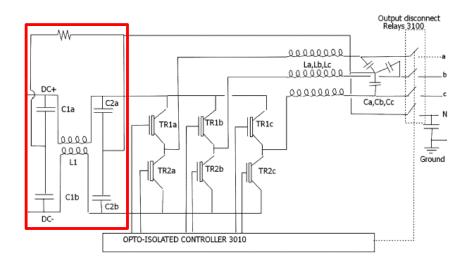

De was published on December 6, 2007, making it prior art under 35 U.S.C. § 102(b). De discloses a common-mode filter (green), including a common-mode inductor 1120 and capacitors 335, connected between DC input terminals of inverter 1 (purple) and output terminals of a rectifier DC power source (orange):

Ex. 1218, Fig. 12 (annotated)

*Id.*, ¶¶ [0020], [0033]-[0034], [0037]-[0038]; Ex. 1202, ¶¶ 194-197.

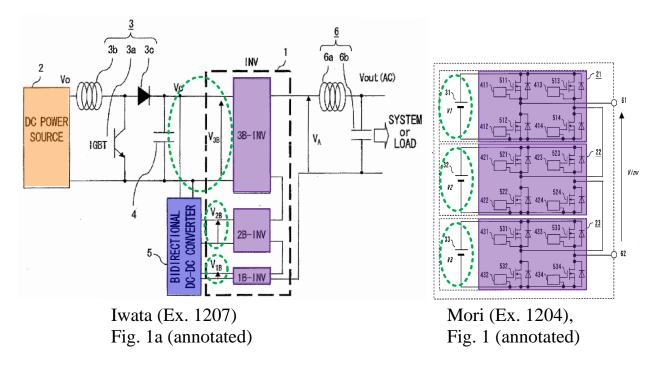

# 4. U.S. Patent Application Publication No. 2008/0192519 ("Iwata") (Ex. 1207)

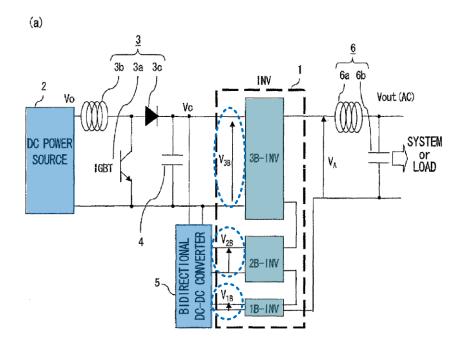

Iwata was published on August 14, 2008, making it prior art under 35 U.S.C. § 102(b). Iwata discloses a DC-AC converter with multiple H-bridge inverters (3B-INV, 2B-INV, and 1B-INV) that are connected in series:

Ex. 1207, Fig. 1a (annotated)

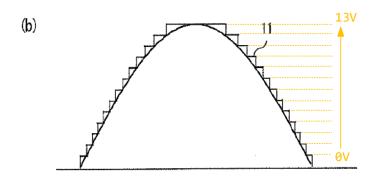

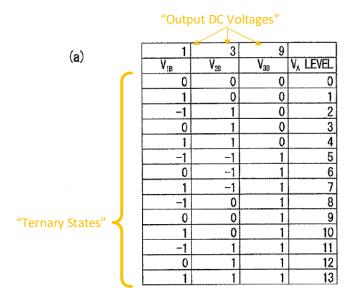

*Id.*, ¶¶ [0003], [0007]-[0009], [0045], Fig. 1b; Ex. 1202, ¶ 185. A bidirectional DC-to-DC converter 5 converts input voltage  $V_{3B}$  from a DC power source 2 to floating voltage supplies  $V_{1B}$  and  $V_{2B}$  with voltages at successive powers of 3 as inputs. Ex. 1207, ¶¶ [0045], [0049]-[0050] ("[T]he relation between  $V_{1B}$ ,  $V_{2B}$ , and  $V_{3B}$  is 1:3:9."), Fig. 1a. Iwata's DC-AC converter generates a "substantially sine wave-like output Voltage waveform 11" as shown in annotated Figure 2(b):

Ex. 1207, Fig. 2(b) (annotated)

*Id.*, ¶ [0050]; Ex. 1202, ¶ 186. The values of that output waveform are expressed with a ternary number system having digits for  $V_{1B}$ ,  $V_{2B}$ , and  $V_{3B}$ .

Ex. 1207, Fig. 2(a) (annotated)

Id.,  $\P$  [0050]; Ex. 1202,  $\P$  187. For a desired V<sub>A</sub> output, each digit determines whether a respective H-bridge is controlled to one of three states: (a) a positive polarity state (+1), (b) an inverse polarity state (-1), and (c) a pass-through state (0). Ex. 1207,  $\P$  [0050]; Ex. 1202,  $\P$  188.

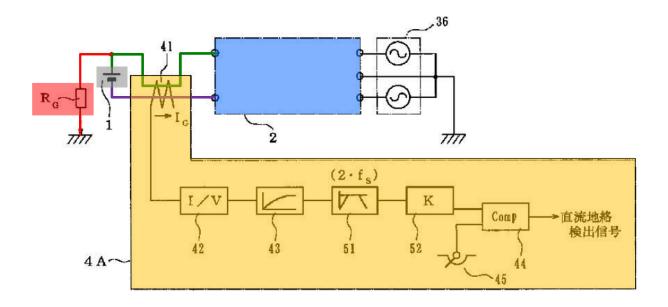

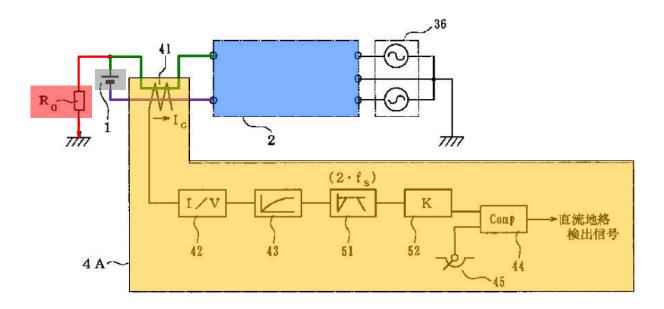

# 5. Japanese Pat. App. Pub. No. JP 11-122819 ("Fujimoto") (Ex. 1233, certified translation Ex. 1234)

Fujimoto is a Japanese patent publication published on April 30, 1999, making it prior art under 35 U.S.C. § 102(b). Fujimoto describes a DC ground fault detector (orange) that includes current transformer 41 inserted in the positive (green) and negative (purple) conductors between Fujimoto's DC power supply 1 (grey) and inverter 2 (blue):

Ex. 1234, Fig. 1 (annotated)

Id., Fig. 3, ¶¶ [0005], [0008], [0010]; Ex. 1202, ¶¶ 190-193. In the event of a ground fault  $R_G$  (red), a "common current"  $I_G$  is induced with an AC component ( $I_{ac}$ ), at twice the frequency of the AC output waveform of the inverter, which is detected by the DC ground fault detector. Ex. 1234, ¶¶ [0005]-[0007], [0010]-[0011]; Ex. 1202, ¶¶ 193.

### 6. U.S. Patent No. 6,112,158 ("Bond") (Ex. 1235)

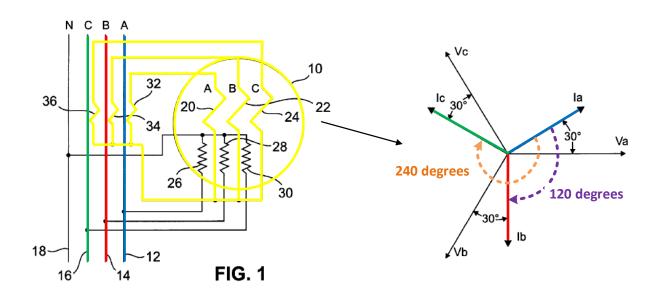

Bond issued on August 29, 2000, making it prior art under 35 U.S.C. § 102(b). Bond discloses a watt-hour metering device 10 (yellow) with a utility120V/208V four wire wye service type connection with neutral at the center of the wye, and with power lines 12 (blue), 14 (red), and 16 (green) delivering current Ia (blue), Ib (red), and Ic (green) at unique phases spaced relatively 0, 120 and 240 degrees apart:

Ex. 1235, Figs. 1, 1a (annotated)

*Id.*, 1:10-22, 1:26-49, 2:55-58, 3:16-23, 3:41-49, 4:4-11, 4:27-58 (table 2), 10:9-11; Ex. 1202, ¶¶ 198-202.

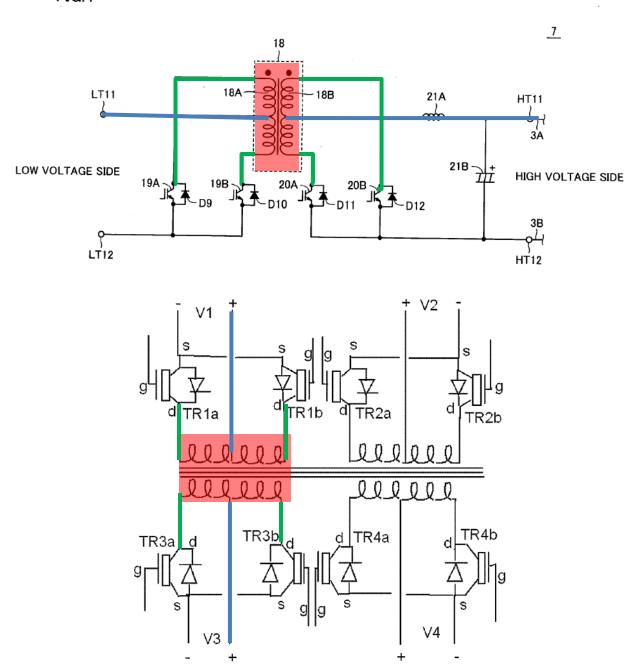

# 7. U.S. Patent Application Publication No. 2009/0086520 ("Nishimura") (Ex. 1208)

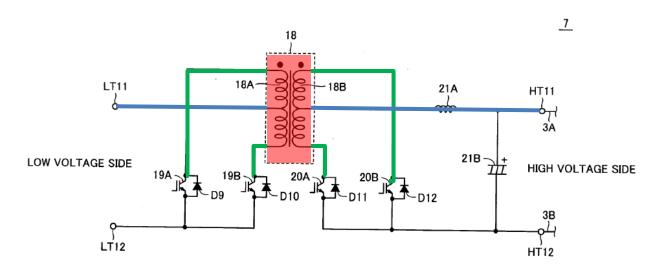

Nishimura was published on April 2, 2009, making it prior art under 35 U.S.C. § 102(b). Nishimura teaches the structure for the bidirectional DC-DC converter in Figure 2 of the '822 patent. Ex. 1208, ¶¶ [0091]-[0101], Fig. 4; Ex. 1201, 18:34-47, Fig. 2. Nishimura's bidirectional DC-DC converter includes center-tapped windings (red) that are connected to the positive terminal of the DC input or output (blue) with ends of the windings connected to the drains of N-Type MOSFET pairs (green):

FIG.4

Ex. 1208, Fig. 4 (annotated)

Id., ¶¶ [0091]-[0101]; Ex. 1202, ¶ 189.

# IV. IDENTIFICATION OF CHALLENGE PURSUANT TO 37 C.F.R. § 42.104(b)

Petitioner requests review of claims 1–13 and 20 on the following grounds and references.

| Grounds | References                            | Basis | Claims Challenged |

|---------|---------------------------------------|-------|-------------------|

| 1       | Mori                                  | 102   | 1-3, 8-10, 12     |

| 2       | Mori                                  | 103   | 1-3, 8-10, 12     |

| 3       | Mori in view of Tolbert               | 103   | 1-3, 8-10, 12     |

| 4, 5    | Mori/Mori-Tolbert in view of De       | 103   | 6, 20             |

| 6, 7    | Mori/Mori-Tolbert in view of Fujimoto | 103   | 4, 11             |

| 8, 9    | Mori/Mori-Tolbert in view Bond        | 103   | 7                 |

| 10 11  | Mori/Mori-Tolbert in view of Iwata | 103 | 5 13  |

|--------|------------------------------------|-----|-------|

| 10, 11 | and Nishimura                      |     | 3, 13 |

The challenged claims are unpatentable based on these grounds as demonstrated by a preponderance of the evidence, including Dr. Baker's expert testimony (*e.g.*, Ex. 1202, ¶¶ 1-60, 132-184, 218-219, 392-395), and Dr. Mullins' expert testimony proving authenticity and public availability prior to May 8, 2011 of certain exhibits. Ex. 1223, ¶¶ 1-40, 41-65 (Ex. 1210), 66-79 (Ex. 1212), 232-248 (Ex. 1215), 268-285 (Ex. 1217), 80-93 (Ex. 1219), 130-154 (Ex. 1241), 214-231 (Ex. 1244), 249-267 (Ex. 1246), 332-353 (Ex. 1252), 193-213 (Ex. 1253), 172-192 (Ex. 1254), 155-171 (Ex. 1255), 308-331 (Ex. 1256), 94-111 (Ex. 1264), 112-129 (Ex. 1265), 354-356.

### A. Level of Ordinary Skill

At the time of the alleged invention of the '822 patent, a person having ordinary skill in the art ("PHOSITA") would have had a bachelor's degree in electrical engineering or a similar discipline and three years of design experience with power electronics, including experience designing power converters. Ex. 1202, ¶¶ 20-23.

#### **B.** Claim Construction

The following terms could be construed as means-plus-function limitations.

37 C.F.R. § 42.104(b)(3). If the Board does not construe these as means-plus-

function limitations, they should be construed, along with all other claim terms, according to their ordinary and customary meaning, consistent with the prosecution history, to a PHOSITA at the time of the alleged invention. 37 C.F.R. § 42.100(b). Whether or not these are means-plus-function terms, the prior art discloses these limitations as addressed below. Ex. 1202, ¶¶ 97-99.

### 1. "DC to AC converter" (Claim 1)

To the extent "DC to AC converter" is found to be a means-plus-function term, it performs the function of "caus[ing] (1) an AC output waveform at said first repetition frequency and having a voltage relative to one of said at least one ground, neutral or reference potential terminals to appear with a unique phase at each of a number N at least equal to one of said set of live AC output terminals, and (2) a common-mode voltage waveform at a second repetition frequency to appear relative to one of said at least one ground, neutral or reference potential terminals and in the same phase on both of said positive and negative terminals of said DC power source, wherein the second repetition frequency is a multiple equal to the same said number N of said first repetition frequency." Ex. 1201, claim 1; Ex. 1202, ¶ 100.

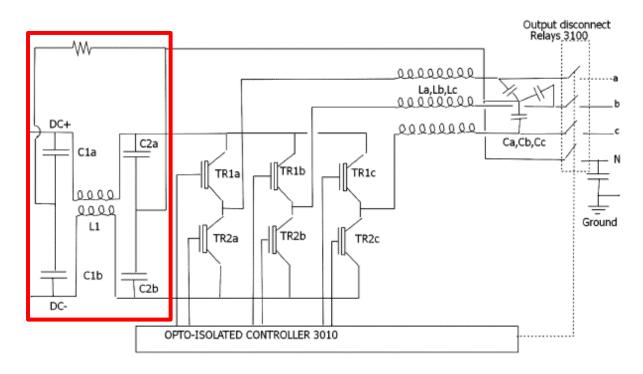

The corresponding structures include four different inverter circuits. One inverter circuit, depicted in Figures 1 and 10, includes a plurality of H-bridges with series connected outputs and with inputs of each H-bridge connected to a different voltage source. Ex. 1201, 6:17-26, Figs. 1, 10; Ex. 1202, ¶¶ 101-105.

Another corresponding structure, in Figure 16, includes three half-bridge switches with inputs connected across a pair of DC input terminals, and each outputting a voltage phase through a respective inductor. Ex. 1201, Fig. 16; Ex. 1202, ¶ 107.

Two other structures are illustrated in Figures 15 and 24. Ex. 1202, ¶¶ 106, 108-109. The Figure 15 structure includes a single H-bridge with a single-phase output connected through an inductor. Ex. 1201, 23:27-44, Fig. 15. The Figure 24 structure is the same as in Figure 16, but with three additional H-bridges, each connected to a different one of the voltage phase outputs. Ex. 1201, 29:25-67, Fig. 24.

### 2. "A switch[ing] controller" (Claims 2 and 5)

To the extent "switch[ing] controller" in claims 2 and 5 is construed to be a means-plus function term, the claim 2 function is:

[controlling a] first electronic switch . . . to connect said positive DC input terminal to the instantaneously most positive of said set of AC output terminals and said at least one ground, neutral or reference potential terminal alternating with connecting said negative DC input terminal to the instantaneously most negative of said set of AC output terminals and said at least one ground, neutral or reference potential terminal,

and the claim 5 function is:

for controlling the three-state electronic switches according to a sampled numerical representation of the desired AC output waveform expressed in a ternary number base.

Ex. 1201, claims 2, 5; Ex. 1202, ¶ 120.

The corresponding structures for both switch controllers include (1) "a microcontroller" with "memory"; or (2) "a crystal reference oscillator," "15-bit divider," and Read Only Memory (ROM) containing precomputed waveforms. Ex. 1201, 12:26-51, 24:8-12; Ex. 1202, ¶¶ 120-125.

### 3. "AC ground leak detector" (Claim 4)

To the extent "AC ground leak detector . . ." is construed to be a means-plus-function term, it performs the function of "detect[ing] an imbalance current at said second frequency and [] thereby provid[ing] a detection signal indicative of an unwanted leakage impedance from a DC conductor to ground." Ex. 1201, claim 4; Ex. 1202, ¶ 110. The corresponding structure is a current transformer including toroid 800 with a toroidal winding 801. Ex. 1201, 25:57-59, 31:65-32:20, 35:66-36:3, 41:21-22, Fig. 18; Ex. 1202, ¶¶ 110-114.

### 4. "bidirectional DC-to-DC converter" (Claims 5, 13)

To the extent "bidirectional DC-to-DC converter" in claims 5 and 13 is construed to be a means-plus function term, the claim 5 function is:

converting the input voltage from said DC power source to a number of floating supplies of voltages equal to the input voltage divided or multiplied by successive powers of 3,

and the claim 13 function is:

to form, along with the DC source voltage, a set of floating DC supplies of voltages having voltage ratios of successive powers of 3. Ex. 1001, cls. 5, 13.

The corresponding structure for both claims is one or more transformers with windings that have turn ratios in proportion to the voltage ratios being output, where each winding corresponding to a floating supply is center tapped (or an equivalent structure). *Id.*, 15:29-34, 18:34-47, 19:5-23, Figs. 2, 10; Ex. 1202, ¶¶ 126-131.

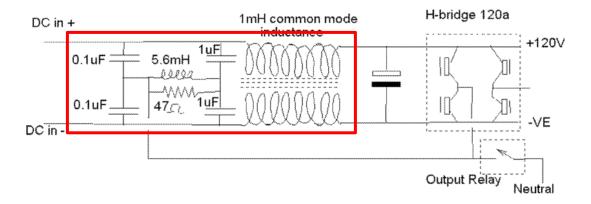

### 5. "common-mode filter" (Claim 6)

To the extent "common mode filter" is a means-plus-function term, it performs the claimed function of "(1) preventing high frequency components of the DC to AC converter internal waveforms being exported to said DC source and (2) minimizing overshoot of said common-mode waveform in order to minimize peak voltages on said positive and negative terminals." Ex. 1201, claims 6; Ex. 1202, ¶¶ 115-119. The corresponding structure is a filter comprising capacitors, inductors, and resistors arranged as shown in Figures 6 and 16 of the '822 patent:

#### FIGURE 6: COMMON MODE INPUT HASH FILTER

Ex. 1201, Fig. 6 (annotated)

Ex. 1201, Fig. 16 (annotated)

Id., 18:18-33; Ex. 1202, ¶¶ 117-118.

### V. SPECIFIC GROUNDS FOR UNPATENTABILITY

- A. Grounds 1-3: Mori Anticipates, and Mori Alone or in View of Tolbert Renders Obvious, Claims 1-3, 8-10, and 12

- 1. Independent Claim 1

- a. [1A]: "A DC to AC conversion apparatus for converting power from a DC source to produce an power output waveform at a first repetition frequency, comprising"

To the extent the preamble is limiting, Mori discloses it. Ex. 1202, ¶¶ 220-225. As shown in Figures 1 and 2, Mori describes a "multiplex inverter 1" (claimed "DC to AC conversion apparatus") that comprises three single-phase inverters (21-23) (purple) that convert power from multiple DC sources (31-33) (orange) to produce an AC power output waveform ( $V_{inv}$ ) at an output terminal (red) at a first repetition frequency (depicted in Figure 2):

Ex. 1204, Figs. 1 (annotated), 2 (cropped and annotated)

$\textit{Id., \P\P [0007], [0009], [0011]-[0012], [0034], Fig. 16; Ex. 1202, \P\P 221-223.}$

# b. [1B-1C]: "a set of at least one live AC output terminals, at least one output terminal designated as a ground, neutral or reference potential terminal"

Mori's single-phase multiplex converter (green), either individually or as part of a three-phase device, has the claimed "set" of a live AC output terminal 61 (red) and a neutral terminal 62 (blue):

Ex. 1204, Figs. 1, 16 (annotated)

Ex. 1204,  $\P$  [0009], [0034]; Ex. 1202,  $\P$  226-231.

c. [1D]: "a floating DC power source having a positive and a negative terminal connected respectively to the positive and negative DC input terminals of a DC to AC converter"

Mori's inverter (*see* Section V.A.1.a, *supra*) has three DC power sources 31-33 (each a claimed "floating DC power source") each having positive and negative terminals (**orange**) connected respectively to the positive and negative DC input terminals of the DC-to-AC converter (**purple**), which includes three single-phase inverters 21-23 connected in series. Ex. 1204, Figs. 1 (annotated below), 16, ¶ [0009], [0034]; Ex. 1202, ¶ 232.

Like the DC power sources in the '822 patent, Mori's DC power sources 31-33 are floating, since their terminals are connected only to the inputs of the DC-to-AC converter at each respective single-phase inverter 21-23 and are not permanently tied to any established potential such as neutral terminal 62. Ex. 1202, ¶ 233; Ex. 1204, ¶ [0002]; Ex. 1201, 6:17-29, 9:51-60, 23:37-42; Ex. 1236, p. 6; Ex. 1242, p. 6.

As shown below, Mori (right-side) discloses a near identical or equivalent DC to AC converter structure to that of the '822 patent (left-side), with multiple H-bridges (Mori's "single phase converter[s]") having outputs connected in series to generate an AC output (V<sub>inv</sub>) (red) with respect to neutral (blue). Ex. 1204, ¶¶ [0002]-[0012], [0015]-[0016], [0019]-[0021], [0034]; *compare* Ex. 1204, ¶¶ [0009]-[0012], Fig. 1 *with* Ex. 1201, 6:16-9:40, Fig. 1. The '822 patent discloses that any

multiple of H-bridges may be used, such as three as Mori discloses. Ex. 1204,  $\P$  [0011]; Ex. 1201, 6:25-26; Ex. 1202,  $\P$  234.

The H-bridge structures in Mori and the '822 patent are insubstantially different, each including MOSFETs connected together in an identical arrangement. Ex. 1201, 7:51-55, 9:51-59, 12:39-51, 15:36-38; Ex. 1204, Fig. 4, ¶¶ [0009]-[0010], [0015]-[0019]. Moreover, the switch timing of the two inverters is also substantially identical, as shown in the comparative annotated figures below, which juxtaposes the state switching (+1, 0, -1) of H-bridges 23, 22, and 21 from Figure 2 of Mori with that of H-bridges 120a, 120b, 120c of Figure 4 of the '822 patent, respectively.

Ex. 1204, Fig. 2 (cropped, annotated); Ex. 1201, Fig. 4 (cropped, annotated)

Ex. 1204, ¶¶ [0002], [0009]-[0012]; Ex. 1201, 9:51-11:45; Ex. 1202, ¶ 235.

As discussed below (*see* Sections V.A.1.d, V.A.1.e, *infra*), Mori's inverter performs the same function recited with respect to elements [1E] and [1F] (converting power from a floating DC source to AC power with a corresponding common-mode voltage waveform on the DC input) in the same way (using cascaded H-bridges) for the same result (an AC sinewave output and common-mode waveform on the DC inputs). Ex. 1202, ¶ 236.

d. [1E]: "wherein the DC to AC converter causes: (1) an AC output waveform at said first repetition frequency and having a voltage relative to one of said at least one ground, neutral or reference potential terminals to appear with a unique phase at each of a number N at least equal to one of said set of live AC output terminals, and"

Mori's multiplex inverter (*see* Section V.A.1.a, *supra*) causes an AC output waveform (depicted as 74 in Figure 2) at a first repetition frequency with a unique phase (N=1) on terminal 61 (**red**) having a voltage V<sub>inv</sub> relative to neutral 62 (**blue**) (claimed "ground, neutral, or reference potential terminal[]") depicted in Figure 1 (annotated above). Ex. 1202, ¶¶ 237-241; Ex. 1204, Figs. 1-3, ¶¶ [0007], [0009], [0011]-[0013].

e. [1F]: "[wherein the DC to AC converter causes:] (2) a commonmode voltage waveform at a second repetition frequency to appear relative to one of said at least one ground, neutral or reference potential terminals and in the same phase on both of said positive and negative terminals of said DC power source, wherein the second repetition frequency is a multiple equal to the same said number N of said first repetition frequency."

Mori's circuit and switch timing, which are insubstantially different to that of the '822 patent, causes the identical "common-mode voltage waveform ..." of element [1F]. Ex. 1202, ¶¶ 242, 261. As shown below, Mori's H-bridge 23 (purple) is connected at its input to DC power supply 33 (orange) (claimed "DC power source"), and connected at one of its output terminals to neutral 62 (blue) (claimed "ground, neutral, or reference potential terminal[]"), which is the same arrangement

as H-bridge 120a, the 120V DC power source, and the neutral terminal of the '822 patent:

Ex. 1202, ¶ 242; Ex. 1201, 7:51-55, 9:51-59, 12:39-51, 15:36-38; Ex. 1204, ¶¶ [0009]-[0010], [0015]-[0019].

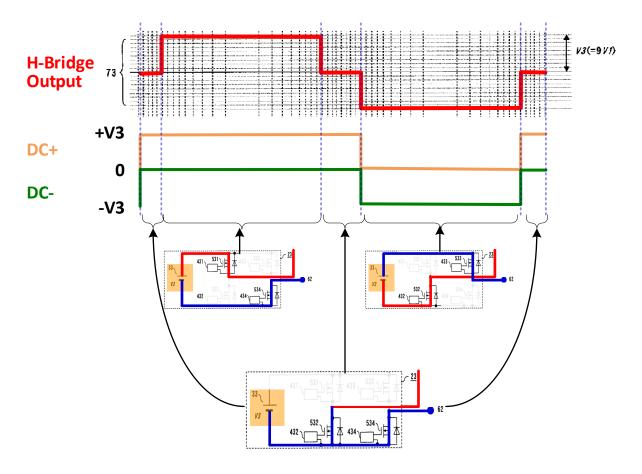

To generate the AC output waveform (*see* Section V.A.1.d, *supra*), Mori's H-bridge 23 modulates between three voltages (+V3, 0, -V3) in a cyclical pattern (**red**) at the same frequency as the sinewave output, which is identical to switching of H-bridge 120a of the '822 patent:

Ex. 1201, Fig. 5 (cropped, annotated)

Ex. 1204, Fig. 2 (cropped, annotated)

Ex. 1202, ¶¶ 243-244; Ex. 1204, ¶¶ [0002], [0004], [0009]-[0012]; Ex. 1201, 10:40-57, 10:65-11:9, 18:21-26, 23:54-57. As the '822 patent acknowledges, this switching causes a 60Hz common-mode voltage square wave on the terminals of the 120V DC supply with respect to neutral. Ex. 1201, Abstract, 4:46-52, 10:35-57, 10:65-11:6, 35:54-58; Ex. 1245 at 9-11; Ex. 1264, 51-57, 302-310; Ex. 1265, 51-57, 323-337, 385-398; Ex. 1213, [0016], Figs. 1, 2, 5. Because Mori's H-bridge 23 has the identical structure and timing, it necessarily causes, and would have been understood to cause, the same common-mode voltage on the terminals of DC supply 33 with respect to neutral. Ex. 1204, Fig. 2, ¶¶ [0002], [0004], [0009]-[0012]; Ex. 1202, ¶ 245.

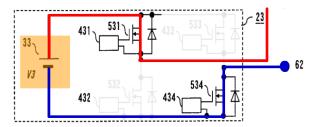

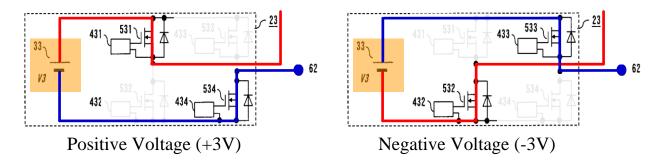

A PHOSITA would have understood that H-bridge 23 generates three output voltages (+V3, 0V, -V3) by connecting the DC supply 33 to the output terminals using the four possible states of the H-bridge that can generate such voltages (as annotated on Figure 1 of Ex. 1204, below):

• Positive State (+3V): transistors 531, 534 are on while transistors 532, 533 are off, connecting DC supply 33 in series between the output terminal (red) and neutral 62 (blue);

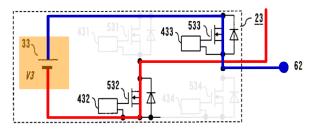

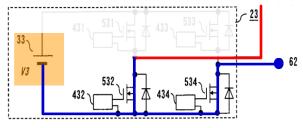

Ex. 1204, Fig. 1 (cropped, annotated)

Negative State (-3V): transistors 532, 533 are on while transistors 531, 534 are off, connecting the DC supply 33 in series and in reverse polarity between the output terminal (red) and neutral 62 (blue);

Id., Fig. 1 (cropped, annotated)

Pass-through High State (0V): transistors 531, 533 are on while transistors 532, 534 are off, connecting the output terminal (red) directly to neutral 62 (blue); and

*Id.*, Fig. 1 (cropped, annotated)

• Pass-through Low State (0V): transistors 532, 534 are on while transistors 531, 533 are off, connecting the output terminal (red) directly to neutral 62 (blue).

Id., Fig. 1 (cropped, annotated)

*See Id.*, ¶¶ [0009]-[0011]; Ex. 1212, pp. 215-217; Ex. 1217, p. 311, Fig. 4; Ex. 1244, pp. 37-38, Fig. 2b; Ex. 1202, ¶ 246.

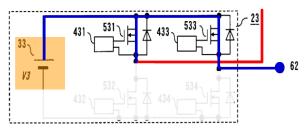

Using these states, as shown below, the output of H-bridge 23 is switched between the three voltages (+V3, 0, -V3) in its cyclical pattern (**red**), with either the positive or negative terminal of DC supply 33 being connected neutral 62 (**blue**). This causes the positive (**orange**) and negative (**green**) terminals of DC supply 33

to shift above (in the positive and pass-through low states) and below (in the negative and pass-through high states) the voltage on the neutral terminal 62 (blue). Ex. 1202, ¶ 247. As illustrated below, this pattern causes a common-mode square waveform to appear at the same frequency as the AC output waveform relative to neutral 62 and in the same phase on both DC+ and DC- terminals of DC supply 33, thus disclosing element [1E]. Ex. 1202, ¶¶ 247-250; Ex. 1204, ¶¶ [0009]-[0011]; Ex. 1212, pp. 215-217; Ex. 1217, p. 311, Fig. 4; Ex. 1244, pp. 37-38, Fig. 2b; Ex. 1245, pp. 10-11.

Ex. 1204, Figs. 1, 2 (cropped, annotated); Ex. 1202, ¶ 248.

In the drawing above where the pass-through low state is used, the positive half of the common-mode waveform (**orange** and **green**) is longer than the negative half of the waveform. Ex. 1202,  $\P$  248. Alternatively, using the pass-through high state as shown below, the positive half is shorter than the negative half. *Id.*,  $\P$  249.

Ex. 1204, Figs. 1, 2 (cropped, annotated); Ex. 1202, ¶ 249.

Mori does not indicate which or if both of the two pass-through states are used to output 0 volts, but one must be used. And, it would have been obvious to use either or both pass-through states, given the limited number of possible schemes for producing Mori's waveforms. Ex. 1202, ¶ 250. Regardless, the difference in using

either pass-through state only slightly changes the generation of the common-mode voltage without changing the common-mode voltage frequency. *Id.* Thus, in any case, the common-mode square waveform has the same frequency as the AC output waveform as required by the claim. *Id.*, ¶¶ 248-251; Ex. 1204, ¶¶ [0009]-[0011]; Ex. 1212, pp. 215-217; Ex. 1217, p. 311, Fig. 4; Ex. 1244, pp. 37-38, Fig. 2b; Ex. 1245, pp. 10-11.

To the extent PO argues that Mori fails to disclose the H-bridge states that cause the claimed common-mode waveform, Tolbert does. Ex. 1202, ¶ 252. Like Mori, Tolbert discloses an inverter in which the outputs of multiple H-bridges are connected in series to generate an AC waveform.

Ex. 1244, Figs. 1 and 2(a) (cropped) (annotated)

Ex. 1202, ¶ 252; Ex. 1244, pp. 37-38.

In Tolbert, each H-bridge is controlled to output +V, 0, and –V (the same as Mori's H-bridge 23) according to 2 bits— $G_{aip}$  which controls transistors S1, S3 in opposite states and  $G_{ain}$  which controls transistors S2, S4 in opposite states. Ex. 1202, ¶ 253; Ex. 1244, pp. 37-38, Figs. 1, 2a. For each side of the H-bridge (S1/S3 on the left and S2/S4 on the right), a bit value of 1 turns on the top transistor and turns off the bottom transistor, and a bit value of 0 turns off the top transistor and turns on the bottom transistor. Ex. 1202, ¶ 253; Ex. 1244, Fig. 2b. These bits control the H-bridge sequentially into the pass-through low state, the positive state, the pass-through high state, and the negative state, creating the common-mode waveform in element [1F] by shifting voltage on the positive (orange) and negative (green) DC input lines above and below neutral (blue) at the same frequency as the H-bridge output (red):

Ex. 1244, Fig. 2(b) (cropped, annotated)

Ex. 1202, ¶¶ 253-256; Ex. 1244, pp. 37-38.

A PHOSITA would have been motivated to use the control bits and sequence taught in Tolbert for controlling Mori's H-bridge 23 because they produce the same voltage outputs disclosed in Mori and because Tolbert teaches this sequence beneficially causes all of the switching devices in the H-bridge to conduct with equal times, equalizing the stress on each device. Ex. 1202, ¶ 257; Ex. 1244, pp. 37-38.

Moreover, such a combination would have been a simple substitution of one known element (Mori's H-bridge control timing) with another known element (Tolbert's H-bridge control timing) to obtain a predictable result (the same H-bridge output waveform and the same input common-mode waveform). Ex. 1202, ¶¶ 258-259.

A PHOSITA would have reasonably expected success in combining these elements as the combination merely requires applying simple logic to control known H-bridge switches, which was well within the level of ordinary skill in the art. *Id.*, ¶ 260.

## 2. Independent Claim 8

a. [8A]: "A method of converting power from a direct current source with improved efficiency to provide AC output power at a standard voltage and frequency and to a number of output terminals corresponding to the number of phases required, comprising:"

To the extent the preamble is limiting, Mori discloses it. Ex. 1202, ¶¶ 274-281. Mori describes a single-phase multiplex inverter 1 that converts power from multiple DC sources to produce a sine wave AC power output waveform ( $V_{inv}$ ) at a single output terminal 61 (claimed "number of output terminals corresponding to the number of phases required"). Ex. 1204, Figs. 1-2, 16, ¶¶ [0007], [0009], [0011]-[0012], [0034]; Ex. 1202, ¶ 275.

Mori's inverter has "improved efficiency" because it reduces CPU processing load compared to prior inverters by using a digital arithmetic circuit, independent

from the CPU, to generate drive signals for H-bridge switches in the inverter. Ex. 1204, ¶¶ [0005]-[0008], [0022]. Further, Mori's inverter has "improved efficiency" by outputting "an extremely smooth voltage waveform," reducing filtering requirements. Ex. 1204, ¶¶ [0012]-[0013]; Ex. 1202, ¶ 277.

A PHOSITA would understand that Mori's AC output is "at a standard voltage and frequency." Ex. 1202, ¶¶ 276-278. Although the '822 patent does not indicate what is "standard," the '822 patent distinguishes AC voltages shaped as single-phase and three-phase sine waves (which have fixed amplitudes and frequencies) as being compatible with a greater variety of loads as compared to other forms of AC power (*e.g.*, square waves). Ex. 1201, 1:10-41. A PHOSITA would have understood that Mori's inverter is compatible with various loads, and thus its output AC voltages are "standard." Ex. 1204, ¶¶ [0001]-[0007]; Ex. 1202, ¶ 278. Accordingly, Mori's "highly accurate" single frequency sine wave voltage, for output to a load, is "at a standard voltage and frequency." Ex. 1202, ¶ 278; Ex. 1204, Figs. 2, 3, ¶¶ [0012]-[0013].

To the extent PO argues that Mori does not disclose a "standard voltage and frequency," these features would have been obvious, since as the '822 patent acknowledges, inverters were known to drive a variety of loads (e.g., induction motors, cellphones, battery chargers, utility grids), and standards existed in the U.S. for powering such loads with sinusoidal voltage at specific amplitudes and

frequencies. Ex. 1202, ¶ 279; Ex. 1201, 1:10-41, 2:32-3:3, 17:51-52("60 Hz AC (in the US)"); 27:27-29, 37:38-43 ("US 277/480-volt service"), Ex. 1237, 2:43-57; Ex. 1238, ¶ [0057]; Ex. 1239, Figs. 1, 4-5, 1:25-29, 3:9-18; Ex. 1240, Fig. 3, 1:40-57, 5:42-44, 6:13-18; Ex. 1232, 14:58-61, 15:19-27, 23:32-34, 33:18-22, 37:40-43, 41:17-20, 48:58-67. Applying such standards for the purpose of making Mori's inverter useful in the U.S. would have been the simple application of a known technique (selecting a standardized voltage and frequency) to a known device (Mori's inverter) in the same way as every other inverter that operated with standardized power in the U.S. (e.g., with a U.S. utility grid). Ex. 1202, ¶ 279. Applying such standards would have been obvious to try because there are a finite number of predictable solutions (due to the standardized voltage level and frequency of the U.S. utility grid) in which Mori's inverter is useful in the U.S., and a PHOSITA would have reasonably expected to succeed in making Mori's inverter useful. Ex. 1202, ¶ 280.

A PHOSITA would have had a high expectation of success in adapting Mori's inverter to such standards, since using them was pervasively well known and within the level of ordinary skill in the art. *Id.*; Ex. 1204, Figs. 2, 3, ¶¶ [0012]-[0013]; Ex. 1237, 2:43-57, Fig. 1.

#### b. [8B]: "configuring said direct current source to be floating"

Mori's DC power sources 31-33 are floating, since their terminals are connected only to the inputs of the inverter and are not permanently tied to any established potential such as neutral 62. Ex. 1202, ¶¶ 281-282; Ex. 1204, ¶ [0002]; Ex. 1201, 6:17-29, 9:51-60, 23:37-42; Ex. 1236, p. 6; Ex. 1242, p. 6. *See* Section V.A.1.c, *supra*.

c. [8C]: "connecting the negative line from said direct current source to a first output terminal required to be instantaneously negative relative to all other output terminals

while deriving from the direct current source positive voltage line the instantaneous voltages required to be output from the other output terminals relative to said first terminal

in a rotating sequence with connecting the positive line from said direct current source to a next-in-sequence output terminal required to be instantaneously positive relative to all other output terminals

while deriving from the negative line of the direct current source the instantaneous voltages relative to said next-in-sequence terminal required to be output from the other terminals"

Mori discloses this limitation. Ex. 1202, ¶¶ 283-290. As discussed (*see* Sections V.A.1.a-c, *supra*), Mori's H-bridge 23 is connected at its input to DC supply 33 (claimed "direct current source"), connected at one output terminal (**red**) to output terminal 61 through H-bridges 21 and 22, and connected at its other output terminal directly to neutral 62 (**blue**):

Ex. 1204, Fig. 1 (annotated)

Ex. 1204, Fig. 2, ¶¶ [0007], [0009], [0011]-[0012], [0034]; Ex. 1202, ¶ 283.

To generate the sine wave output (*see* Sections V.A.1.d, *supra*), Mori and Mori-Tolbert teach modulating H-bridge 23 between three voltages (+V3, 0, -V3) in a cyclical pattern (**red** below, claimed "rotating sequence"), which alternatively connects DC supply 33 (in its positive state) to output terminals 61 (through H-bridges 21 and 22) and 62 during the positive half of the sine wave, and in reverse polarity (in its negative state) to those same terminals during the negative half of the sine wave:

Ex. 1204, Figs. 1, 2 (both cropped and annotated)

Ex. 1204, ¶¶ [0009]-[0011], [0015], [0018]-[0021]; Ex. 1212, pp. 215-217; Ex. 1217, p. 311, Fig. 4; Ex. 1244, pp. 37-38, Fig. 2b; Ex. 1202, ¶ 284.

While in the positive state during the positive half of the output sine wave, H-bridge 23 connects the negative DC input terminal to output terminal 62 (blue) (the "first output terminal") through switch 534, which, at that time, is "instantaneously negative" relative to the other output terminal 61 (red). Ex. 1202, ¶¶ 285-286; Section V.A.1.e, *supra*; Ex. 1204, Figs. 1, 2, ¶¶ [0009]-[0011], [0015], [0018]-[0021]; Ex. 1212, pp. 215-217; Ex. 1217, p. 311, Fig. 4; Ex. 1244, pp. 37-38, Fig. 2b.

While in the negative state during the negative half of the output sine wave, H-bridge 23 connects the positive DC input terminal to output terminal 62 (**blue**) through switch 533, which, at that time, is "instantaneously positive" relative to the other output terminal 61 (**red**) (claimed "next-in-sequence output terminal required to be instantaneously positive relative to all other output terminals"). Ex. 1202, ¶ 287; Section V.A.1.e, *supra*; Ex. 1204, Figs. 1, 2, ¶¶ [0009]-[0011], [0015], [0018]-[0021]; Ex. 1212, pp. 215-217; Ex. 1217, p. 311, Fig. 4; Ex. 1244, pp. 37-38, Fig. 2b.

During both sine wave halves, the sine wave output voltage on output terminal 61 is generated from the input terminal of DC supply 33 not connected to output terminal 62 (and from the other H-bridges 21 and 22) (claimed "deriving from the [direct current source positive/negative line] the instantaneous voltages..."). Ex. 1204, Figs. 1, 2, ¶¶ [0009]-[0011], [0015], [0018]-[0021]; Ex. 1212, pp. 215-217; Ex. 1217, p. 311, Fig. 4; Ex. 1244, pp. 37-38, Fig. 2b; Ex. 1202, ¶¶ 288-290.

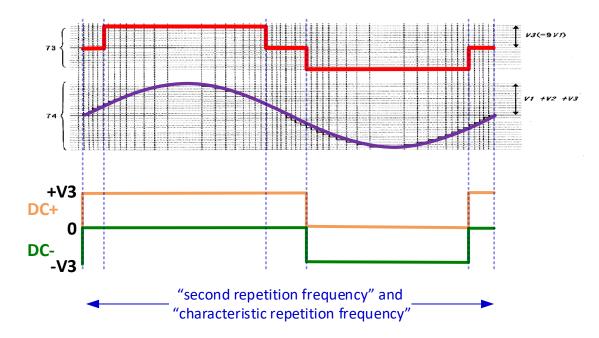

d. [8D]: "selecting the timing of said rotating sequence such that a common mode waveform with a characteristic repetition frequency appears in phase on both the direct current source positive and negative lines."

Mori and Mori-Tolbert discloses this limitation. Ex. 1202, ¶¶ 291-297. As explained (*see* Sections V.A.1.e, V.A.2.c, *supra*), the structure, switch states, and timing of H-bridge 23 in Mori and Mori-Tolbert is the same as that of H-bridge 120a in the '822 patent, resulting in the same common-mode square wave, having the

same frequency as the AC output waveform, superimposed in phase on both terminals of the DC supplies respectively connected to the inputs of the H-bridges. Ex. 1202, ¶¶ 291-297; Ex. 1201, 7:51-55, 9:51-59, 10:40-57, 10:65-11:9, 12:39-51, 15:36-38, 18:21-26, 23:54-57; Ex. 1204, Figs. 2, 4, ¶¶ [0002], [0004], [0009]-[0012], [0015]-[0019]; Ex. 1212, pp. 215-217; Ex. 1217, p. 311, Fig. 4; Ex. 1244, Figs. 1, 2a, 2b, pp. 37-38; Ex. 1245, pp. 10-11; Ex. 1264, 51-57, 302-310; Ex. 1265, 51-57, 323-337, 385-398. Mori's multiplex inverter 1 selects "the timing of said rotating sequence such that a common mode waveform with a characteristic repetition frequency appears in phase on both" inputs from DC supply 33, thus teaching element [8D]. Ex. 1202, ¶ 294.

# 3. Dependent Claim 2

The apparatus of claim 1 wherein said DC to AC converter further comprises: a first electronic switch controlled by a switching controller to connect said positive DC input terminal to the instantaneously most positive of said set of AC output terminals and said at least one ground, neutral or reference potential terminal alternating with connecting said negative DC input terminal to the instantaneously most negative of said set of AC output terminals and said at least one ground, neutral or reference potential terminal

As explained (*see* Sections V.A.1.e, V.A.2.c, *supra*), Mori teaches that H-bridge 23, during the positive half of the output sine wave, connects the negative DC input terminal to neutral output terminal 62 (**blue**), which at this time is more negative than output terminal 61 (**red**), and during the negative half of the output sine wave, connects the positive DC input terminal to neutral output terminal 62

(blue), which at this time is more positive than output terminal 61 (red) (claimed "connect said positive DC input terminal to the instantaneously most positive [AC output terminal] and said [neutral] terminal alternating with connecting said negative DC input terminal to the instantaneously most negative [AC output terminal] and said [neutral] terminal"):

Ex. 1204, Figs. 1 and 2 (both cropped, annotated)

*Id.*, ¶¶ [0009]-[0012], [0015], [0018]-[0021]; Ex. 1212, pp. 215-217; Ex. 1217, p. 311, Fig. 4; Ex. 1202, ¶¶ 262-265; Section V.A.1.e, *supra*.

Alternatively, connecting the positive/negative DC input terminals to output terminal 61 (red) when it is "most positive" during the positive half of the sine wave

and "most negative" during the negative half of the sine wave also teaches claim 2. Ex. 1202, ¶¶ 262-263; Ex. 1204, ¶¶ [0009]-[0012], Fig. 2; Section V.A.1.e, *supra*.

As discussed in Section V.A.1.e, Mori's DC-to-AC converter uses the positive, negative, and at least one of two pass-through states in a manner that discloses claim 2's switching pattern. Ex. 1204, ¶¶ [0009]-[0012], Fig. 2. To the extent PO contends that Mori lacks disclosure of such states, Tolbert discloses a switching pattern that uses them to produce the same output in Mori, as shown below and discussed above in Section V.A.1.e. As shown below, Tolbert's switching pattern includes alternating between using the pass-through low state where the negative (green) terminal of DC supply  $V_{dc}$  is connected to the AC output terminal (red) and neutral (blue) and using the pass-through high state where the positive (orange) terminal of DC supply  $V_{dc}$  is connected to the AC output terminal (red) and neutral (blue):

Ex. 1244, Fig. 2 (cropped, annotated)

Ex. 1244, Fig. 2b, pp. 37-38; Ex. 1212, pp. 215-217; Ex. 1217, p. 311, Fig. 4; Ex. 1202, ¶¶ 266-268.

For the same reasons discussed in Section V.A.1.e (*e.g.*, to produce Mori's voltage waveforms), a PHOSITA would have been motivated to use the switching sequence as taught in Tolbert for Mori's H-bridge 23 and had a reasonable expectation of success. Ex. 1202, ¶¶ 257-260, 268. Thus, whether or not claim 2

requires alternating between both pass-through states, Mori and/or Mori-Tolbert teach claim 2. Ex. 1202, ¶¶ 268-269.

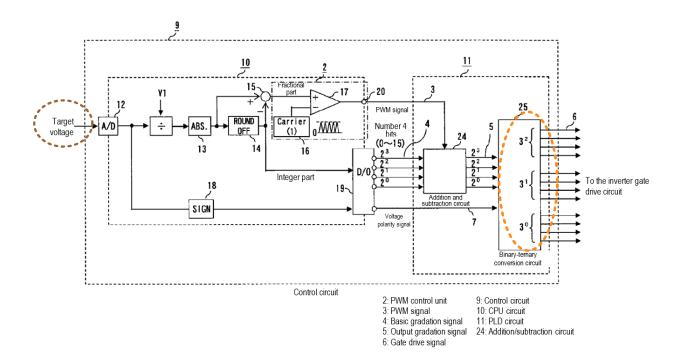

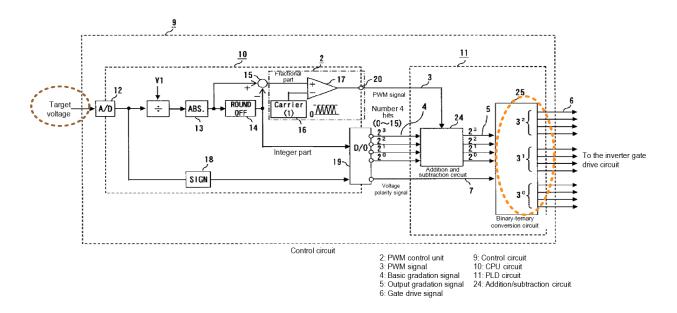

The '822 patent describes a corresponding structure of the "switching controller" as including "a microcontroller" with "memory." Ex. 1201, 12:26-51, 24:8-12; see Section IV.B.2, supra. Mori's control circuit (claimed "switching controller") performs claim 2's function and is similarly described as a "CPU (Central Processing Unit) 10 and a PLD (Programmable Logic Device) circuit 11" and a "microcomputer or a microcomputer-based controller such as a DSP (Digital Signal Processor)." Ex. 1202, ¶ 270; Ex. 1204, ¶¶ [0006]-[0008], [0015], Figs. 4, 9, 10, 13, 15. A PHOSITA would have understood that CPUs and microcomputers execute software stored in memory. Ex. 1202, ¶ 270. Both controllers are insubstantially different from and perform the same functions (as in claim 2) in the same way (controlling H-bridge using drive signals) for the same result (connecting positive and negative DC input terminals to the instantaneously most positive and negative of the AC output terminals and neutral). Id., ¶ 271.

## 4. Dependent Claims 3 and 9

Claim 3: The DC to AC conversion apparatus of claim 1 wherein said second repetition frequency is a multiple equal to the same said number N of said first repetition frequency and said number N is equal to 1, 2 or 3.

Claim 9: The method of claim 8 in which said characteristic frequency is a multiple of 1, 2 or 3 times the AC output power frequency.

Mori's single-phase converter has one live AC output terminal—"N" is 1. *Id.*, ¶¶ 272-273. As explained (*see* Section V.A.1.e, V.A.2.d, *supra*), Mori's common-mode voltage waveform (**orange** and **green**) frequency (claimed "second repetition frequency" and "characteristic frequency") is the same as its AC output's frequency (**purple**) (claimed "first repetition frequency" and "AC output power frequency"):

Ex. 1204, Fig. 2 (cropped, annotated)

Ex. 1204,  $\P$  [0002], [0004], [0009]-[0012]; Ex. 1202,  $\P$  272-273, 298-299.

## 5. Dependent Claim 10

The method of claim 8 in which said step of deriving instantaneous voltages from the direct current source positive line or negative line comprises using one of . . . (b) a pulse-width modulator.

Mori discloses this claim. Ex. 1202, ¶¶ 300-302. As explained, the "step of deriving instantaneous voltages from the direct current source positive line or negative line" is disclosed by the operation of H-bridge 23 in Mori and Mori-Tolbert. *See* Section V.A.2.c, *supra*; Ex. 1202, ¶ 301; Ex. 1204, Figs. 1, 2, ¶¶ [0009]-[0011], [0015], [0018]-[0021]. Mori further discloses PWM control unit 2 in CPU 10 (claimed "pulse-width modulator") that uses "PWM (Pulse Width Modulation) control [] together with gradation control" at the transitions between H-bridge states (purple):

Ex. 1204, Fig. 3 (annotated)

Ex. 1204, Figs. 8-15, ¶¶ [0005], [0011], [0013]-[0015], [0017]-[0018], [0021]-[0034]; Ex. 1202, ¶¶ 301-302.

#### 6. Dependent Claim 12

The method of claim 8 in which said step of deriving instantaneous voltages from the direct current source positive line or negative line comprises expressing a desired voltage using a finite number of digits  $(T(n), T(n-1), T(n-2) \dots T3, T2, T1)$  in a ternary number system such that the instantaneously desired voltage is equal to  $3^m[T(n)+T(n-1)/3+T(n-1)/9+\dots T1/3^{(n-1)}$  or  $3T(n)+T(n-1)+T(n-1)/3+\dots T1/3^{(n-1)}$  times the voltage from said direct current source, where the power m may be zero.

Mori and Mori-Tolbert teach "said step of deriving instantaneous voltages from the direct current source positive line or negative line." *See* Section V.A.2.c, *supra*; Ex. 1202, ¶¶ 303-314. Mori further discloses control circuit 9 that samples a target voltage (**brown**) (claimed "desired voltage") and converts the target voltage into a ternary number having three ternary digits (3², 3¹, 3⁰) (**orange**) (claimed "finite number of digits ([] T3, T2, T1) in a ternary number system"):

Ex. 1204, Fig. 4 (annotated)

Ex. 1204,  $\P$  [0015]-[0019]; Ex. 1202,  $\P$  304.

Each of Mori's H-bridges 23, 22, and 21 is controlled to output its respective input voltage—9V, 3V, and 1V—multiplied by the state (*i.e.*, +1, 0, -1) of the respective corresponding ternary digit (3<sup>2</sup>, 3<sup>1</sup>, 3<sup>0</sup>) so that H-bridge 23 outputs +9V, 0V, or -9V (**red**), H-bridge 22 outputs +3V, 0V, or -3V (**blue**), and H-bridge 21 outputs +1V, 0V, or -1V (**green**)—with the outputs summed to generate a single-phase waveform (**purple**) as a sequence of small voltage gradations:

Ex. 1204, Fig. 2 (annotated)

Ex. 1204, ¶¶ [0002], [0007], [0011]-[0012], [0019]-[0020], claim 1; Ex. 1202, ¶ 305. Mori's instantaneously desired voltage for a phase is 9V\*T3+3V\*T2+1V\*T1. Ex. 1202, ¶ 306.

Claim 12 further recites that the instantaneously desired voltage is equal to either of two recited formulas—one of which is reproduced and annotated below—times the voltage from the DC source:

$$3^{m}[T(n) + T(n-1)/3 + T(n-1)/9 + \dots T1/3^{(n-1)}].$$

Ex. 1201, 42:66-43:7. A PHOSITA would have understood this formula as representing a weighted sum of ternary digits, with the multiplier (the weight) for

each digit defined by a sequence, with the beginning and end of the sequence given by the weights for T1 and T(n), and the middle expression (**blue**) providing a pattern for the weights of the intermediate digits. Ex. 1202, ¶¶ 307-308. However, for  $n \ge 3$ , this middle expression has no discernible pattern, and thus cannot be understood. *Id.*, ¶ 308.

But for n=2, no intermediate digits exist, so a PHOSITA would have understood the formula to simplify to the first and last digit expressions (irrespective of what pattern the middle expression was intended to show for other n values). *Id.*, ¶ 309. Multiplying the formula by "the voltage from said direct current source," the formula for N=2 can be rewritten as:

$$V_{DC} * 3^m * [T2 + T1/3]$$

*Id.* This formula is disclosed by Mori/Mori-Tolbert's control of H-bridges 22 and 23, which output  $\pm 3V$  and  $\pm 9V$  respectively, such that each instantaneous phase voltage is 9\*T2+3\*T1, for voltage steps where the output of H-bridge 21 is 0V. Ex. 1204, Fig. 2, ¶¶ [0002], [0007], [0011]-[0012], [0019]-[0020], claim 1; Ex. 1202, ¶ 310. This matches the above formula with m=0, but "m" can be scaled for different voltages  $V_{DC}$  ( $V_{DC}=V3=9V$  in this Mori/Mori-Tolbert combination). Ex. 1202, ¶ 310. The Mori/Mori-Tolbert combination as described above thus teaches claim 12.

Alternatively, it would also have been obvious to modify Mori/Mori-Tolbert to include only two H-bridges (removing H-bridge 21), such that Mori/Mori-Tolbert describes every voltage step with the formula 9\*T3+3\*T2 discussed above. It was known to include more or less H-bridge levels in Mori's design, with more H-bridges adding more voltage steps, and less H-bridges decreasing complexity, component count, and cost. See e.g., Ex. 1244, pp. 36-37; Ex. 1231 (certified translation of Ex. 1230), Fig. 10, ¶ 24 (discussing simplicity of two-level H-bridge inverter); Ex. 1202, ¶ 311. This would have been nothing more than applying a known technique (reducing the H-bridges from three to two) to improve a similar device (by simplifying the design and reducing cost) in the same way as known to PHOSITAs. Ex. 1244, pp. 36-37; Ex. 1231, Fig. 10, ¶ 24; Ex. 1202, ¶ 312. Similarly, using two H-bridges would have been obvious to try since the design is scalable with only a finite number of possible levels being practical with a reasonable expectation of success. Ex. 1202, ¶ 312.

Moreover, varying the weighting of the multipliers would have been obvious to a PHOSITA in view of Mori/Mori-Tolbert and a PHOSITA's technical ability. *Id.*, ¶313. Mori expressly discloses six other ratios—1:2:4, 1:3:4, 1:3:5, 1:3:6, 1:3:7, and 1:2:8—and that pulse-width-modulating may be used to scale the magnitude of the inverter output from between 0 to V1, 0 to V2, and 0 to V3. Ex. 1204, Figs. 2-