### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

| In re <i>Ex Parte</i> Reexamination of:                           | )                                         |

|-------------------------------------------------------------------|-------------------------------------------|

| U. S. Patent No. 9,786,822                                        | ) Control No.: <i>To be assigned</i>      |

| Issue Date: Oct. 10, 2017                                         | ) Group Art Unit: <i>To be assigned</i>   |

| Inventor: Mordehai Margalit                                       | ) Examiner: To be assigned                |

| Appl. No. 14/570,449                                              | ) Confirmation No.: <i>To be assigned</i> |

| Filing Date: Dec. 15, 2014                                        | )                                         |

| For: LIGHT EMITTING DIODE<br>PACKAGE AND METHOD OF<br>MANUFACTURE | )<br>)<br>)                               |

| Mail Stop <i>Ex Parte</i> Reexam                                  |                                           |

Mail Stop *Ex Parte* Reexam Attn: Central Reexamination Unit Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

Dear Commissioner:

## REQUEST FOR EX PARTE REEXAMINATION OF U.S. PATENT NO. 9,786,822

# TABLE OF CONTENTS

| I.   | Introduction1 |                                                              |                                                                     |  |

|------|---------------|--------------------------------------------------------------|---------------------------------------------------------------------|--|

| II.  | Relat         | Related Proceedings1                                         |                                                                     |  |

| III. | Ident         | Identification of Claims and Citation of Prior Art Presented |                                                                     |  |

| IV.  | Over          | view of tl                                                   | ne '822 Patent                                                      |  |

|      | A.            | Specifi                                                      | cation and Drawings of the '822 Patent                              |  |

|      | В.            | Prosec                                                       | ution History of the '822 patent                                    |  |

|      | C.            | The Ef                                                       | fective Priority Date of the '822 Patent                            |  |

| V.   | Clain         | n Constru                                                    | rction                                                              |  |

| VI.  | State         | ment of S                                                    | Substantial New Questions of Patentability                          |  |

|      | A.            | SNQ1:                                                        | <i>Epler</i> Discloses or Suggests Claims 1, 2, 5-7, and 9 12       |  |

|      |               | 1.                                                           | Overview of <i>Epler</i>                                            |  |

|      |               | 2.                                                           | Claim 1                                                             |  |

|      |               | 3.                                                           | Claim 2                                                             |  |

|      |               | 4.                                                           | Claim 5                                                             |  |

|      |               | 5.                                                           | Claim 6                                                             |  |

|      |               | 6.                                                           | Claim 7                                                             |  |

|      |               | 7.                                                           | Claim 9                                                             |  |

|      | В.            | SNQ2:                                                        | Epler in View of Fan Discloses or Suggests Claim 8                  |  |

|      |               | 1.                                                           | Claim 8                                                             |  |

|      | C.            | SNQ3:                                                        | <i>Epler</i> in View of <i>Aldaz</i> Discloses or Suggests Claim 10 |  |

|      |               | 1.                                                           | Claim 10                                                            |  |

|      | D.            | SNQ4:                                                        | Epler in View of Lester Discloses or Suggests Claims 1, 2, 5-7,     |  |

|      |               | and 9                                                        |                                                                     |  |

|      |               | 1.                                                           | Claim 1                                                             |  |

|      |               | 2.                                                           | Claims 2, 5-7, and 9 40                                             |  |

|      | E.            | SNQ5:                                                        | Epler in View of Lester and Fan Discloses or Suggests Claim 8       |  |

|      | F.            | SNQ6:                                                        | Epler in View of Lester and Aldaz Discloses or Suggests Claim 10 41 |  |

|      | G.            | SNQ7:                                                        | Epler in View of Han Discloses or Suggests Claims 1, 2, 5-7, and    |  |

|      |               | 9                                                            |                                                                     |  |

|      | H.            | SNQ8:                                                        | Epler in View of Han and Fan Discloses or Suggests Claim 8          |  |

| I.                      | SNQ9: Epler in View of Han and Aldaz Discloses or Suggests Claim 10 |                                                                    |    |

|-------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|----|

| J.                      | SNQ1                                                                | 0: Epler in View of Han and Lester Discloses or Suggests Claims 1, |    |

|                         | 2, 5-7,                                                             | , and 9                                                            | 43 |

| K.                      | SNQ1                                                                | 1: Epler in View of Han, Lester, and Fan Discloses or Suggests     |    |

|                         | Claim                                                               | 8                                                                  | 44 |

| L.                      | SNQ1                                                                | 2: Epler in View of Han, Lester, and Aldaz Discloses or Suggests   |    |

| Claim 10                |                                                                     | 10                                                                 | 44 |

| M.                      | SNQ1                                                                | 3: Epler in View of Nagahama Discloses or Suggests Claims 1, 2,    |    |

|                         | 5-7, ai                                                             | nd 9                                                               | 44 |

| N.                      | SNQ1                                                                | 4: Epler in View of Nagahama and Fan Discloses or Suggests         |    |

|                         | Claim                                                               | 8                                                                  | 46 |

| О.                      | SNQ1                                                                | 5: Epler in View of Nagahama and Aldaz Discloses or Suggests       |    |

|                         | Claim                                                               | 10                                                                 | 46 |

| P.                      | SNQ1                                                                | 6: Epler in View of Nagahama and Lester Discloses or Suggests      |    |

| Claims 1, 2, 5-7, and 9 |                                                                     | s 1, 2, 5-7, and 9                                                 | 46 |

| Q.                      | SNQ1                                                                | 7: Epler in View of Nagahama, Lester, and Fan Discloses or         |    |

|                         | Sugge                                                               | sts Claim 8                                                        | 46 |

| R.                      | SNQ1                                                                | 8: Epler in View of Nagahama, Lester, and Aldaz Discloses or       |    |

|                         | Sugge                                                               | sts Claim 10                                                       | 47 |

| S.                      | SNQ1                                                                | 9: Shimokawa Discloses Claims 1, 2, and 5-10                       | 47 |

|                         | 1.                                                                  | Overview of Shimokawa                                              | 47 |

|                         | 2.                                                                  | Claim 1                                                            | 48 |

|                         | 3.                                                                  | Claim 2                                                            | 61 |

|                         | 4.                                                                  | Claim 5                                                            | 61 |

|                         | 5.                                                                  | Claim 6                                                            | 62 |

|                         | 6.                                                                  | Claim 7                                                            | 62 |

|                         | 7.                                                                  | Claim 8                                                            | 62 |

|                         | 8.                                                                  | Claim 9                                                            | 63 |

|                         | 9.                                                                  | Claim 10                                                           | 63 |

| Τ.                      | SNQ2                                                                | 0: Shimokawa in View of Aldaz Discloses or Suggests Claim 10       | 63 |

|                         | 1.                                                                  | Claim 10                                                           | 63 |

| U.    | SNQ21: Shimokawa in View of Han Discloses or Suggests Claims 1, 2,        |    |  |

|-------|---------------------------------------------------------------------------|----|--|

|       | and 5-10                                                                  | 66 |  |

| V.    | SNQ22: Shimokawa in View of Han and Aldaz Discloses or Suggests           |    |  |

|       | Claim 10                                                                  | 68 |  |

| W.    | SNQ23: Shimokawa in View of Nagahama Discloses or Suggests Claims         |    |  |

|       | 1, 2, and 5-10                                                            | 68 |  |

| Х.    | SNQ24: Shimokawa in View of Nagahama and Aldaz Discloses or               |    |  |

|       | Suggests Claim 10                                                         | 70 |  |

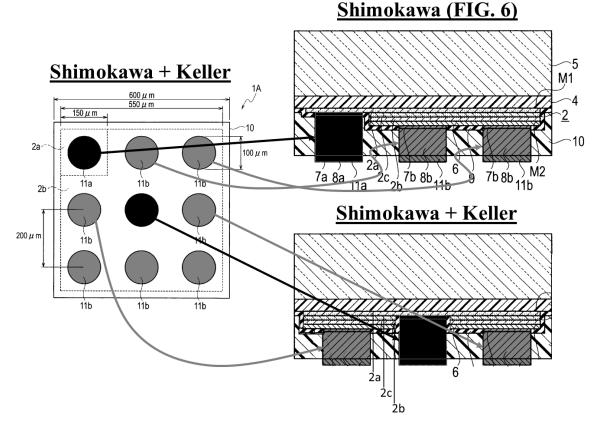

| Y.    | SNQ25: Shimokawa in view Keller Discloses or Suggests Claims 1, 2, and    |    |  |

|       | 5-10                                                                      | 70 |  |

| Z.    | SNQ26: Shimokawa in View of Keller and Aldaz Discloses or Suggests        |    |  |

|       | Claim 10                                                                  | 75 |  |

| AA.   | SNQ27: Shimokawa in View of Keller and Han Discloses or Suggests          |    |  |

|       | Claims 1, 2, and 5-10                                                     | 75 |  |

| BB.   | SNQ28: Shimokawa in View of Keller, Han, and Aldaz Discloses or           |    |  |

|       | Suggests Claim 10                                                         | 75 |  |

| CC.   | SNQ29: Shimokawa in view Keller and Nagahama of Discloses or              |    |  |

|       | Suggests Claims 1, 2, and 5-10                                            | 75 |  |

| DD.   | SNQ30: Shimokawa in view of Keller, Nagahama, and Aldaz Discloses or      |    |  |

|       | Suggests Claim 10                                                         | 75 |  |

| Detai | led Explanation of the Pertinence and Manner of Applying the Prior Art to |    |  |

| the C | laims                                                                     | 75 |  |

| A.    | Bases for Proposed Rejections of the Claims                               | 75 |  |

| B.    | Proposed Rejections                                                       | 77 |  |

|       | 1. Proposed Rejection #1                                                  | 78 |  |

|       | 2. Proposed Rejection #2                                                  | 78 |  |

|       | 3. Proposed Rejection #3                                                  | 78 |  |

|       | 4. Proposed Rejection #4                                                  | 78 |  |

|       | 5. Proposed Rejection #5                                                  | 78 |  |

|       | 6. Proposed Rejection #6                                                  | 78 |  |

|       | 7. Proposed Rejection #7                                                  | 78 |  |

VII.

|       | 8.         | Proposed Rejection #8  | 79 |

|-------|------------|------------------------|----|

|       | 9.         | Proposed Rejection #9  | 79 |

|       | 10.        | Proposed Rejection #10 | 79 |

|       | 11.        | Proposed Rejection #11 | 79 |

|       | 12.        | Proposed Rejection #12 | 79 |

|       | 13.        | Proposed Rejection #13 | 79 |

|       | 14.        | Proposed Rejection #14 | 79 |

|       | 15.        | Proposed Rejection #15 | 80 |

|       | 16.        | Proposed Rejection #16 | 80 |

|       | 17.        | Proposed Rejection #17 | 80 |

|       | 18.        | Proposed Rejection #18 | 80 |

|       | 19.        | Proposed Rejection #19 | 80 |

|       | 20.        | Proposed Rejection #20 | 80 |

|       | 21.        | Proposed Rejection #21 | 80 |

|       | 22.        | Proposed Rejection #22 | 81 |

|       | 23.        | Proposed Rejection #23 | 81 |

|       | 24.        | Proposed Rejection #24 | 81 |

|       | 25.        | Proposed Rejection #25 | 81 |

|       | 26.        | Proposed Rejection #26 | 81 |

|       | 27.        | Proposed Rejection #27 | 81 |

|       | 28.        | Proposed Rejection #28 | 81 |

|       | 29.        | Proposed Rejection #29 | 82 |

|       | 30.        | Proposed Rejection #30 | 82 |

| VIII. | Conclusion |                        | 82 |

# LIST OF EXHIBITS

| Ex. PAT-A     | U.S. Patent No. 9,786,822 ("the '822 patent")                                                      |

|---------------|----------------------------------------------------------------------------------------------------|

| Ex. PAT-B     | Prosecution History of the '822 patent                                                             |

| Ex. PA-DEC    | Declaration of Dr. Baker                                                                           |

| Ex. PA-DEC CV | Curriculum vitae of Dr. Baker                                                                      |

| Ex. PA-1      | U.S. Patent Application Publication No. 2010/0019260 to Epler <i>et al.</i> (" <i>Epler</i> ")     |

| Ex. PA-2      | U.S. Patent No. 6,562,709 to Lin ("Lin")                                                           |

| Ex. PA-3      | U.S. Patent No. 8,581,291 to Shimokawa <i>et al.</i> ("Shimokawa")                                 |

| Ex. PA-4      | U.S. Patent No. 5,716,862 to Ahmad et al.("Ahmad")                                                 |

| Ex. PA-5      | U.S. Patent Application Publication No. 2010/0314635 to Brunner <i>et al.</i> (" <i>Brunner</i> ") |

| Ex. PA-6      | U.S. Patent Application Publication No. 2004/0130002 to Weeks <i>et al.</i> (" <i>Weeks</i> ")     |

| Ex. PA-7      | U.S. Patent Application Publication No. 2009/0090932 to Bour <i>et al.</i> (" <i>Bour</i> ")       |

| Ex. PA-8      | U.S. Patent Application Publication No. 2010/0314651 to Lin (" <i>Lin II</i> ")                    |

| Ex. PA-9      | U.S. Patent Application Publication No. 2004/0000672 to Fan <i>et al.</i> (" <i>Fan</i> ")         |

| Ex. PA-10 | U.S. Patent Application Publication No. 2008/0153281<br>to Knollenberg <i>et al.</i> (" <i>Knollenberg</i> ") |

|-----------|---------------------------------------------------------------------------------------------------------------|

| Ex. PA-11 | U.S. Patent Application Publication No. 2010/0308367 to Aldaz <i>et al.</i> (" <i>Aldaz</i> ")                |

| Ex. PA-12 | U.S. Patent Application Publication No. 2010/0084675 to Ueno <i>et al.</i> (" <i>Ueno</i> ")                  |

| Ex. PA-13 | U.S. Patent Application Publication No. 2009/0166644 to Hiroyama <i>et al.</i> (" <i>Hiroyama</i> ")          |

| Ex. PA-14 | U.S. Patent Application Publication No. 2008/0293177 to Kim <i>et al.</i> (" <i>Kim</i> ")                    |

| Ex. PA-15 | U.S. Patent Application Publication No. 2005/0017262 to Shei <i>et al.</i> (" <i>Shei</i> ")                  |

| Ex. PA-16 | U.S. Patent Application Publication No. 2011/0037086 to Kim <i>et al.</i> (" <i>Kim IP</i> ")                 |

| Ex. PA-17 | U.S. Patent No. 6,657,234 to Tanizawa ("Tanizawa")                                                            |

| Ex. PA-18 | U.S. Patent Application Publication No. 2005/0067613 to Kim ("Kim III")                                       |

| Ex. PA-19 | U.S. Patent Application Publication No. 2010/0301307 to Fattal <i>et al.</i> (" <i>Fattal</i> ")              |

| Ex. PA-20 | U.S. Patent Application Publication No. 2008/0251781 to Han <i>et al.</i> (" <i>Han</i> ")                    |

| Ex. PA-21 | U.S. Patent Application Publication No. 2008/0006836 to Lee (" <i>Lee</i> ")                                  |

| Ex. PA-22 | U.S. Patent Application Publication No. 2008/0286894 to Chae <i>et al.</i> (" <i>Chae</i> ")                           |

|-----------|------------------------------------------------------------------------------------------------------------------------|

| Ex. PA-23 | U.S. Patent Application Publication No. 2002/0050600 to Hayakawa (" <i>Hayakawa</i> ")                                 |

| Ex. PA-24 | U.S. Patent Application Publication No. 2010/0203661 to Hodota (" <i>Hodota</i> ")                                     |

| Ex. PA-25 | U.S. Patent No. 5,679,965 to Schetzina ("Schetzina")                                                                   |

| Ex. PA-26 | Schubert, Light Emitting Diodes, Second Edition, 2006 ("Schubert")                                                     |

| Ex. PA-27 | U.S. Patent Application Publication No. 2004/0256631 to Shin ("Shin")                                                  |

| Ex. PA-28 | U.S. Patent Application Publication No. 2005/0194605 to Shelton <i>et al.</i> ("Shelton")                              |

| Ex. PA-29 | U.S. Patent Application Publication No. 2008/0217629 to Lee <i>et al.</i> (" <i>Lee II</i> ")                          |

| Ex. PA-30 | Boulanger, Thermoelectric Material Electroplating A<br>Historical Review (2010) ("Boulanger")                          |

| Ex. PA-31 | Datta, Electrochemical Processing Technologies in<br>Chip Fabrication Challenges and Opportunities (2003)<br>("Datta") |

| Ex. PA-32 | U.S. Patent Application Publication No. 2012/0126262 to Huang <i>et al.</i> (" <i>Huang</i> ")                         |

| Ex. PA-33 | U.S. Patent Application Publication No. 2008/0296604 to Chou <i>et al.</i> (" <i>Chou</i> ")                           |

|           | ·                                                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. PA-34 | U.S. Patent No. 7,791,090 to Lester et al. ("Lester")                                                                                                       |

| Ex. PA-35 | Japanese Unexamined Patent Application Publication<br>No. 2004-327636 (Nov. 18 2004) (English translation)<br>to Hanaoka <i>et al.</i> (" <i>Hanaoka</i> ") |

| Ex. PA-36 | U.S. Patent No. 7,105,857 to Nagahama <i>et al.</i> (" <i>Nagahama</i> ")                                                                                   |

| Ex. PA-37 | U.S. Patent Application Publication No. 2009/0121241 to Keller <i>et al.</i> (" <i>Keller</i> ")                                                            |

| Ex. PA-38 | U.S. Patent Application Publication No. 2005/0133806 to Peng <i>et al.</i> (" <i>Peng</i> ")                                                                |

| Ex. PA-39 | U.S. Patent Application Publication No. 2012/0012871 to Hsia <i>et al.</i> (" <i>Hsia</i> ")                                                                |

| Ex. PA-40 | U.S. Patent Application Publication No. 2006/0157717 to Nagai <i>et al.</i> (" <i>Nagai</i> ")                                                              |

| Ex. PA-41 | U.S. Patent Application Publication No. 2007/0164454 to Andrews (" <i>Andrews</i> ")                                                                        |

| Ex. PA-42 | U.S. Patent Application Publication No. 2004/0150097 to Gaynes <i>et al.</i> (" <i>Gaynes</i> ")                                                            |

| Ex. PA-43 | U.S. Patent No. 5,770,216 to Mitchnick <i>et al.</i> (" <i>Mitchnick</i> ")                                                                                 |

| Ex. LIT-1 | Complaint (Dkt. #1), LED Wafer Sols. LLC v. Samsung<br>Elecs. Co., No 6:21-CV-00292 (W.D. Tex. Mar. 25,<br>2021)                                            |

| Ex. LIT-2 | Joint Claim Construction Statement (Dkt. #59), LED<br>Wafer Sols. LLC v. Samsung Elecs. Co., No 6:21-CV-<br>00292 (W.D. Tex. Feb. 21, 2022)                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ex. LIT-3 | Patent Owner '822 Patent Infringement Contentions,<br>LED Wafer Sols. LLC v. Samsung Elecs. Co., No 6:21-<br>CV-00292 (W.D. Tex.)                                       |

| Ex. LIT-4 | Transfer of LED Wafer Sols. LLC v. Samsung Elecs.<br>Co., No 6:21-CV-00292 (W.D. Tex.) to LED Wafer<br>Sols. LLC v. Samsung Elecs. Co., No 3:22-CV-04809<br>(N.D. Cal.) |

#### I. Introduction

An *ex parte* reexamination is requested on claims 1, 2, and 5-10 ("the challenged claims") of U.S. Patent No. 9,786,822, which issued on October 10, 2017 to Margalit ("the '822 patent," Ex. PAT-A), for which the U.S. Patent and Trademark Office ("Office") files identify LED Wafer Solutions LLC ("LED Wafer" or "Patent Owner") as the assignee. In accordance with 37 C.F.R. § 1.510(b)(6), Requester Samsung Electronics Co., Ltd. ("Requester") hereby certifies that the statutory estoppel provisions of 35 U.S.C. § 315(e)(1) and 35 U.S.C. § 325(e)(1) do not prohibit it from filing this *ex parte* reexamination request.

This request raises substantial new questions of patentability based on prior art that the Office did not have before it or did not fully consider during the prosecution of the '822 patent, and which discloses or suggests the features recited in the challenged claims. Requester respectfully urges that this request be granted and that reexamination be conducted with "special dispatch" pursuant to 35 U.S.C. § 305. The Office should find the claims unpatentable over this art.

In accordance with 37 C.F.R. § 1.20(c), the fee for *ex parte* reexamination (nonstreamlined) is submitted herewith. If this fee is missing or defective, please charge the fee as well as any additional fees that may be required to Deposit Account No. 50-2613.

#### II. Related Proceedings

On March 25, 2021, Patent Owner filed suit against Requester asserting, *inter alia*, infringement of the '822 patent in *LED Wafer Solutions LLC v. Samsung Electronics Co., Ltd.*, No 6-21-CV-00292 (W.D. Tex.). (Ex. LIT-1.) Thereafter, on August 22, 2022, the case was transferred to *LED Wafer Solutions LLC v. Samsung Electronics Co., Ltd.*, No 3-22-CV-04809 (N.D. Cal.). (Ex. LIT-4.)

Requester filed an *inter partes* review petition against the '822 patent on September 10, 2021. IPR2021-01526, Paper 1. The Patent Trial and Appeal Board ("the PTAB") denied that petition on March 22, 2022. IPR2021-01526, Paper 9. Petitioner's motion for rehearing of the decision was denied on June 8, 2022. IPR2021-01526, Papers 10 and 11.

This request, however, does not raise "the same or substantially the same prior art or arguments" previously presented, including in IPR2021-01526. 35 U.S.C. § 325(d). This request is based on prior art that the Office did not have before it or did not fully consider during the prosecution of the '822 patent, that the PTAB did not have before it in IPR2021-01526, and which

discloses or suggests the features recited in the challenged claims, especially under the broadest reasonable interpretation standard applicable to this request. This request also presents new combinations of references that were not before the Office or the PTAB. In fact, no prior art references were applied to the claims in any office action during prosecution. (Ex. PAT-B, 11-18 (Notice of Allowance), 69-73 (Non-Final Office Action), 119-123 (Restriction Requirement).) And the references used in this request are substantially different than those used in IPR2021-01526. In IPR2021-01526, the PTAB denied institution, because it determined that Petitioner had not demonstrated sufficiently that Wirth (U.S. Patent No. 8,835,937) teaches or suggests "a first surface of said semiconductor LED contacts a first portion of a bottom surface of said optically transparent layer," as recited in claim 1. IPR2021-01526, Paper 9 at 8-14 (P.T.A.B. Mar. 22, 2022). The Board reached this determination based on its finding that "Petitioner has not explained adequately why a person of ordinary skill in the art would have considered Wirth's current spreading layer to be part of the claimed 'semiconductor LED' in view of Wirth's teachings." IPR2021-01526, Paper 9 at 8-14 (P.T.A.B. Mar. 22, 2022). This request neither cites Wirth nor maps to a current spreading layer as a part of any semiconductor LED. As discussed below in Section VI, the primary references in this request (Epler and Shimokawa) provide substantially different disclosure regarding this limitation. Regardless, the Office erred in a manner material to patentability by not considering the teachings, arguments, obviousness combinations, and evidence presented in this request (Section VI).

#### III. Identification of Claims and Citation of Prior Art Presented

Requester respectfully requests reexamination of claims 1, 2, and 5-10 of the '822 patent in view of the following prior art references, which are also listed on the attached PTO Form SB/08.

| Ex. PA-1  | U.S. Patent Application Publication No. 2010/0019260 to Epler <i>et al.</i> (" <i>Epler</i> ") |

|-----------|------------------------------------------------------------------------------------------------|

| Ex. PA-9  | U.S. Patent Application Publication No. 2004/0000672 to Fan <i>et al.</i> (" <i>Fan</i> ")     |

| Ex. PA-11 | U.S. Patent Application Publication No. 2010/0308367 to Aldaz <i>et al.</i> (" <i>Aldaz</i> ") |

| Ex. PA-34 | U.S. Patent No. 7,791,090 to Lester et al. ("Lester")                                      |

|-----------|--------------------------------------------------------------------------------------------|

| Ex. PA-3  | U.S. Patent No. 8,581,291 to Shimokawa <i>et al.</i> (" <i>Shimokawa</i> ")                |

| Ex. PA-20 | U.S. Patent Application Publication No. 2008/0251781 to Han <i>et al.</i> (" <i>Han</i> ") |

| Ex. PA-36 | U.S. Patent No. 7,105,857 to Nagahama <i>et al.</i> (" <i>Nagahama</i> ")                  |

| Ex. PA-37 | U.S. Patent Application Publication No. 2009/0121241 to Keller et al. (" <i>Keller</i> ")  |

A copy of each of the above-listed references is attached to this request pursuant to 37 C.F.R. § 1.510(b)(3). A copy of the '822 patent is also attached to this request as Exhibit PAT-A pursuant to 37 C.F.R. § 1.510(b)(4).

#### IV. Overview of the '822 Patent

#### A. Specification and Drawings of the '822 Patent

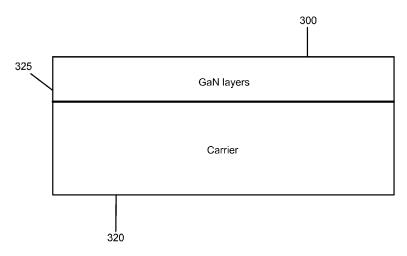

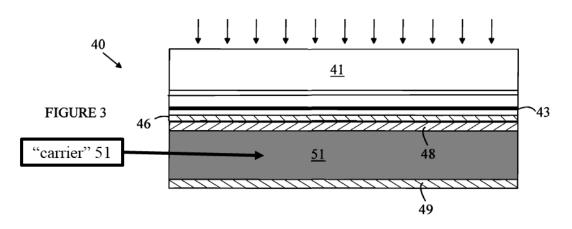

The '822 patent relates to "a light emitting diode (LED) device." (Ex. PAT-A, 1:16-19; *see also id.*, Abstract, 2:6-30; Ex. PA-DEC, ¶31.) The '822 patent admits that light emitting diode (LED) devices were well known and depicts a prior art LED device in Figure 3 below. (Ex. PAT-A, 2:54-59, 4:16-18, FIGs. 1-3.)

#### (Ex. PAT-A, FIG. 3; Ex. PA-DEC, ¶31.)

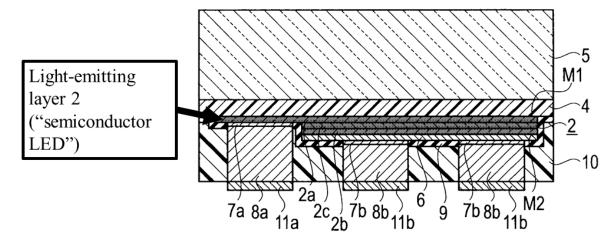

The prior art light emitting device 30 of Figure 3 includes a semiconductor LED layer 300, a metallic interface 325,<sup>1</sup> and a carrier layer 320. (Ex. PAT-A, 3:64-4:2, 4:16-18.) The semiconductor LED layer 300 includes a GaN layer. (*Id.*, FIG. 3.) GaN refers to a gallium nitride "which is a type of bandgap semiconductor suited for use in high power LEDs." (*Id.*, 3:28-30.) The '822 patent states that GaN LEDs "comprise a P-I-N junction device having an intrinsic (I) layer disposed between a N-type doped layer and a P-type doped layer." (*Id.*, 3:32-34; Ex. PA-DEC, ¶32.)

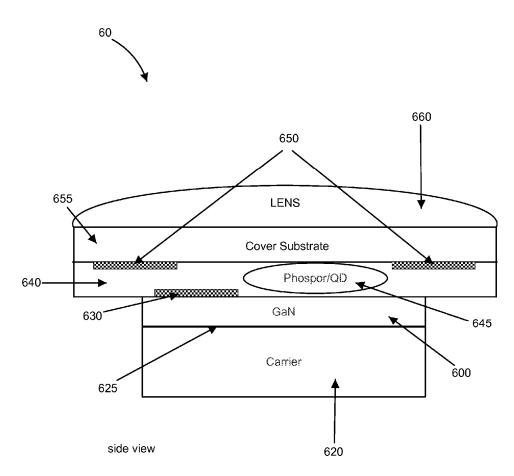

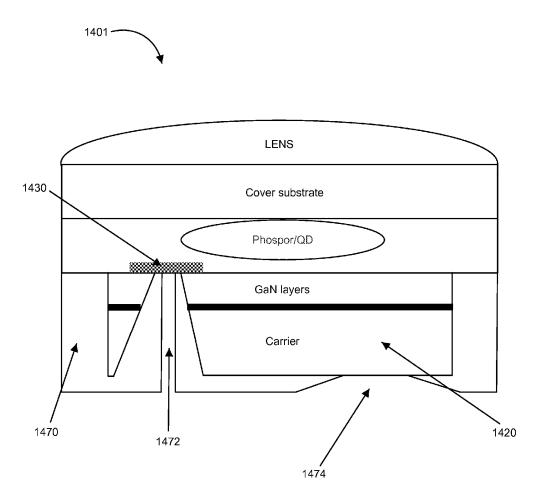

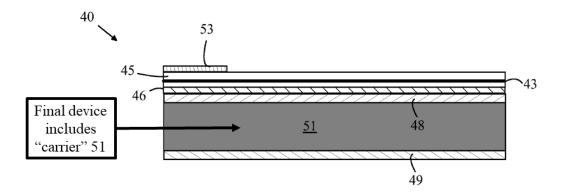

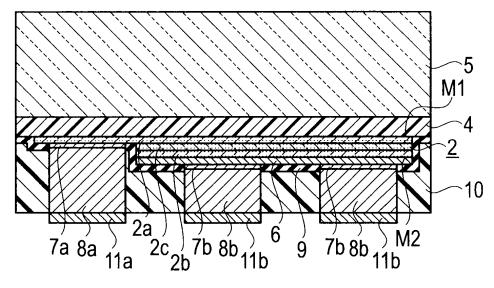

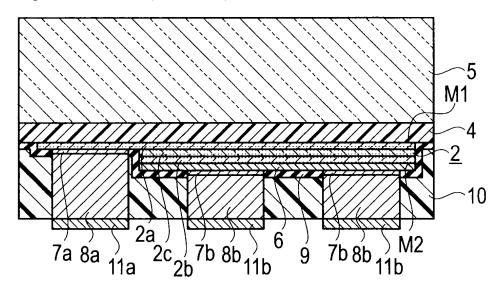

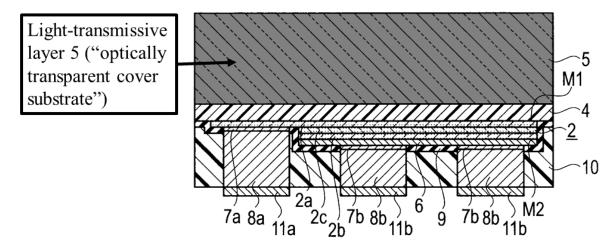

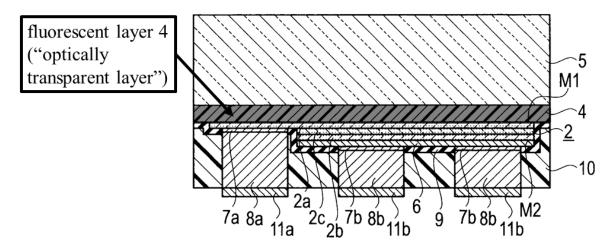

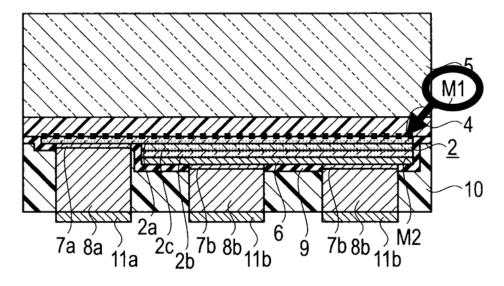

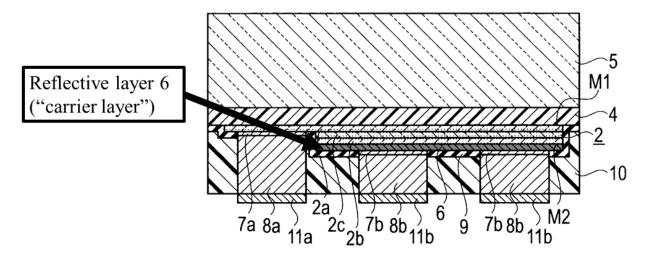

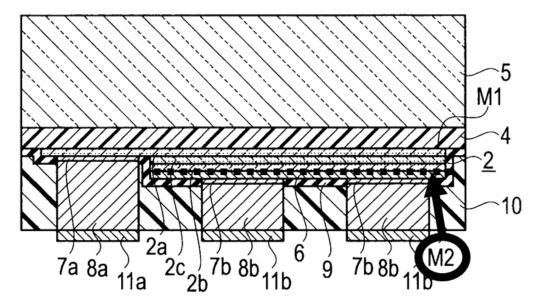

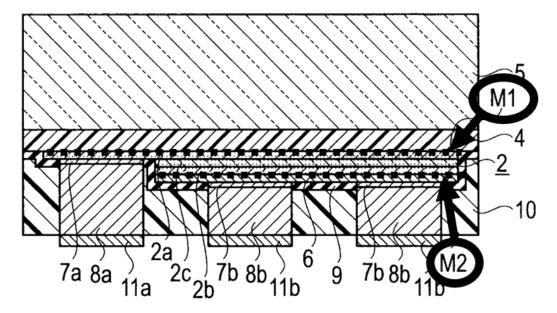

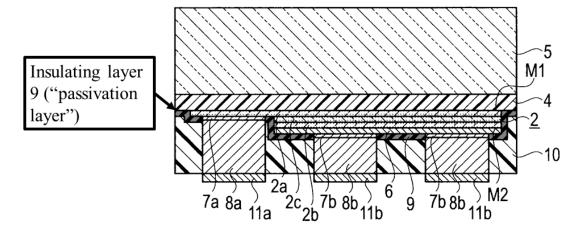

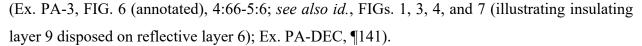

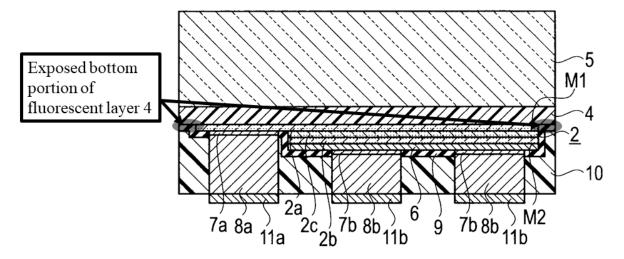

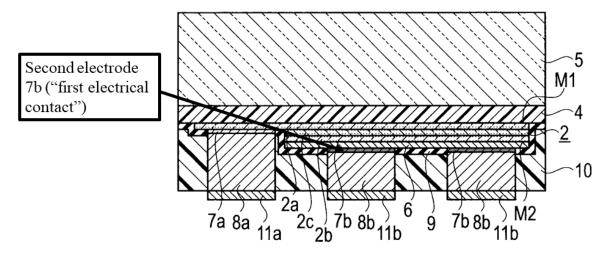

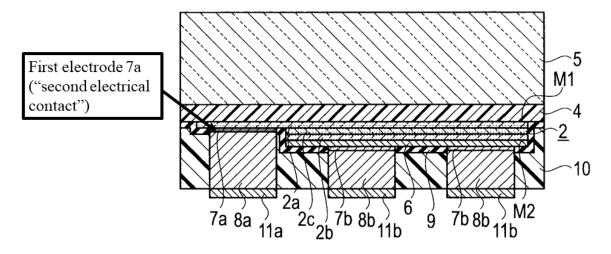

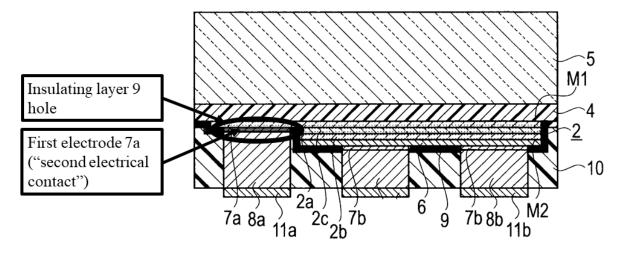

The disclosed embodiments of the '822 patent build on the prior art device of Figure 3. For instance, the disclosed embodiments describe an LED device comprised of additional layers that "act to promote mechanical, electrical, thermal, or optical characteristics of the device" (Ex. PAT-A, 2:2-4, 19-23; *see also id.*, Abstract), as seen in Figures 6 and 14, reproduced below. (*Id.*, 4:55-59, 7:16-23, FIGS. 6, 14; *see also id.*, 2:64-66, 3:13-14; Ex. PA-DEC, ¶33.) Like the prior-art LED device in Figure 3 above, each of the devices 60 and 1401 in Figures 6 and 14, respectively, includes the GaN LED layer separated from the carrier layer by a metallic interface (e.g., element 625 in Figure 6 and the dark black line between "GaN layers" and "Carrier" in Figure 14). (*Id.*, 4:55-59; *compare id.*, FIGs. 6, 14 *with* FIG. 3.)

<sup>&</sup>lt;sup>1</sup> Element 325 points to GaN layers in Figure 3, but element 325 is described as a metallic interface in the '822 patent. (Ex. PAT-A, FIG. 3, 3:64-4:2, 4:16-18.)

#### (Id., FIG. 6; Ex. PA-DEC, ¶33.)

The LED device 60, as shown by Figure 6 above, further includes an optically transparent or transmissive adhesive layer 640 (*id.*, 4:60-65), a cover substrate 655 (*id.*, 5:17-24), and an optical lens 660 (*id.*, 5:25-30). The transparent or optically permissive adhesive layer 640 may contain "a region containing phosphor and/or quantum dot material (QD) 645." (*Id.*, 5:9-11.) The optical lens 660 "act[s] to spread, diffuse, collimate, or otherwise redirect and form the output of the LED." (*Id.*, 5:26-30.) Like device 60 in Figure 6, the device 1401 in Figure 14 below includes similar layers. (*Id.*, 7:16-23; Ex. PA-DEC, ¶34.)

#### (Ex. PAT-A, FIG. 14; Ex. PA-DEC, ¶34.)

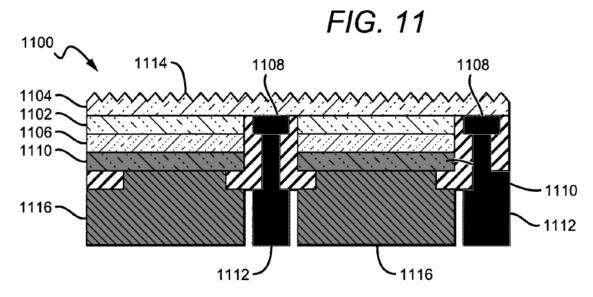

Device 1401 further includes a passivation layer 1470. (Ex. PAT-A, 7:19-21; *see also id.*, 6:22-26 (the device in Figure 11 "including a passivation layer 1170 that has been applied to surround certain portions of the device around LED semiconducting layer 1100, metallic interface 1125, and carrier layer 1120"), FIG. 11.) Device 1401 also includes contact holes 1472, 1474, which have been drilled or etched into passivation layer material 1470, along with the carrier and GaN layers. (*Id.*, 7:19-21; *see also id.*, 6:14-21, FIG. 10.) The '822 patent states that "this exposes a first contact 1472 at metal pad 1430 and a second contact 1474 at carrier 1420." (*Id.*, 7:21-22; Ex. PA-DEC, ¶35.)

As explained below and in the accompanying declaration of Dr. Baker, all the limitations in the challenged claims were known in the prior art. (*See infra* Section VI; Ex. PA-DEC, ¶36.)

#### B. Prosecution History of the '822 patent

During prosecution, no prior art references were applied to the claims in any office action. (Ex. PAT-B, 11-18 (Notice of Allowance), 69-73 (Non-Final Office Action), 119-123 (Restriction

Requirement).) The claims, however, were amended in response to a written description rejection. (*Id.*, 61-64 (Applicant's Remarks), 69-73 (Non-Final Office Action).) Neither *Epler*, *Fan*, *Aldaz*, *Lester*, *Nagahama*, *Shimokawa*, *Han*, nor *Keller* were considered during prosecution of the '822 patent. (*See generally* Ex. PAT-B.)

#### C. The Effective Priority Date of the '822 Patent

For purposes of this reexamination only, Requester assumes that claims 1, 2, and 5-10 are entitled to the filing date of related provisional application Nos. 60/449,685 and 61/449,686, which is March 6, 2011. (Ex. PAT-A, 2.) *Epler, Fan, Nagahama, Han*, and *Keller* each issued more than one year prior to March 6, 2011, and thus qualify as prior art at least under pre-AIA 35 U.S.C. § 102(b); *Shimokawa*, which was filed on September 9, 2009, *Aldaz*, which was filed on April 23, 2010, and *Lester*, which was filed on June 11, 2007, qualify as prior art at least under pre-AIA 35 U.S.C. § 102(e).

#### V. Claim Construction

"During patent examination, the pending claims must be 'given their broadest reasonable interpretation consistent with the specification." MPEP § 2111; *see also* MPEP § 2258. Limitations in the specification are not read into the claims. MPEP § 2258. The standard of claim interpretation in reexamination is different than that used by the courts in patent litigation and the Board in *inter partes* review proceedings.<sup>2</sup> Therefore, any claim interpretations submitted or implied herein for the purpose of this reexamination do not necessarily correspond to the appropriate construction under the legal standards mandated in litigation. MPEP § 2686.04.11; *see also In re Zletz*, 893 F.2d 319, 322, 13 USPQ2d 1320, 1322 (Fed. Cir. 1989). For purposes of this request, Requester believes that no constructions of the challenged claims are needed.

In the Western District of Texas litigation involving the '822 patent (*see generally* Ex. LIT-1), Seoul Semiconductor proposed that an "electrical contact in electrical communication with said first surface of said semiconductor LED," as recited in claim 1 of the '822 patent, should be

<sup>&</sup>lt;sup>2</sup> Requester reserves all rights and defenses available including, without limitation, defenses as to invalidity, unenforceability, and non-infringement regarding the '822 patent. Further, because the claim interpretation standard used by courts in patent litigation is different from the appropriate standard for this reexamination, any claim constructions submitted or implied herein for the purpose of this reexamination are not binding upon Requester in any litigation related to the '822 patent. Specifically, any interpretation or construction of the claims presented herein or in Dr. Baker's declaration for reexamination, either implicitly or explicitly, should not be viewed as constituting, in whole or in part, the Requester's own interpretation or construction of such claims.

construed to mean an "electrical contact that is in a conduction path with the first surface of the semiconductor LED." (Ex. LIT-2, 5.) Patent Owner asserted that the limitation should be given its plain and ordinary meaning. (*Id.*) In addition, the Patent Owner and Requester also agreed that a "carrier layer," as recited in claim 1 of the '822 patent, should be given its plain and ordinary meaning. (*Id.*, 1.) No other other claim construction positions were offered for the '822 patent. (*Id.*, 1-5.)

While Requester believes no constructions are needed, the prior art mappings found in Section VI of this Request include analysis explaining how the claims of the '822 patent are unpatentable under the constructions advanced in the Western District of Texas litigation. Nonetheless, the claims would be unpatentable under any reasonable construction of the terms given how closely the prior art maps to the claims. This is particularly true given that the broadest reasonable interpretation standard governs this request.

#### VI. Statement of Substantial New Questions of Patentability

As mentioned above, *Epler, Fan, Aldaz, Lester, Nagahama, Shimokawa, Han*, and *Keller* were never made of record or considered by the Office during original prosecution of the '822 patent. However, the references (in various combinations for respective claims) disclose or suggest all of the features of claims 1, 2, and 5-10 of the '822 patent.

**<u>SNQ1</u>**: *Epler* raises a substantial new question of patentability (SNQ1) with respect to claims 1, 2, 5-7, and 9 of the '822 patent.

**<u>SNQ2</u>**: *Epler* and *Fan* raise a substantial new question of patentability (SNQ2) with respect to claim 8 of the '822 patent.

**<u>SNQ3</u>**: *Epler* and *Aldaz* raise a substantial new question of patentability (SNQ3) with respect to claim 10 of the '822 patent.

**<u>SNQ4</u>**: *Epler* and *Lester* raise a substantial new question of patentability (SNQ4) with respect to claims 1, 2, 5-7, and 9 of the '822 patent.

**<u>SNQ5</u>**: *Epler*, *Lester*, and *Fan* raise a substantial new question of patentability (SNQ5) with respect to claim 8 of the '822 patent.

**<u>SNQ6</u>**: *Epler*, *Lester*, and *Aldaz* raise a substantial new question of patentability (SNQ6) with respect to claim 10 of the '822 patent.

**<u>SNQ7</u>**: *Epler* and *Han* raise a substantial new question of patentability (SNQ7) with respect to claims 1, 2, 5-7, and 9 of the '822 patent.

**<u>SNQ8</u>**: *Epler*, *Han*, and *Fan* raise a substantial new question of patentability (SNQ8) with respect to claim 8 of the '822 patent.

**<u>SNQ9</u>**: *Epler*, *Han*, and *Aldaz* raise a substantial new question of patentability (SNQ9) with respect to claim 10 of the '822 patent.

**<u>SNQ10</u>**: *Epler*, *Han*, and *Lester* raise a substantial new question of patentability (SNQ10) with respect to claims 1, 2, 5-7, and 9 of the '822 patent.

**<u>SNQ11</u>**: *Epler*, *Han*, *Lester*, and *Fan* raise a substantial new question of patentability (SNQ11) with respect to claim 8 of the '822 patent.

**<u>SNQ12</u>**: *Epler*, *Han*, *Lester*, and *Aldaz* raise a substantial new question of patentability (SNQ12) with respect to claim 10 of the '822 patent.

**<u>SNQ13</u>**: *Epler* and *Nagahama* raise a substantial new question of patentability (SNQ13) with respect to claims 1, 2, 5-7, and 9 of the '822 patent.

<u>SNQ14</u>: *Epler*, *Nagahama*, and *Fan* raise a substantial new question of patentability (SNQ14) with respect to claim 8 of the '822 patent.

<u>SNQ15</u>: *Epler*, *Nagahama*, and *Aldaz* raise a substantial new question of patentability (SNQ15) with respect to claim 10 of the '822 patent.

**<u>SNQ16</u>**: *Epler*, *Nagahama*, and *Lester* raise a substantial new question of patentability (SNQ16) with respect to claims 1, 2, 5-7, and 9 of the '822 patent.

<u>SNQ17</u>: *Epler*, *Nagahama*, *Lester*, and *Fan* raise a substantial new question of patentability (SNQ17) with respect to claim 8 of the '822 patent.

**<u>SNQ18</u>**: *Epler*, *Nagahama*, *Lester*, and *Aldaz* raise a substantial new question of patentability (SNQ18) with respect to claim 10 of the '822 patent.

<u>SNQ19</u>: *Shimokawa* raises a substantial new question of patentability (SNQ19) with respect to claims 1, 2, and 5-10 of the '822 patent.

**<u>SNQ20</u>**: *Shimokawa* and *Aldaz* raise a substantial new question of patentability (SNQ20) with respect to claim 10 of the '822 patent.

**SNQ21**: *Shimokawa* and *Han* raise a substantial new question of patentability (SNQ21) with respect to claims 1, 2, and 5-10 of the '822 patent.

<u>SNQ22</u>: *Shimokawa*, *Han*, and *Aldaz* raise a substantial new question of patentability (SNQ22) with respect to claim 10 of the '822 patent.

<u>SNQ23</u>: *Shimokawa* and *Nagahama* raise a substantial new question of patentability (SNQ23) with respect to claims 1, 2, and 5-10 of the '822 patent.

<u>SNQ24</u>: *Shimokawa*, *Nagahama*, and *Aldaz* raise a substantial new question of patentability (SNQ24) with respect to claim 10 of the '822 patent.

<u>SNQ25</u>: *Shimokawa* and *Keller* raise a substantial new question of patentability (SNQ25) with respect to claims 1, 2, and 5-10 of the '822 patent.

<u>SNQ26</u>: *Shimokawa*, *Keller*, and *Aldaz* raise a substantial new question of patentability (SNQ26) with respect to claim 10 of the '822 patent.

<u>SNQ27</u>: *Shimokawa*, *Keller*, and *Han* raise a substantial new question of patentability (SNQ27) with respect to claims 1, 2, and 5-10 of the '822 patent.

<u>SNQ28</u>: *Shimokawa*, *Keller*, *Han*, and *Aldaz* raise a substantial new question of patentability (SNQ28) with respect to claim 10 of the '822 patent.

<u>SNQ29</u>: *Shimokawa*, *Keller*, and *Nagahama* raise a substantial new question of patentability (SNQ29) with respect to claims 1, 2, and 5-10 of the '822 patent.

<u>SNQ30</u>: *Shimokawa*, *Keller*, *Nagahama*, and *Aldaz* raise a substantial new question of patentability (SNQ30) with respect to claim 10 of the '822 patent.

Thus, for these reasons and the reasons discussed below and in the accompanying declaration of Dr. Baker (Ex. PA-DEC), *Epler* raises a substantial new question of patentability (SNQ1) with respect to claims 1, 2, 5-7, and 9 of the '822 patent; *Epler* and *Fan* raise a substantial new question of patentability (SNQ2) with respect to claim 8 of the '822 patent; *Epler* and *Aldaz* raise a substantial new question of patentability (SNQ3) with respect to claim 10 of the '822 patent; *Epler* and *Lester* raise a substantial new question of patentability (SNQ3) with respect to claim 10 of the '822 patent; *Epler* and *Lester* raise a substantial new question of patentability (SNQ4) with respect to claims 1, 2, 5-7, and 9 of the '822 patent; *Epler, Lester*, and *Fan* raise a substantial new question of patentability (SNQ6) with respect to claim 10 of the '822 patent; *Epler* and *Han* raise a substantial new question of patentability (SNQ6) with respect to claim 10 of the '822 patent; *Epler* and *Han* raise a substantial new question of patentability (SNQ6) with respect to claims 1, 2, 5-7, and 9 of the '822 patent; *Epler, Han*, and *Fan* raise a substantial new question of patentability (SNQ6) with respect to claims 1, 2, 5-7, and 9 of the '822 patent; *Epler, Han*, and *Fan* raise a substantial new question of patentability (SNQ8) with respect to claim 8 of the '822 patent; *Epler, Han*, and *Aldaz* raise a substantial new question of patentability (SNQ8) with respect to claim 8 of the '822 patent; *Epler, Han*, and *Aldaz* raise a substantial new question of patentability (SNQ9) with respect to claim 10 of the '822 patent; *Epler, Han*, and *Lester* raise a substantial new question of patentability (SNQ10) with respect to claims 1, 2, 5-7, and 9 of the '822 patent; *Epler, Han*, *Lester*, and *Fan* raise a substantial new question of patentability (SNQ10) with respect to claims 1, 2, 5-7, and 9 of the '822 patent; *Epler, Han*, *Lester*, and *Fan* raise a substantial new question of patentability (SNQ10) with

patentability (SNQ11) with respect to claim 8 of the '822 patent; Epler, Han, Lester, and Aldaz raise a substantial new question of patentability (SNQ12) with respect to claim 10 of the '822 patent; Epler and Nagahama raise a substantial new question of patentability (SNQ13) with respect to claims 1, 2, 5-7, and 9 of the '822 patent; Epler, Nagahama, and Fan raise a substantial new question of patentability (SNQ14) with respect to claim 8 of the '822 patent; Epler, Nagahama, and Aldaz raise a substantial new question of patentability (SNQ15) with respect to claim 10 of the '822 patent; Epler, Nagahama, and Lester raise a substantial new question of patentability (SNQ16) with respect to claims 1, 2, 5-7, and 9 of the '822 patent; Epler, Nagahama, Lester, and Fan raise a substantial new question of patentability (SNQ17) with respect to claim 8 of the '822 patent; Epler, Nagahama, Lester, and Aldaz raise a substantial new question of patentability (SNQ18) with respect to claim 10 of the '822 patent; Shimokawa raises a substantial new question of patentability (SNQ19) with respect to claims 1, 2, and 5-10 of the '822 patent; Shimokawa and Aldaz raise a substantial new question of patentability (SNQ20) with respect to claim 10 of the '822 patent; Shimokawa and Han raise a substantial new question of patentability (SNQ21) with respect to claims 1, 2, and 5-10 of the '822 patent; Shimokawa, Han, and Aldaz raise a substantial new question of patentability (SNQ22) with respect to claim 10 of the '822 patent; Shimokawa and Nagahama raise a substantial new question of patentability (SNQ23) with respect to claims 1, 2, and 5-10 of the '822 patent; Shimokawa, Nagahama, and Aldaz raise a substantial new question of patentability (SNQ24) with respect to claim 10 of the '822 patent; Shimokawa and Keller raise a substantial new question of patentability (SNQ25) with respect to claims 1, 2, and 5-10 of the '822 patent; Shimokawa, Keller, and Aldaz raise a substantial new question of patentability (SNQ26) with respect to claim 10 of the '822 patent; Shimokawa, Keller, and Han raise a substantial new question of patentability (SNQ27) with respect to claims 1, 2, and 5-10 of the '822 patent; Shimokawa, Keller, Han, and Aldaz raise a substantial new question of patentability (SNQ28) with respect to claim 10 of the '822 patent; Shimokawa, Keller, and Nagahama raise a substantial new question of patentability (SNQ29) with respect to claims 1, 2, and 5-10 of the '822 patent; Shimokawa, Keller, Nagahama, and Aldaz raise a substantial new question of patentability (SNQ30) with respect to claim 10 of the '822 patent.

#### A. SNQ1: *Epler* Discloses or Suggests Claims 1, 2, 5-7, and 9

As explained below and in the attached declaration of Dr. Baker (Ex. PA-DEC), *Epler* discloses or suggests the limitations of claims 1, 2, 5-7, and 9 of the '822 patent. (Ex. PA-DEC, ¶41.)

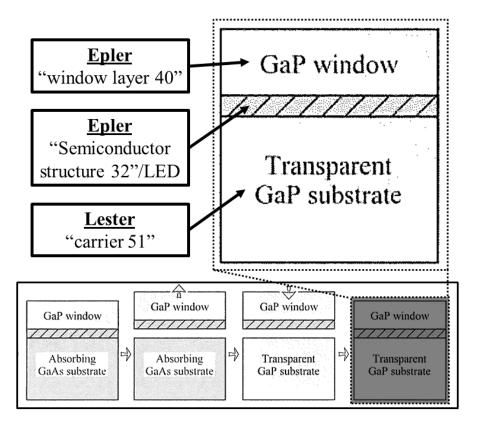

#### 1. Overview of *Epler*

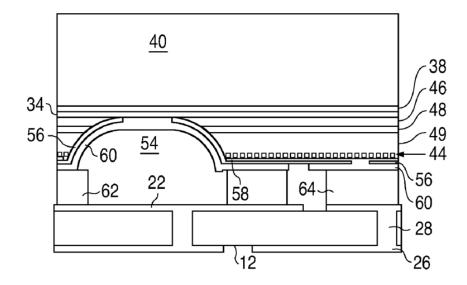

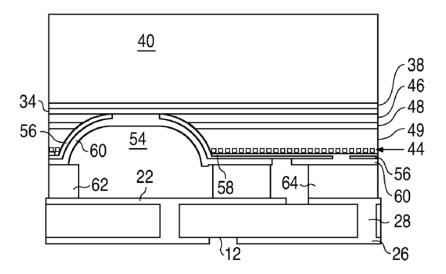

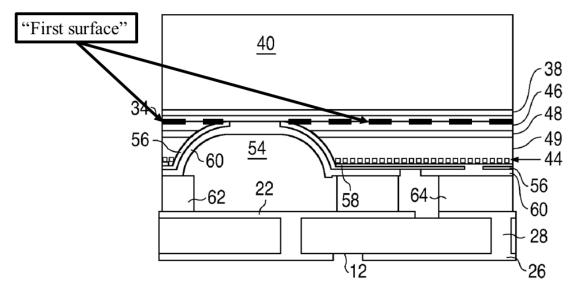

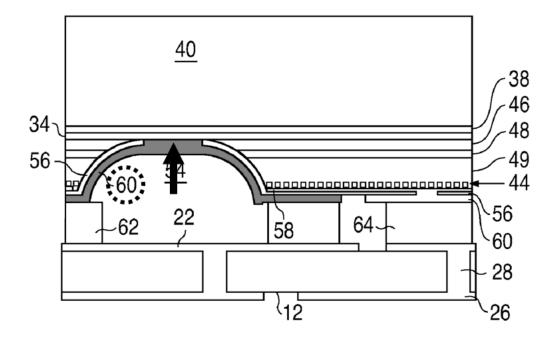

*Epler* relates to LED technologies and discloses a "semiconductor light emitting device." (Ex. PA-1, Abstract,  $\P\P[[0001]-[0002], [0034]-[0035], FIGs. 6-7.)$  The device includes a light emitting region and emits "rays of light." (*Id.*,  $\P\P[0030], [0034].$ ) An example semiconductor light emitting device is illustrated in Figure 6. (*Id.*,  $\P[0017].$ )

(*Id.*, FIG. 6.)

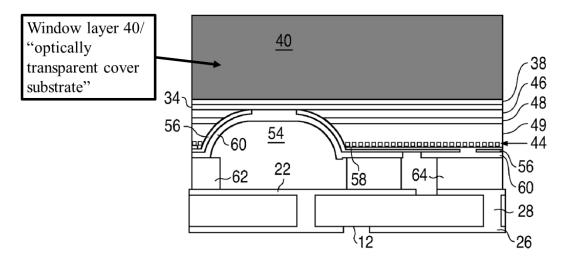

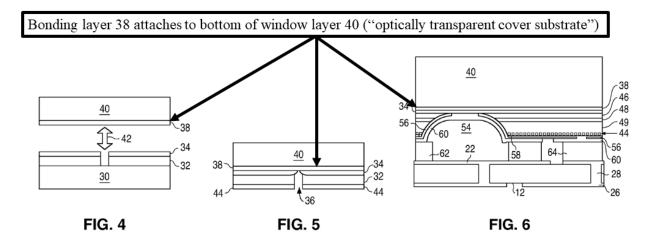

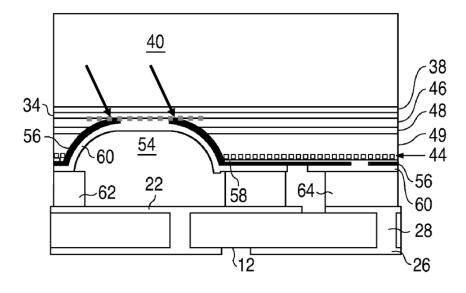

The top layers of the *Epler* semiconductor light emitting device affect light output. For instance, one or more phosphors may be disposed in semiconductor bonding material to shape the color of the emitted light. (*Id.*, ¶[0027], FIG. 6.) When the *Epler* semiconductor light emitting device includes bonding layers 34 and 38, bonding layer 38 may be formed on a window layer 40. (*Id.*, ¶[0027].) When the *Epler* semiconductor light emitting device does not include bonding layer 38, bonding layer 34 is attached to the bottom of the window layer as described with respect to layer 38. (*Id.*, ¶[0016], [0020], [0027], FIGs. 4-6.)

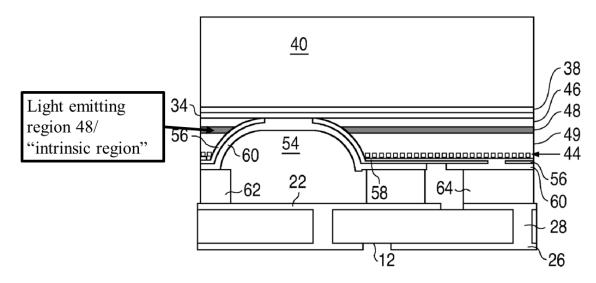

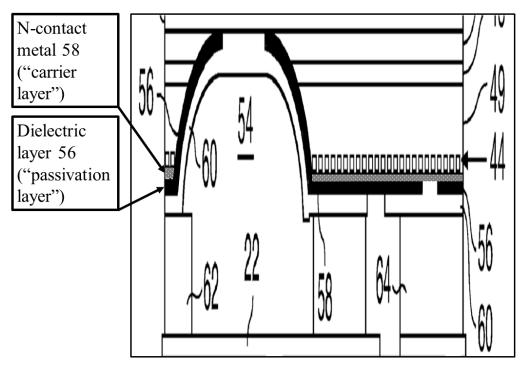

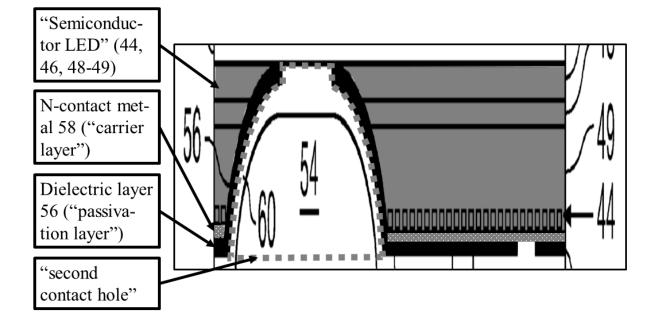

Beneath the top optical layers, *Epler* discloses an "n-type region 49," which includes a "porous region 44," a light emitting region 48" (an active region), and a "p-type region 46," which together comprise a semiconductor LED. (*Id.*, ¶¶[0001]-[0002], [0034], [0020], [0030], FIG. 6.) An n-contact metal 58 is formed on porous layer 44 of the n-type region 49 (porous layer 44 is a

pitted section of n-type region 49). (*Id.*, ¶¶[0032], [0034]-[0035], FIG. 6.) And a p-contact metal 60 is formed on an exposed portion of conductive bonding layer 34. (*Id.*, ¶¶[0032], [0034]-[0035], FIG. 6.) A dielectric layer 56 insulates portions of the n-contact metal 58 and p-contact metal 60. (*Id.*, ¶[0034], FIG. 6.)

*Epler* discloses that one or more openings are etched through layers of the *Epler* semiconductor light emitting device as a part of a contact formation process. (Ex. PA-1, ¶[0034], FIG. 6.) A first opening/hole through dielectric layer 56 allows p-contact metal 60 to make electrical contact with bonding layer 34 and form a p-type conductive path of the semiconductor device. (*Id.*, ¶¶[0034]-[0035], FIG. 6.) In a similar fashion, a second opening/hole through dielectric layer 56 allows n-contact metal 58 to make electrical contact and form an n-type conductive path of the semiconductor light emitting device. (*Id.*, ¶¶[0034]-[0035], FIG. 6.)

#### 2. Claim 1

#### a. A light emitting device, comprising:

To the extent the preamble is limiting, *Epler* discloses this limitation. (Ex. PA-DEC, ¶46.) For example, *Epler*, which relates to LED technologies (*e.g.*, Ex. PA-1, Abstract, FIGs. 1, 6, ¶¶[0001]-[0002]), discloses a "semiconductor light emitting device." (*Id.*, ¶¶[0034]-[0035], FIGs. 6-7.) The device includes a light emitting region and emits "rays of light." (*Id.*, ¶¶[0030], [0034].) An example semiconductor light emitting device is illustrated in Figure 6. (*Id.*, ¶[0017].)

(*Id.*, FIG. 6.) A similar device with a different mounting configuration is illustrated in Figure 7. (*Id.*, FIG. 7, ¶¶[0017]-[0018].)

#### b. an optically transparent cover substrate;

*Epler* discloses this limitation. (Ex. PA-DEC, ¶¶47-49.) For example, *Epler* discloses a "window layer 40" ("optically transparent cover substrate") that may be a "**transparent substrate**." (Ex. PA-1, ¶[0026] (emphasis added), FIG. 6.) Light is configured to pass through window layer 40 as an "optically transparent" material. (*Id.*, ¶[0027] ("For example, a red-emitting phosphor may be disposed in bonding layer 38, and a yellow- or green-emitting phosphor such as cerium-doped yttrium aluminum garnet may be disposed in or on window layer 40, such that the composite light emitted from the device appears warm white. Alternatively, a mixture of phosphors may be disposed in a silicone bonding layer 38, to provide the desired spectrum. In such devices, window layer 40 may be transparent."); Ex. PA-DEC, ¶47.)

Window layer 40 is bonded to the semiconductor light emitting device during manufacturing and is a cover that overlays the remaining components of the semiconductor light emitting device. (Ex. PA-1, FIGs. 4, 6, ¶¶[0017], [0026], [0034]; Ex. PA-DEC, ¶48.)

#### (Ex. PA-1, FIG. 6 (annotated); Ex. PA-DEC, ¶48.)

The transparent window layer 40 also provides mechanical support to the semiconductor light emitting device (Ex. PA-1, ¶¶[0026]-[0027], [0039] ("Since window layer 40 provides mechanical support to the semiconductor structure during and after removal of the growth substrate, a package substrate or other mount is not required.")), which is consistent with how the transparent cover substrate is described in the '822 patent (Ex. PAT-A, 5:20-25 ("The cover substrate 655 provides structural presence and mechanical coupling for elements of the LED

device 60. The cover substrate 655 is also transparent or optically permissive to light in the wavelength emitted by LED layer 600 and Phosphor layer.")).

#### c. an optically transparent layer attached to a bottom surface of said optically transparent cover substrate, said optically transparent layer including an optically definable material;

Epler discloses or suggests this limitation. (Ex. PA-DEC, ¶§50-56.)

Bonding layer 34 alone and in combination with bonding layer 38 each discloses "an optically transparent layer," as claimed. (Ex. PA-DEC, ¶51.) For example, *Epler* discloses a "bonding layer 34" ("optically transparent layer"). (Ex. PA-1, ¶[0024], FIG. 6.) Bonding layer 34 is formed of "transparent" material such that it has a "minimal[]" impact on the wavelength of the light that is emitted from the semiconductor light emitting device. (*Id.*) *Epler* discloses that "[s]uitable materials" for bonding layer 34 "include, for example, transparent conductive oxides such as indium tin oxide (ITO), zinc oxide, and ruthenium oxide." (*Id.*)

In addition, the material consisting of bonding layer 34 and 38 also comprise an "optically transparent layer," as claimed. (Ex. PA-DEC, ¶52.) For instance, *Epler* discloses that the bonding layer 38 "may be the same material as bonding layer 34" (Ex. PA-1, ¶[0027], FIG. 6), and is therefore optically transparent for the previously discussed reasons (*id.*, ¶[0024]). Furthermore, *Epler* discloses that a variety of suitable "transparent" materials can be used for bonding layer 38 and refers to 38 as a "transparent bonding layer 38." (*Id.*, ¶¶[0024], [0027].) *Epler* also discloses that bonding layers 34 and 38 are "bonded" together "for example by anodic bonding, direct bonding layer" and, accordingly, form a transparent layer of the semiconductor light emitting device. (*Id.*, ¶[0027-28], FIG. 6; Ex. PA-DEC, ¶52.) The material comprising 34 and 38 is a "layer" under the broadest reasonable interpretation. (Ex. PA-DEC, ¶52.) For example, a layer may include a thickness of material, and material that constitutes a "layer" does not become multiple layers simply because a manufacturer decided to deposit it in multiple steps rather than in a single step. (*Id.*)

*Epler* discloses that bonding layers 34 and 38 may be "attached to a bottom surface of said optically transparent cover substrate," as claimed. (Ex. PA-DEC, ¶53.) Bonding layer 38 is an optional material that can be included in the semiconductor light emitting device "[i]f conductive bonding layer 34 and window layer 40 are not suitable for bonding." (Ex. PA-1, ¶[0027]; Ex. PA-DEC, ¶53.) Indeed, *Epler* discloses that bonding layer 38 "may be the same material as bonding

layer 34," which also denotes that bonding layer 38 is an optional layer. (Ex. PA-1, ¶[0027]; Ex. PA-DEC, ¶53.) When the *Epler* semiconductor light emitting device includes bonding layers 34 and 38, bonding layer 38 may be "formed on window layer 40" ("optically transparent cover substrate") such that it is attached to a bottom surface of said optically transparent cover substrate. (Ex. PA-1, ¶[0027].) Figures 4-6 illustrate the fabrication of a "bonded structure," wherein bonding layer 38 of the semiconductor light emitting device attaches to the bottom of window layer 40 ("optically transparent cover substrate"). (Ex. PA-1, ¶[0016], [0020], FIGs. 4-6; Ex. PA-DEC, ¶53.)

#### (Ex. PA-1, FIGs. 4-6 (annotated); Ex. PA-DEC, ¶53.)

When the *Epler* semiconductor light emitting device does not include bonding layer 38, bonding layer 34, which may be the same material as bonding layer 38, would be attached to the bottom of the window layer 40 as described with respect to layer 38. (Ex. PA-1, ¶¶[0016], [0020], [0027], FIGs. 4-6; Ex. PA-DEC, ¶54.)

*Epler* discloses that the bonding layer 38 material may "includ[e] an optically definable material," as claimed, at least because the bonding material may include one or more phosphors to help shape the color of emitted light. (Ex. PA-1, ¶[0027], FIG. 6; Ex. PA-DEC, ¶55.) "For example, a red-emitting phosphor may be disposed in bonding layer 38" to allow the light emitted from the device to appear warm white. (Ex. PA-1, ¶[0027], FIG. 6; Ex. PA-DEC, ¶55.) "Alternatively, a mixture of phosphors may be disposed in a silicone bonding layer 38, to provide [a] desired spectrum." (Ex. PA-1, ¶[0027], FIG. 6; Ex. PA-DEC, ¶55.) This disclosure is

consistent with the '822 patent, which also discloses a similar phosphor-based configuration. (Ex. PAT-A, 5:9-16.)

Additionally, because *Epler* discloses that bonding layer 34 and bonding layer 38 can be the same material, *Epler* discloses that layer 34 may also include one or more phosphors ("optically definable material"). (Ex. PA-1, ¶[0027].) To the extent *Epler* does not explicitly disclose that bonding layer 34 may include such a phosphor, the configuration would have been obvious. (Ex. PA-DEC, ¶56.) Adding a phosphor to bonding layer 34 would have yielded similar lighting benefits to those described with respect to bonding layer 38 and could have easily been manufactured by a POSITA in a similar way. (*Id.*, ¶[0027]; Ex. PA-DEC, ¶56.) *See KSR Intern. Co. v. Teleflex Inc.*, 550 U.S. 398, 416-17 (2007).

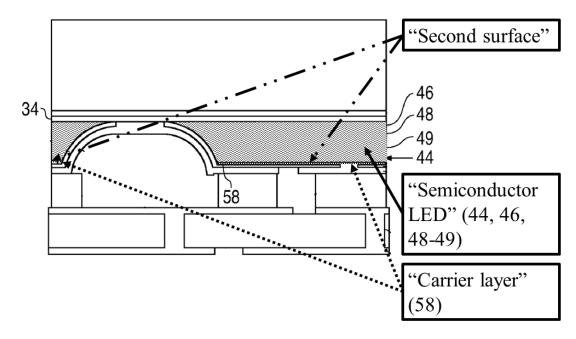

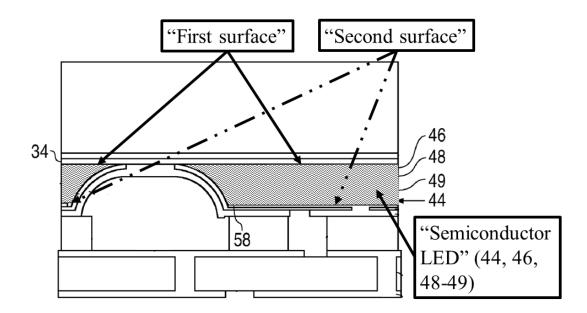

d. a semiconductor LED including a positively-doped region, an intrinsic region, and a negatively-doped region, wherein said intrinsic region is between said positively-doped region and said negatively-doped region, and a first surface of said semiconductor LED contacts a first portion of a bottom surface of said optically transparent layer;

Epler discloses this limitation. (Ex. PA-DEC, ¶¶57-60.) Epler discloses "a semiconductor LED including a positively-doped region, an intrinsic region, and a negatively-doped region," as claimed. (Ex. PA-DEC, ¶57.) For instance, Epler discloses an "n-type region 49," which includes a "porous region 44," a "light emitting region 48" (an active region), and a "p-type region 46," which together comprise a semiconductor LED. (Ex. PA-1, ¶¶[0034], [0020], [0030]; Ex. PA-DEC, ¶57; see generally Ex. PA-1, ¶¶[0001]-[0002] (describing a semiconductor LED as including an n-type layer, an active layer, a p-type layer).) A person of ordinary skill in the art ("POSITA") would have understood that p-type region 46 refers to a positively doped semiconductor material ("positively-doped region") and that n-type region refers to a negatively doped semiconductor material ("negatively-doped region"). (Ex. PA-1, ¶¶[0021]-[0023], [0032]; Ex. PA-4, 1:61-65 ("electron 'holes' become the charge carriers and the doped silicon is referred to as positive or Ptype silicon . . . additional electrons become the charge carriers and the doped silicon is referred to as negative or N-type silicon"); Ex. PA-5, ¶¶[0003]-[0005]; Ex. PA-DEC, ¶57.) Epler discloses that light emitting/active region 48 "may be doped . . . [or] not intentionally doped" and so does not include the n-type or p-type doping of layers 46 and 49. (Ex. PA-1, ¶¶[0022] (emphasis added), [0034]; Ex. PA-DEC, ¶57.) Indeed, Epler explains that a "not intentionally doped" region refers to region with a "dopant concentration [of] zero" (i.e., the region is not doped at all). (Ex. PA-1,

¶[0032].) Because *Epler* discloses that light emitting/active region 48 may not be doped, such that it has a dopant concentration of zero, light emitting/active region 48 discloses an "intrinsic region" under the broadest reasonable interpretation. (Ex. PA-DEC, ¶57.)

*Epler* discloses that "wherein said intrinsic region is between said positively-doped region and said negatively-doped region," as claimed. (Ex. PA-DEC, ¶58.) For instance, *Epler* discloses that "[t]he light emitting region is grown over the n-type region" and that "the p-type region is grown over the light emitting region." (Ex. PA-1, ¶¶[0023], [0034]; Ex. PA-DEC, ¶58.) Figure 6 illustrates this configuration, wherein the light emitting region 48 is sandwiched between the ptype region 46 and n-type region 49:

(Ex. PA-1, FIG. 6 (annotated); Ex. PA-DEC, ¶58).

*Epler* discloses that "a first surface of said semiconductor LED contacts a first portion of a bottom surface of said optically transparent layer," as claimed. (Ex. PA-DEC, ¶59.) For instance, referring to the fabrication process depicted in Figures 2-5, *Epler* discloses that "bonding layer 34 is formed over the top layer of semiconductor structure 32, generally the p-type region, using a conventional thin-film deposition technique such as vacuum evaporation, sputtering, and electron beam deposition." (Ex. PA-1, ¶[0024].) Additionally, the bottom of 34 and top of p-type region 46 (which is part of semiconductor structure 32 in Figures 2-5) are in contact such that "[c]onductive bonding layer 34 serves as the electrical contact to the p-type region." (*Id.*, ¶[0034].) Figure 6 also illustrates how a first surface of p-type region 46 of the semiconductor LED contacts the bottom of 34:

#### (Ex. PA-1, FIG. 6 (annotated); Ex. PA-DEC, ¶59).

Bonding layer 34 would similarly contact the first surface of p-type region 46 in the embodiment wherein the semiconductor light emitting device does not include optional bonding layer 38. (Ex. PA-1, ¶[0024], [0027], [0034], FIG. 6; Ex. PA-DEC, ¶60.)

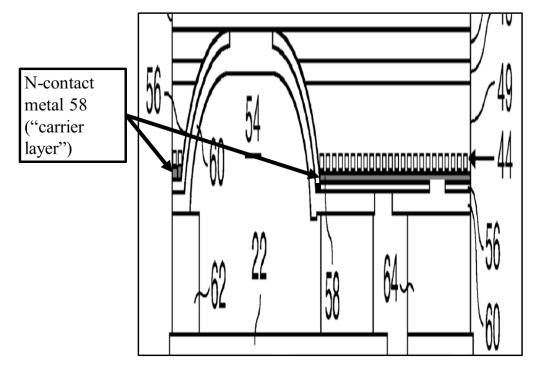

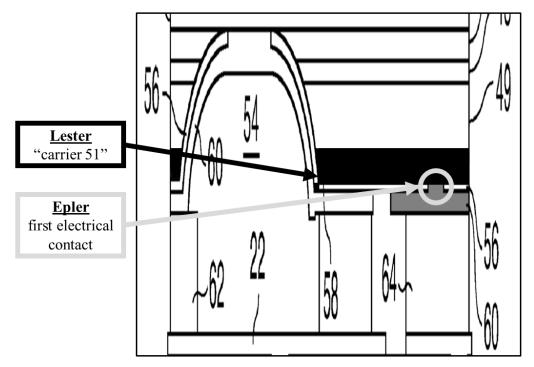

#### e. a carrier layer proximal to a second surface of said semiconductor LED, said first and second surfaces on opposing sides of said semiconductor LED;

*Epler* discloses this limitation, based at least on the broadest reasonable interpretation of the term "carrier layer." (Ex. PA-DEC, ¶¶61-63.) For example, *Epler* describes an "[n]-contact metal 58" formed on a porous layer 44 of the n-type region 49 (porous layer 44 is a pitted section of n-type region 49). (Ex. PA-1, ¶¶[0034]-[0035], [0032], FIG. 6; Ex. PA-DEC, ¶61.) N-contact metal 58 is configured to conduct electricity. (Ex. PA-1, ¶¶[0011], [0034]-[0035], FIGs. 6-7; Ex. PA-DEC, ¶61.) The N-contact metal 58 meets the term "carrier layer" under the broadest reasonable interpretation, at least because it supports the base of the semiconductor LED (i.e., layers 44, 46, 48, and 49). (Ex. PA-1, ¶¶[0011], [0034]-[0035], FIGs. 6-7; Ex. PA-DEC, ¶61.) In fact, Patent Owner has applied the "carrier layer" term broadly in district court, as evidenced by Patent Owner's infringement allegations, which allege that even a thin metal interconnect layer corresponds to the claimed "carrier layer." (Ex. LIT-3, 11-12 (asserting that a copper interconnect layer is a carrier layer); Ex. PA-DEC, ¶61.) *See Amazon.com, Inc. v. Barnesandnoble.com, Inc.*, 239 F.3d 1343, 1351 (Fed. Cir. 2001) (citation omitted) ("A patent may not, like a 'nose of wax,' be twisted one way to avoid anticipation and another to find infringement."). Thus, the annotated

portion of Figure 6 below, which corresponds to n-contact metal 58, discloses the claimed "carrier layer," based on Patent Owner's infringement allegations. (Ex. PA-DEC, ¶61.)

(Ex. PA-1, ¶[0034], FIG. 6 (excerpted, enlarged, and annotated); Ex. PA-DEC, ¶61.)

As illustrated below, the n-contact metal 58 illustrated above ("carrier layer") is "proximal to a second surface of said semiconductor LED," as claimed. (Ex. PA-DEC, ¶62.) For instance, *Epler* discloses that "[n]-contact metal 58 is **formed on the remaining part of porous region 44**" of the semiconductor LED after an opening is etched through layers 44, 46, 48, and 49 to expose bonding layer 34. (Ex. PA-1, ¶[0034] (emphasis added), FIGs. 6-7; Ex. PA-DEC, ¶62.) Layering 58 on the remaining part of 44 (which includes the bottom of the "semiconductor LED" (*see supra* §VI.A.2.d)) layers 58 "proximal to a second surface of said semiconductor LED," as claimed:

(Ex. PA-1, FIG. 6 (annotated), ¶[0034]; Ex. PA-DEC, ¶62).

As illustrated in Figure 6 and described, the top of the p-type region 46 ("first surface") of the semiconductor LED and the bottom of the porous region 44 ("second surface") of the semiconductor LED are on "opposing sides," as claimed:

(Ex. PA-1, ¶[0034], FIG. 6 (annotated); Ex. PA-DEC, ¶63).

# f. a passivation layer disposed on said carrier layer and on an exposed portion of said bottom surface of said optically transparent layer;

*Epler* discloses this limitation. (Ex. PA-DEC, ¶¶64-65.) For instance, *Epler* discloses "dielectric layer 56" ("passivation layer"). (Ex. PA-1, ¶[0034]; Ex. PA-DEC, ¶64.) Dielectric layer 56 "electrically isolate[s]" n-contact metal 58 ("carrier layer") to ensure that the recombination of electrical carriers occurs in the radiative region, and, as shown in Figure 6, is "disposed on" the portion of n-contact metal 58 discussed above in Section VI.A.2.e ("said carrier layer"):

(Ex. PA-1, ¶[0034], FIG. 6 (excerpted, enlarged, and annotated); Ex. PA-DEC, ¶64.) Indeed, *Epler* explains that the dielectric layer 56 may be composed of a " $SiN_x$ " material, consistent with the '822 patent. (Ex. PA-1, ¶¶[0034], [0039]; Ex. PAT-A, ("The passivation layer 1170 can comprise a non conductive layer and can be composed of . . . SiN.").) Additionally, given *Epler*'s explanation that n-contact metal 58 "is formed on" porous region 44, and the fact that dielectric layer 56 is illustrated proximate to n-contact metal 58 in Figure 6, a POSITA would have understood that dielectric layer 56 is formed on ("disposed on") the portion of n-contact metal 58 discussed above in Section VI.A.2.e ("carrier layer") after that portion of n-contact metal 58 is formed on region 44. (Ex. PA-1, ¶[0034], FIG. 6; Ex. PA-DEC, ¶64.)

*Epler* further discloses that the dielectric layer 56 ("passivation layer") is "on an exposed portion of said bottom surface of said optically transparent layer," as claimed. (Ex. PA-DEC, ¶65.) For instance, *Epler* discloses that "one or more openings which expose bonding layer 34 are etched through the semiconductor structure." (Ex. PA-1, ¶¶[0034].) After the bottom of bonding layer 34 is exposed, "contacts are formed." (*Id.*) As a part of the contact formation process and illustrated by the below dotted line, dielectric layer 56 is layered on a portion of the exposed bottom of bonding layer 34:

(Ex. PA-1, ¶[0034], FIG. 6 (annotated); Ex. PA-DEC, ¶65). Thus, dielectric layer 56 ("passivation layer") is "on an exposed portion of said bottom surface of" bonding layer 34 and accordingly on the bottom of the "optically transparent layer." (Ex. PA-1, ¶[0034], FIGs. 6-7; Ex. PA-DEC, ¶65.)

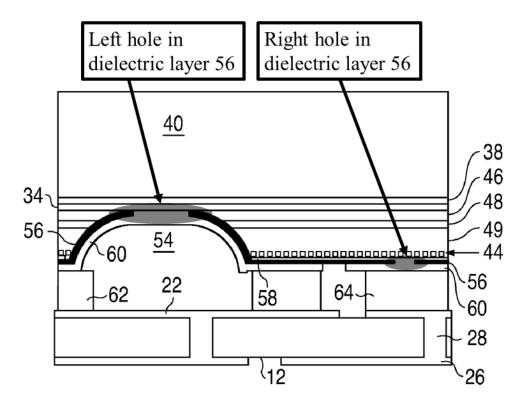

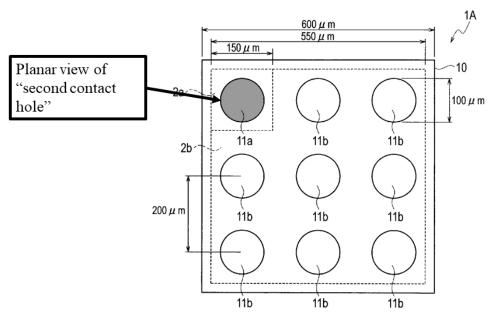

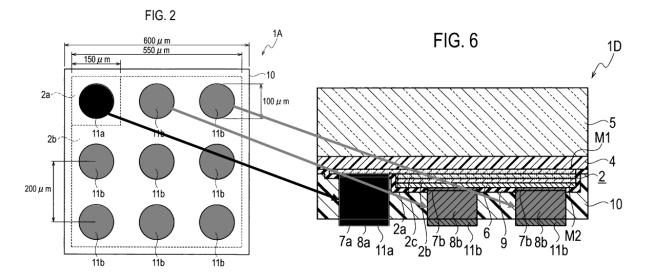

# g. a first electrical contact disposed on said carrier layer in a first contact hole defined in said passivation layer; and

*Epler* discloses this limitation. (Ex. PA-DEC, ¶¶66-70.) For instance, *Epler* discloses "a first contact hole defined in said passivation layer," as claimed. (*Id.*, ¶66.) As shown in annotated Figure 6 below, dielectric layer 56 ("passivation layer") does not cover the entire length of the semiconductor light emitting device. (Ex. PA-1, ¶¶[0034]-[0035], FIG. 6; Ex. PA-DEC, ¶66.) Rather, dielectric layer 56 includes two openings, a left opening and a right opening ("hole defined in said passivation layer"):

(Ex. PA-1, ¶¶[0034]-[0035], FIG. 6; Ex. PA-DEC, ¶66.)

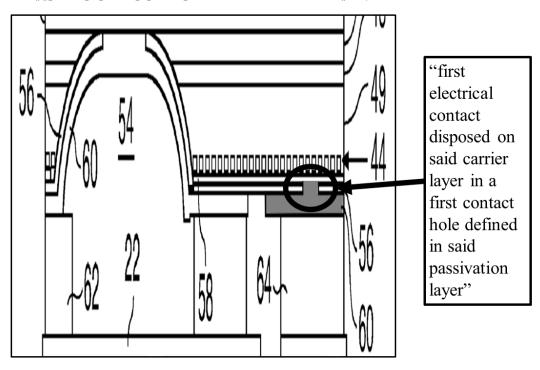

A "first electrical contact," as claimed, is formed in the right hole in dielectric layer 56 ("passivation layer"). (Ex. PA-1, ¶¶[0034]-[0035], FIG. 6; Ex. PA-DEC, ¶67.) As disclosed by *Epler* and further explained in the following paragraphs, after creation of the hole on the right-hand side of the dielectric layer 56, an additional portion of n-contact metal 58 illustrated in annotated Figure 6 below is formed such that an electrical contact ("first electrical contact") is formed in the hole with the portion of n-contact metal 58 discussed above in Section VI.A.2.e ("carrier layer"). <sup>3</sup> (Ex. PA-1, ¶¶[0030], [0034]-[0035], FIG. 6; Ex. PA-DEC, ¶67.) Thus, a

<sup>&</sup>lt;sup>3</sup> In addition to label 58, Figure 6 includes a label 60 for the same n-contact metal region. Based on *Epler*'s disclosure, a POSITA would have understood that this inclusion of label 60 is a typographical error. (Ex. PA-DEC, ¶67.) For example, in the specification, 60 refers to a "pcontact metal," which a POSITA would have understood corresponds to the p-contact region on the left side of the device illustrated in Figure 6, not the n-contact region on the right side of the device illustrated in Figure 6. (Ex. PA-1, ¶¶[0034]-[0035], [0020]-[0023], FIG. 6; Ex. PA-DEC, ¶67.) In fact, Figure 6 already includes a separate label 60 for the p-contact metal on the left side of the device illustrated in Figure 6. (Ex. PA-1, FIG. 6.) Additionally, Figure 7, which illustrates a device that is similar to the device in Figure 6 except without a package substrate, does not include label 60 for the n-contact metal region that is also identified by label 58. (Ex. PA-1,

conductive path to the n-type region 49 is formed via an n-path top-side contact 22 (which is not labeled in the below figure), bottom-side contact 26, conductive pillar 28, and n-interconnect 64. (Ex. PA-1, ¶¶[0030], [0034]-[0035], FIG. 6; Ex. PA-DEC, ¶67.)

(Ex. PA-1, ¶¶[0034]-[0035], FIG. 6 (excerpted, enlarged, and annotated) (illustrating a "first electrical contact" formed in the right hole in dielectric layer 56 ("passivation layer")); Ex. PA-DEC, ¶67.)

A POSITA would have understood that the two portions of n-contact metal 58 are formed by first forming the portion of n-contact metal 58 discussed above in Section VI.A.2.e (the claimed "carrier layer"), then forming passivation layer 56 and the contact holes in passivation layer 56, and finally forming the portion of n-contact metal 58 discussed above in this Section. (Ex. PA-DEC,  $\P68$ .) This is the case because each portion of n-contact metal 58 and dielectric layer 56 must be formed in sequence, consistent with known semiconductor fabrication techniques available at the time. (*Id.*; *see generally* Ex. PA-27, FIG. 3,  $\P[0047]$  (explaining that after an nelectrode is formed "a transparent, nonconductive passivation layer 47 is formed . . . to protect the light emitting diode chip" and that thereafter "portions of the passivation layer are punched so as

<sup>[0039]</sup>, FIG. 7; Ex. PA-DEC, [67.) Thus, a POSITA would have understood that label 58 also refers to the right n-contact metal region erroneously marked as 60 on the right side of the device illustrated in Figure 6. (Ex. PA-DEC, [67.)

to expose" the n-electrode in operation 305); Ex. PA-28, ¶[0037] (explaining that LED manufacturing "includes depositing a dielectric layer 32 in which vias 34 are formed to provide access to the . . . the n-type electrode 14, followed by metallization processing that fills the vias 34 with an electrically conductive material 36 and that forms intermediate connecting pads, specifically . . . an intermediate n-type connecting pad 44"); Ex. PA-29, ¶[0056] ("forming an insulation layer on the substrate having the n-type electrodes 64 and the p-type electrode pads 66 as shown in FIG. 7. Thereafter, the insulation layer is patterned through a photolithography and etching process to form openings exposing the n-type electrodes 64 and the p-type electrode pads 66. Subsequently, through an e-beam evaporation technology, the openings are filled and the metal layer covering the top surface of the insulation layer is formed.").

Alternatively, this limitation would have been obvious, because a POSITA would have had good reason to form two portions of n-contact metal 58 by, first, forming the portion of n-contact metal 58 discussed above in Section VI.A.2.e (the claimed "carrier layer"), second, forming passivation layer 56, third, forming contact holes in passivation layer 56, and, finally, forming the portion of n-contact metal 58, including within the right hole in the passivation layer 56, to form the claimed "first electrical contact." (Ex. PA-DEC, ¶69.) N- and p-region connections were routinely formed by first depositing metals on n- and p-type materials, and thereafter layering additional metal on the deposited metal through an insulation, via/etching, etc., process. (Id.; see generally Ex. PA-27, FIG. 3, ¶[0047] (explaining that after an n-electrode is formed "a transparent, nonconductive passivation layer 47 is formed . . . to protect the light emitting diode chip" and that thereafter "portions of the passivation layer are punched so as to expose" the n-electrode in operation 305); Ex. PA-28, ¶[0037] (explaining that LED manufacturing "includes depositing a dielectric layer 32 in which vias 34 are formed to provide access to the ... the n-type electrode 14, followed by metallization processing that fills the vias 34 with an electrically conductive material 36 and that forms intermediate connecting pads, specifically ... an intermediate n-type connecting pad 44"); Ex. PA-29, ¶[0056] ("forming an insulation layer on the substrate having the n-type electrodes 64 and the p-type electrode pads 66 as shown in FIG. 7. Thereafter, the insulation layer is patterned through a photolithography and etching process to form openings exposing the n-type electrodes 64 and the p-type electrode pads 66. Subsequently, through an e-beam evaporation technology, the openings are filled and the metal layer covering the top surface of the insulation layer is formed."); Ex. PA-11, ¶[0036]; Ex. PA-37, ¶¶[0049]-[0050].). A POSITA would have

had good reason to manufacture the n-contact metal 58 in this fashion, including to reduce costs by using established and widely-available methods to manufacture such devices; to simply manufacturing by using established and reliable methods to manufacture such devices; to electrically isolate the p- and n-contacts; and to improve the thermal performance of the device and yield. (Ex. PA-DEC, ¶69; Ex. Pa-11, ¶¶[0011], [0037]; Ex. PA-27, ¶[0020] Ex. PA-28, ¶[0037]; Ex. PA-29, ¶[0056].)

Because *Epler* teaches or suggests that the disclosed "first electrical contact" is formed on the portion of n-contact metal 58 discussed above in Section VI.A.2.e ("carrier layer") inside the hole in dielectric layer 56 ("passivation layer") *Epler* discloses or renders obvious that the "first electrical contact" is "disposed on said carrier layer in a first contact hole defined in said passivation layer," as claimed. (Ex. PA-DEC, ¶70.) Indeed, *Epler* discloses that the left opening/hole allows the left p-contact metal 60 to make electrical contact with bonding layer 34 and form a p-type conductive path of the semiconductor device. (Ex. PA-1, ¶¶[0034]-[0035], FIG. 6; Ex. PA-DEC, ¶70.) In a similar fashion, *Epler* discloses that the right hole allows the n-contact metal 58 to form the n-type conductive path of the semiconductor light emitting device. (Ex. PA-1, ¶¶[0034]-[0035], FIG. 6; Ex. PA-DEC, ¶70.) This disclosure is consistent with the '822 patent, which describes a similar contact 1472 in Figure 14. (Ex. PAT-A, 7:16-22, FIG. 14; Ex. PA-DEC, ¶70.)

> h. a second electrical contact disposed in a second contact hole defined in said passivation layer, said carrier layer, and said semiconductor LED, said second electrical contact in electrical communication with said first surface of said semiconductor LED.

*Epler* discloses this limitation. (Ex. PA-DEC, ¶¶71-73.) For instance, *Epler* discloses "pcontact metal 60" forming a contact with bonding layer 34 ("second electrical contact") in opening 54 ("second contact hole"). (Ex. PA-1, ¶¶[0034]-[0035], FIG. 6; Ex. PA-DEC, ¶71.) P-contact metal 60 makes electrical contact with p-interconnects 62 and bonding layer 34 to form a conductive path to the p-type region 46 via top-side contact 22, a p-path bottom-side contact 26 (which is not labeled in the below figure), and a p-path conductive pillar 28 (which is not labeled in the below figure). (Ex. PA-1, ¶¶[0024], [0030], [0034]-[0035], FIG. 6; Ex. PA-DEC, ¶71.)

(Ex. PA-1, ¶¶[0034]-[0035], FIG. 6 (annotated) (illustrating a p-type electrical contact); Ex. PA-DEC, ¶71.)