Lab 1 - ECE 421L

Authored by

Prelab

First of all, getting the username and password from Dr. Baker is important to get access into our ftp.cmosedu.com. After that, following the 1st tutorial for html is a good resource to start getting more experience.

Lab Work

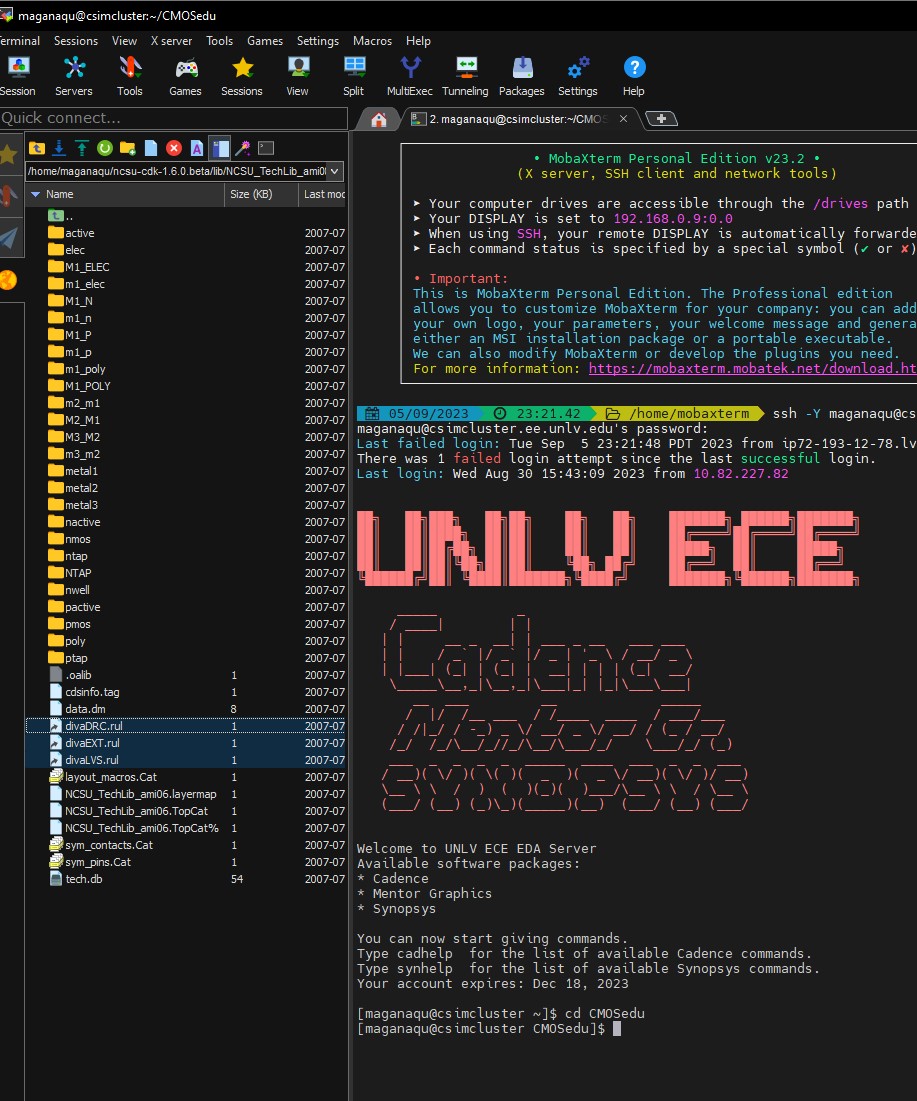

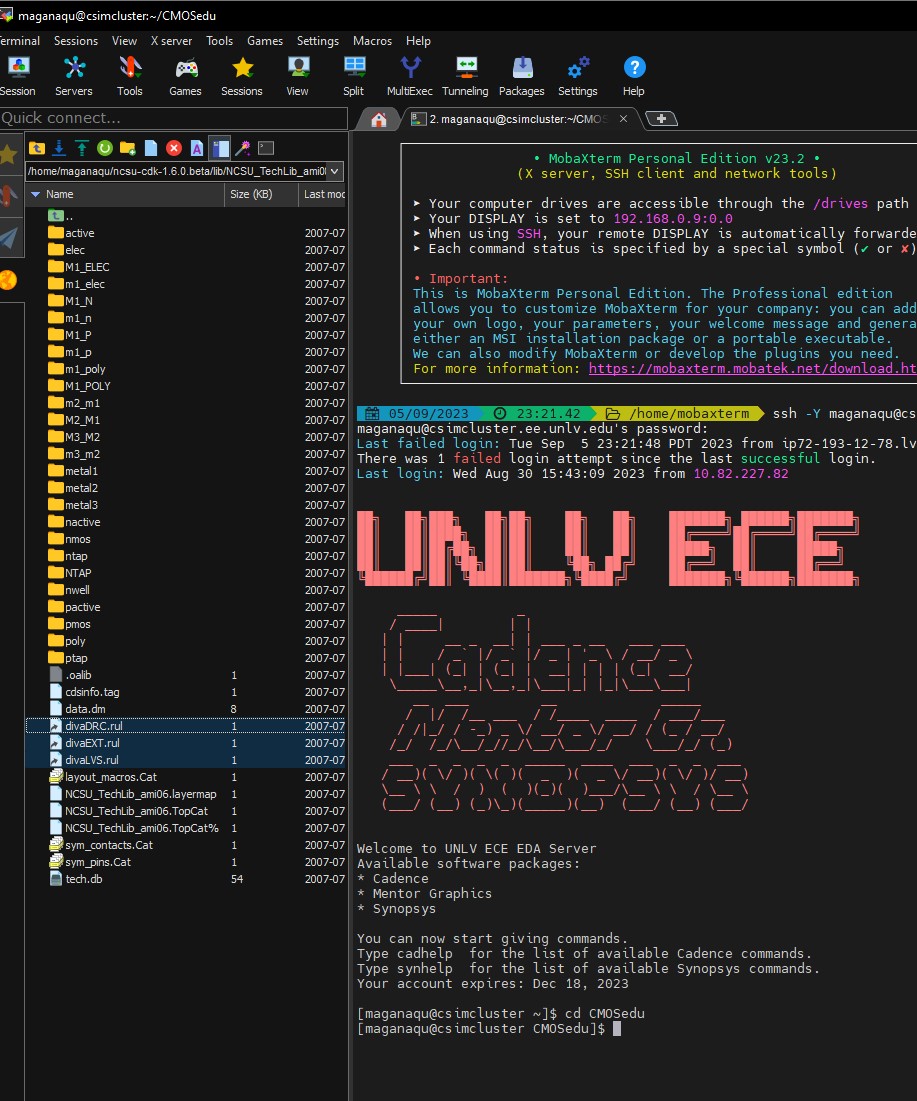

To begin with, keep in mind to follow our Tutorial 1 here so we remove our files (divaDRC.rul, divaEXT.rul, and divaLVS.rul) located on $HOME/ncsu-cdk-1.6.0.beta/lib/NCSU_TechLib_ami06. And download, unzip our new diva rul files, so we can add them in the spots where we deleted the old ones, as shown in the next picture.

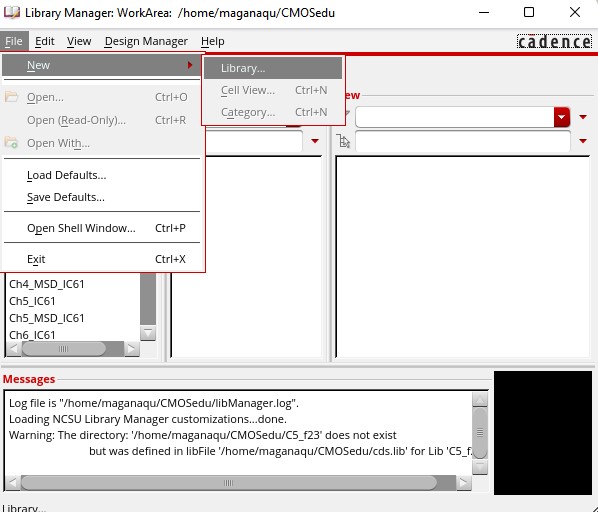

After getting access to Virtuoso,we will be able to see our library manager. This will be useful to create a new library called Tutorial_1.

Do not forget to have the next set up before pressing OK

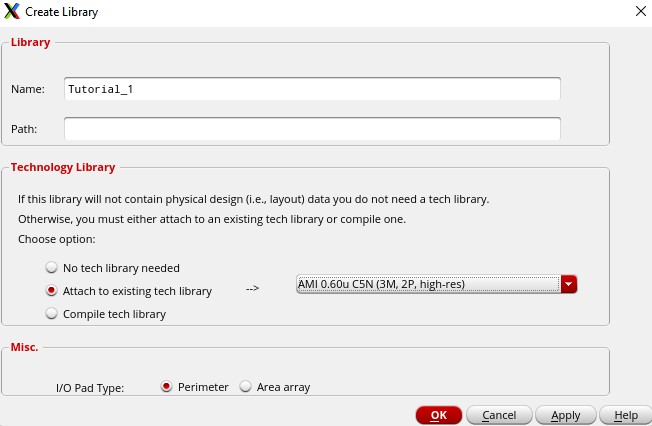

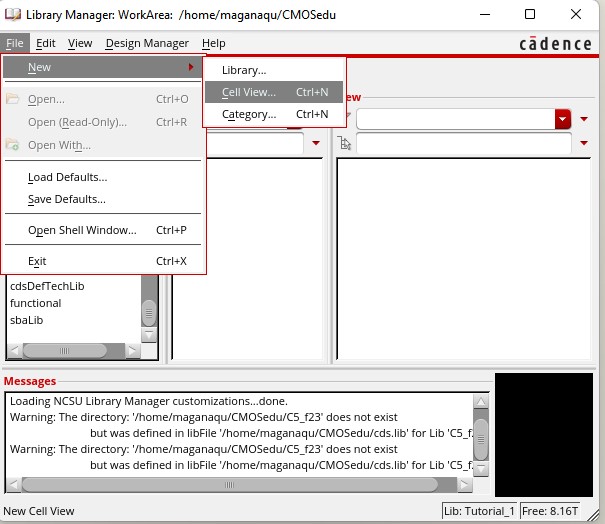

To edit our new library, we can follow the next path: FILE / NEW / CELL VIEW as shown in the picture

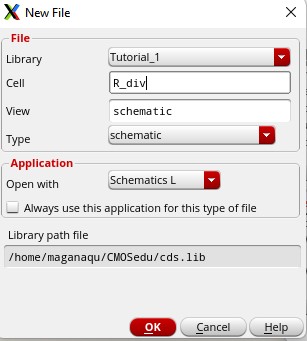

And then we add our cell as R_div

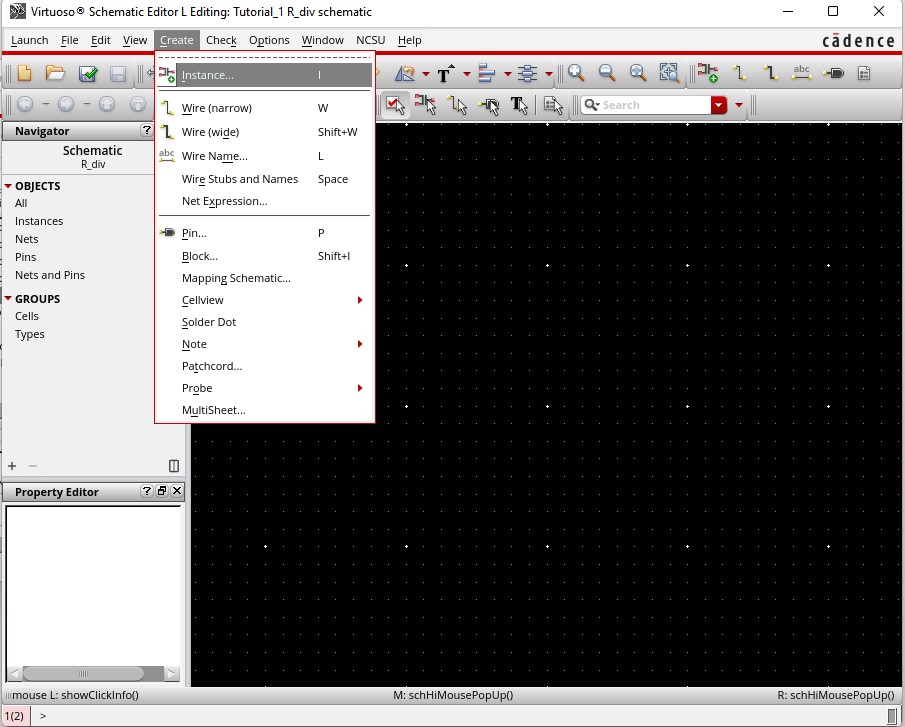

Once we are done, this new screen will show up, at this point we can go on the long way which is Create / Instance. Or simply the shortcut, press I

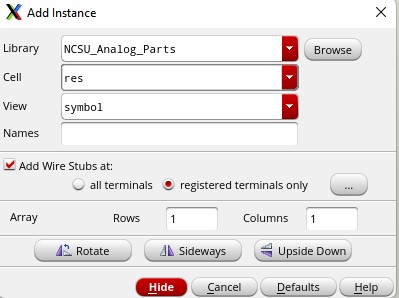

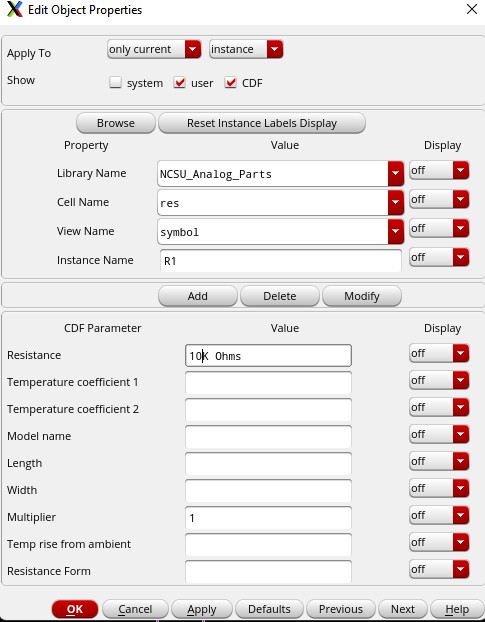

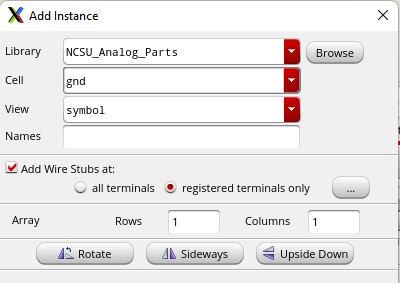

we will add our resistors by selecting this configuration:

Follow the same path for other compenents like Ground gnd, or our Power Supppy in DC vdc

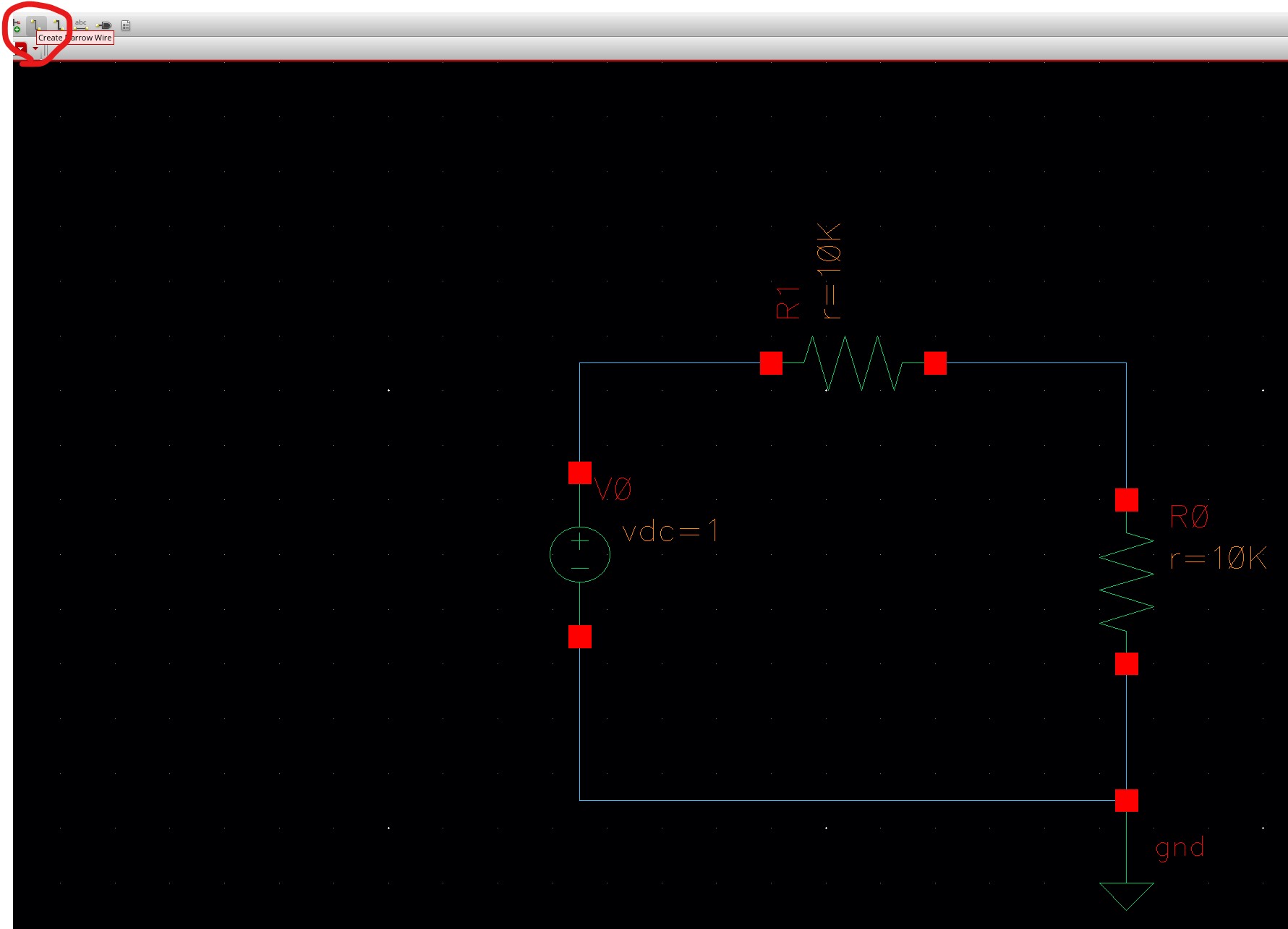

At the end, you can just press Create Narrow Wire to connect our components from the circuit

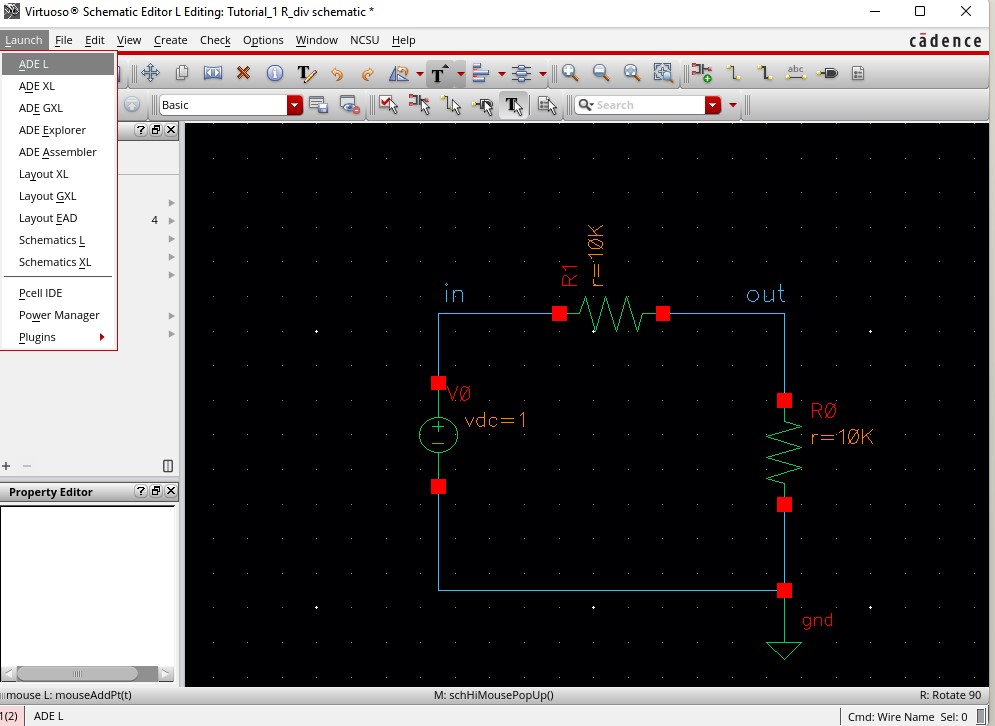

We will select Check and Save on the right corner and then we can go to Launch and ADE L to start the simulation of our circuit design.

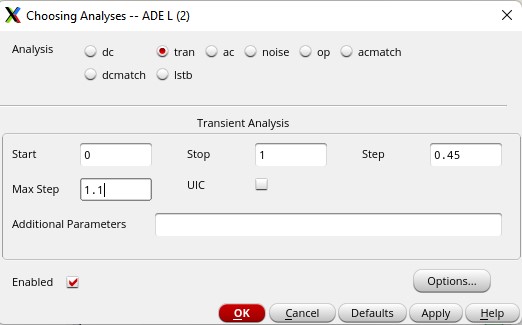

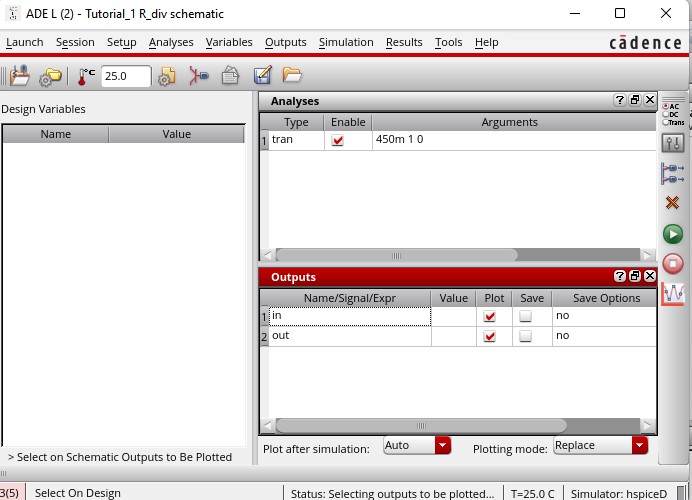

Go to Analyses / Choose... and have this set up:

Also go to Outputs, select TO BE PLOTTED and then from the circuit design, select IN and OUT.

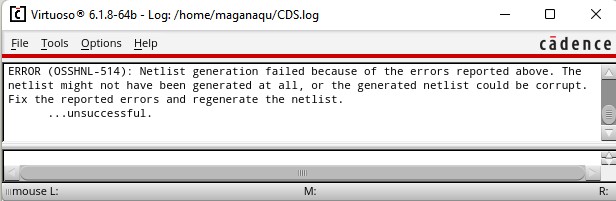

unfortunately did not work ;c