Lab 5 - EE 421L

Pre Lab

For the pre lab, we are asked to go through Tutorial 3 which covers how to layout and simulate an inverter.

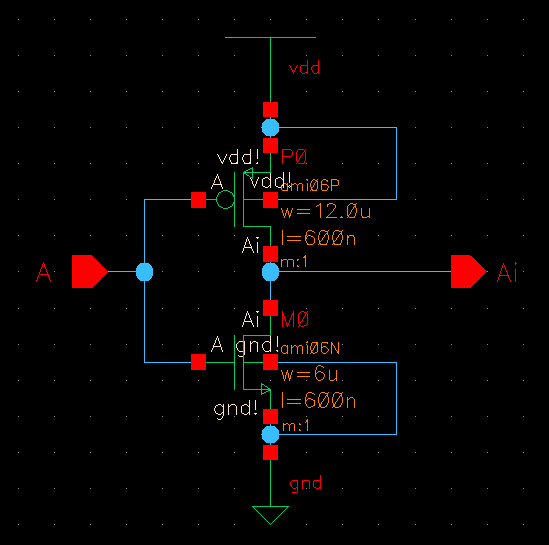

It first starts us off with creating a schematic for the invertor which can be seen below.

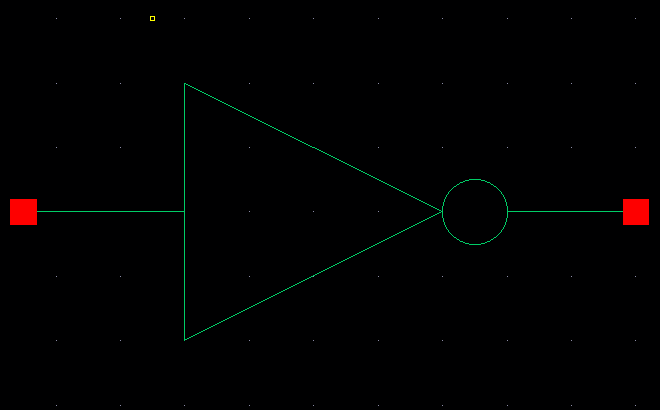

We then make a symbol out the schematic that we created and make it like how it is below.

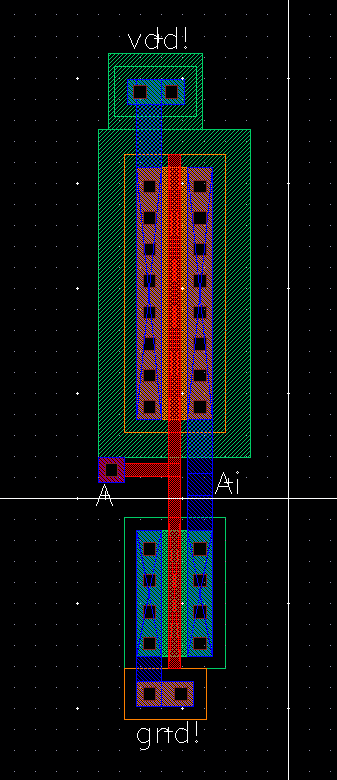

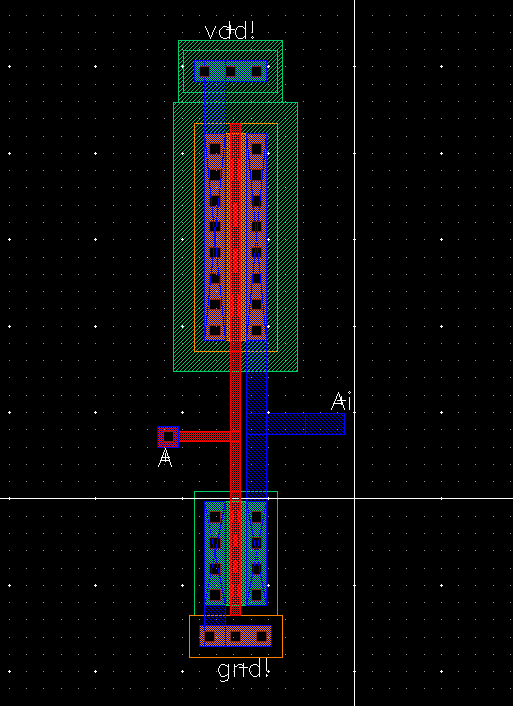

Now we make the layout for the inverter which should look like this.

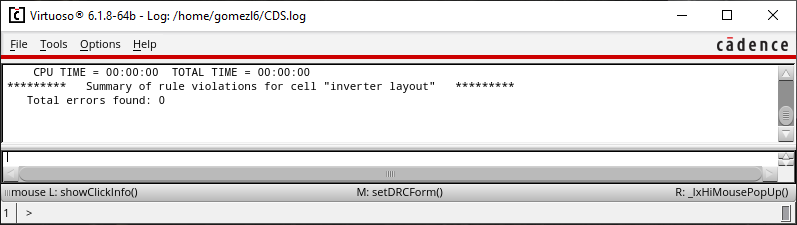

Now we check that it passes DRC.

We can then extract the layout which will look like this

Now we are able to run the LVS using our schematic and our extracted layout

The LVS gives a match.

Lab Work

For the lab, we are asked to make schematics, layouts, and symbols of two inverters with one being 12u/6u and the other being 48u/24u using a multiplier of 4. We are then also supposed to simulate the inverters using the symbols we createdby using the spectre and the UltraSim simulators.

First, I will start off with the 12u/6u inverter by creating the schematic.

After checking for no errors, now we will create a symbol for the schematic

Now we make the corresponding layout for the inverter

DRC clean

Now we extract the layout so that we can LVS.

Now to setup for the LVS check.

Now running the LVS we get a match.

Now I setup a schematic using the symbol which will be used to simulate.

First, I run the simulation using the spectre simulator

Then, we run the simulation again using the UltraSim

Now we go onto the next inverter which is a 48u/24u using a multiplier of 4. First, we start off with the schematic.

Now, we convert the schematic into a symbol.

Now we make the layout for the inveter

DRC clean

Now to extract the layout so that we can LVS.

Now to setup the LVS.

Running the LVS gives us a match.

Now to make the schematic that will be used for simulating.

First, we simulate using spectre.

Now, we simulate using UltraSim.

Based on the simulations, it seems that as you increase the capacitace, the output transitions slower. Comparing the two inverters, it seems that the size of the MOSFET also affects the output with the smaller one transitioning slower because of the higher resistance and the larger one transitioning faster becuase their isn't as much resistance.

Here is a zip file of my work.