Lab 4 - EE 421L

Pre Lab

For the pre lab, we are supposed to go through Tutorial 2 which consists on laying out NMOS and PMOS devices.

We first start off with the NMOS which it has us setting up the layout and the schematic for it.

Lab Work

We start off the lab by creating a schematic to simulate a ID vs. VDS for a NMOS device for VGS varying from 0 to 5V in 1V steps and VDS varies from 0 to 5 V in 1 mV steps. The NMOS measures 6u by 0.6u.

Now when we run the simulation this is what we get.

Now we will make a schematic that simulates a ID vs. VGS for a NMOS device for VDS = 100 mV and VGS varies from 0 to 2V in 1 mV steps. The NMOS also measures 6u by 0.6u.

This is what we get when running the simulation.

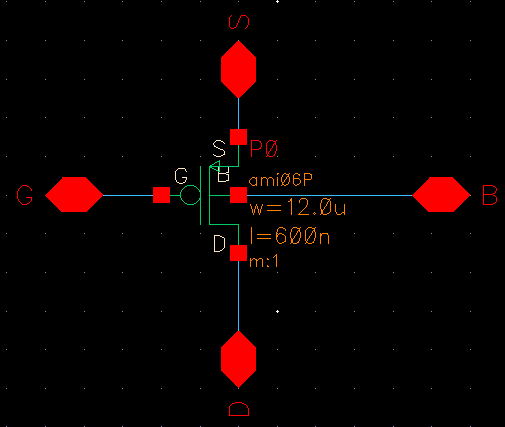

Now we move on to the PMOS which we start off with a schematic to simulate a ID vs. VSD of a PMOS device for VSG that varies from 0 to 5 V in 1 V steps and VSD varies from 0 to 5 in 1 mV steps. The PMOS measures 12u by 0.6u.

This is what I get from the simulation.

Now we make a schematic that simulates a ID vs. VSG of a PMOS device with VSD = 100 mV and VSG varies from 0 to 2 V in 1 mV steps. The PMOS also measures 12u by 0.6u.

Running the simulation results in this.

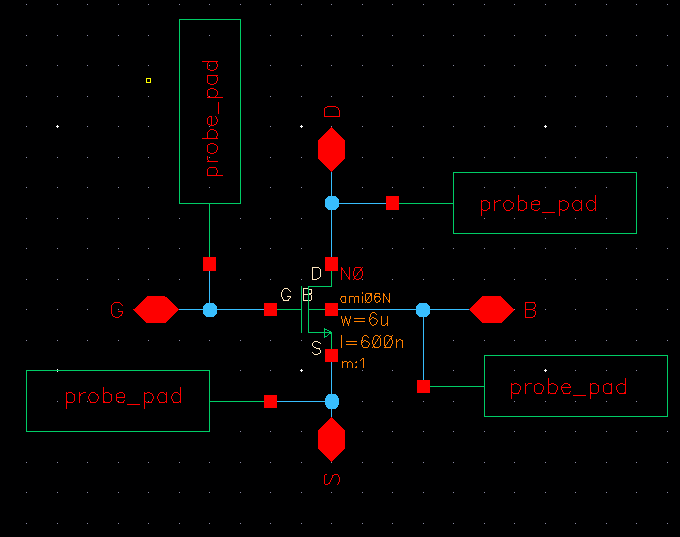

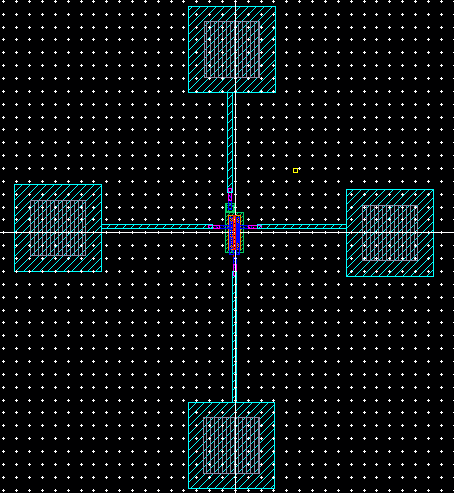

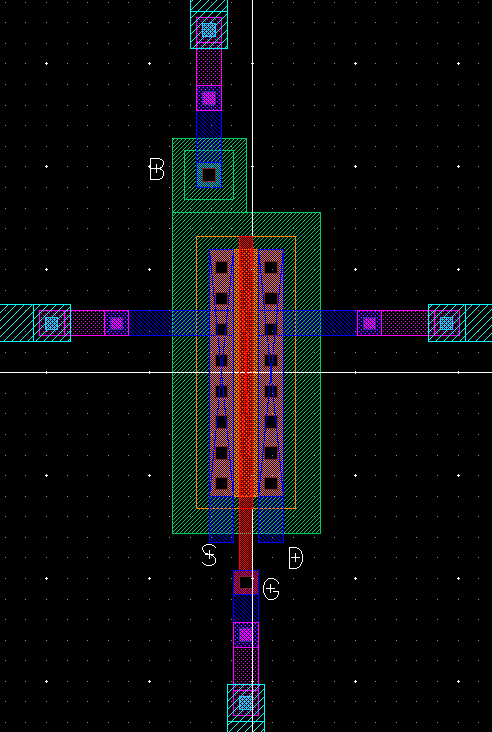

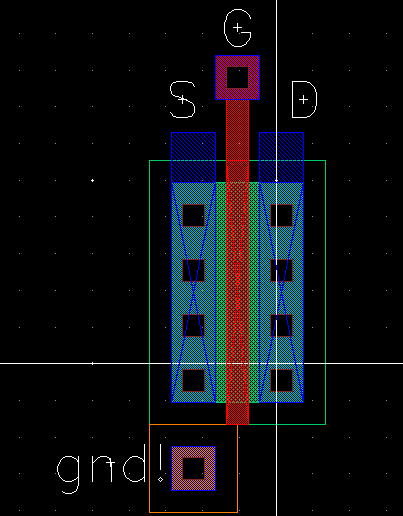

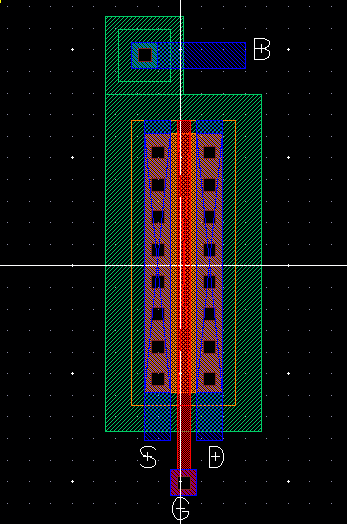

Now we are to layout a 6u by 0.6u NMOS device with all 4 MOSFET terminals connected to probe pads.

Close up view of the NMOS.

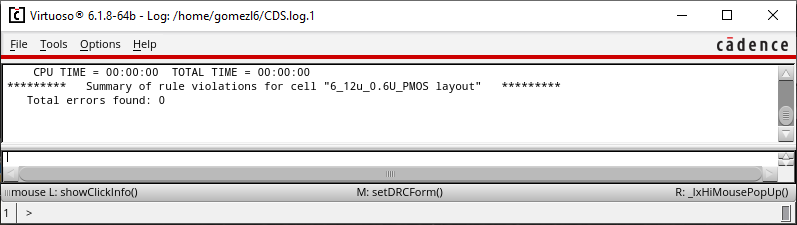

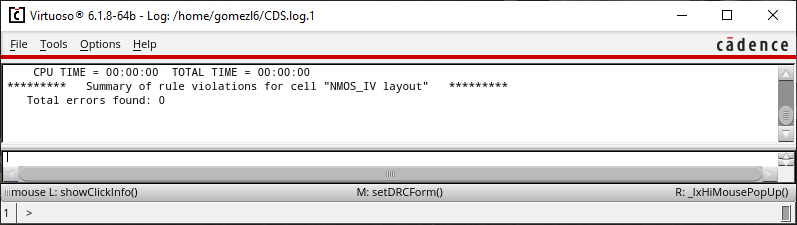

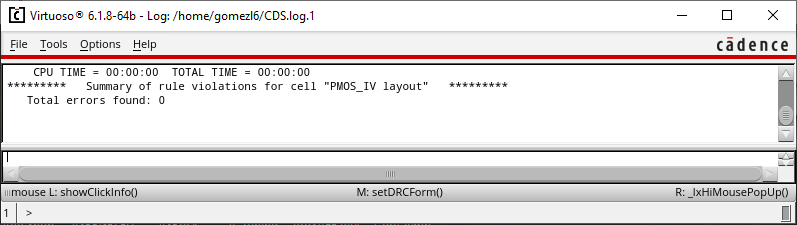

DRC clean

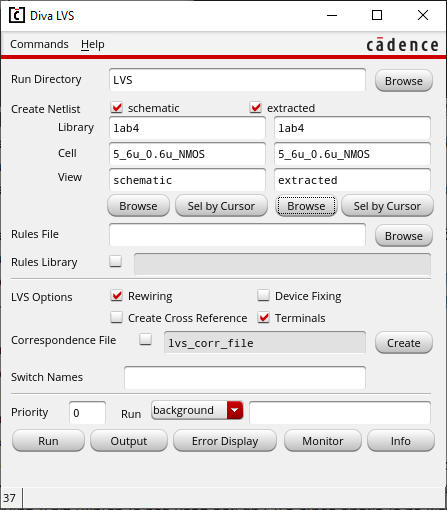

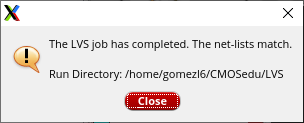

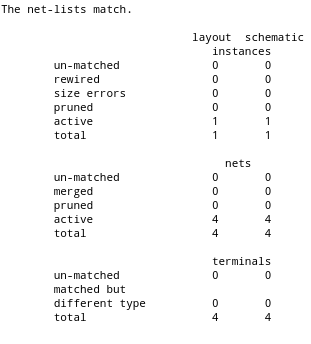

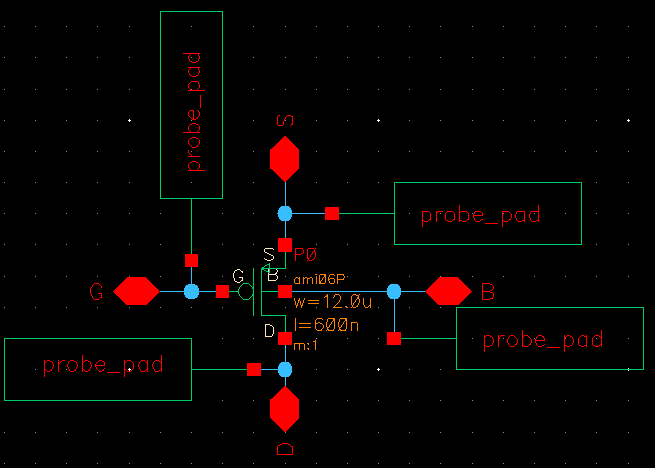

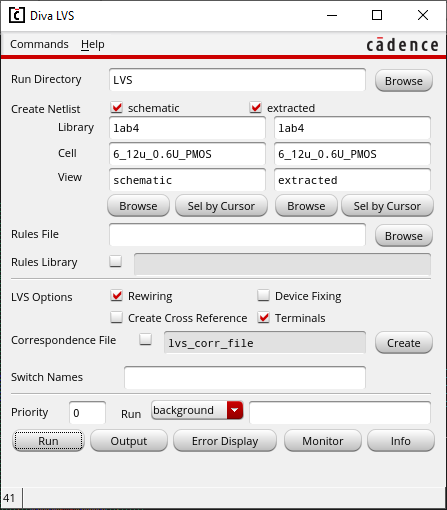

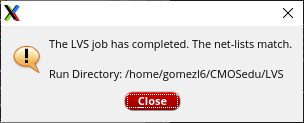

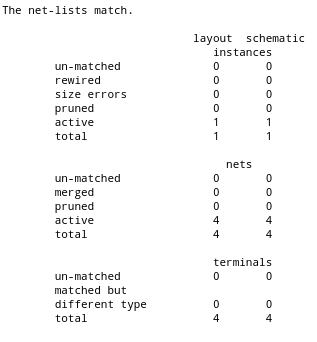

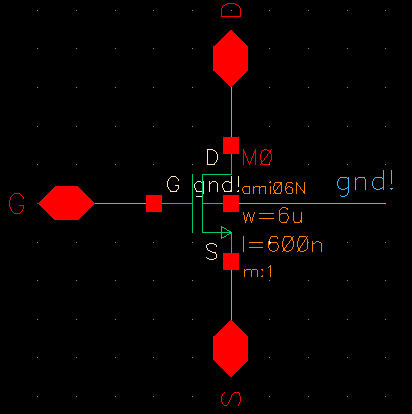

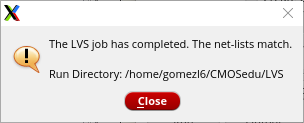

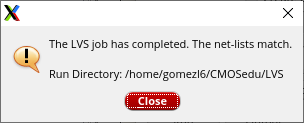

Now to make a corresponding schematic so that we can LVS check it.