Lab 3 - EE 421L

Now we can create the symbol and then go in and draw it out which will look like this.

After checking and saving our symbol, we can now try it out to make sure that it works. First, I will make a copy of the R_div cell and call it sim_R_div.

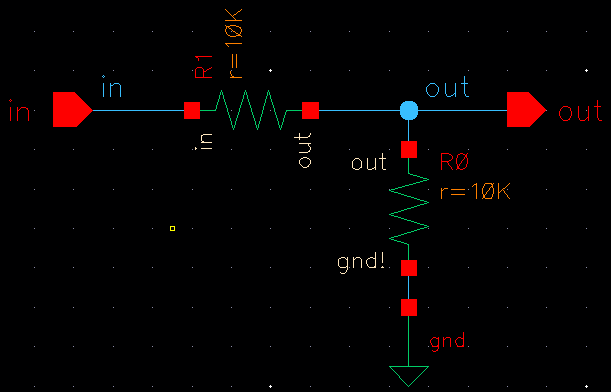

Now we create a schematic that makes use of the newly created symbol.

And when running the simulation we end up with the same results we got in the original schematic.

Now we can proceed to make the layout for the schematic but before that, we have to create a layout for a 10k resistor. Our resistor will measure 56.1 for length and 4.5 for width. We also add in the connections on both ends of our box both with 2 contacts and also apply the metal1 on the contacts. To finish it off, we add in the res_id to the center box in order to indicate that it is a resistor. The final setup can be seen below.

After making sure that our layout passes DRC, we can then extract our layout and verify that we got the correct resistance.

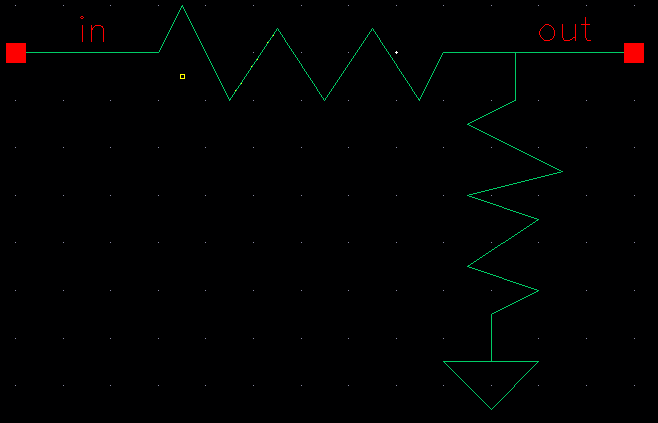

Now using the 10k resistor layout we just made, we can now make the layout for the voltage divider which looks like this.

Now I run DRC to check for any errors.

Now we have to extract our layout which will be used to verify if it matches up with our schematic using the LVS feature.

Now to begin with the layout I will lay down resistors in parallel and add in the metal connections for each of the bits.

Now we run the DRC check to verify that the layout was setup right.

Now we can extract our layout which will look like this.

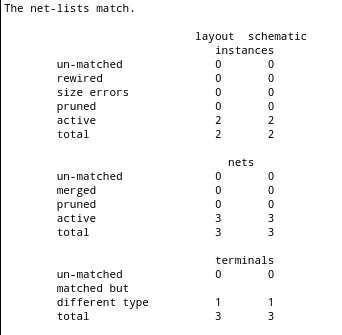

Now we have to run the LVS to ensure that the layout and the schematic match up

The schematic and layout match up.

The zip file of the final design can be seem below which includes lab 2 and 3.