Lab 2 - EE 421L

Pre Lab

After reading through the entire lab write-up, we start the prelab by downloading the lab2.zip file from the write-up and unzipping in the CMOSedu directory in MobaXterm.

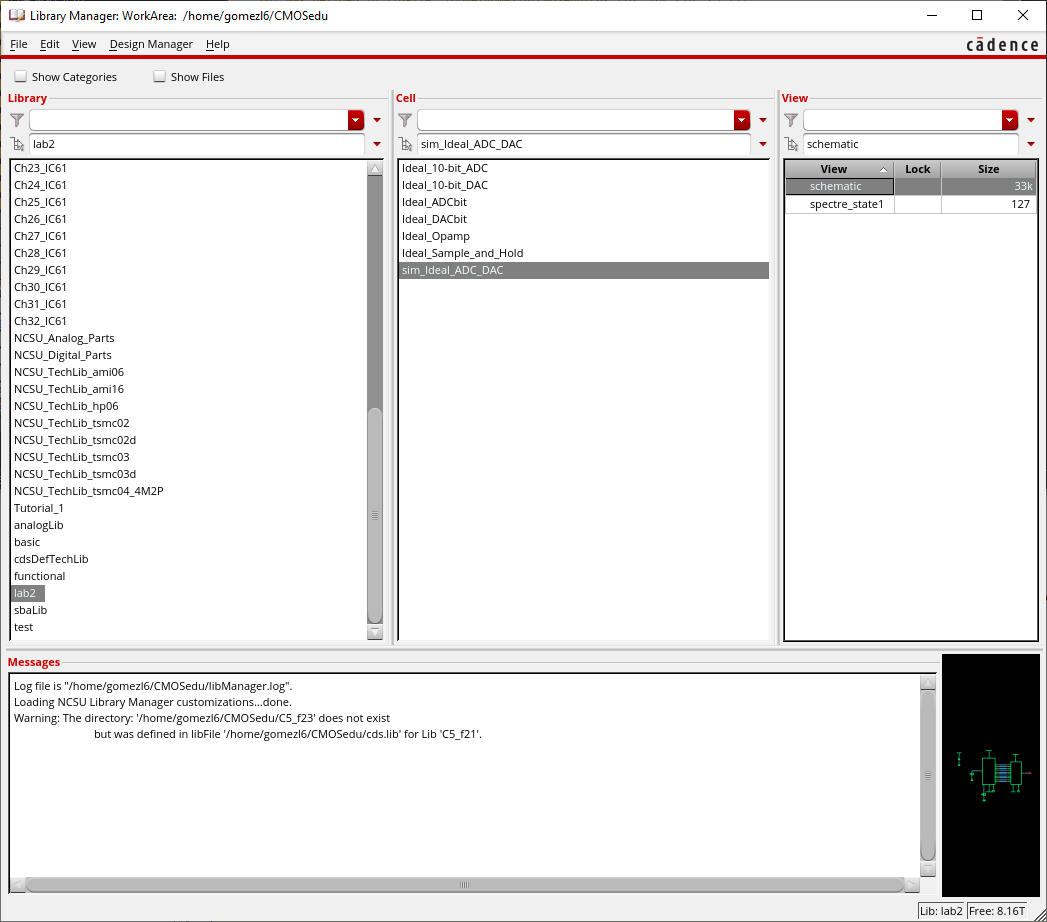

After adding in the DEFINE into the cds.lib file, we can now go into the file manager and open the cell named sim_Ideal_ADC_DAC.

This is how the schematic looks like.

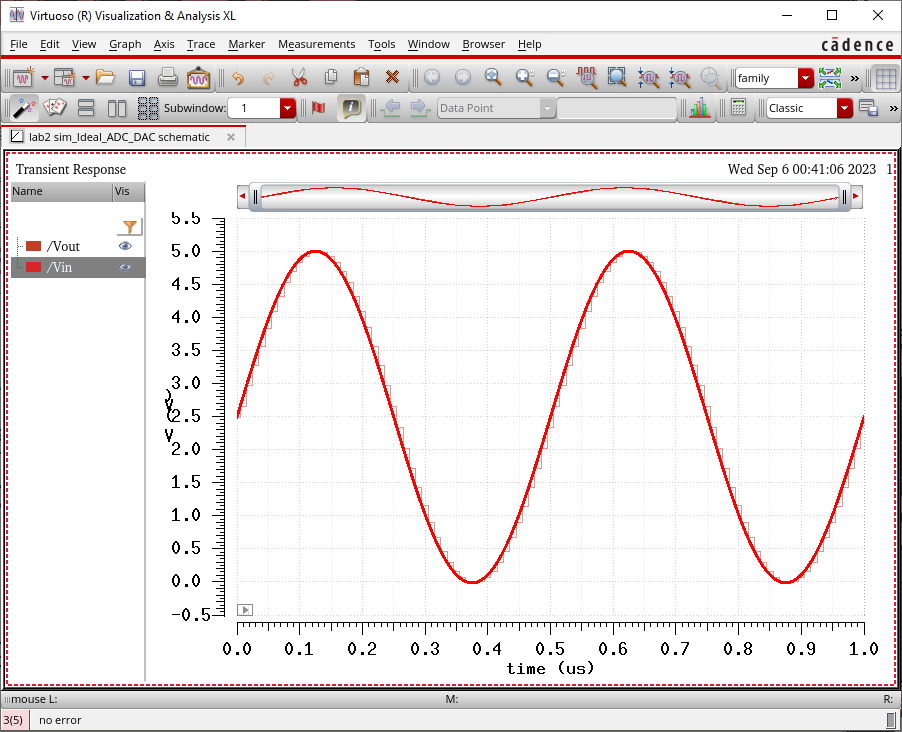

Now we can run ADE L and the simulation looks like this.

Lab Work

To start off with creating the DAC, first, we make a voltage divider schematic that we could use to make a symbol.

We can then create the symbol which can be seen below. The symbol will work as one bit.

We can now use the created symbol to make the 10-bit DAC. The resulting schematic can be seen below.

Then, we are able to create a symbol of our 10-bit DAC schematic.

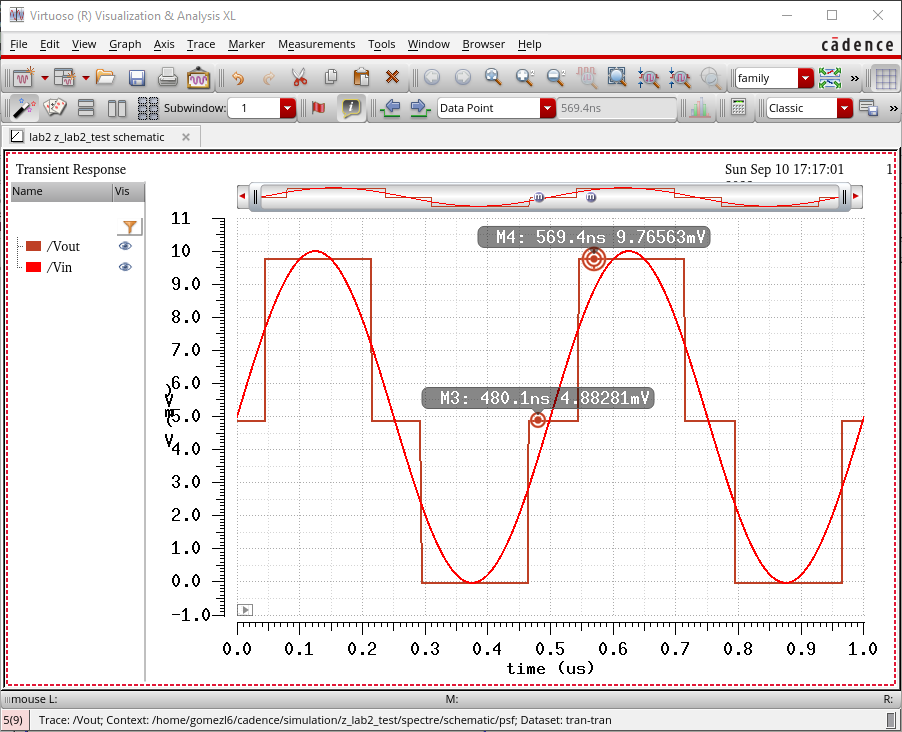

Now, we are suppposed to find the time delay for the DAC which can be done by setting bits 0:8 to ground and then setting 9 to a pulse source. First, I did the hand calculations and ended up getting 70ns.

So to solve for the time delay, we will use the resistance we got and also the 10 pF load.

Time Delay = 0.7 (10k)(10pF) = 70ns

Now to verify our hand calculations using a simulation with our DAC.

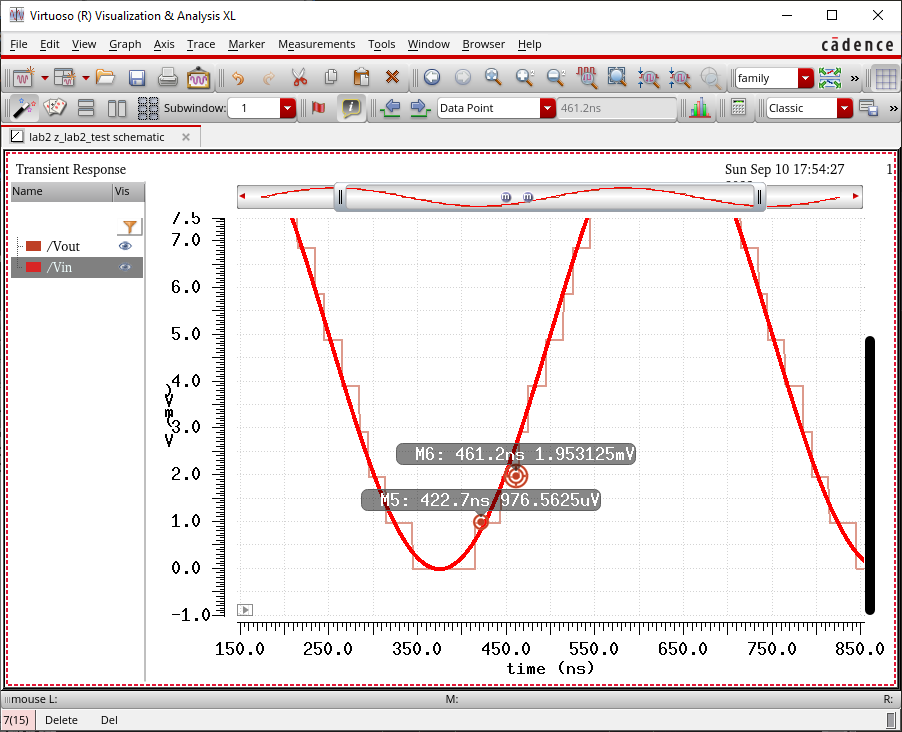

These are the results from the simulation

We can now simulate our DAC by replacing the Ideal_10-bit_DAC with ours in the sim_Ideal_ADC_DAC.

After running the simulation, we can see that the result is similar to the result we got with the ideal DAC.

Now lets see what happens if we were to add in a 10k load.

It seems like when adding in the extra 10k load, the voltage output is cut in half of the input voltage. This could be because since the output resistance of the DAC is 10k, adding in the extra 10k resistance resulted in another voltage divider which would explain why the output voltage was halfed.

Now, instead of the extra resistance load, we will now try running it with the 10pF load.

It seems like adding in the capacitor smoothened out the output voltage while also creating a delay.

And lastly, we will add in both the resistor and the capacitor.

It seems like for this one, the result has a mix of what happened with the resistor and the capacitor with the resistor causing the output voltage to be cut in half while the capacitor smoothened out the curve.

The lab also ask what happens if the resistance of the switches isn't small compared to R in a real circuit. If the switches were to have a high resistance, then we would also have to take into account those values because just like when we added in the extra resistor, it resulted in a lower output voltage. The same thing would occur with the switches with them interfering with the voltage dividers which would then result a smaller voltage.