Lab 1 - EE 421L

Now, we can go into Cadence by typing in cd CMOSedu and then virtuoso & which should load up the library manager.

We will now create a new library named Tutorial_1 by going into file->new->library. It should be setup like how it is below.

After verifying that the DEFINE was added into the cds.lib file, we can now add in a cell into the newly created library called R_div by selecting the library then going to file->new->cell view and the setup should look like how it is below.

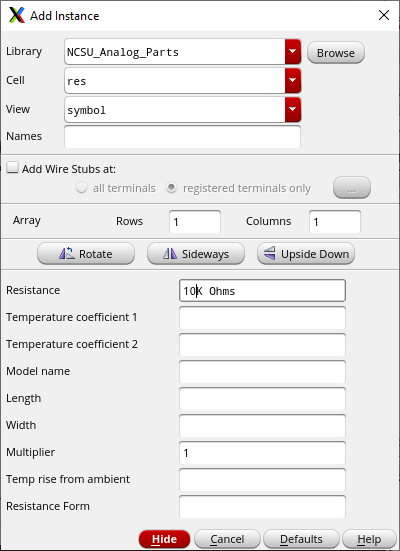

Now we are able to start creating our schematic by using create->instance or the shortcut key I to add in components. We can then select our components in the component browser by selecting NCSU_Analog_Parts in the library and to add in a resistor, we select R_L_C and then select res and can then set the resistance to 10k.

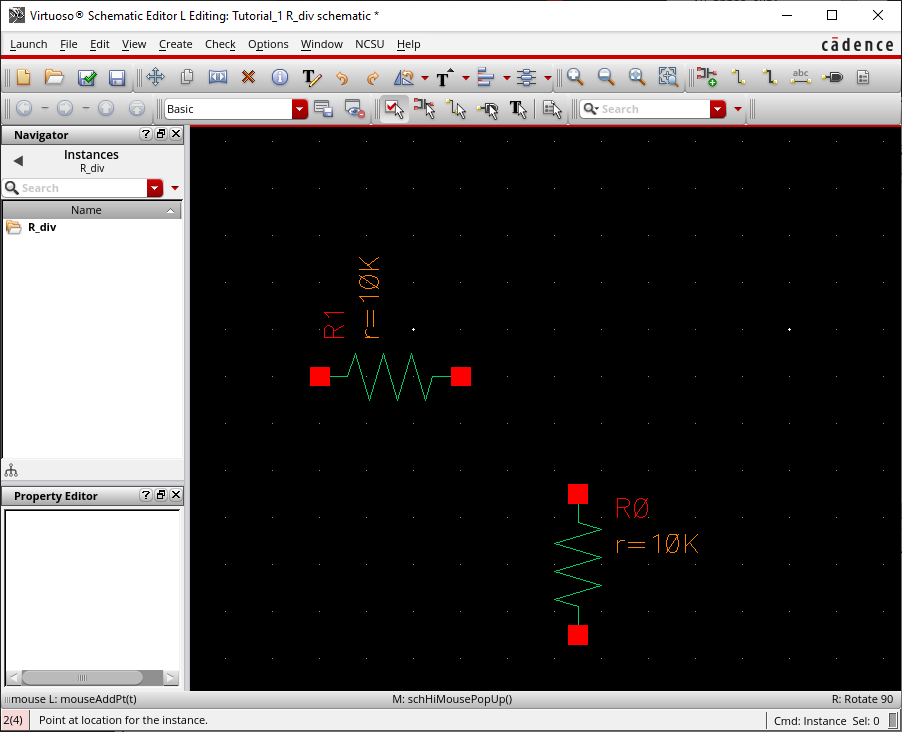

The final schematic should end up looking like this once all the componenets have been placed.

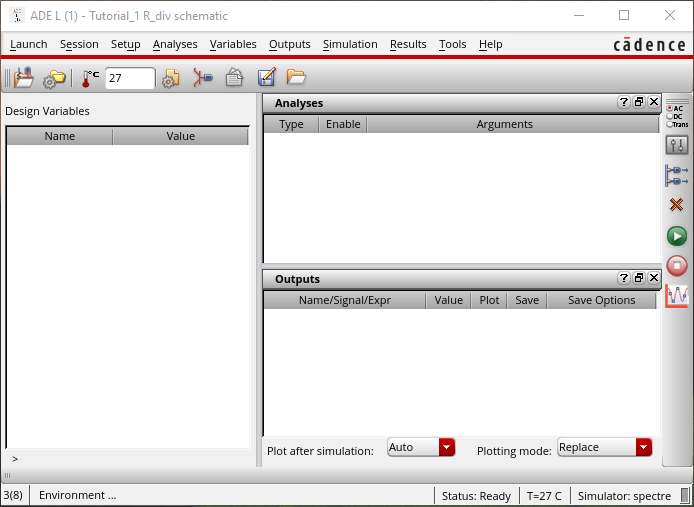

If there is no errors, we can then simulate our schematic by going into launch->ADE L.

We can now setup our simulation by setting the analysis to .tran and by selecting our outputs that we are simulating which in this case is in and out.

Now we are ready to simulate.

The simulation results can be seen below.

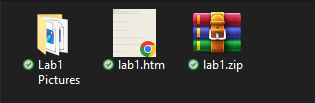

Lastly, we are supposed to occasionally backup our files in case if anything goes wrong, then we won't have to worry about losing all of our progress. First, I will throw all of my files in a zip folder.

Then, I will email the zip file to myself that way I have the backup files easily available in case anything happens with my work.