Lab 7 - ECE 421L

Prelab: In this

prelab, we demonstrate the workings of a ring oscillator.

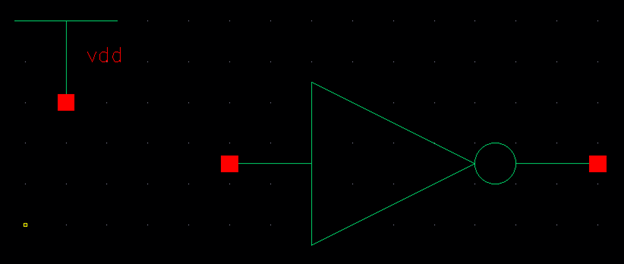

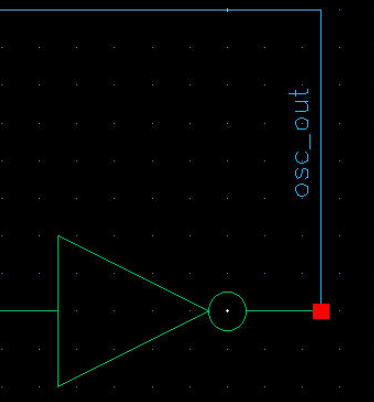

For our first step,

we use the Inverter symbol as our steppingstone w/ a VDD as the supply net.

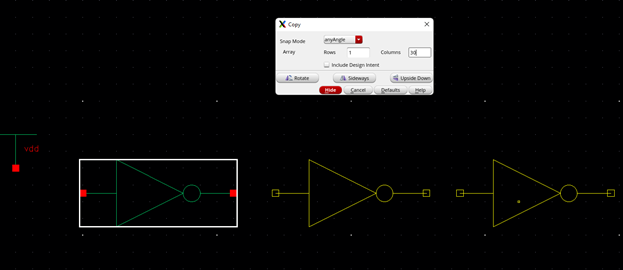

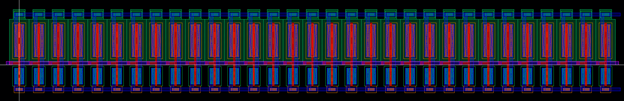

Next, we layout our 31

ring oscillator with the following steps as a short cut, Select

Inverter-> Keybind C (For copy)-> Columns = 30

![]()

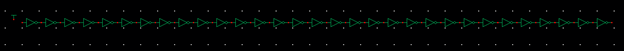

We now have the following:

We finish it up by connecting the ends

to each other:

![]()

![]()

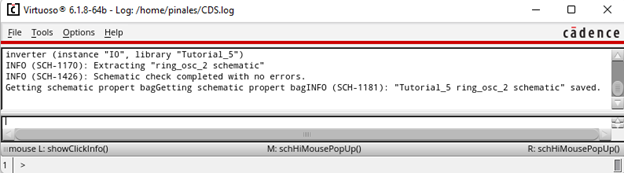

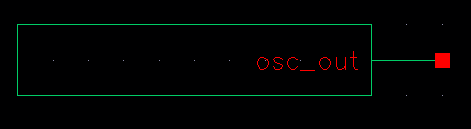

For our labeling I have gone with the

same label as tutorial, osc_out. Now we have our ring

oscillator set up which we then proceed to the simulation of the schematic.

But before we do the simulation, we

first must edit the simulation for certain parameters needed for the schematic.

VDD = 5 V

Select the outputs to plot -> select osc_out

Set the analysis to a transient with a length of 200 ns

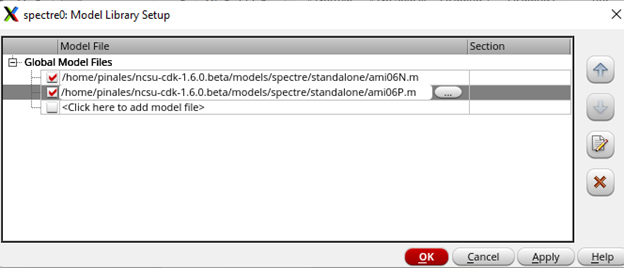

*Note – When simulation make sure the

model libraries are saved to simulation. (Setup -> model libraries)

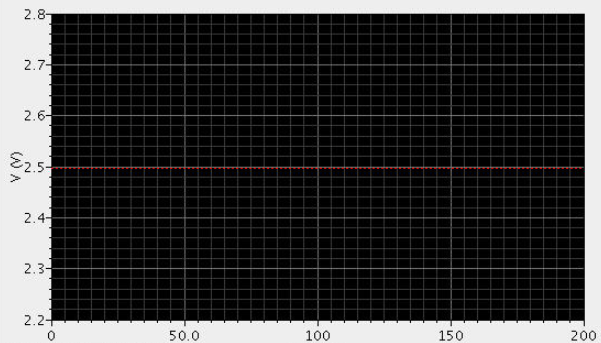

As shown in the simulation, we have a

steady voltage of 2.5V.

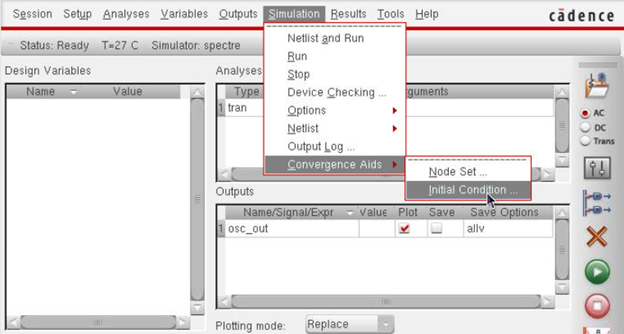

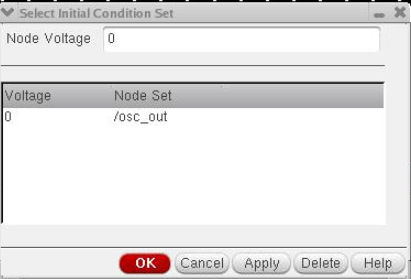

Now, from ADE L simulation window

-> Convergence Aids -> initial condition -> Select node 0:

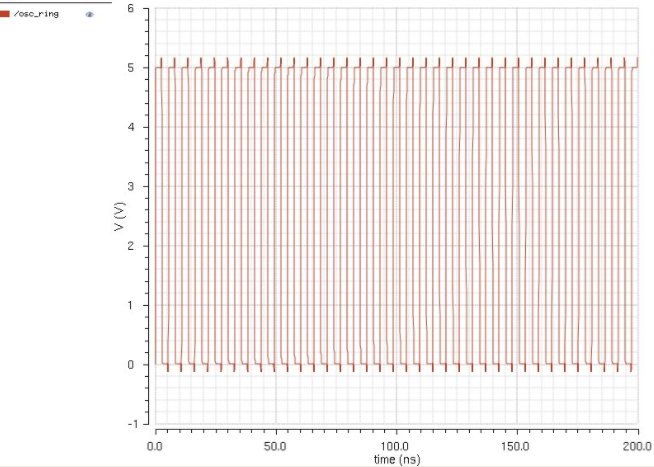

Simulation of

Ring Oscillator:

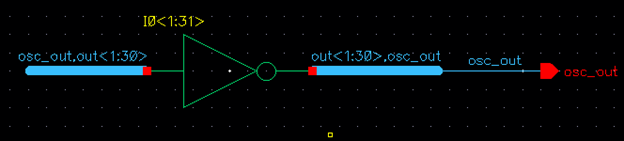

Now, once the completion of the Ring

Oscillator, we turn the wires into busses for the 31 inverters in place.

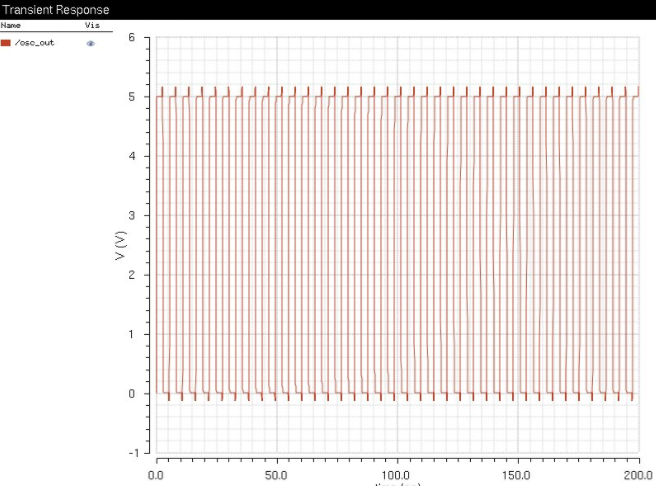

Finally, we simulate the given the

circuit to get the following result:

A similar output is shown to give us

an understanding on if the circuit satisfies the previous schematic. No we turn the circuit into a symbol and proceed to the

layout.

Symbol:

Now, We then

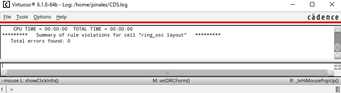

proceed to the layout of the given circuit with a DRC and LVS to see if the

schematic and layout match up.

Layout

Boom! That’s the end to Prelab 7.

Lab

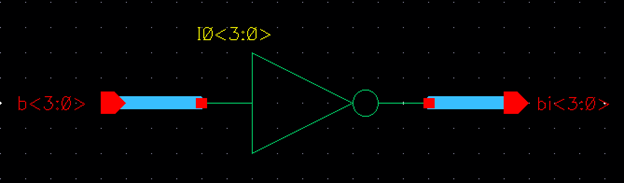

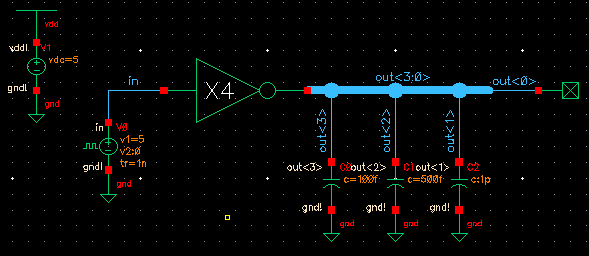

Experiment 1:

4-Bit Inverter

Schematic:

Simulation:

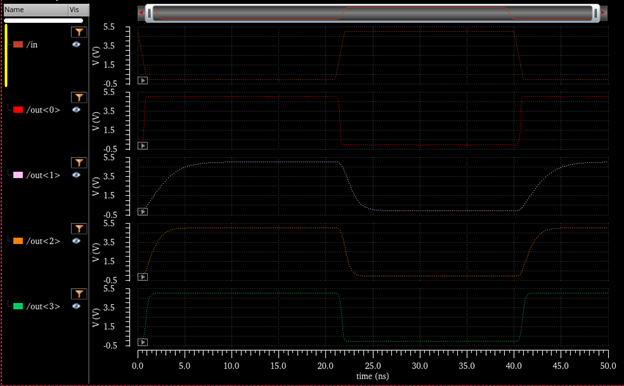

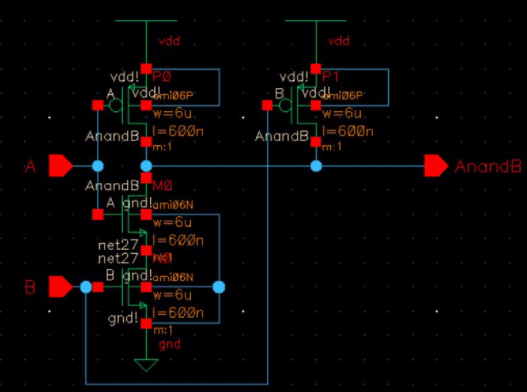

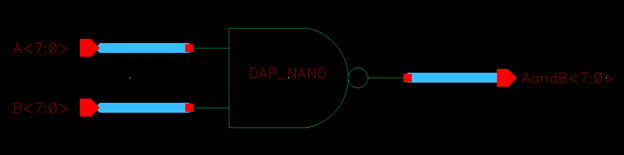

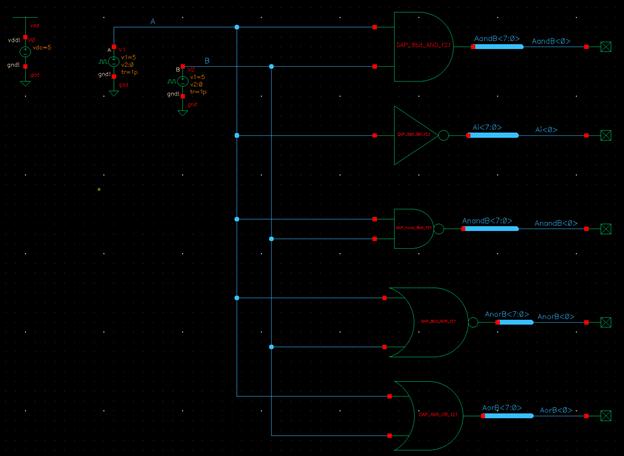

Experiment 2: 8-bit array of NAND, NOR, AND,

inverter and OR gates

Transistor Level Schematics:

NAND:

NOR:

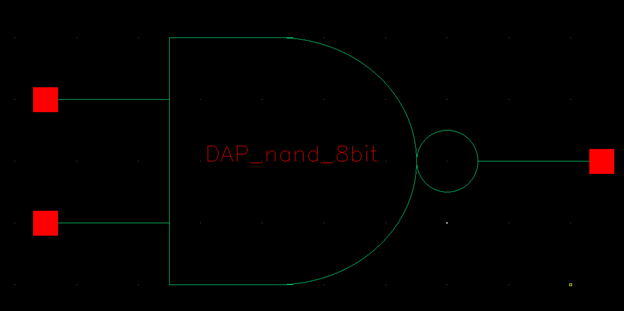

8-Bit NAND Schematic:

8-Bit NAND Symbol:

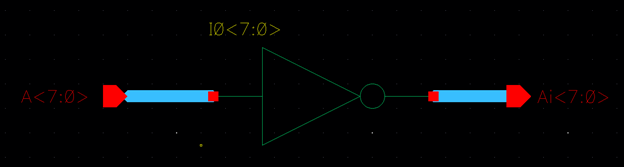

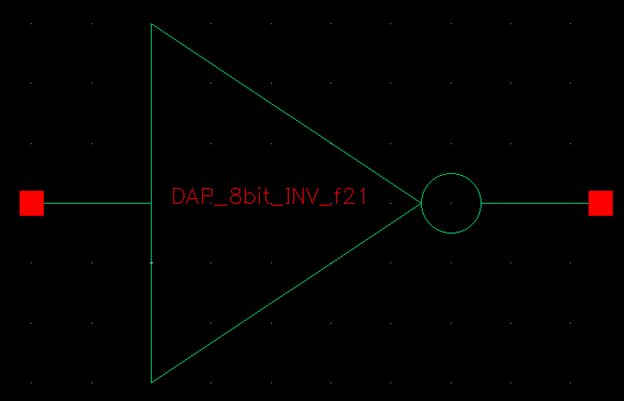

8-Bit Inverter

Schematic:

Symbol 8-Bit

Inverter:

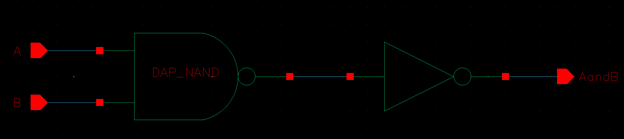

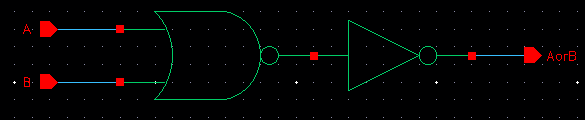

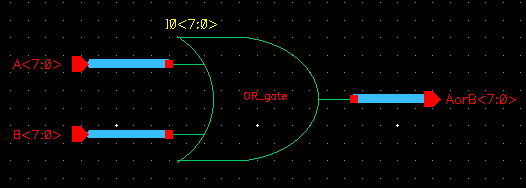

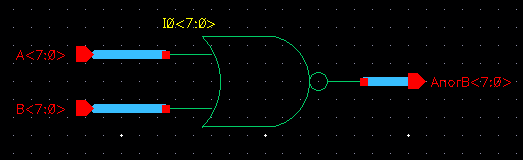

*Note – For efficiency, we build the

AND and OR gates bypassing transistor level by simply

adding an inverter into the NAND and NOR gates output:

AND:

OR:

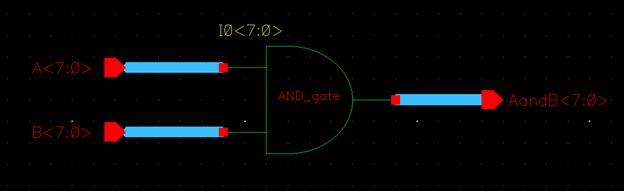

8-Bit AND

Schematic:

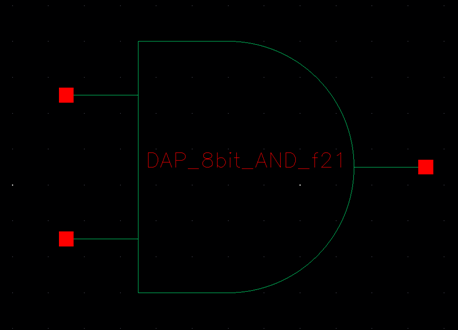

8-Bit AND

Symbol:

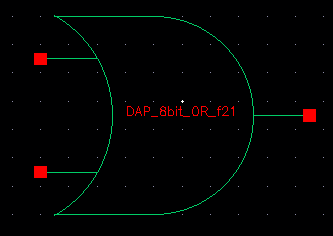

8-Bit OR

Schematic:

8-Bit OR

Symbol:

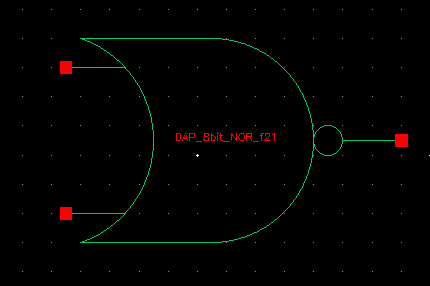

8-Bit NOR

Schematic:

8-Bit NOR

Symbol:

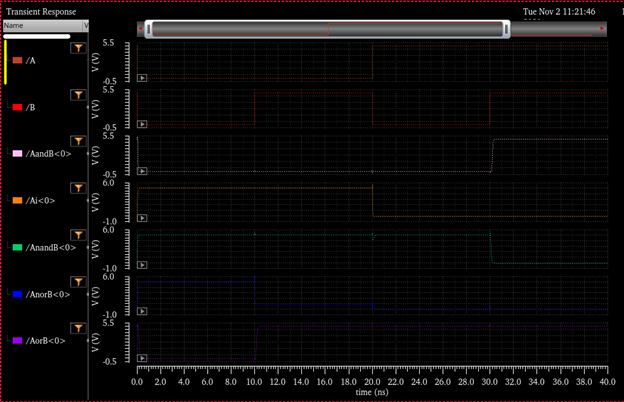

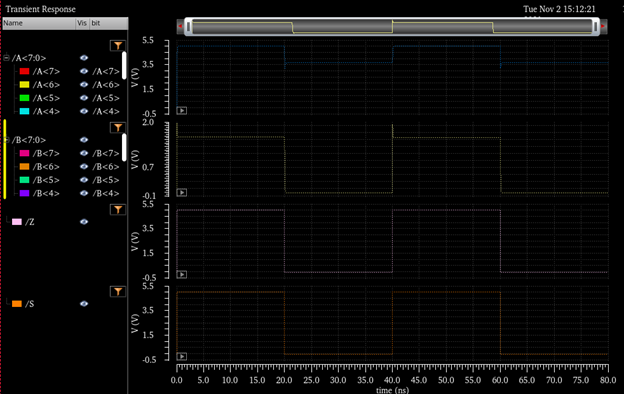

Simulation of

Gates:

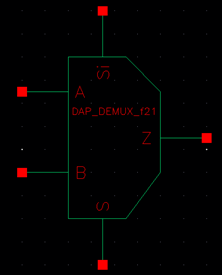

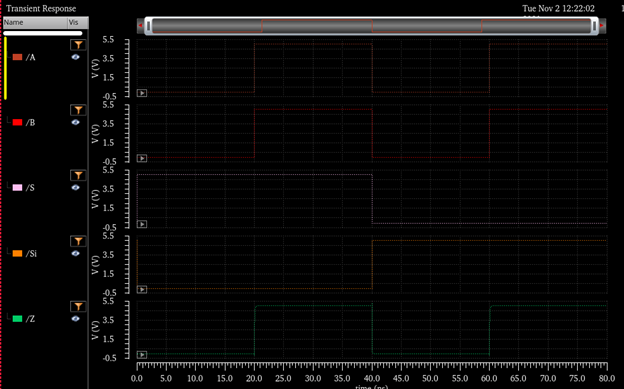

Experiment 3: 2-to-1 DEMUX/MUX:

-

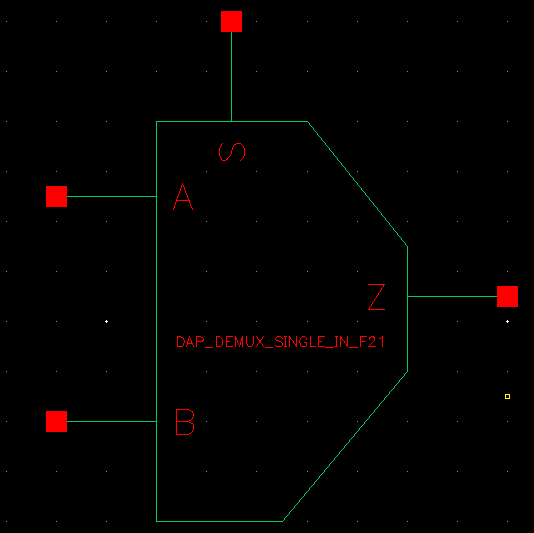

DEMUX -Symbol

2-input Select

w/ Simulation:

-

MUX S has a high A propogate through,

whereas Si has a strong B propogate through.

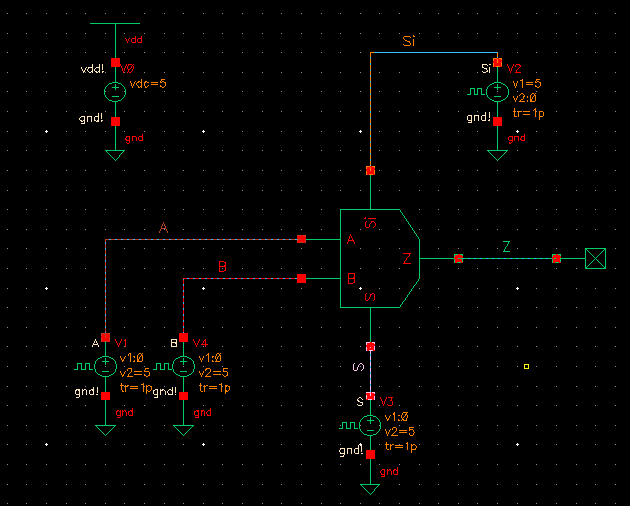

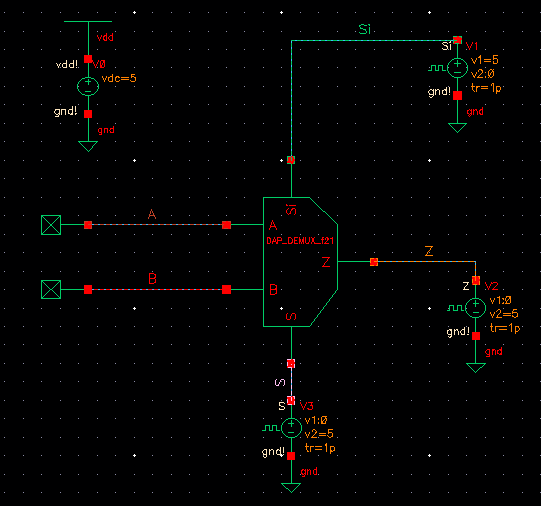

DEMUX

Simulation w/Schematic:

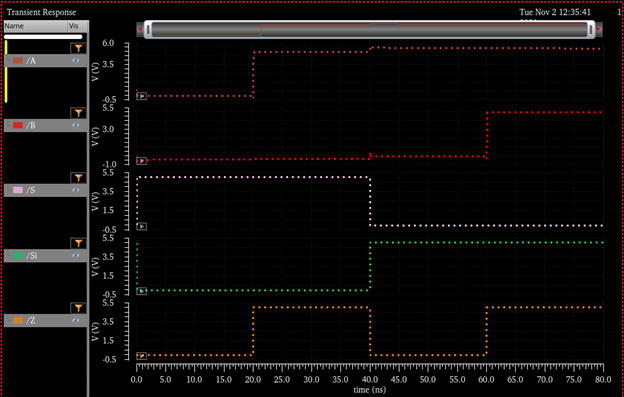

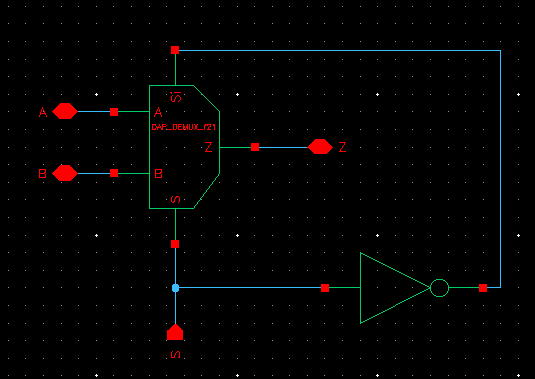

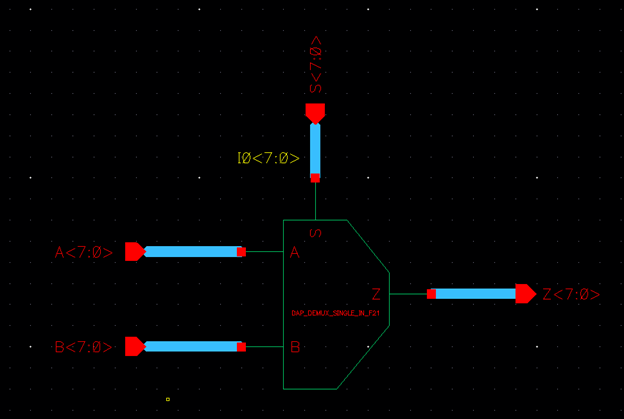

Single Input

Select Schematic w/Symbol & Simulation:

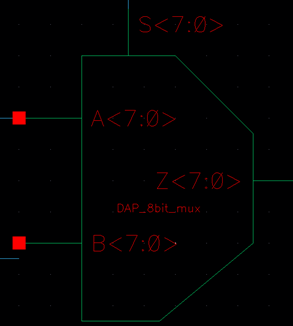

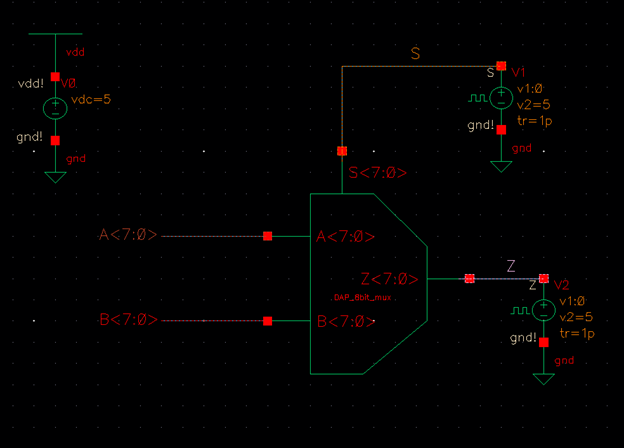

8-Bit Mux/Demux Schematic/Simulation:

Symbol:

Schematic:

Simulation:

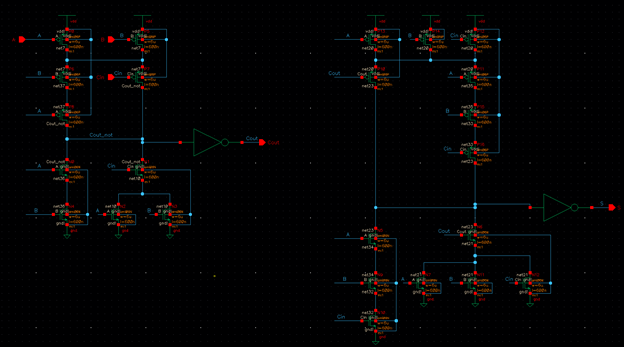

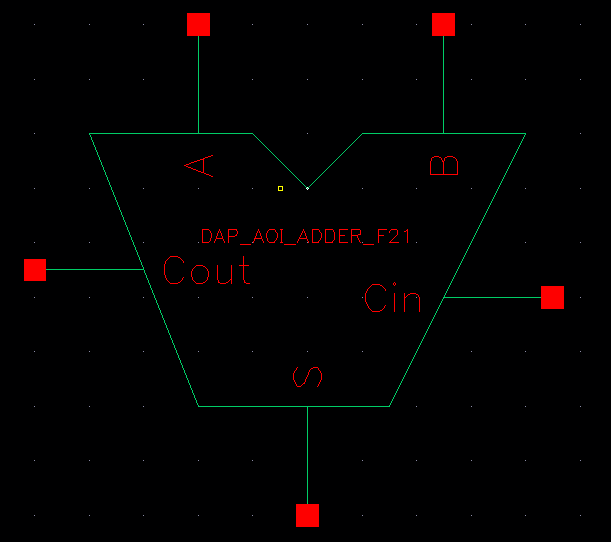

Experiment 4

AOI Full Adder:

Schematic:

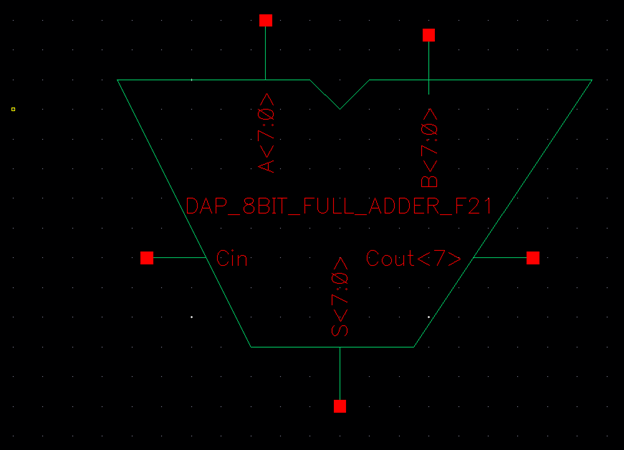

Symbol:

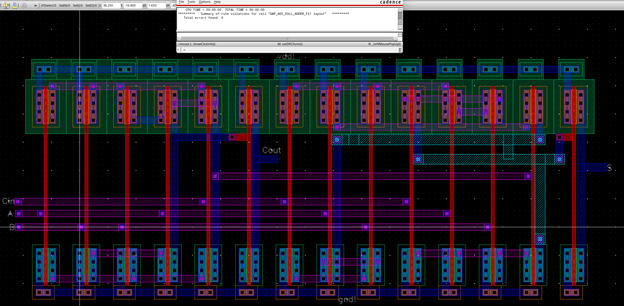

Layout:

![]()

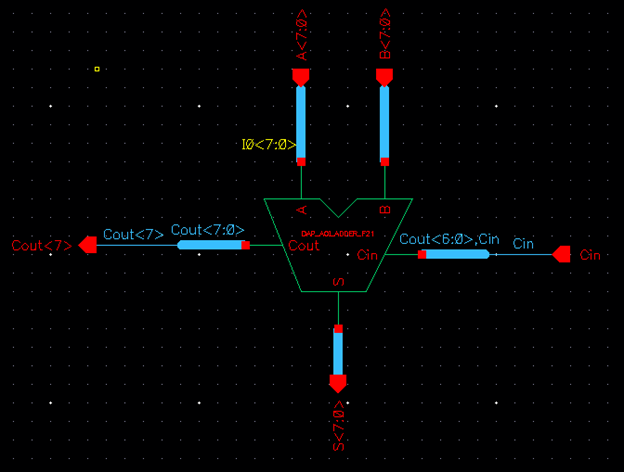

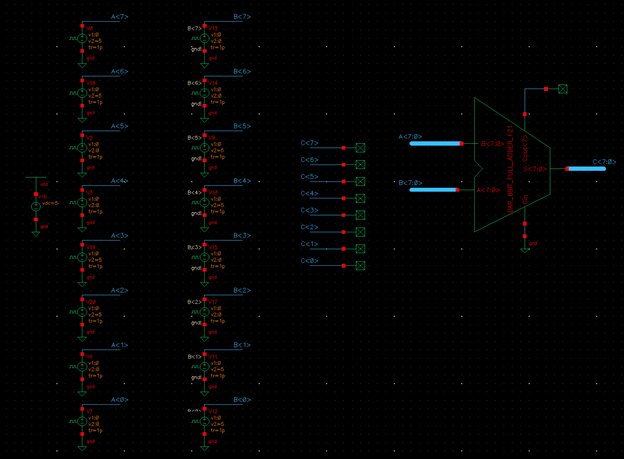

Schematic of

8-bit Adder:

Symbol:

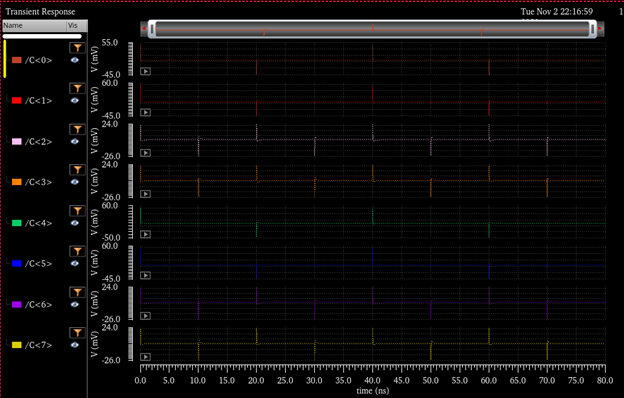

Simulation:

Layout:

![]()

Extracted:

![]()

This concludes Lab 7.

Add a return to the listing of your

labs