For the prelab, I was tasked with going through tutorial 4 which shows the process for laying out a 2 input NAND gate. The first step for laying out a CMOS NAND gate is to first create a schematic with our input and output pins. In this case we only needed to add 2 inputs(a & b) and 1 output(AnandB). The schematic above has error markers because we're editing our previously created inverters so we haven't told the rest of our files that we are no longer creating an inverter.

After creating my schematic I next created a symbol out of that schematic. This step is again really basic as I've done this multiple times throughout the lab. The only difference this time is I had to create a specific symbol instead of just a box. In this case, I had to create a NAND symbol.

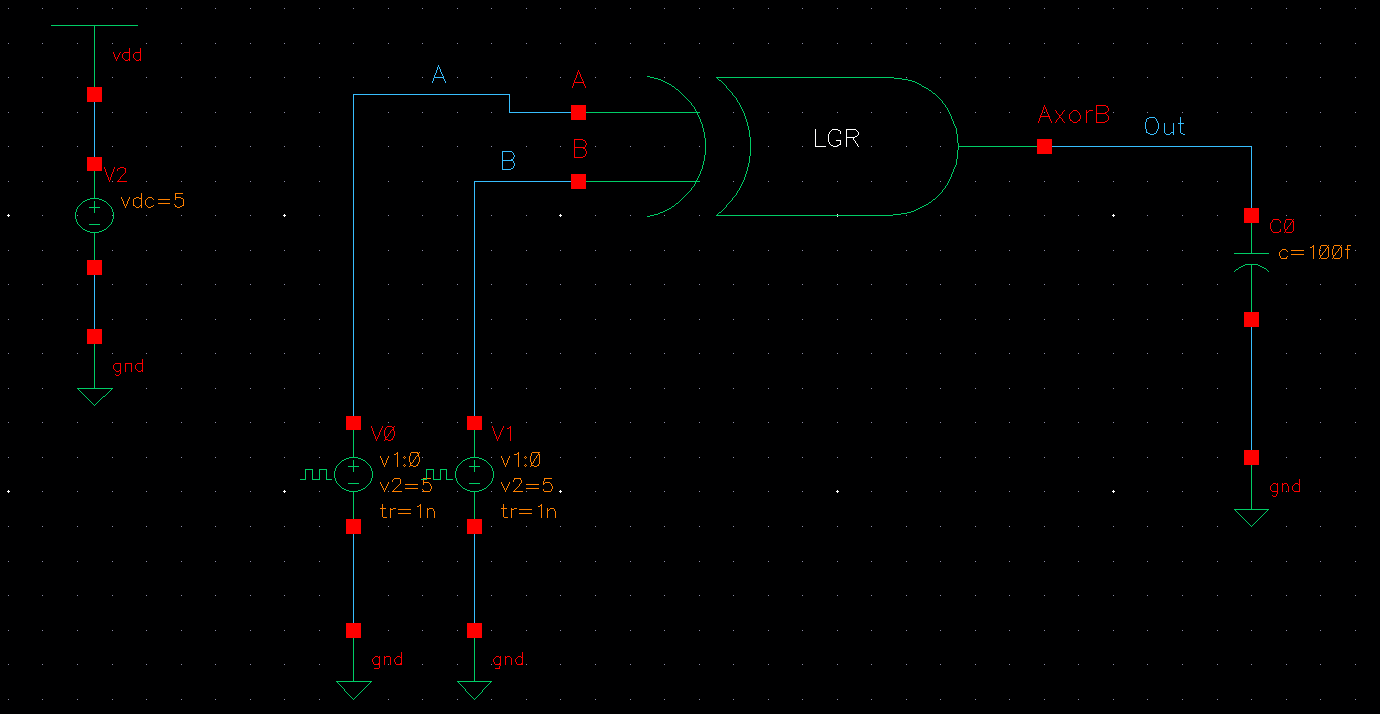

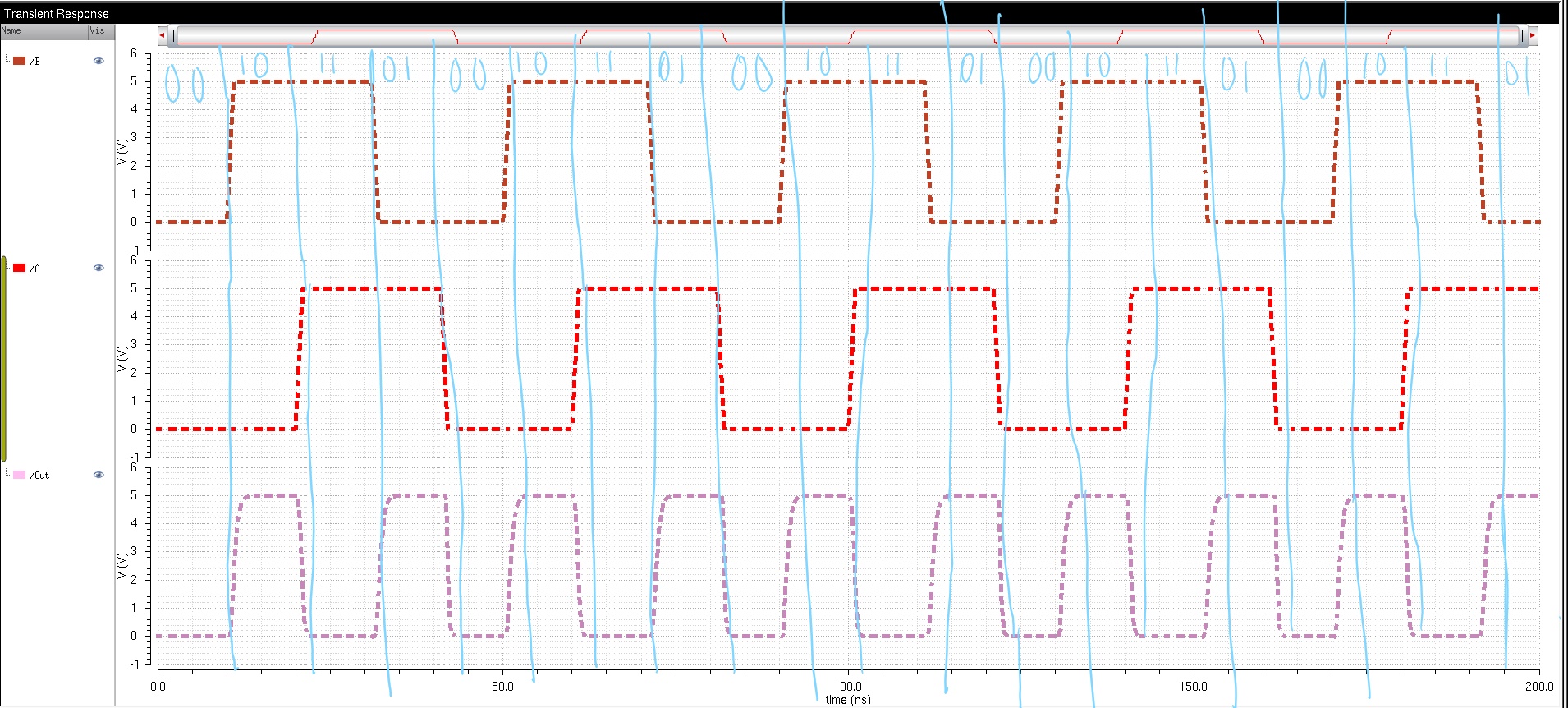

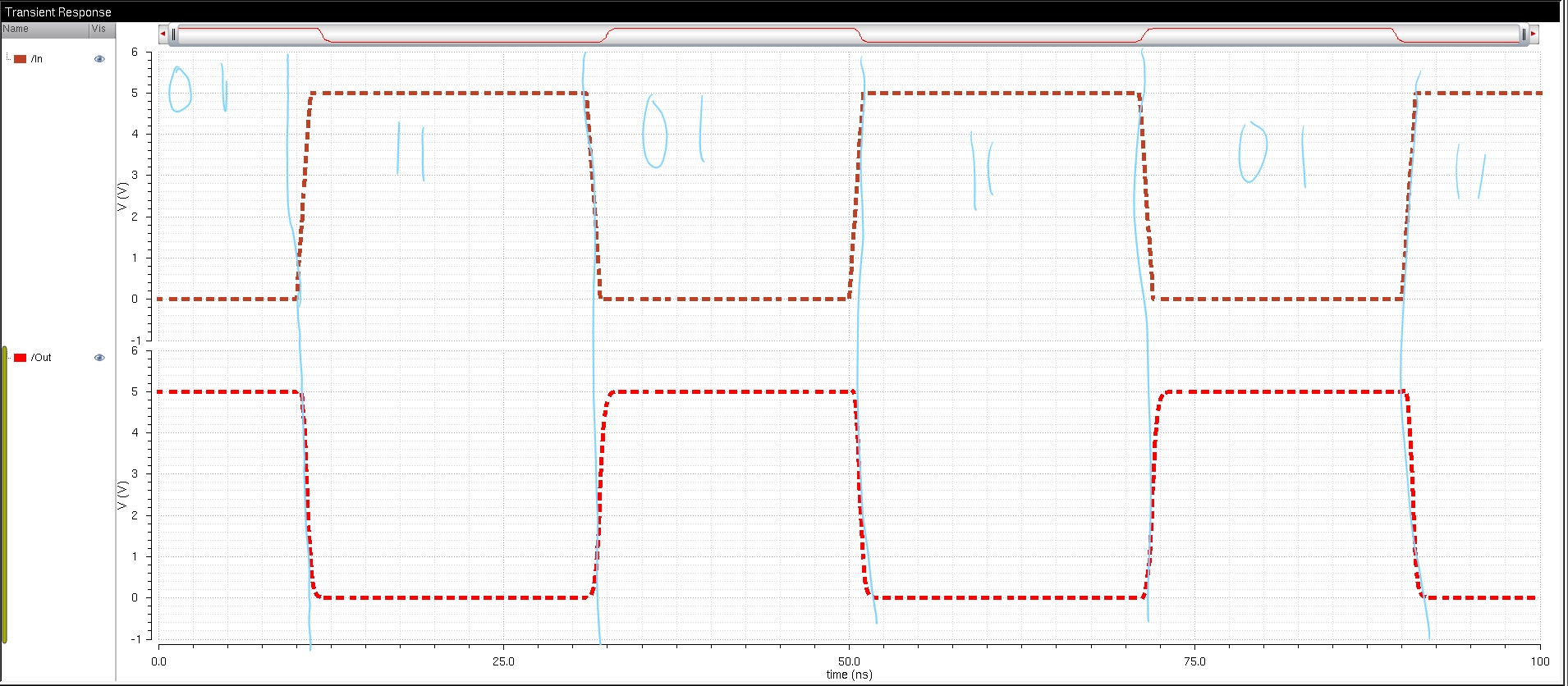

The next step was simmming the symbol to make sure that our schematic is correctly behaving like a nand gate. To do this we added a pulse signal to one of our inputs so that it alternates between "0" and "1" (not exactly a digital since pulse signal is analog but you get the point.) and our other signal is set to VDD so it's always high.

Following tutorial 4, we're only simming 2 cases. The first case both inputs are set to 1 in which case our NAND should output 0 and the case in which 1 input is set to 1 and the other is 0 which should output 1. As we can see in the screenshot above our schematic is in fact behaving like a NAND.

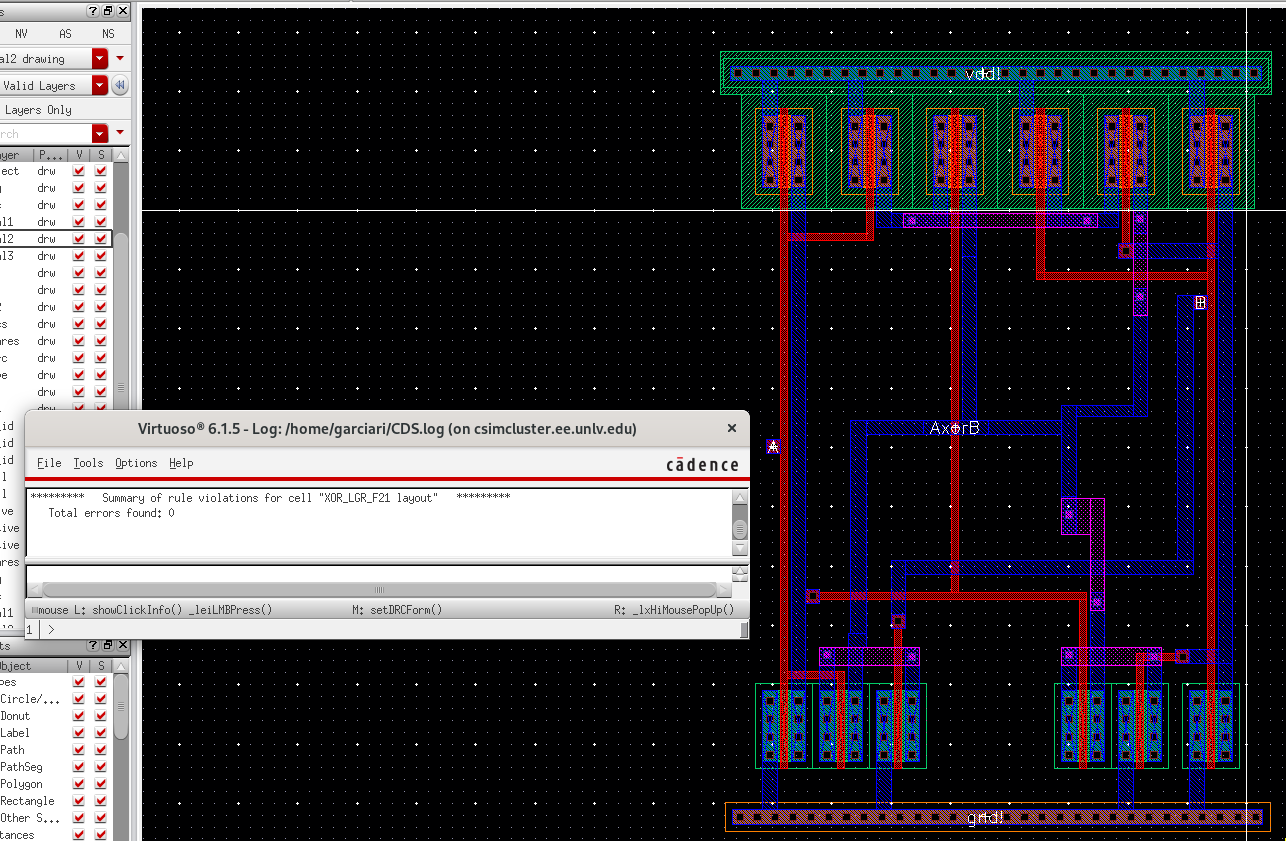

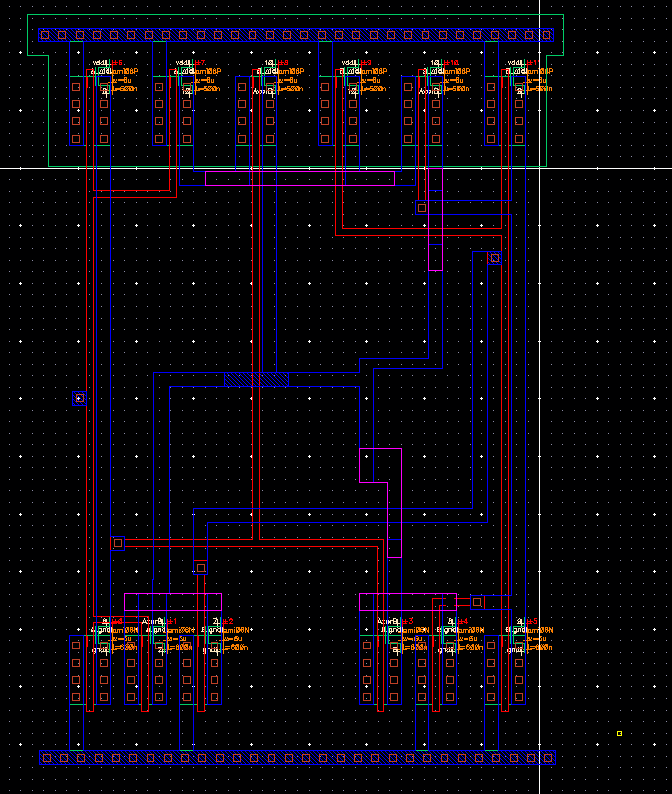

Since I've confirmed that our NAND schematic is in fact following NAND behavior I can move onto the next step in the tutorial which is laying out the NAND gate. This step was simple except that I've learned 2 new ways of laying out. The first is since our schematic has the drains of the pmos connected together, we can over lay the drains on top of each other in our layout to reduce width. The second is since both sources of our NMOS are connected together we can overlay 2 of the NMOS and remove the one of their contact areas to have a shared drain and source. I drc'd my layout to confirm my layout follows DRC rules and moved onto the next step.

I next extracted my design and LVS'd to confirm that my layout fits LVS rules.

We passed LVS.

Normally we would be finished however we had an added step in which we see how our layout PMOS doesn't actually match the size of our schematic PMOS. To see this we had to edit LVS rules so that it would account for tracking FET sizing.