Lab 2 - EE421L

Damian Aceves Franco

acevesfr@unlv.nevada.edu

09/01/2021

Design of a 10-bit digital-to-analog converter (DAC)

Pre-lab work

- Read through this entire lab write-up before doing the pre-lab

- Download lab2.zip to your desktop.

- This

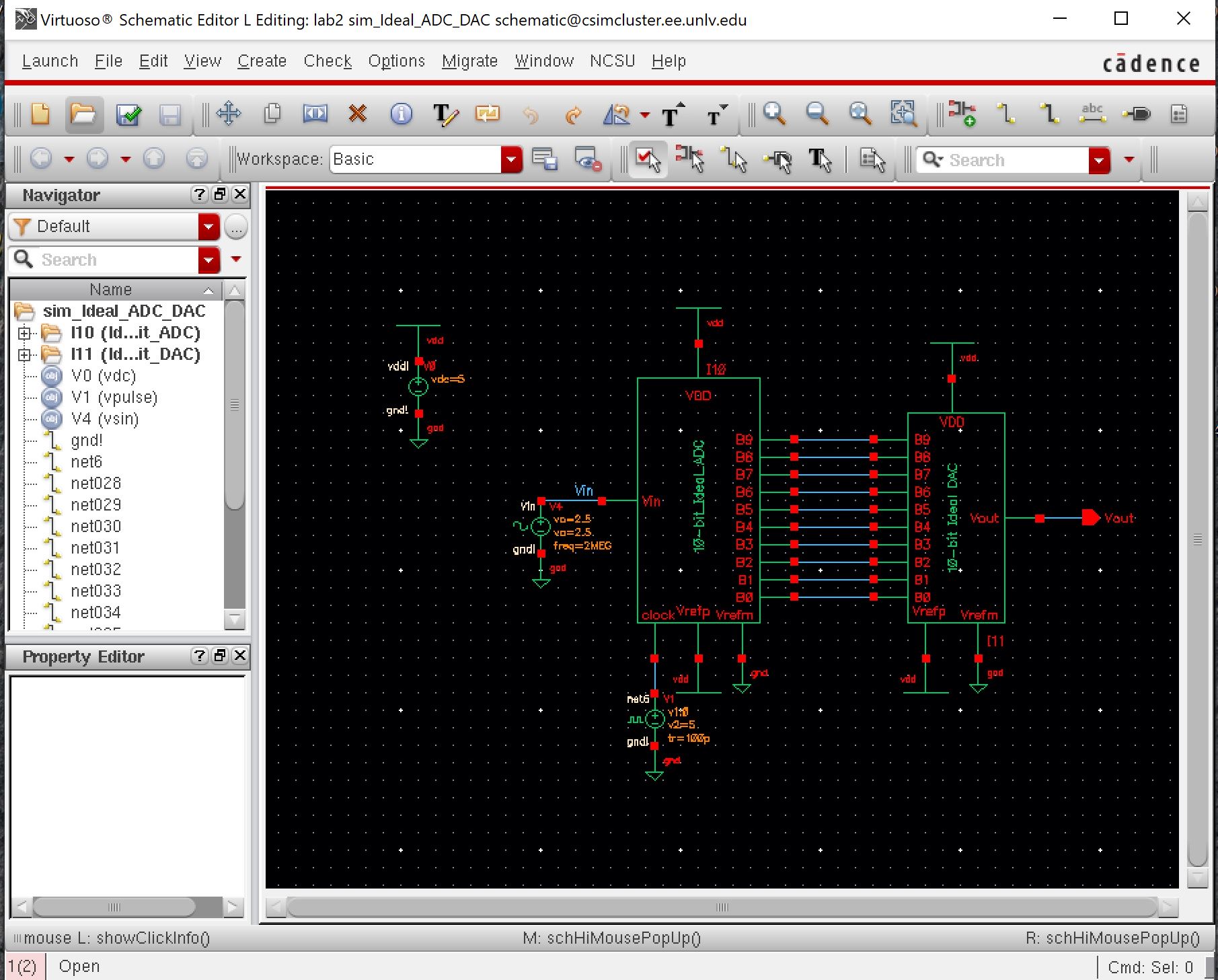

archive contains a simulation example using an ideal 10-bit

Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter

(DAC).

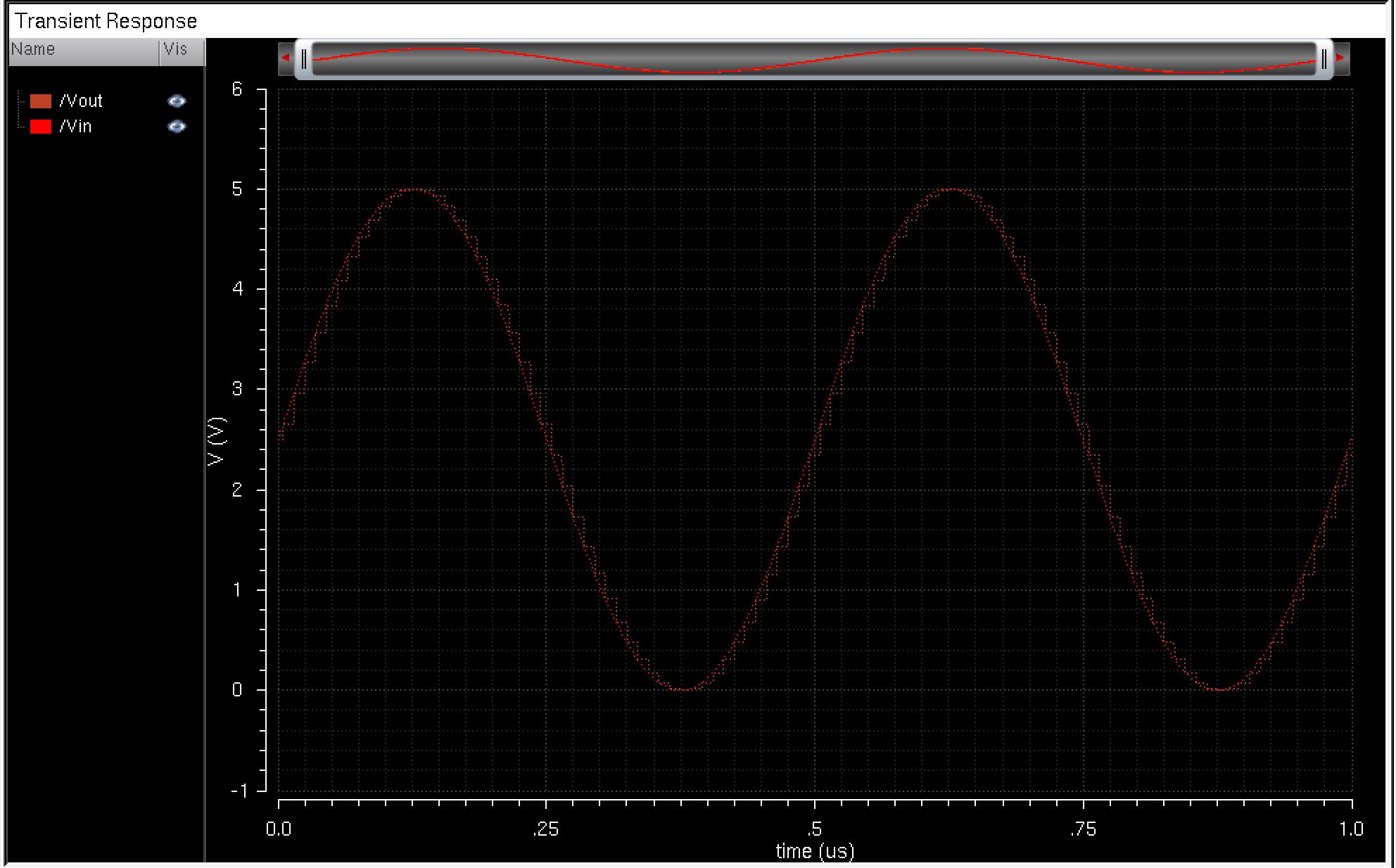

- Prior to coming to lab make sure you understand how the input voltage, Vin, is related to B[9:0] and Vout.

- In your lab report:

- 1) provide narrative of the steps seen above,

- 2) provide, and discuss, simulation results different from the above to illustrate your understanding of the ADC and DAC,

- 3) explain how you determine the least significant bit (LSB, the minumum voltage change on the ADC's input to see a change in the digital code B[9:0]) of the converter. Use simulations to support your understanding.

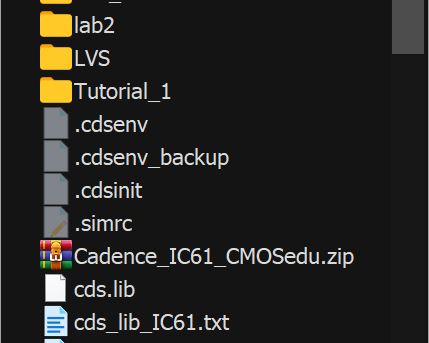

up load lab2.zip to MobaxTerm and unzip

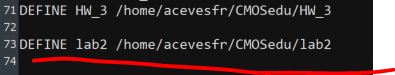

then check to see if the design directory is in the cds.lib if now type it and save

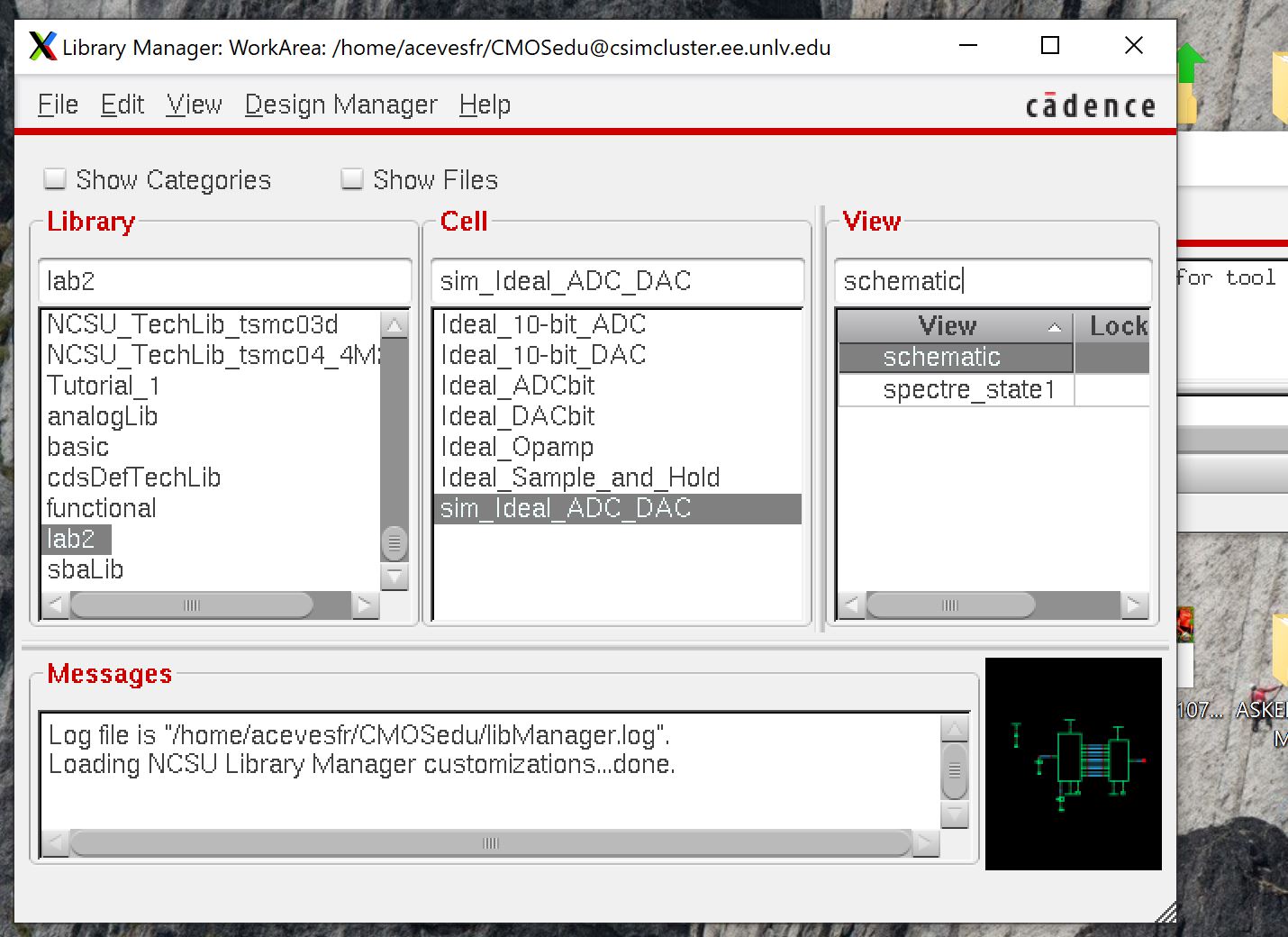

now run virtuoso and open the schematic

then run ADE L

The least significant bit (LSB) is determined my useing the equation 1LSB=(Vdd)/2^n.

in this case the 1LSB is 5/2^10 = 4.88mV

return to labs