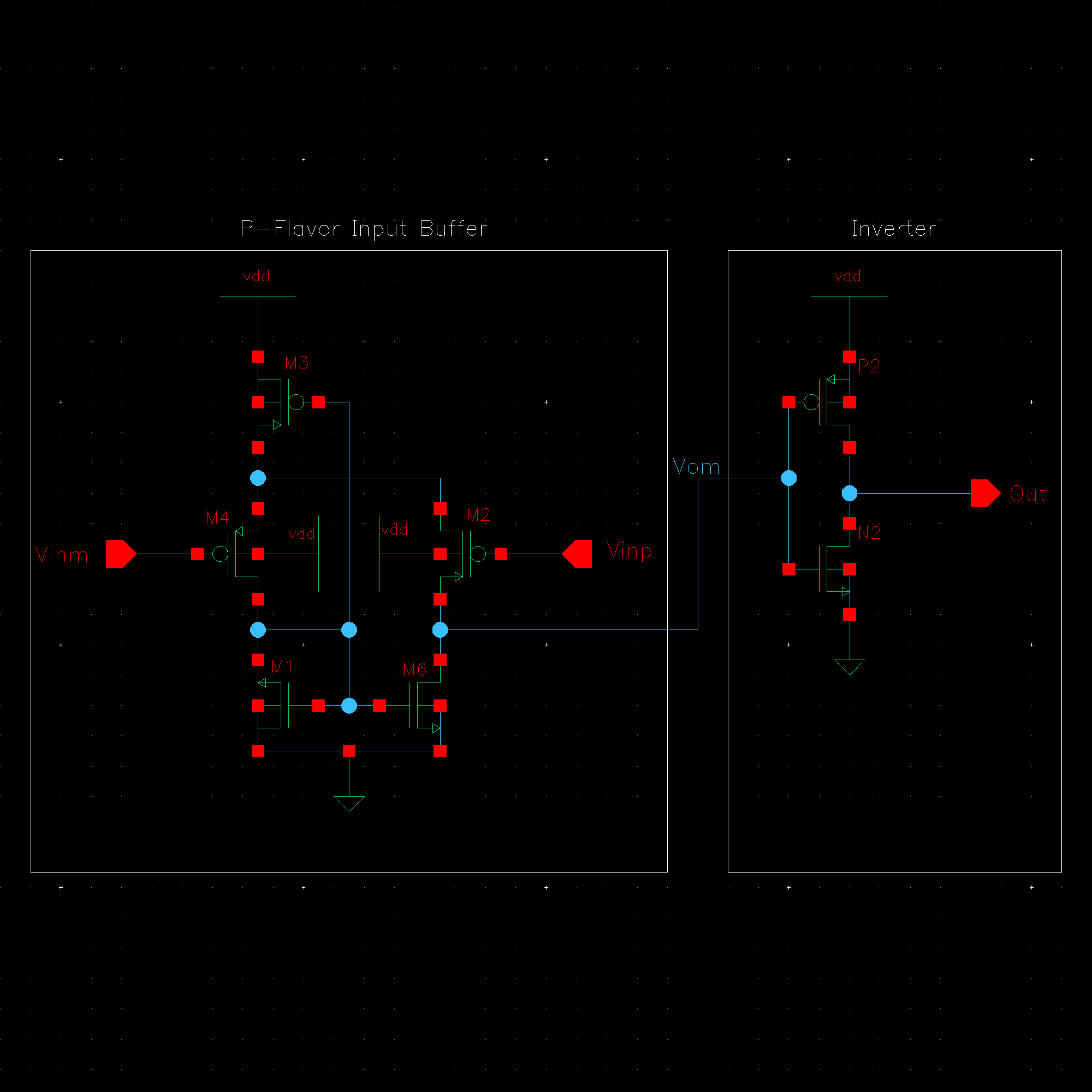

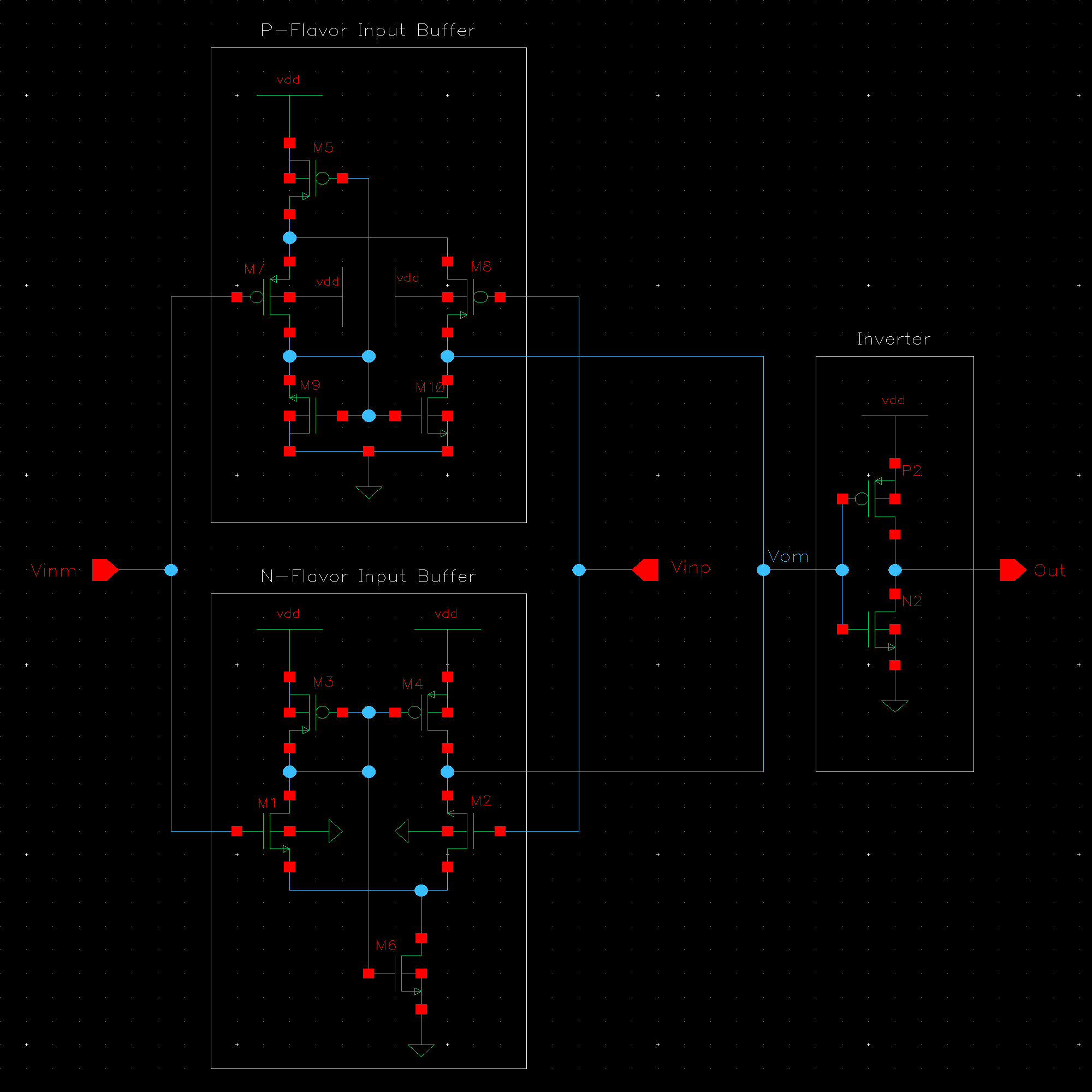

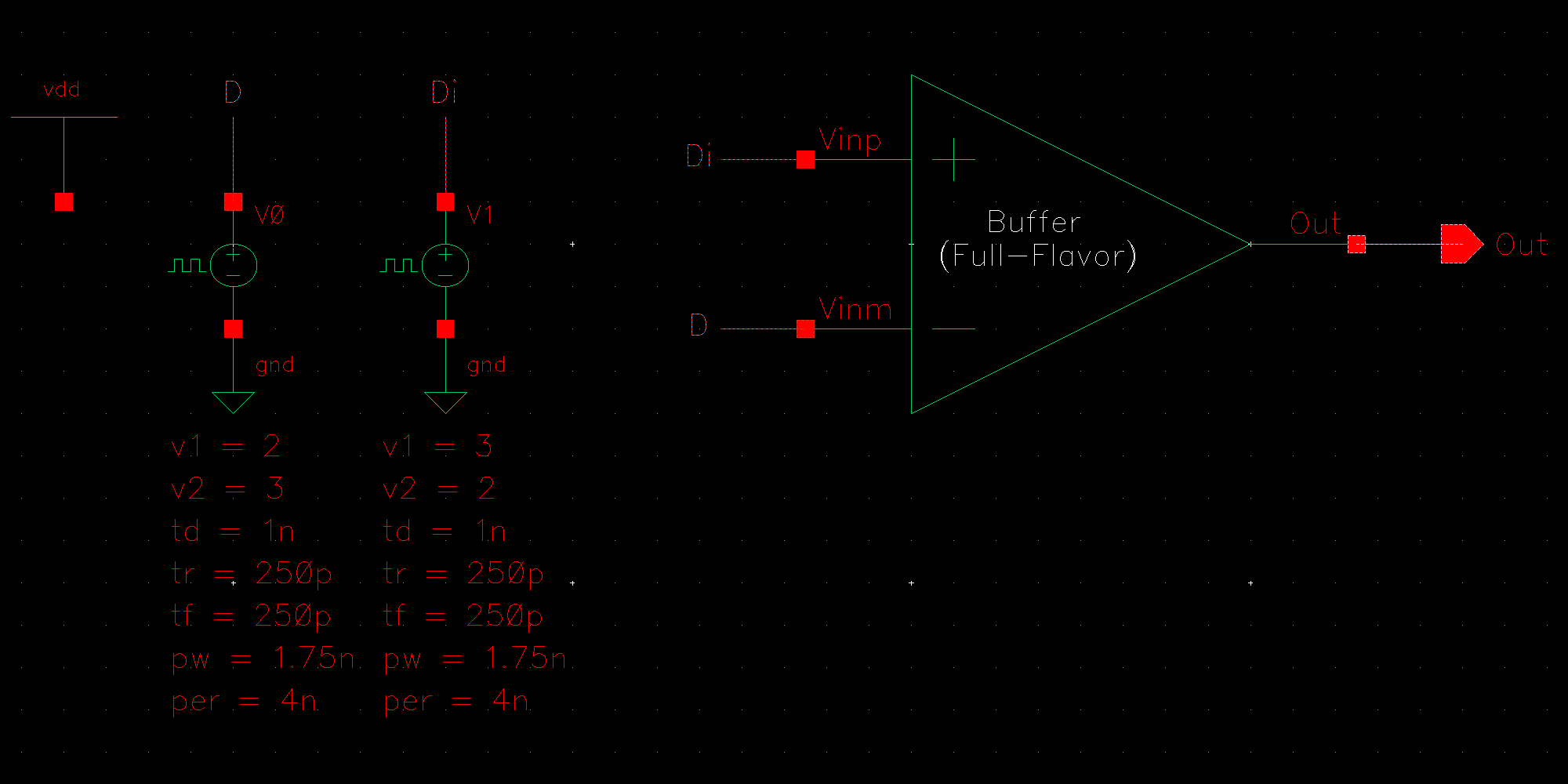

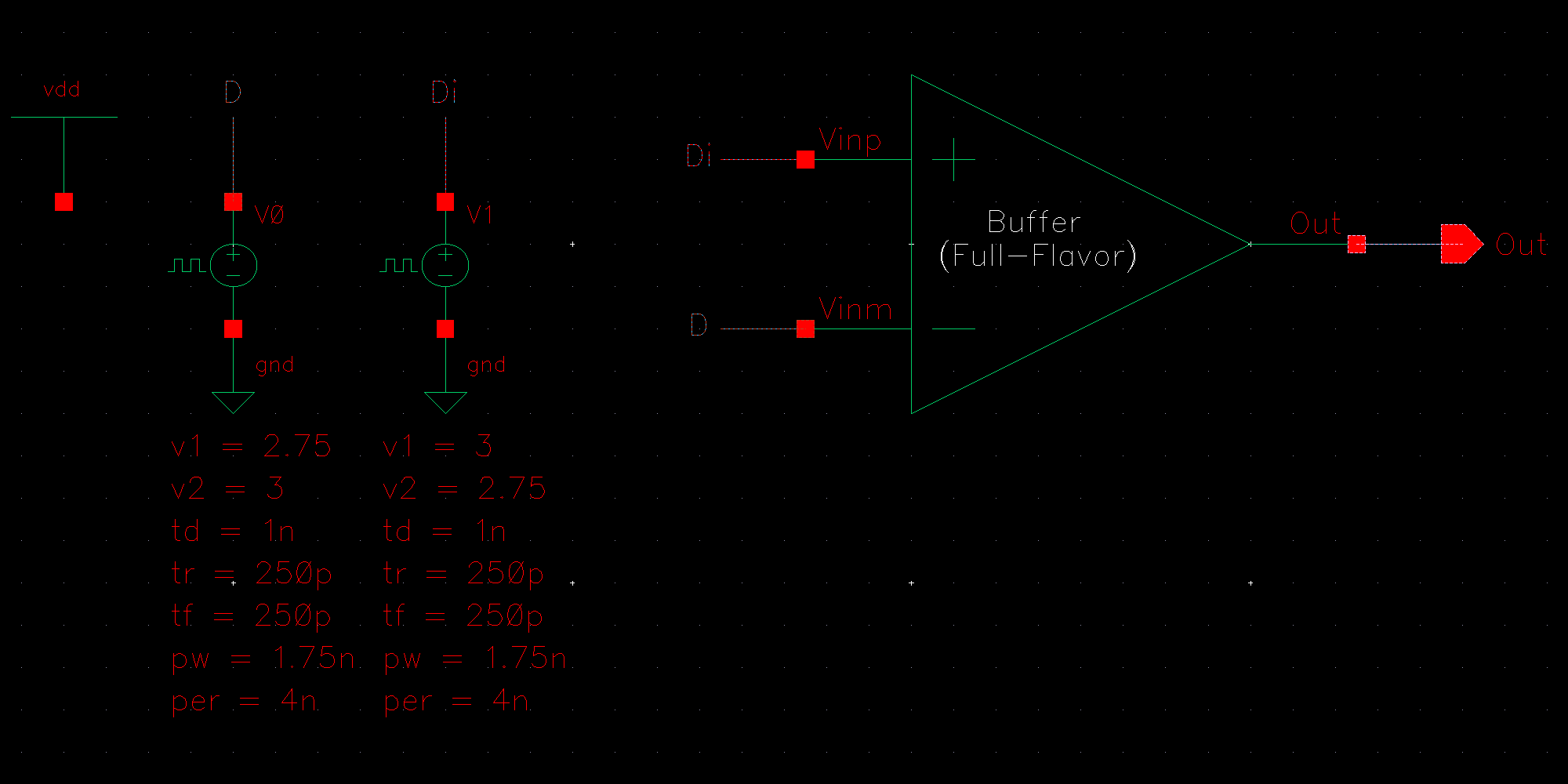

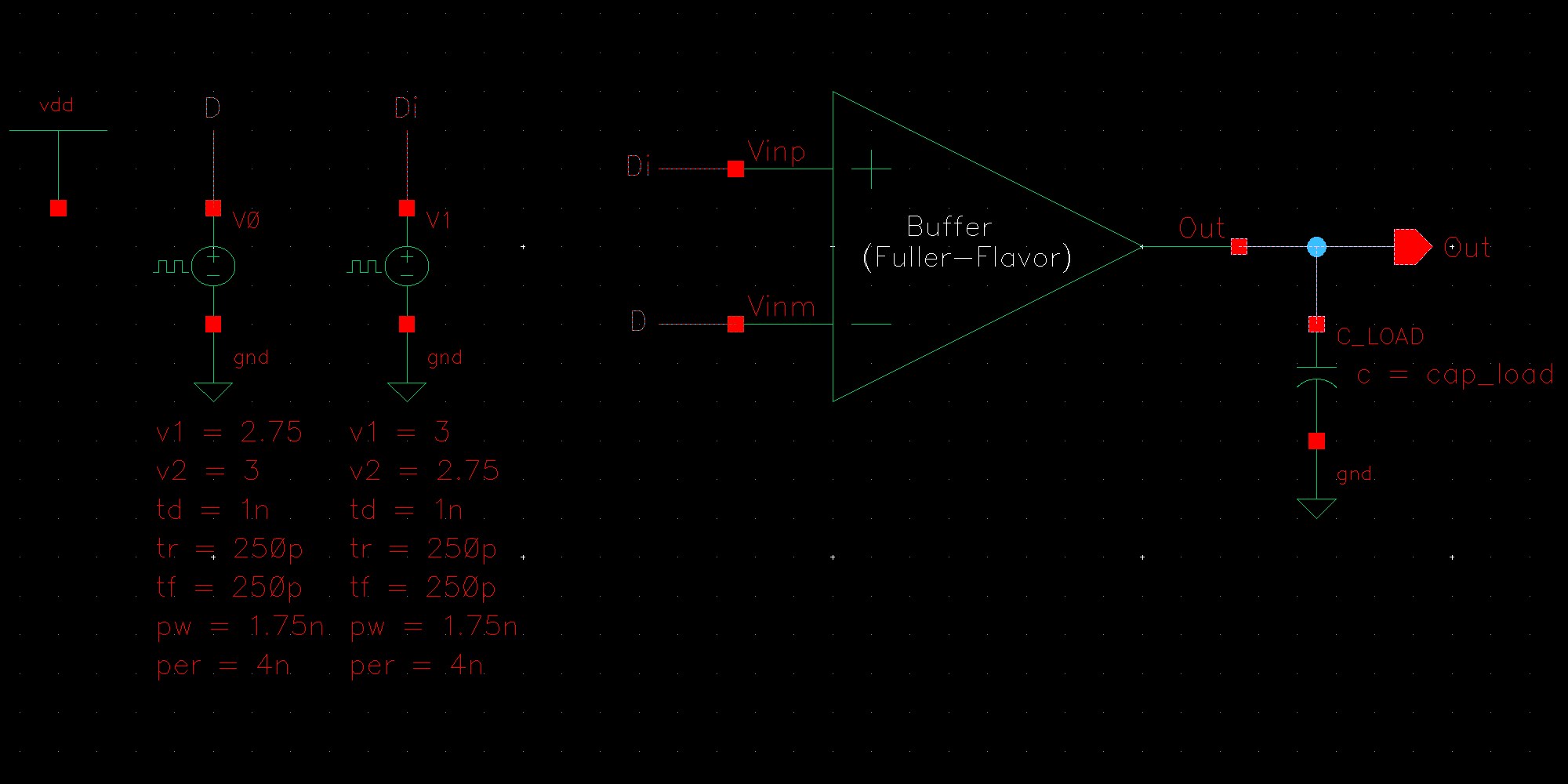

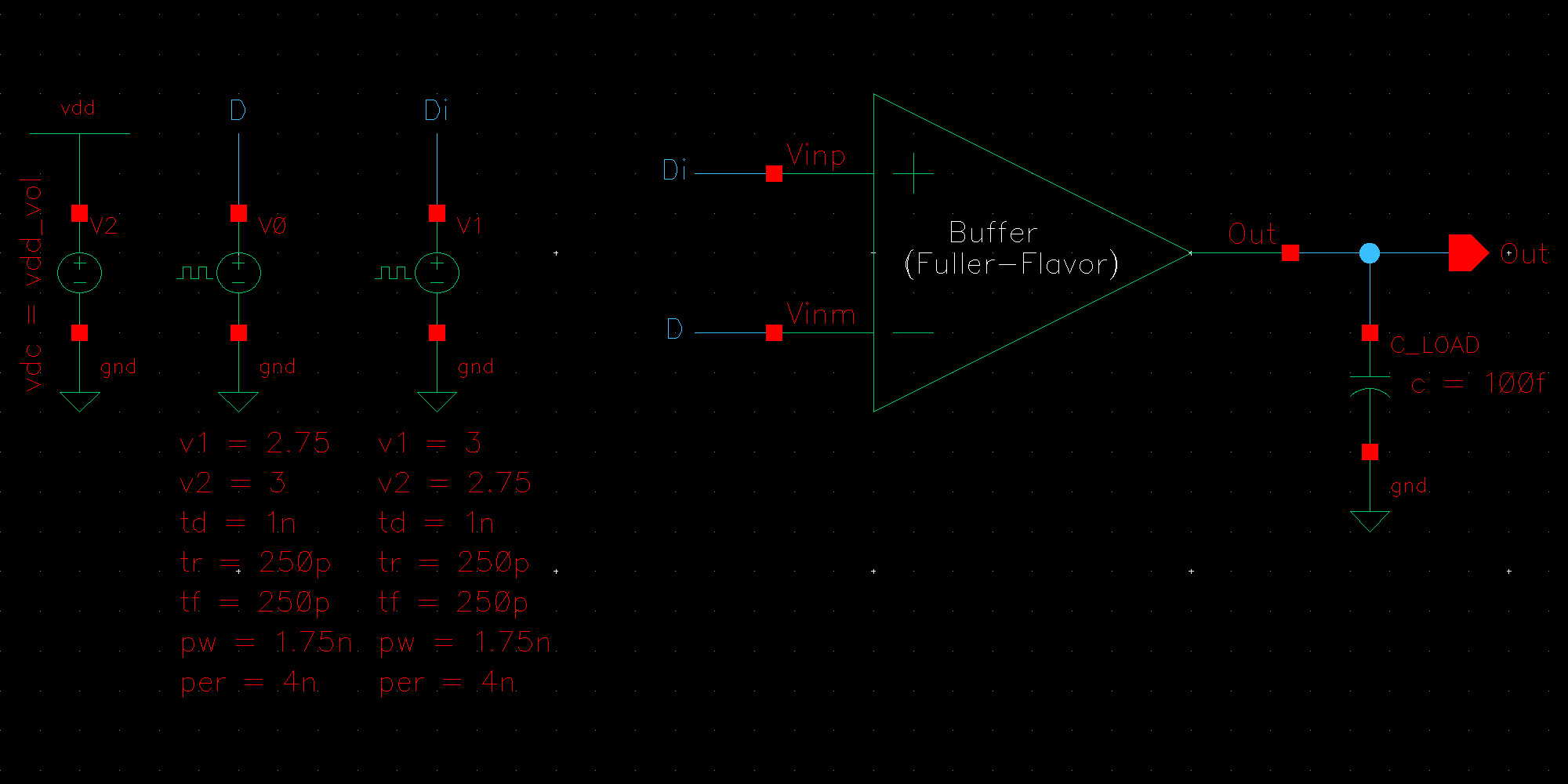

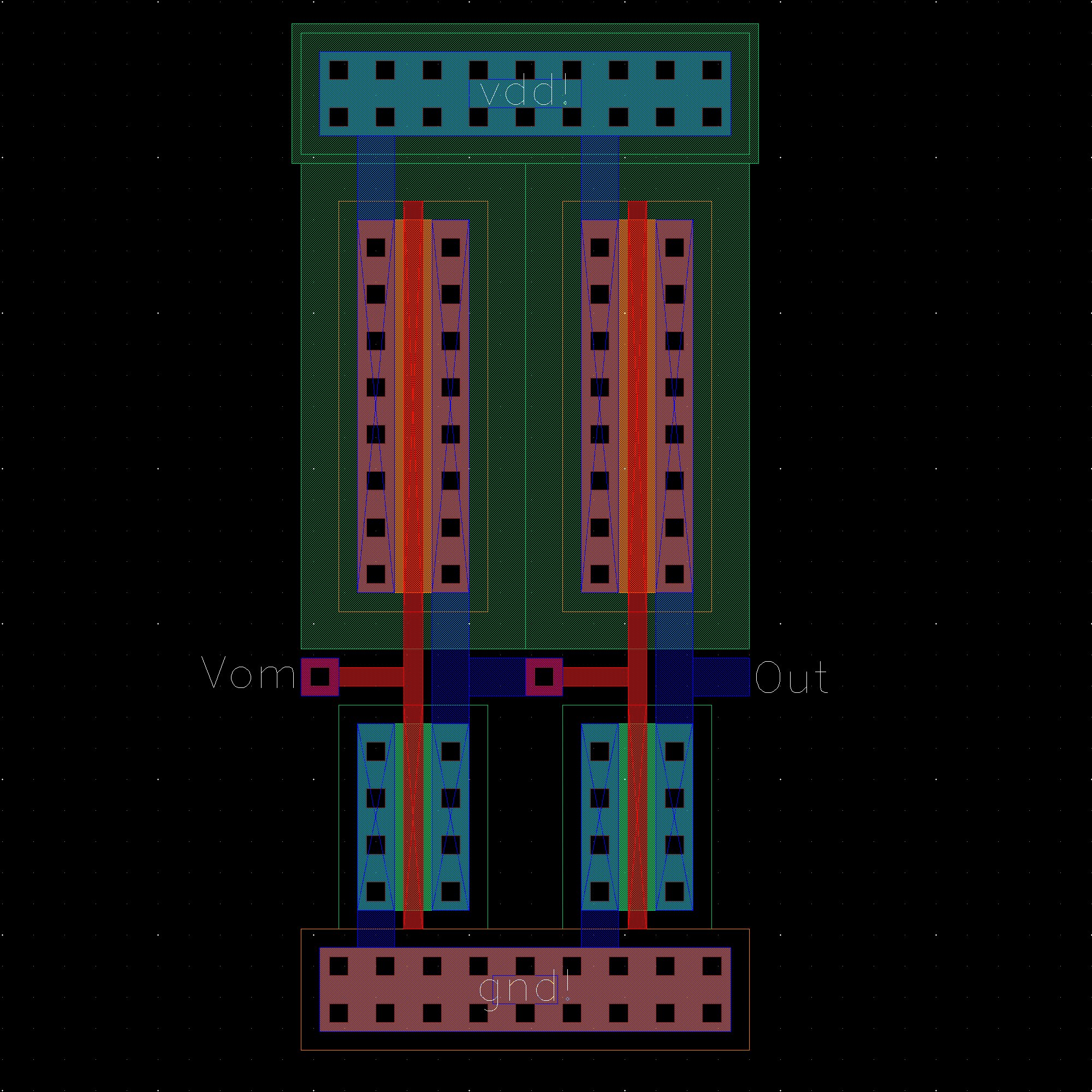

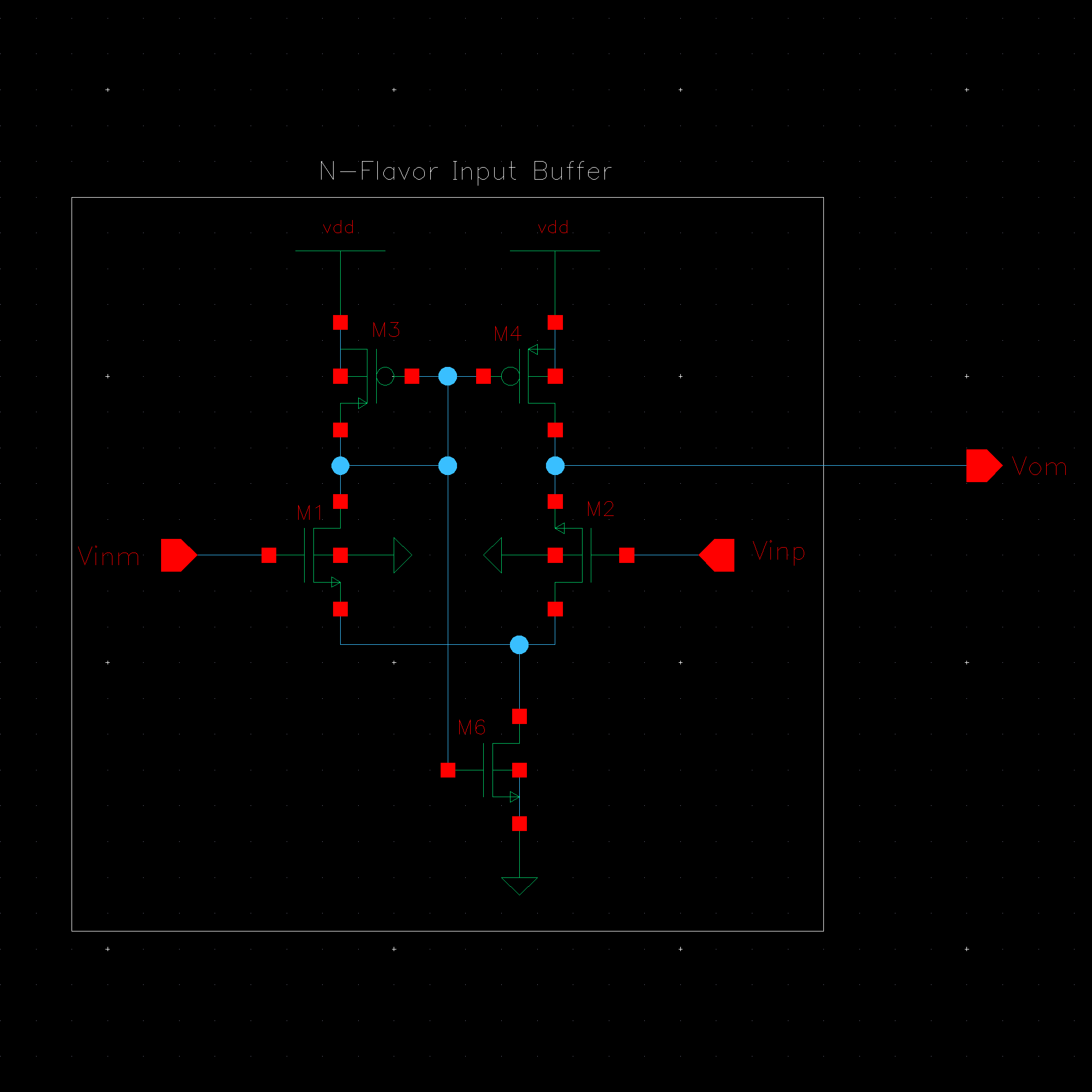

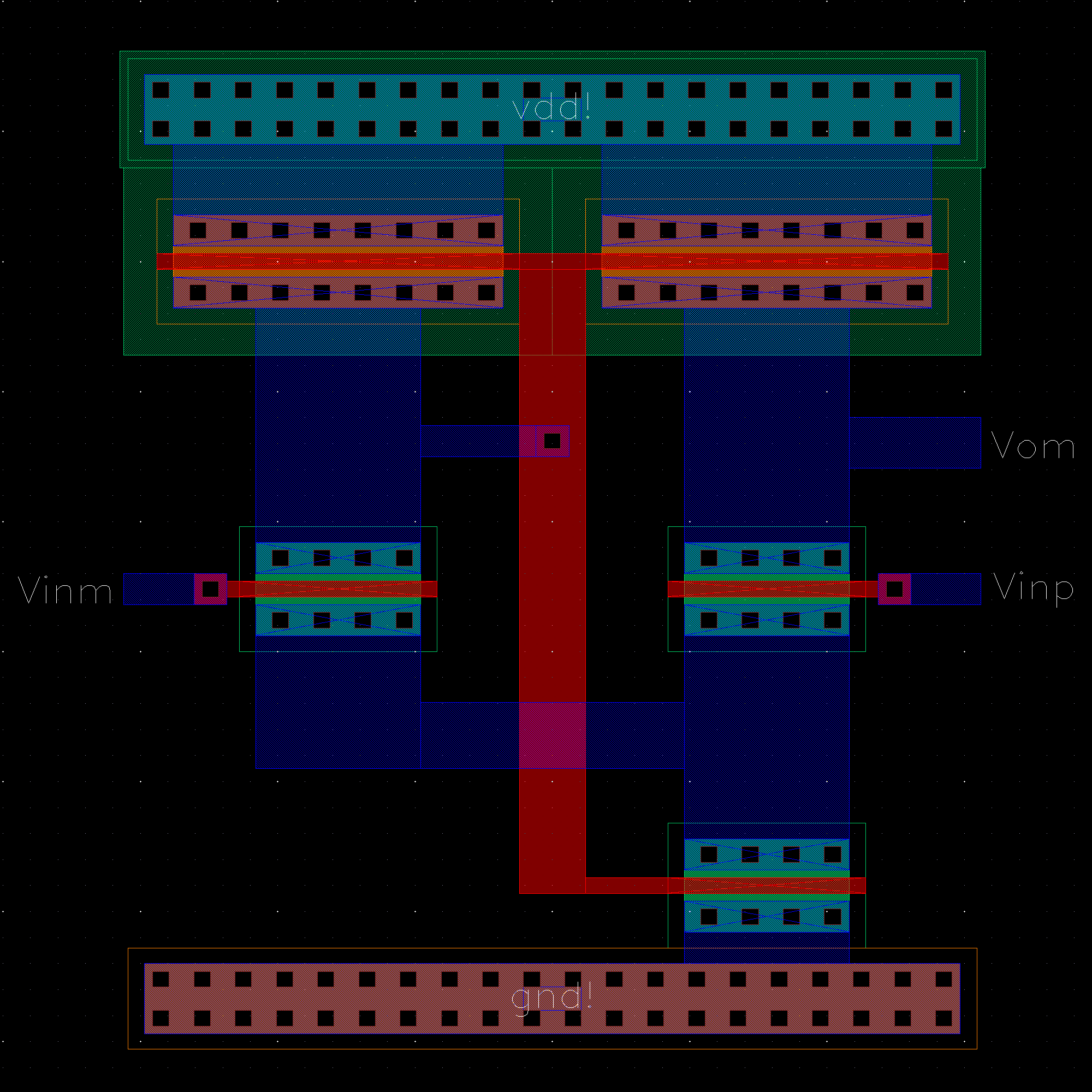

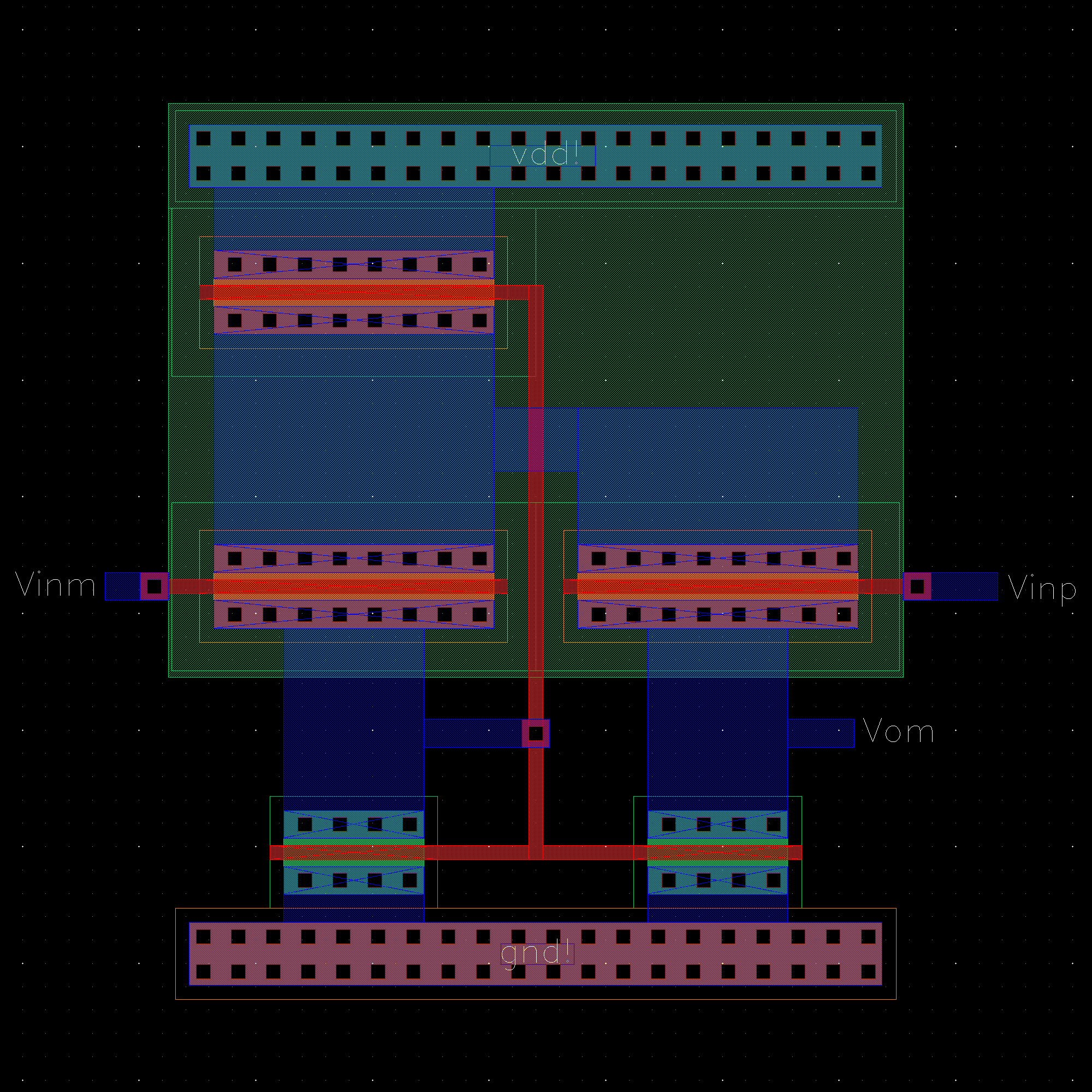

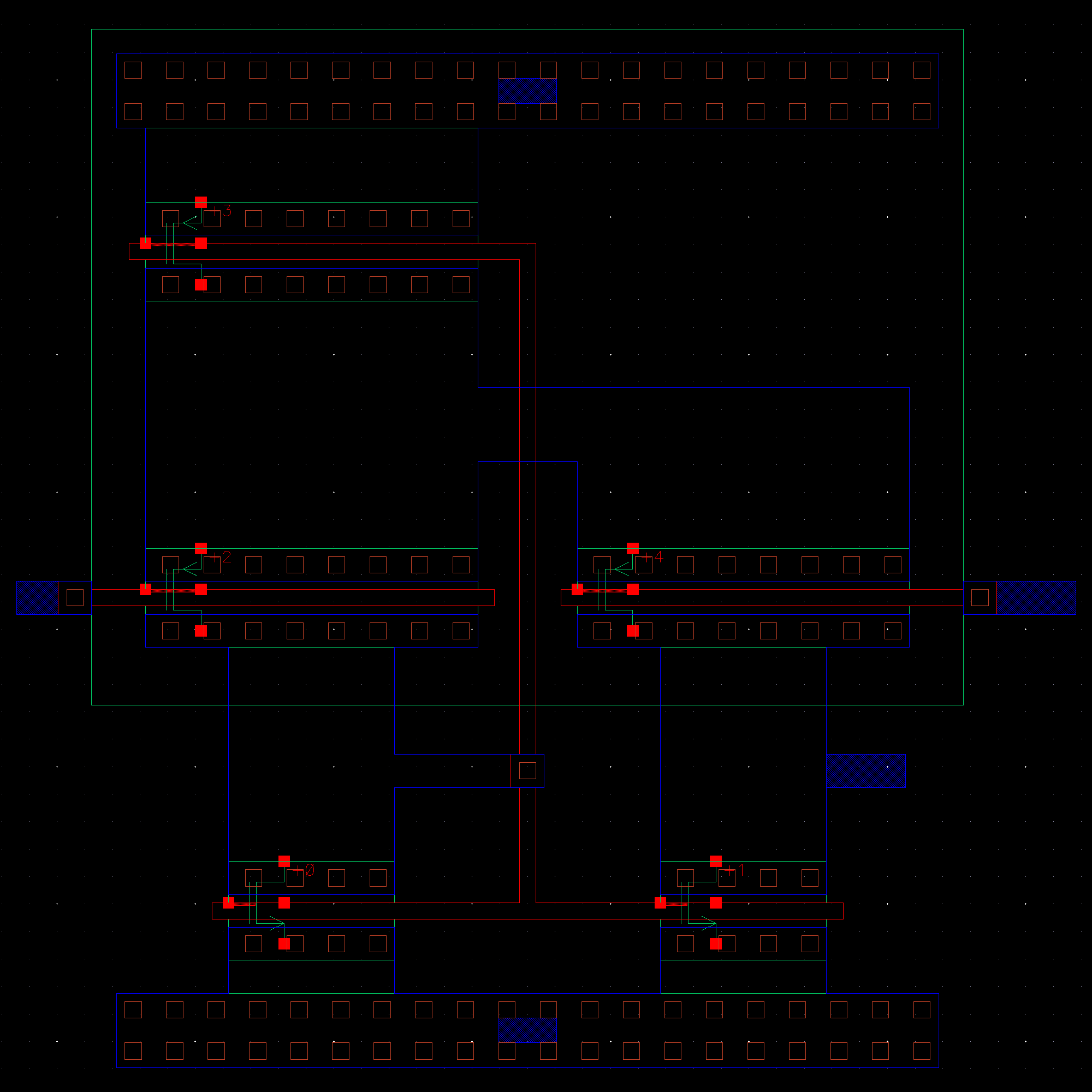

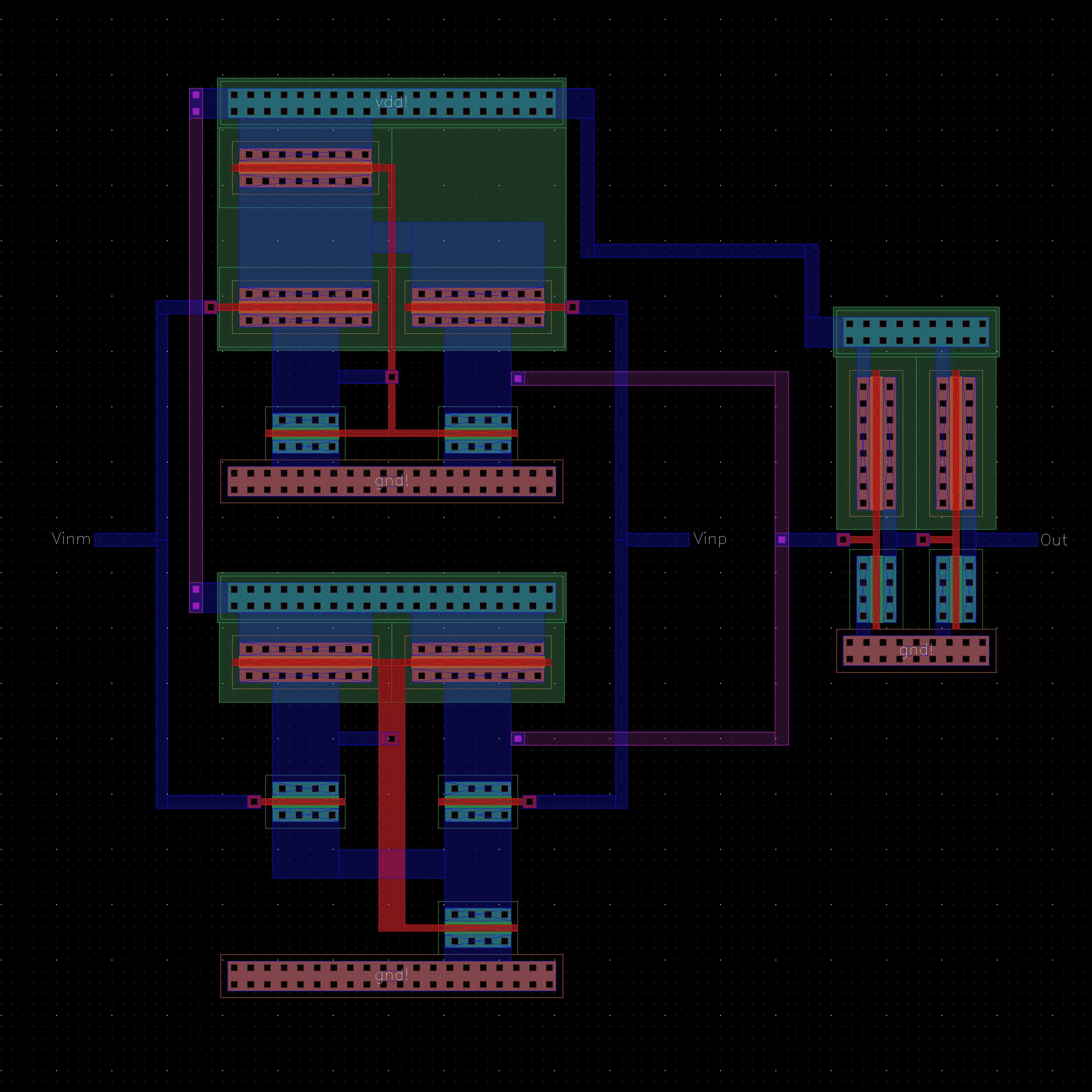

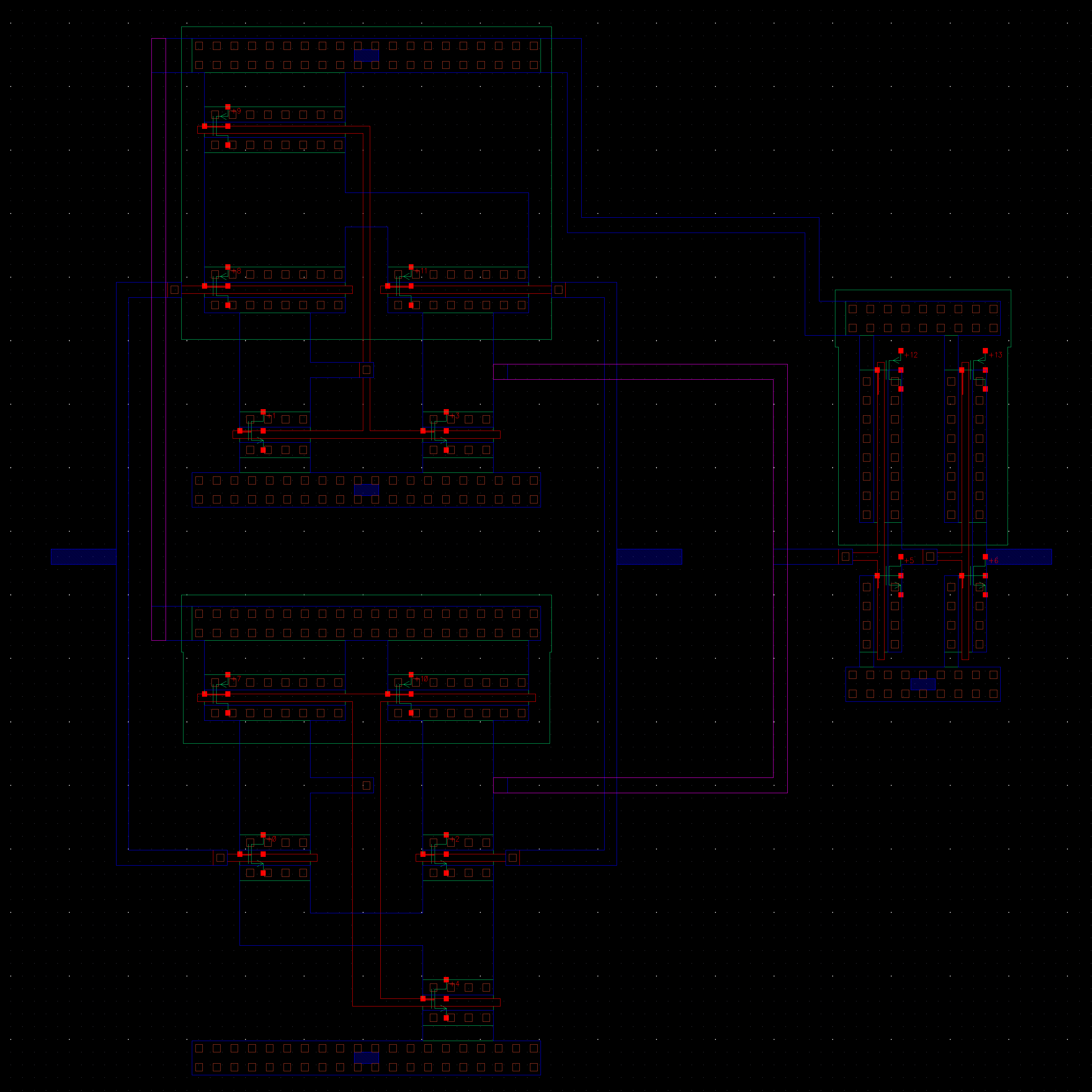

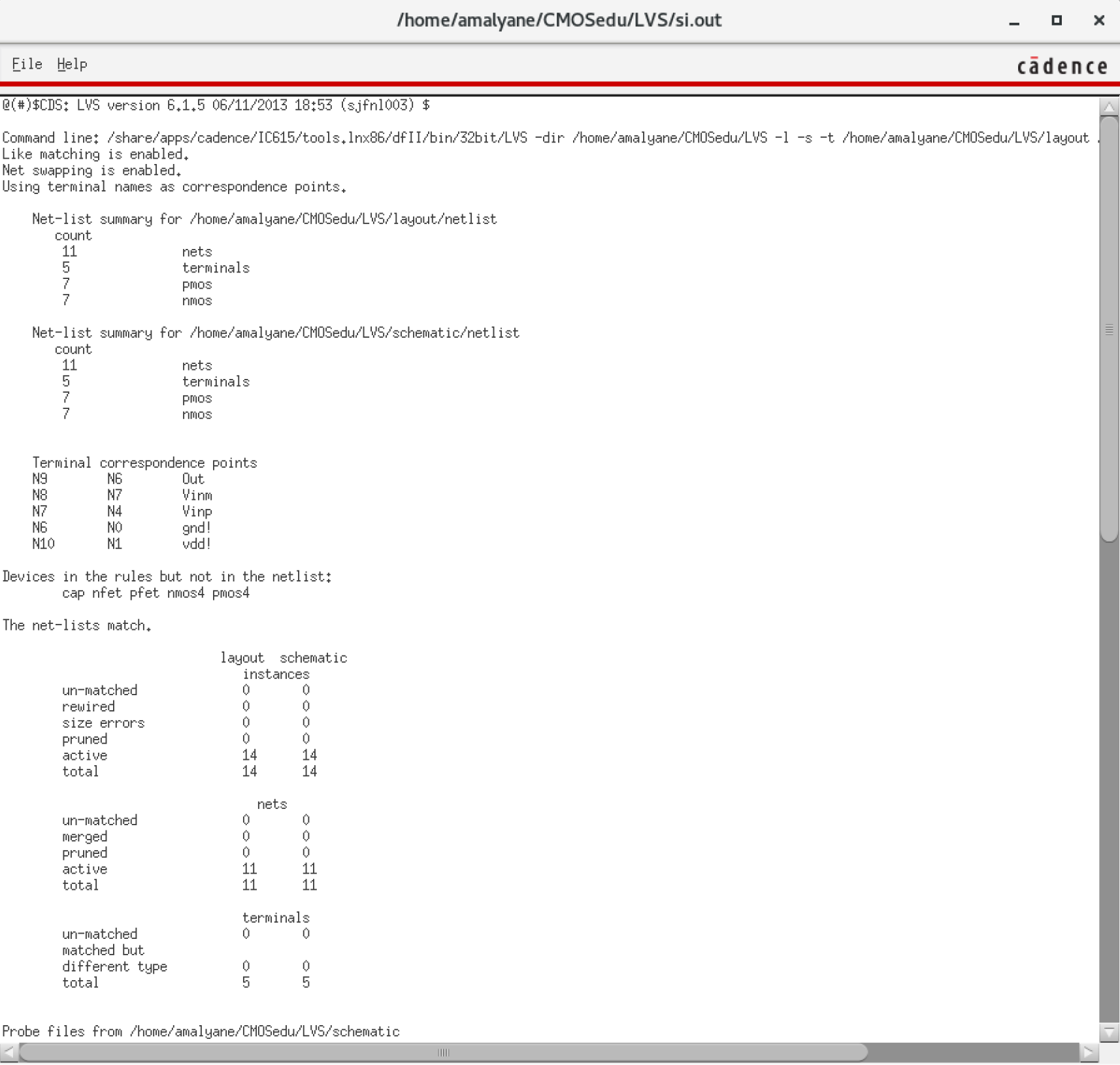

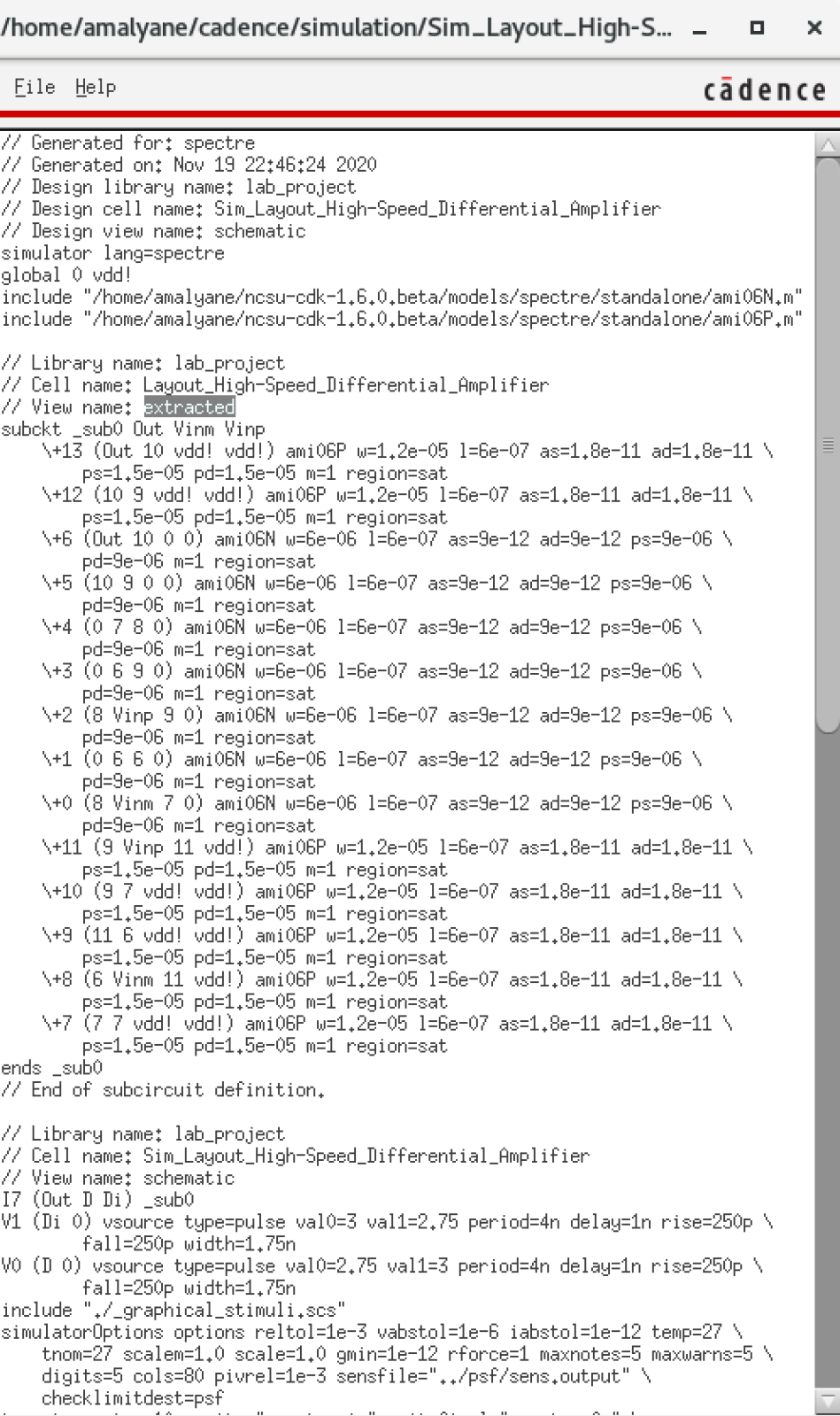

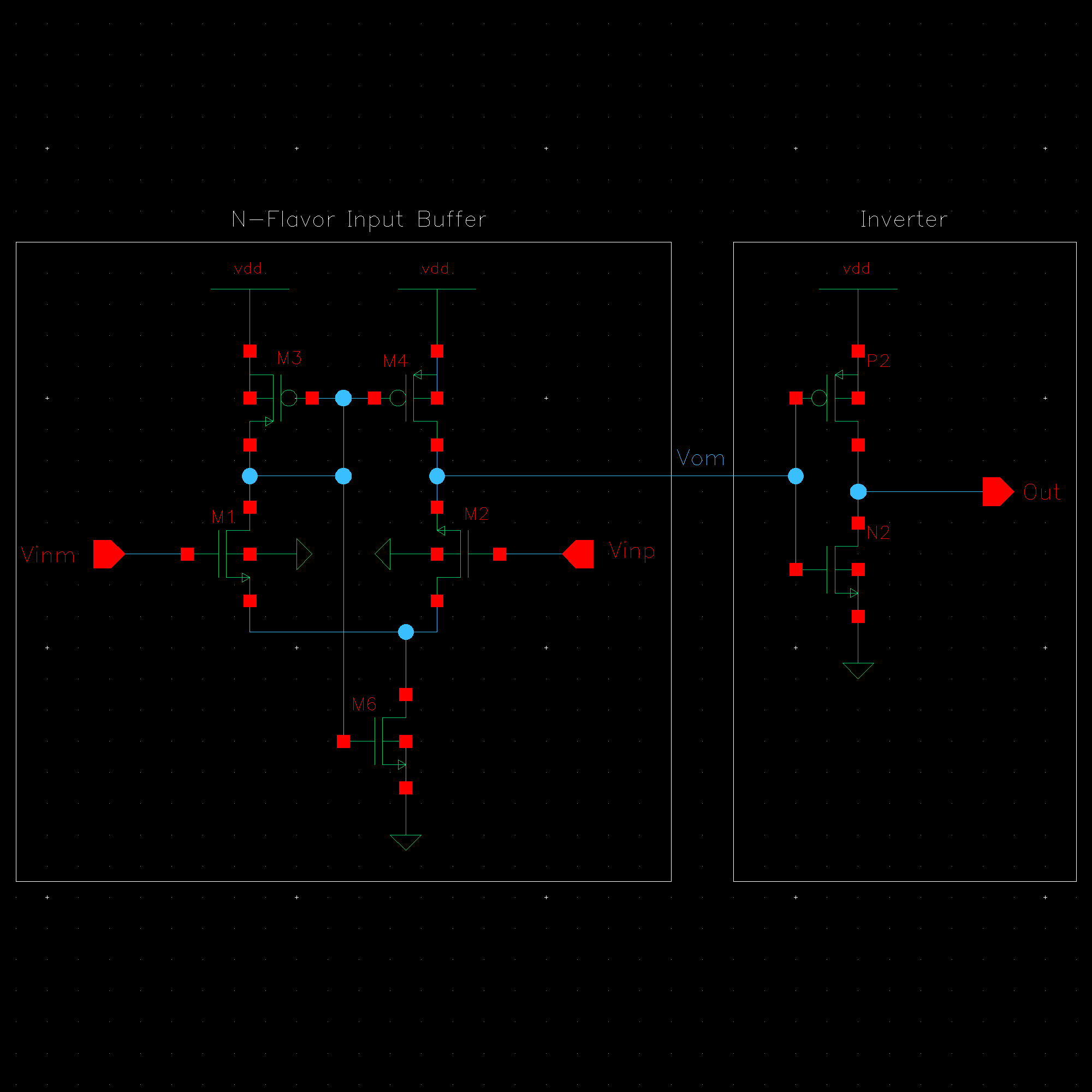

NMOS are 6u/0.6u and PMOS are 12u/0.6u.

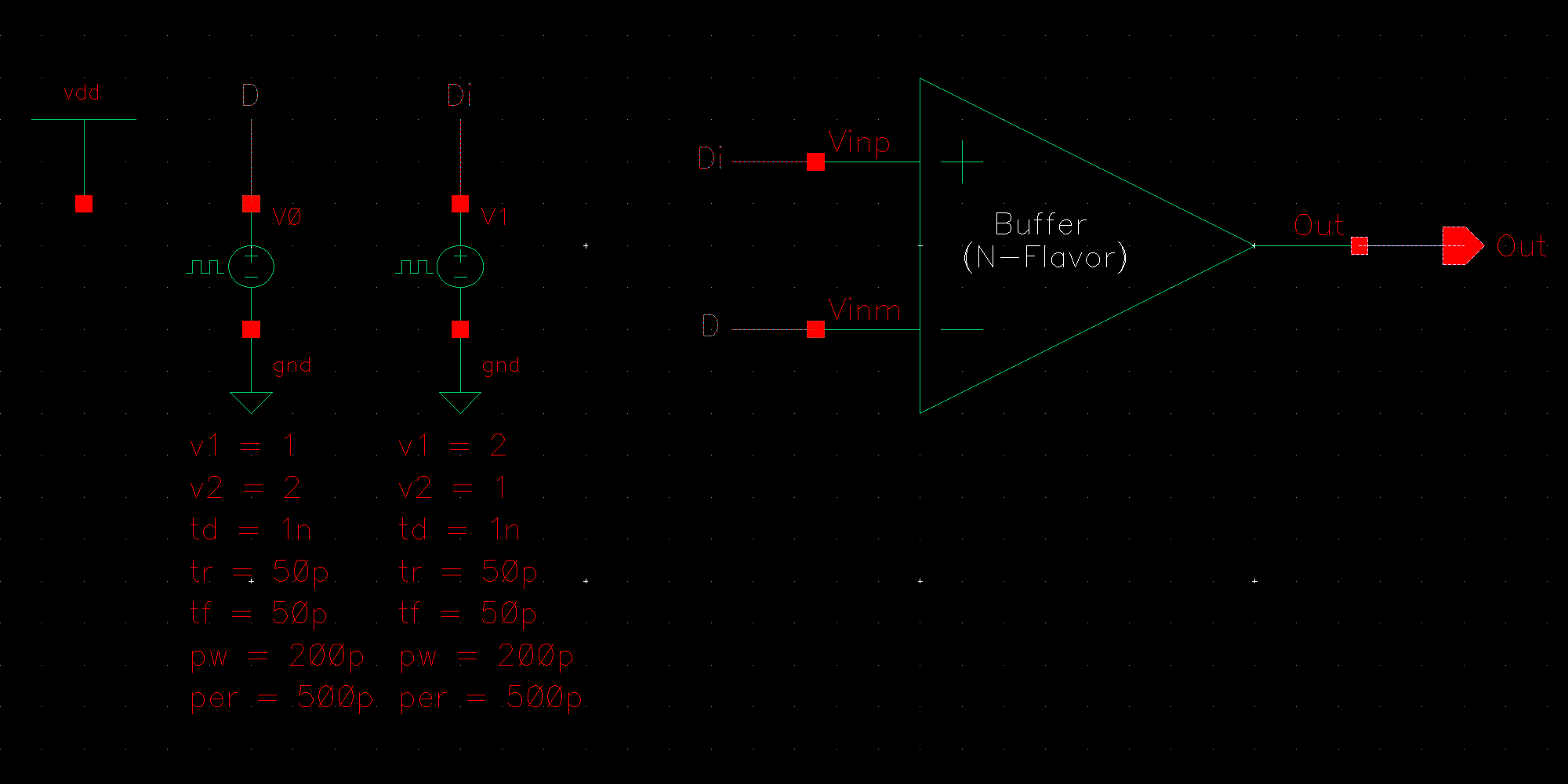

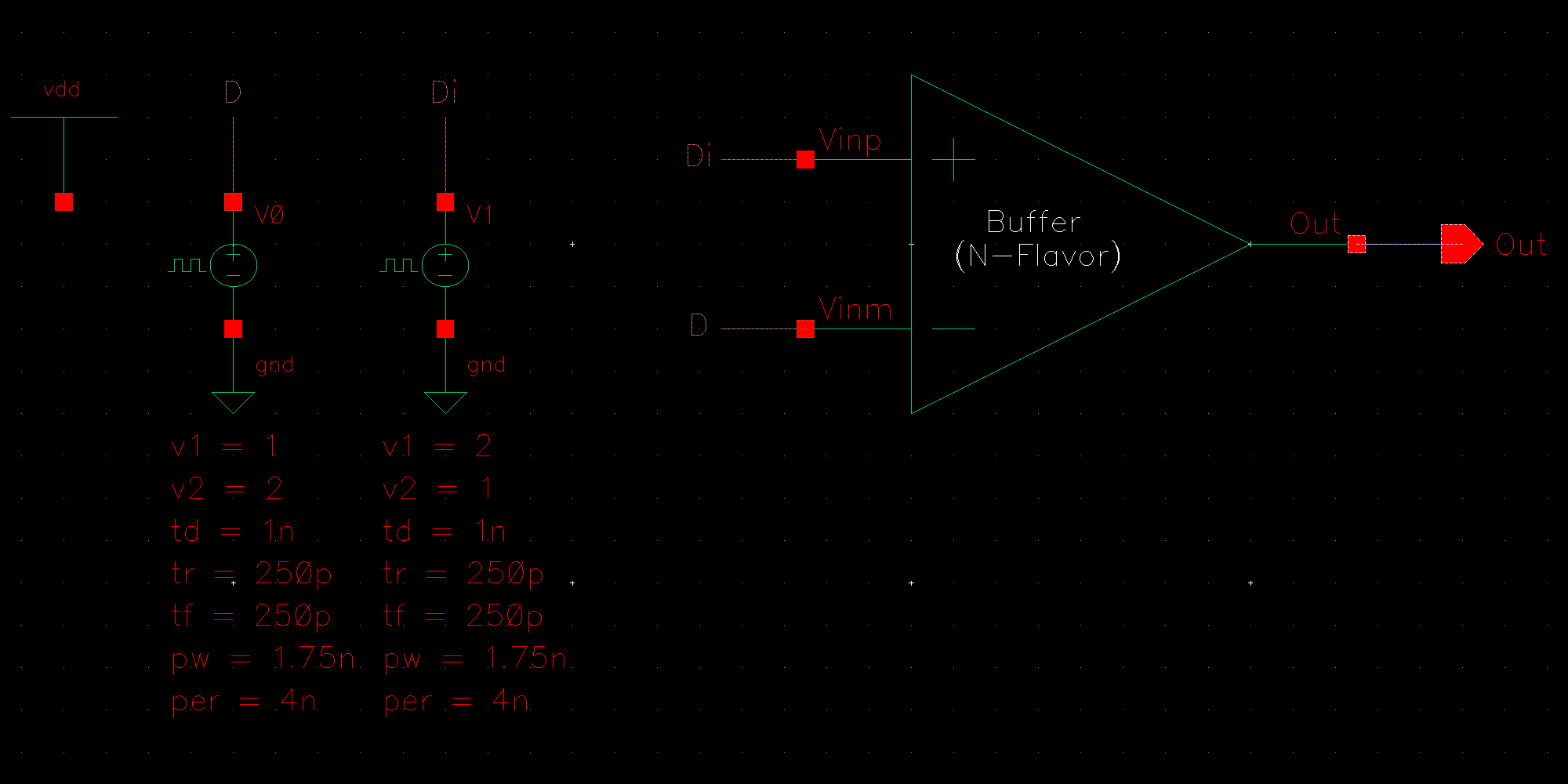

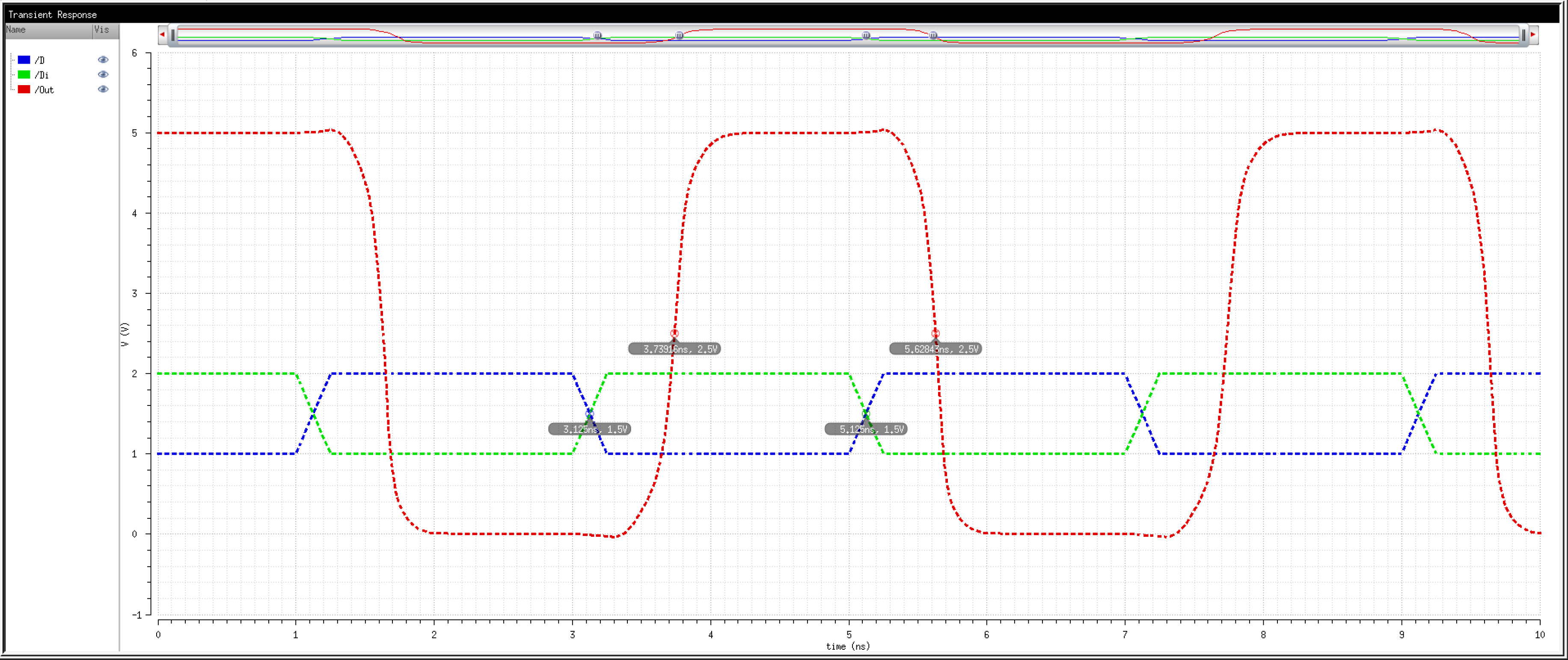

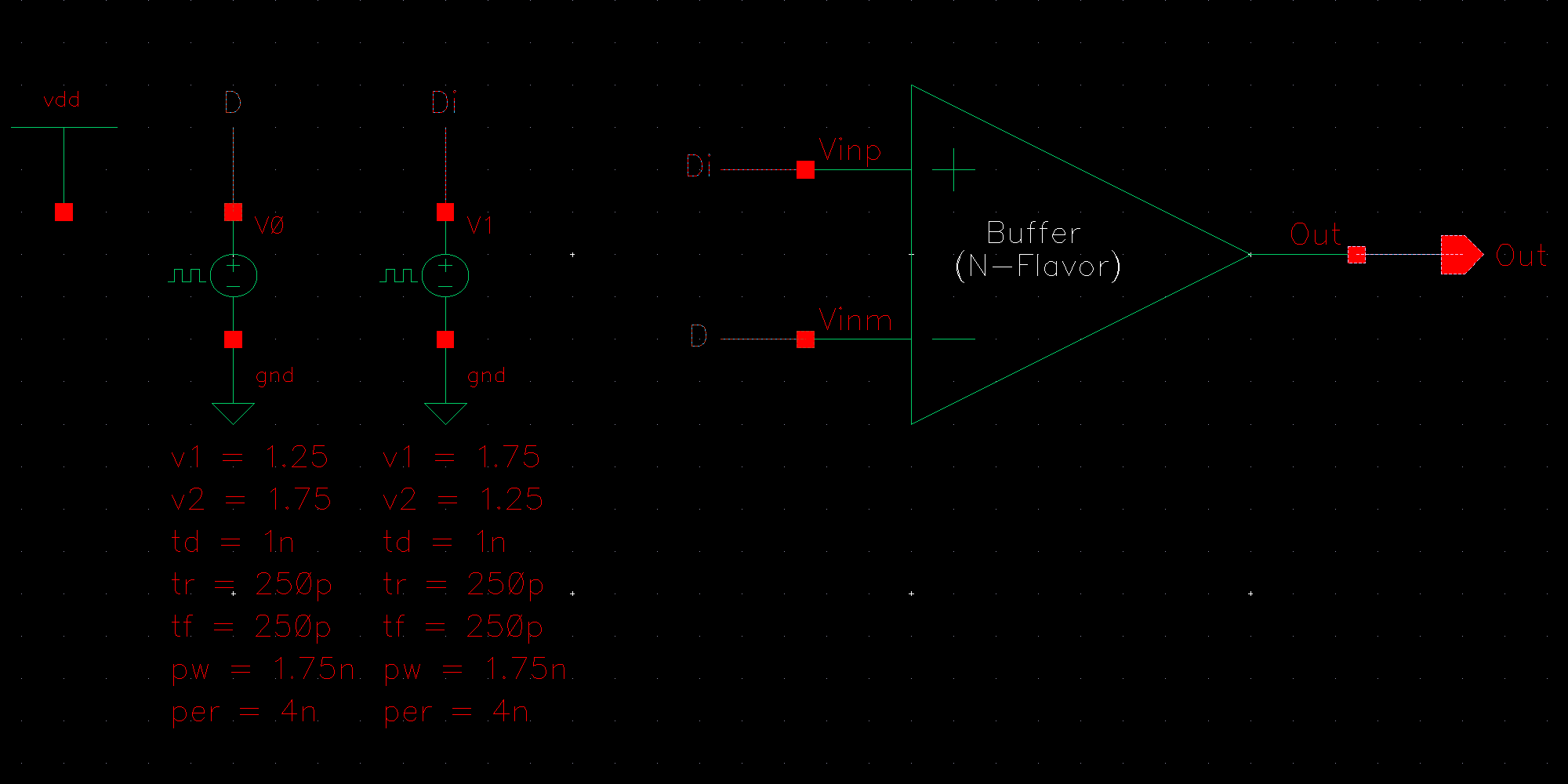

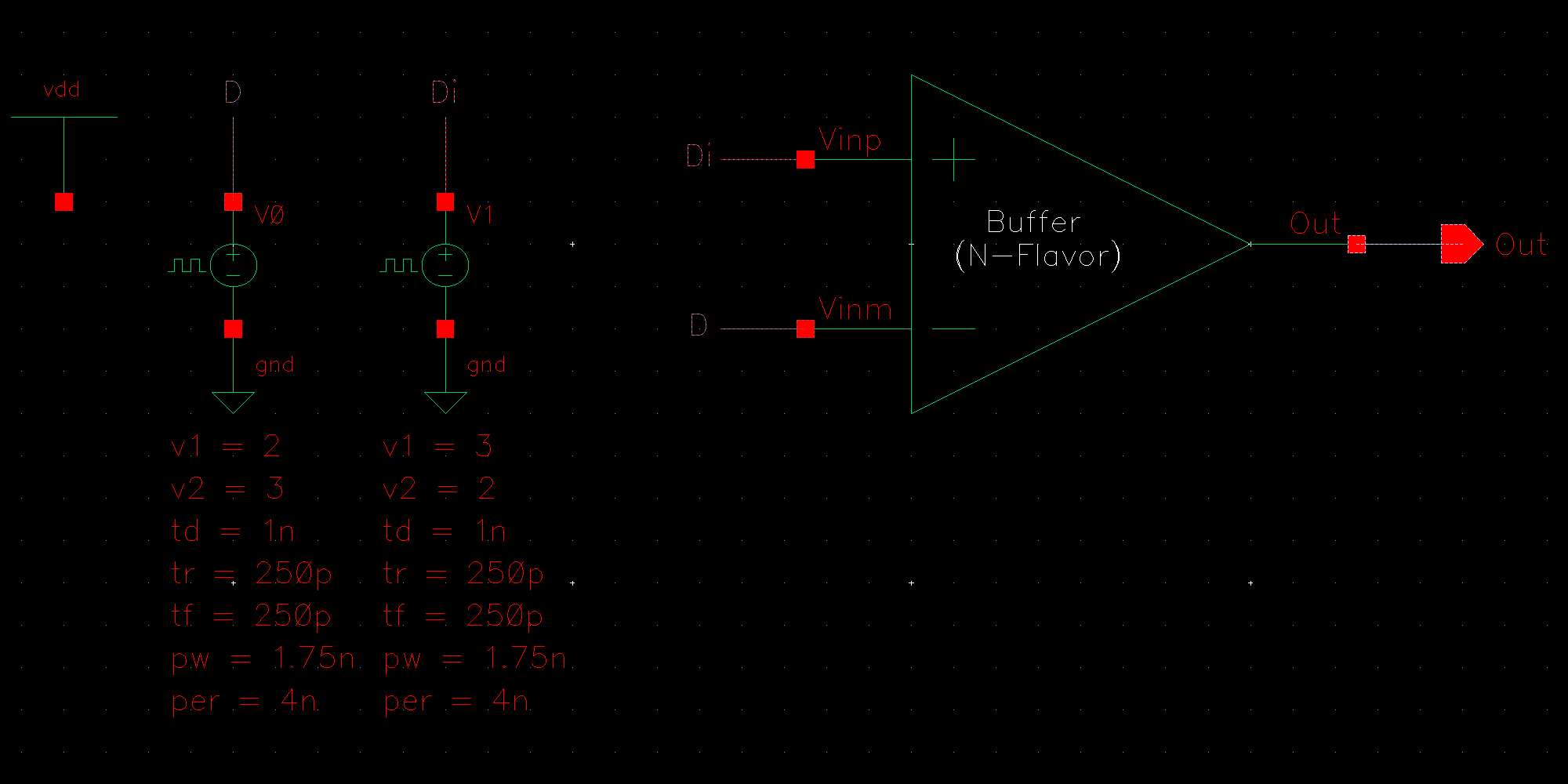

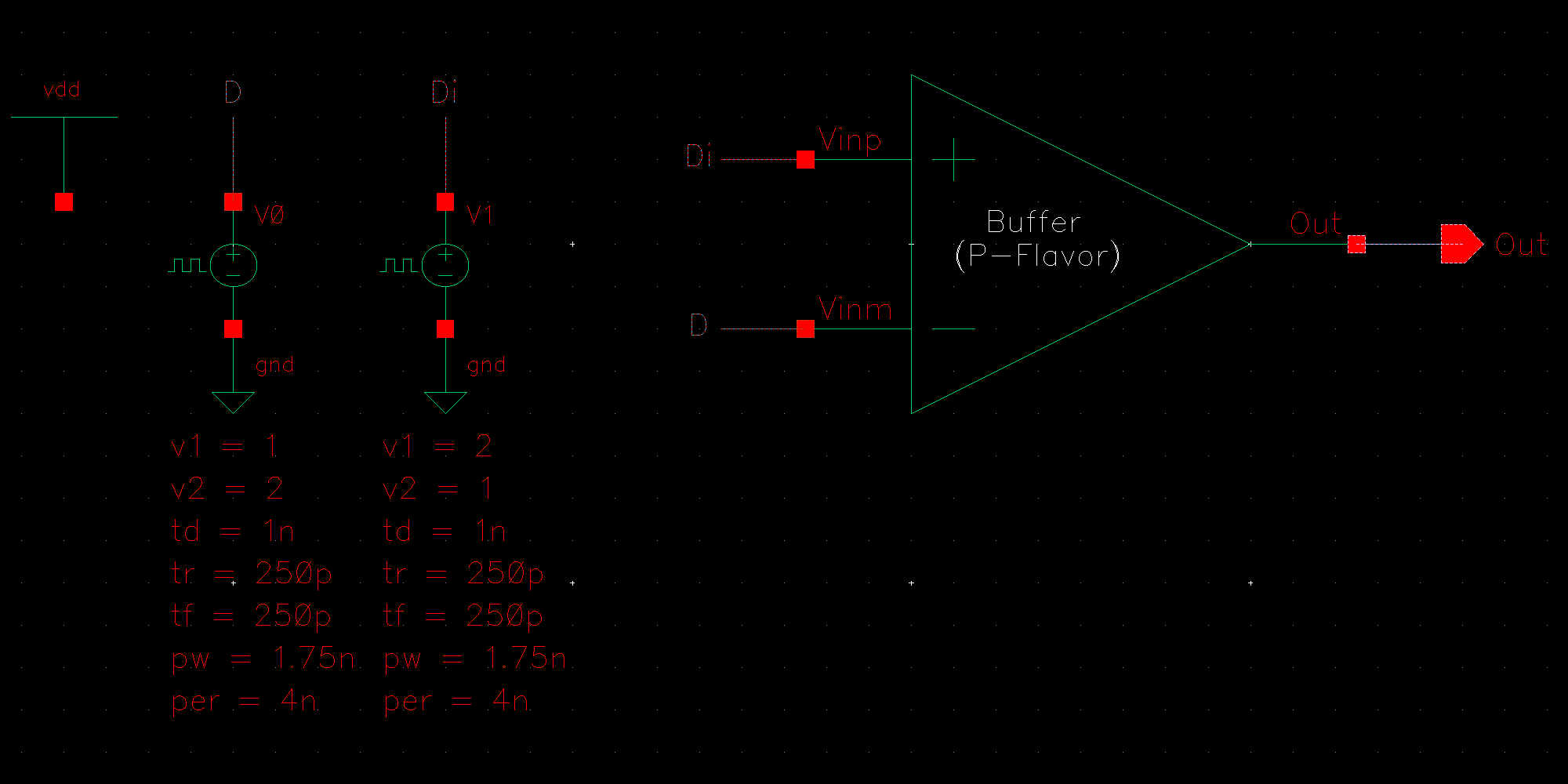

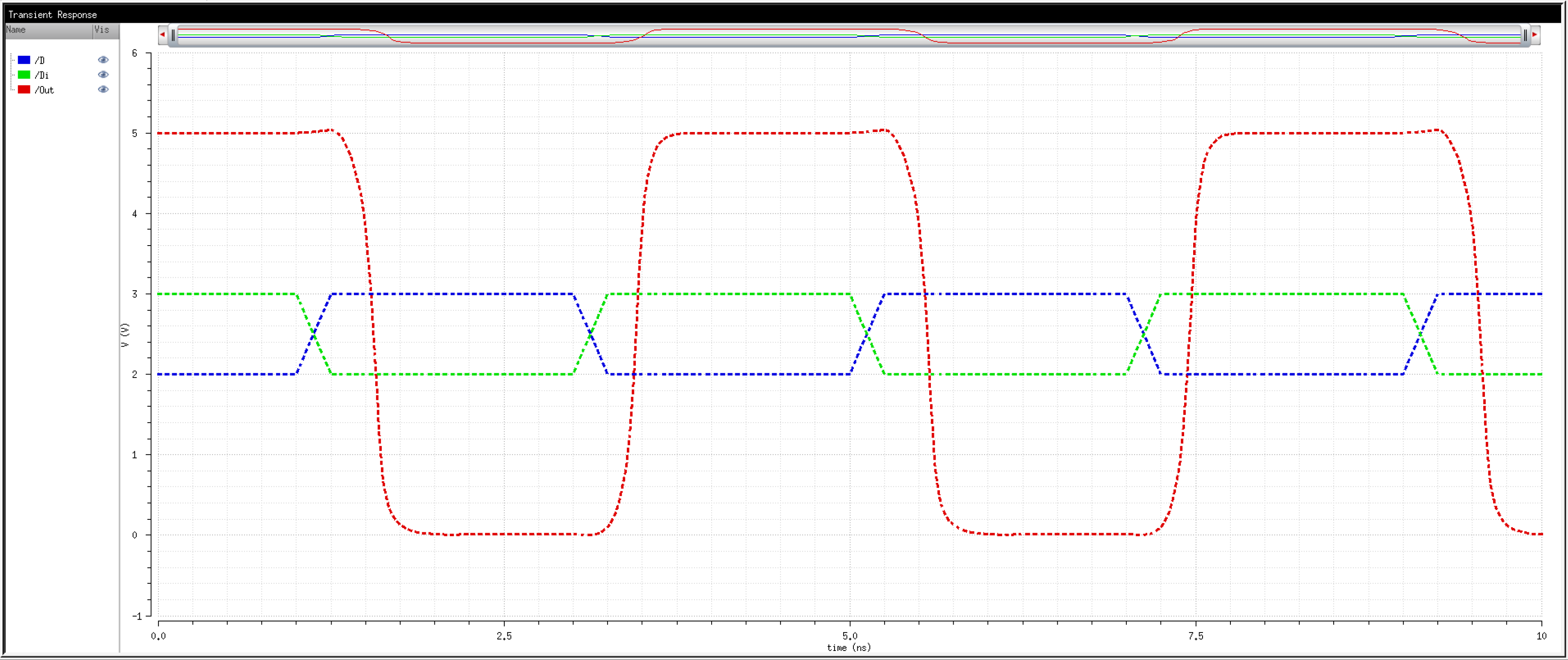

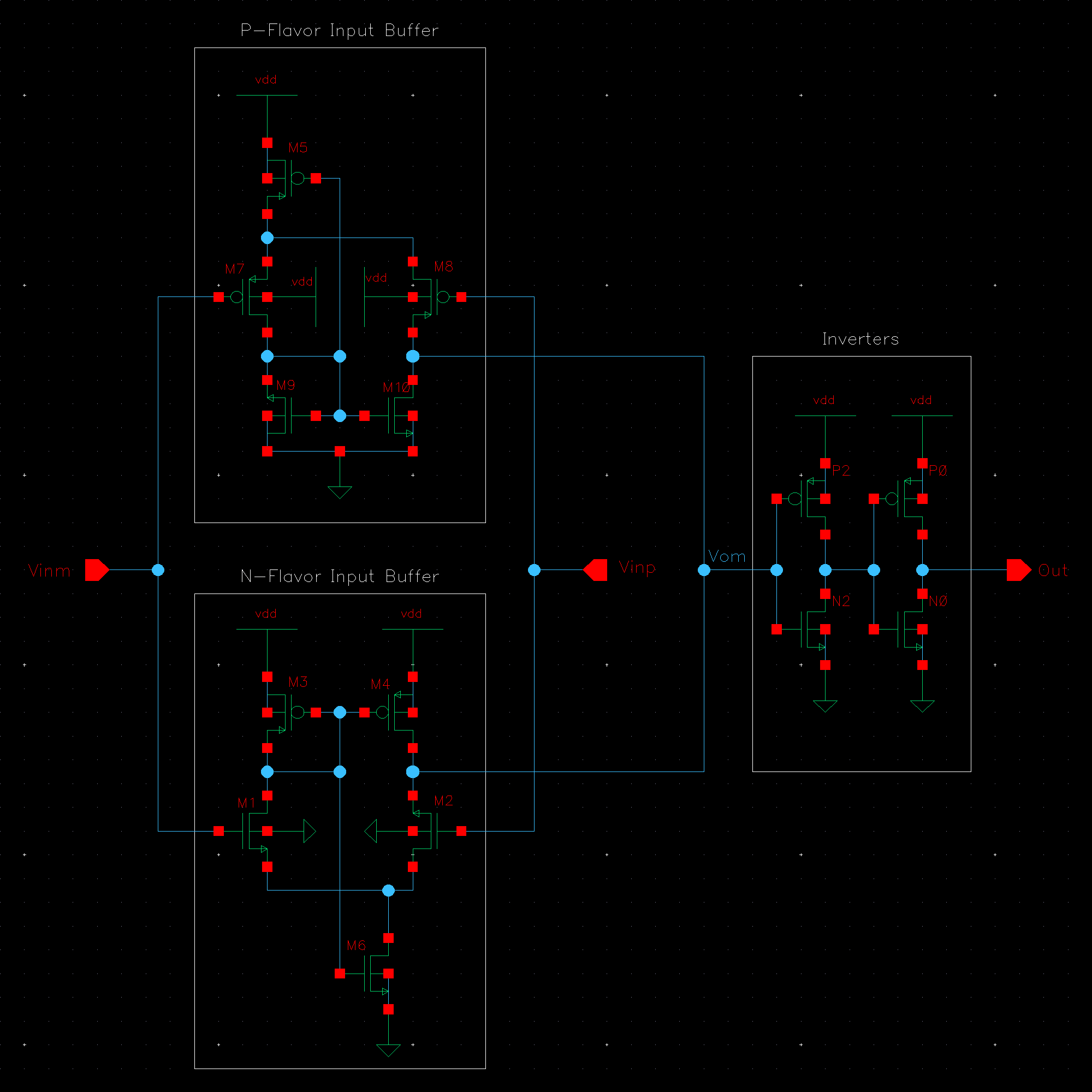

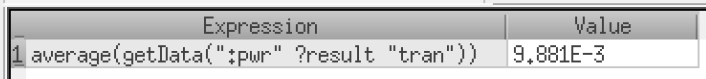

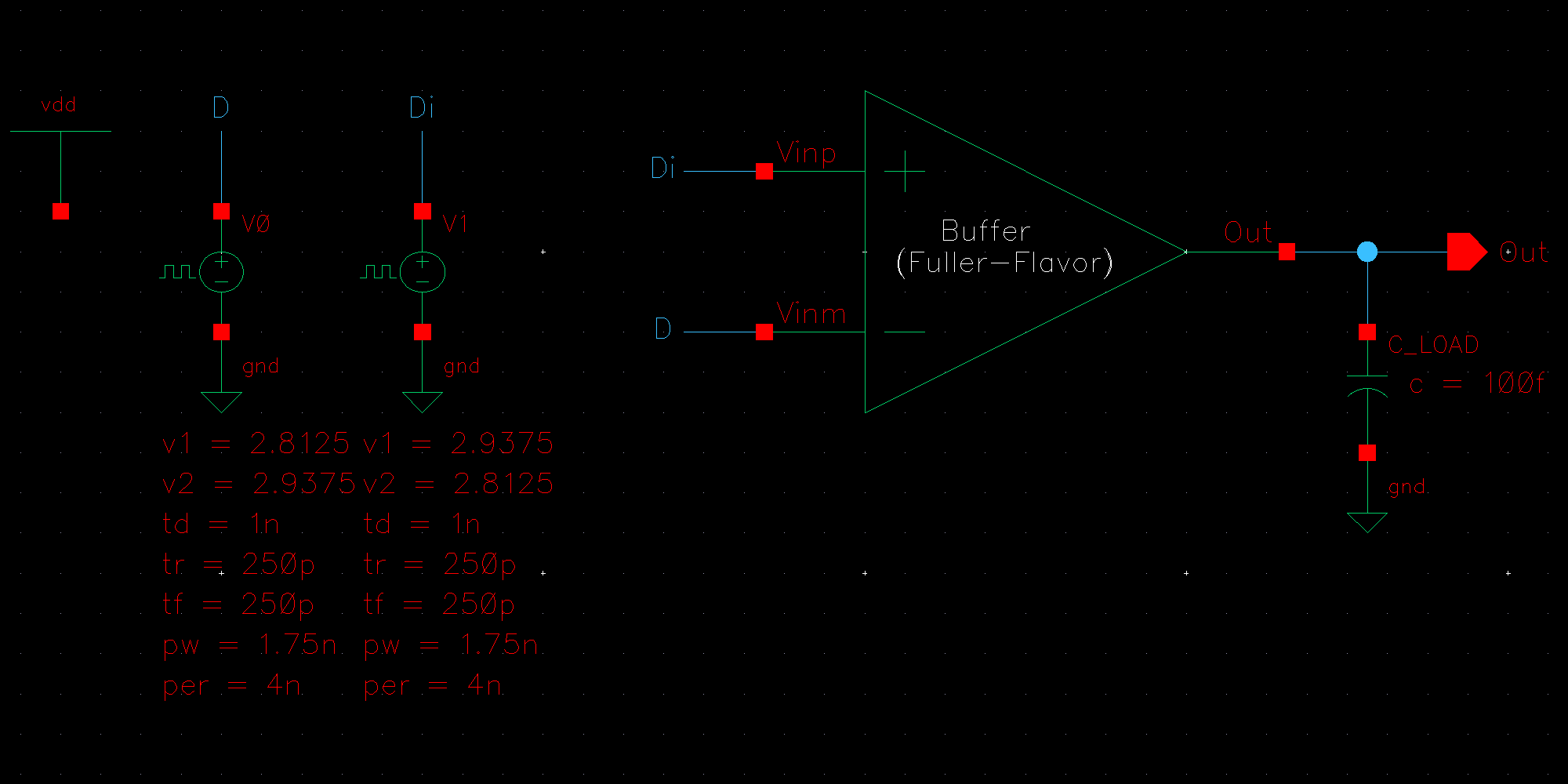

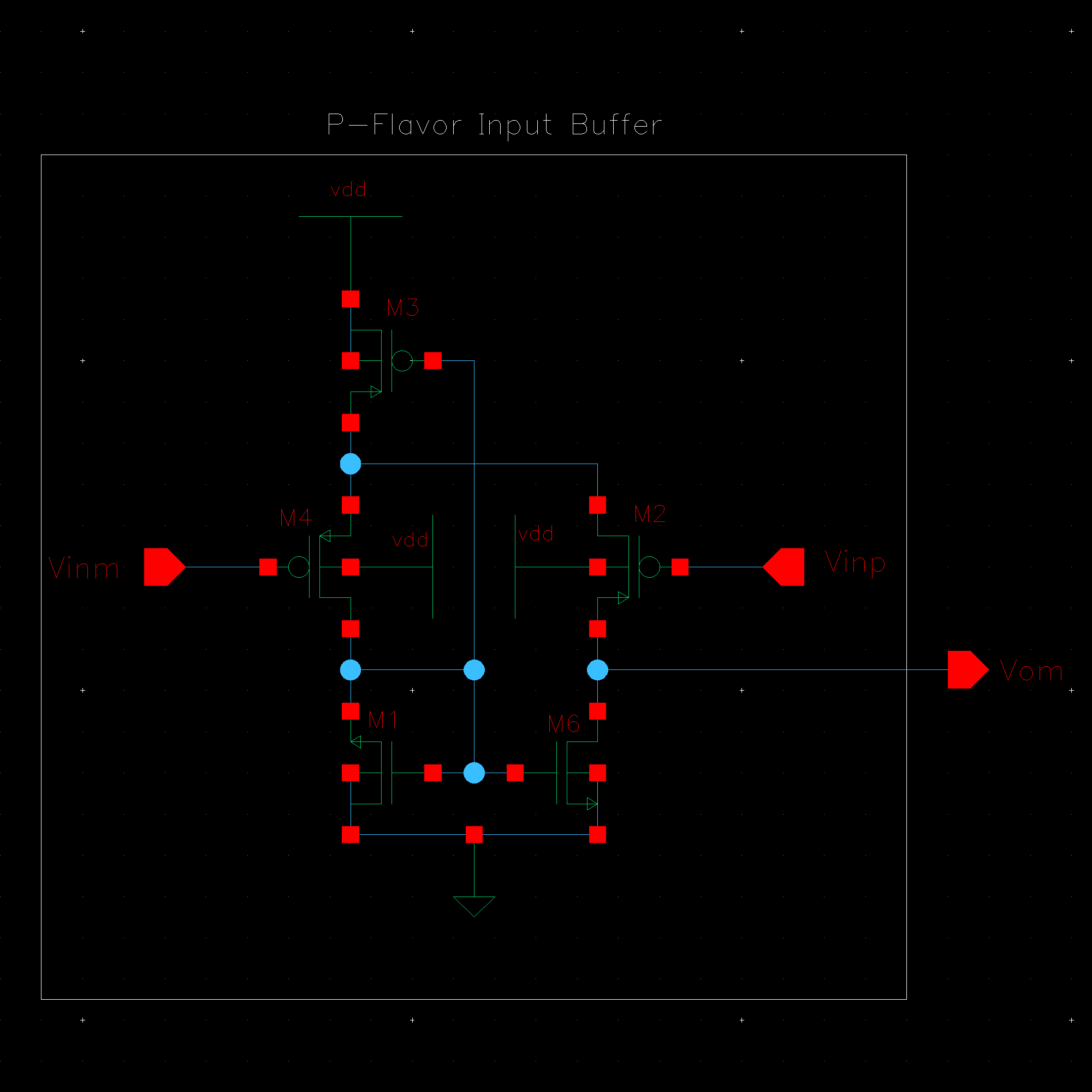

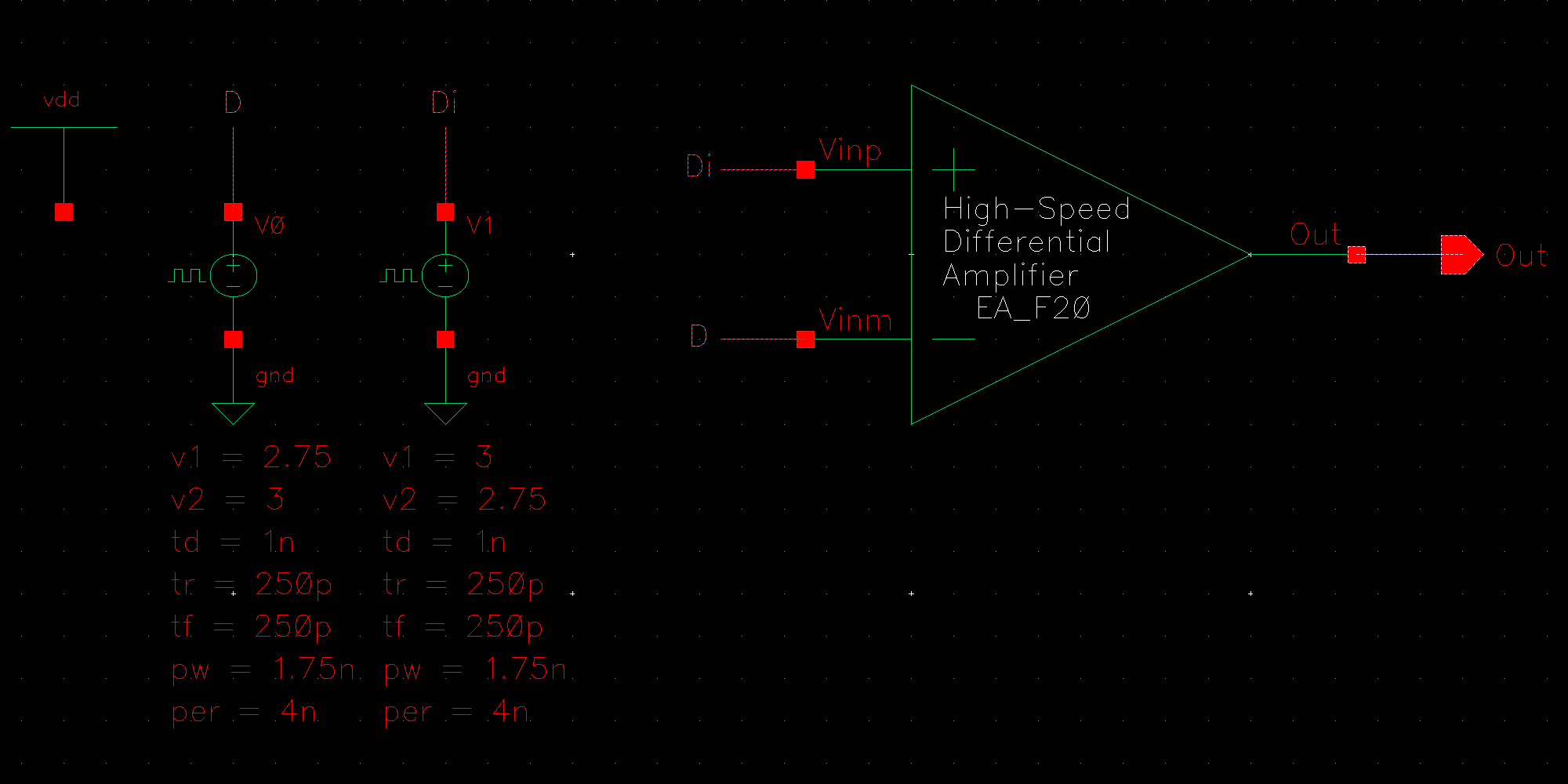

The detailed operation of the circuit is described in the book. Let us take the high level approach and consider that the circuit does what it is designed to do; take in an input and its complement and amplify the difference between them.

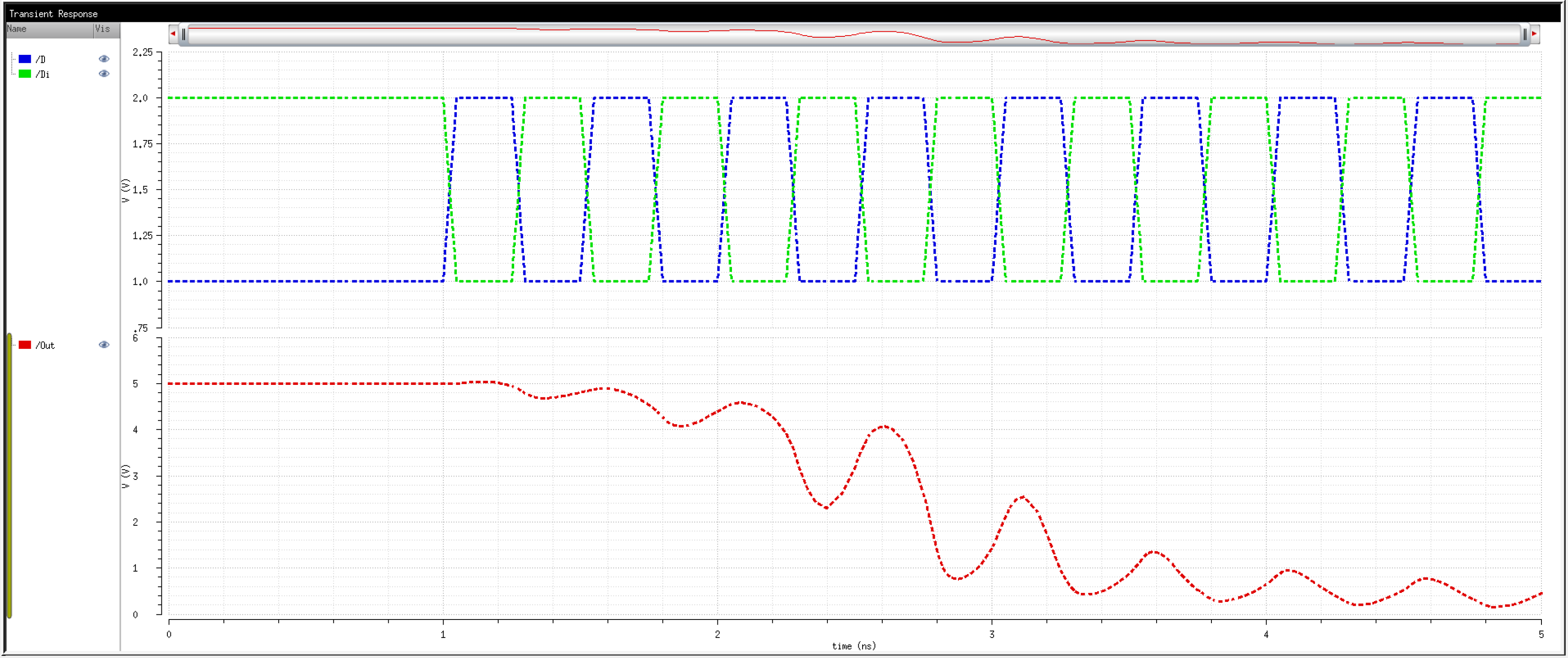

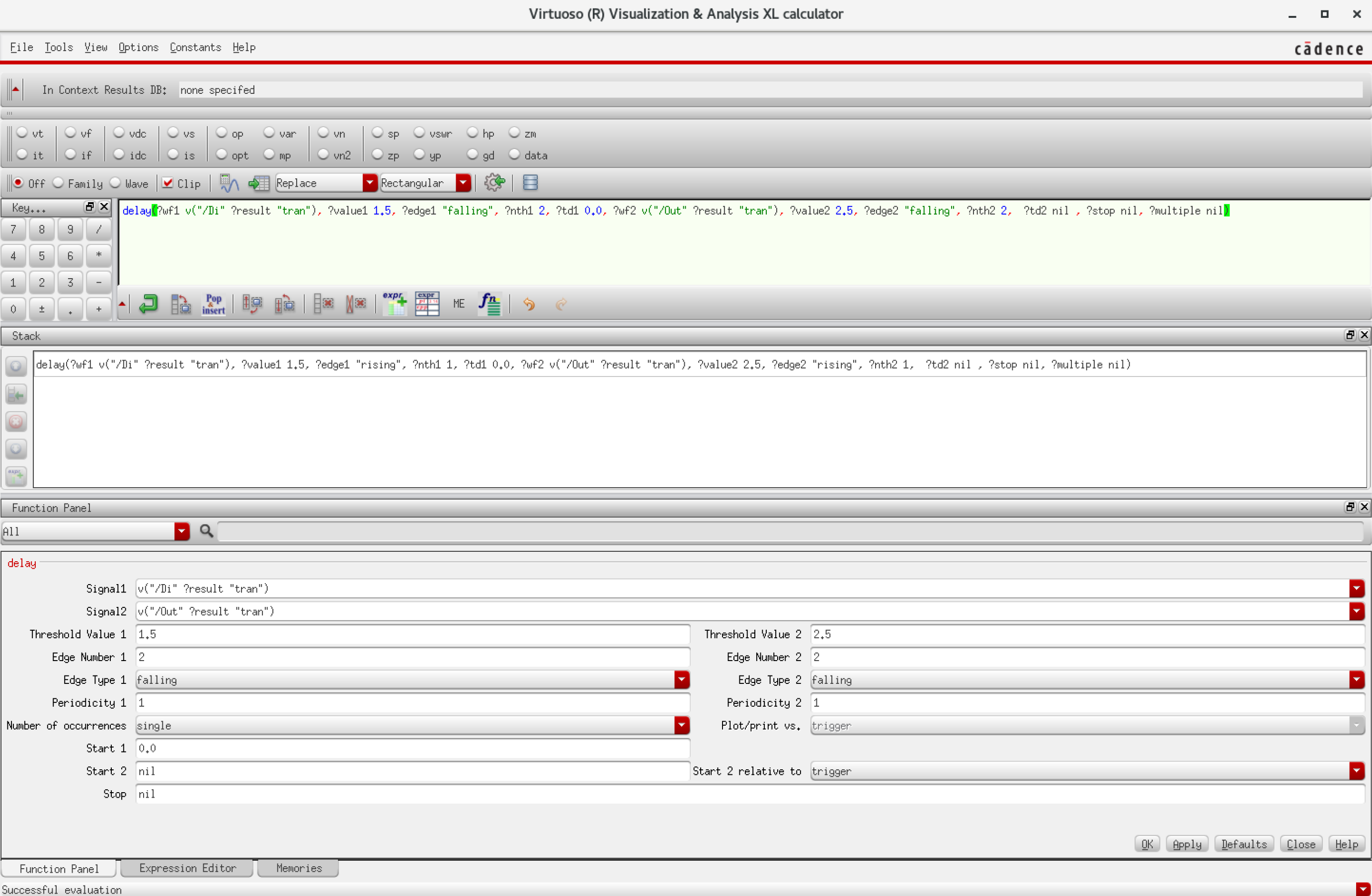

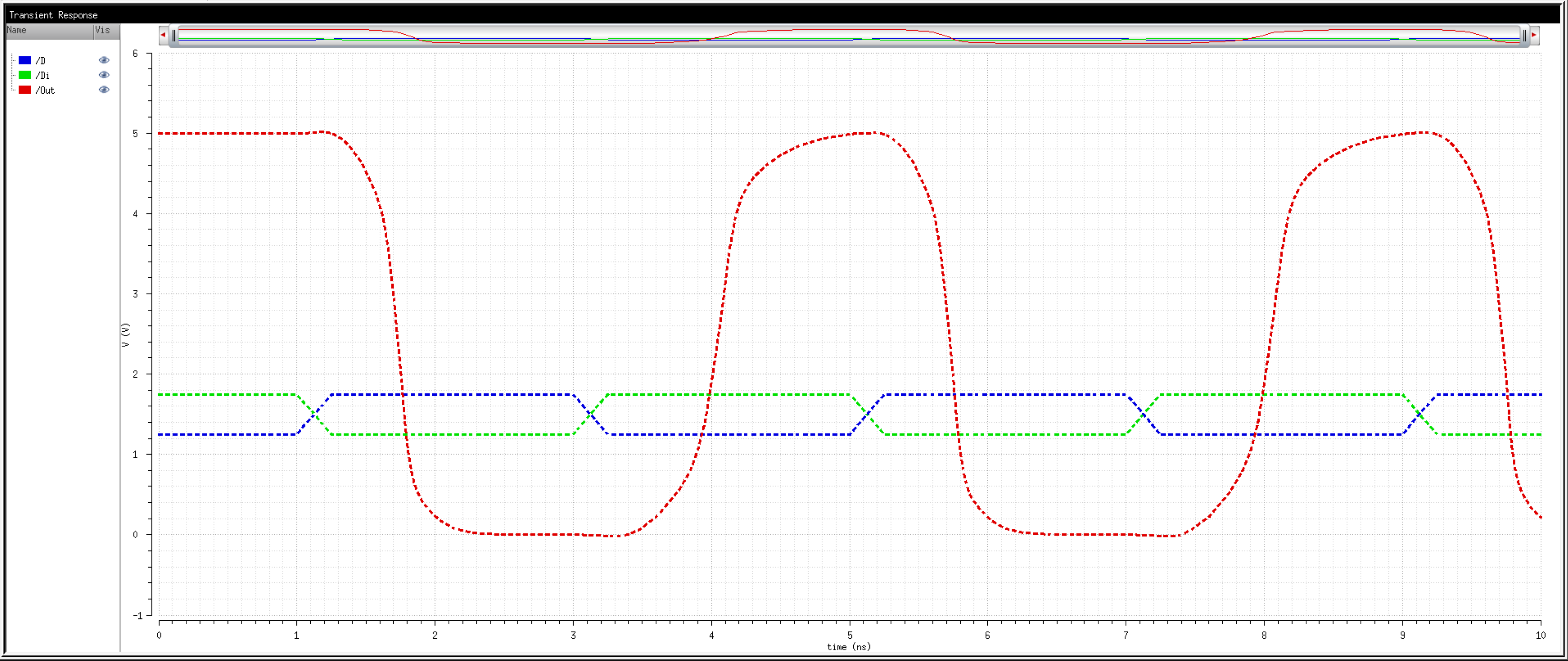

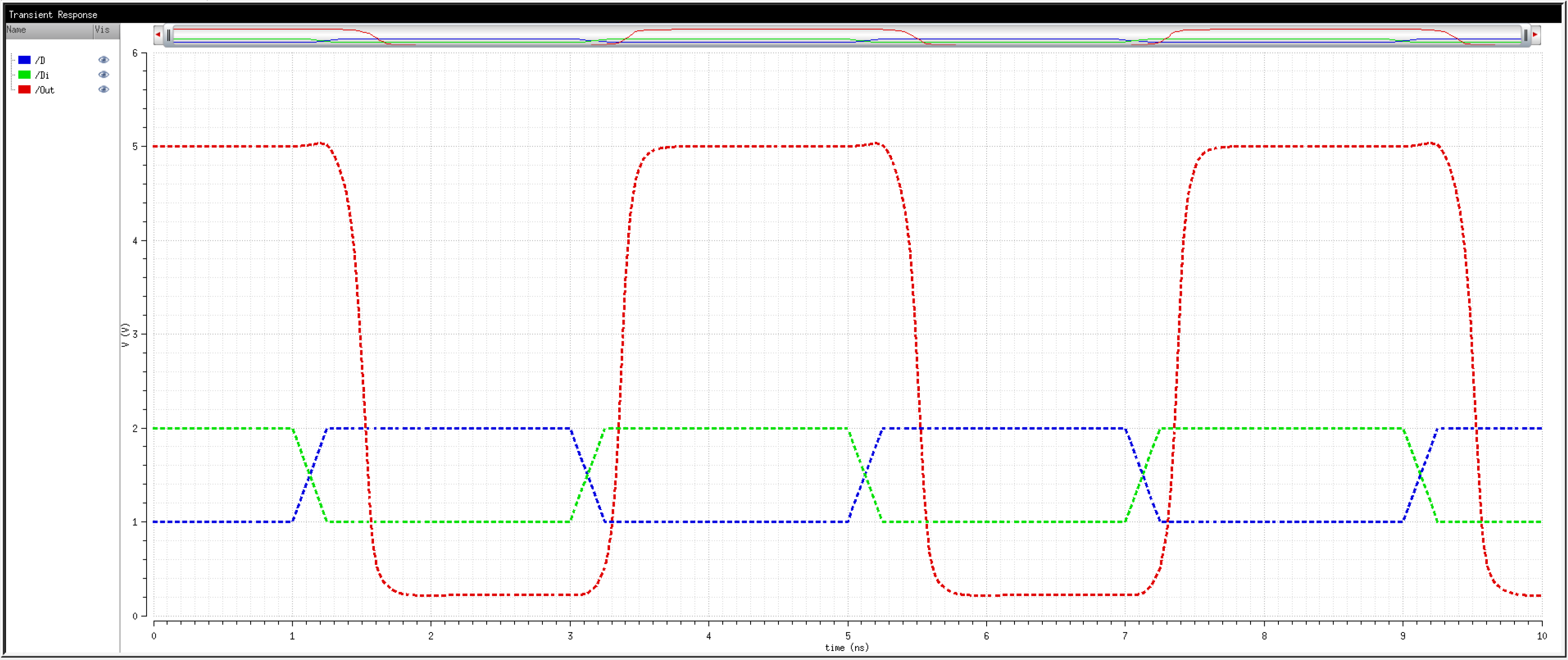

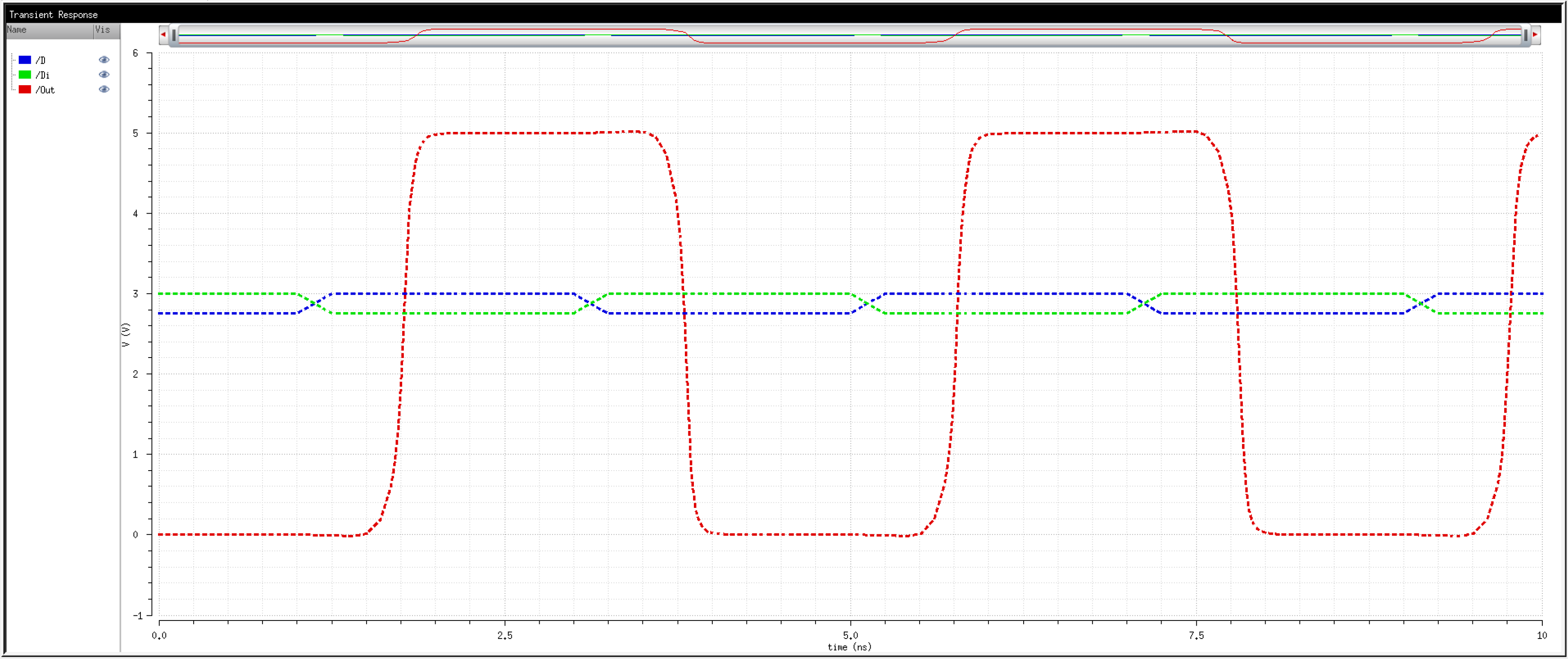

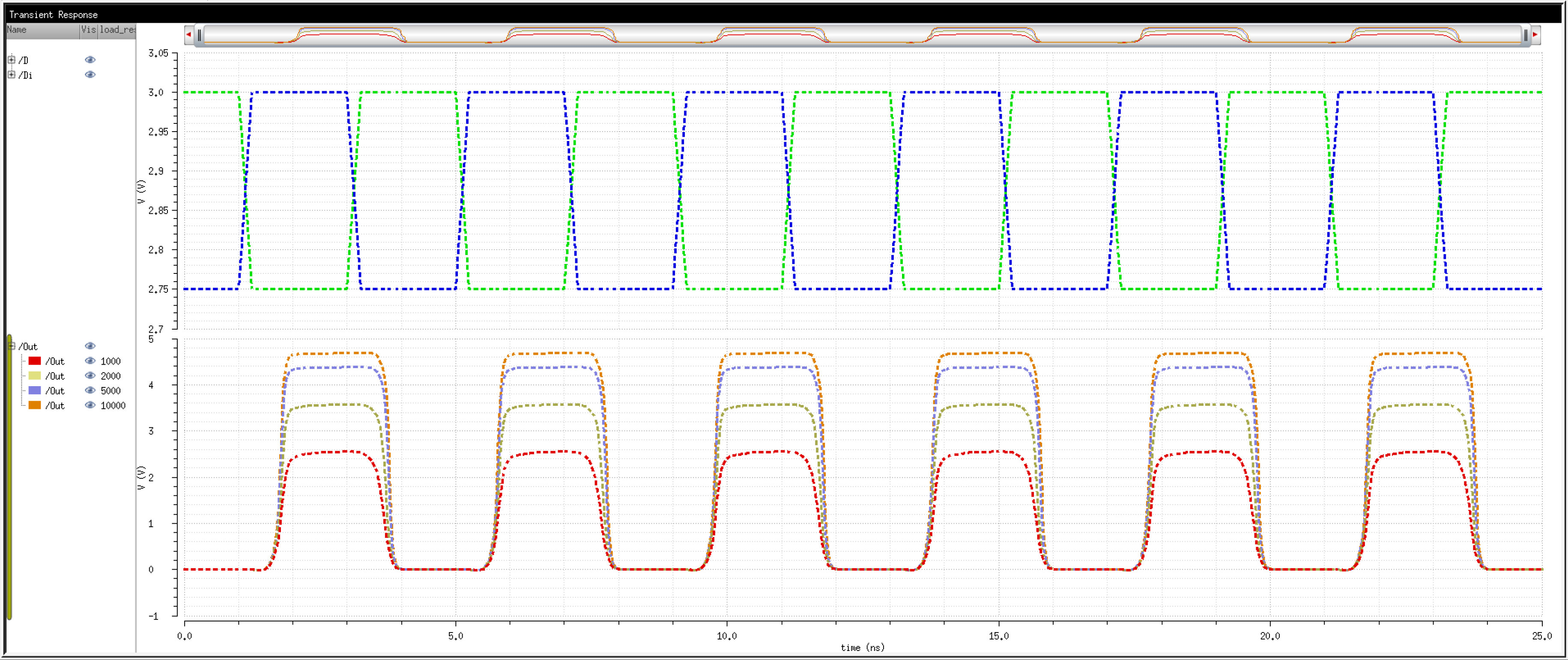

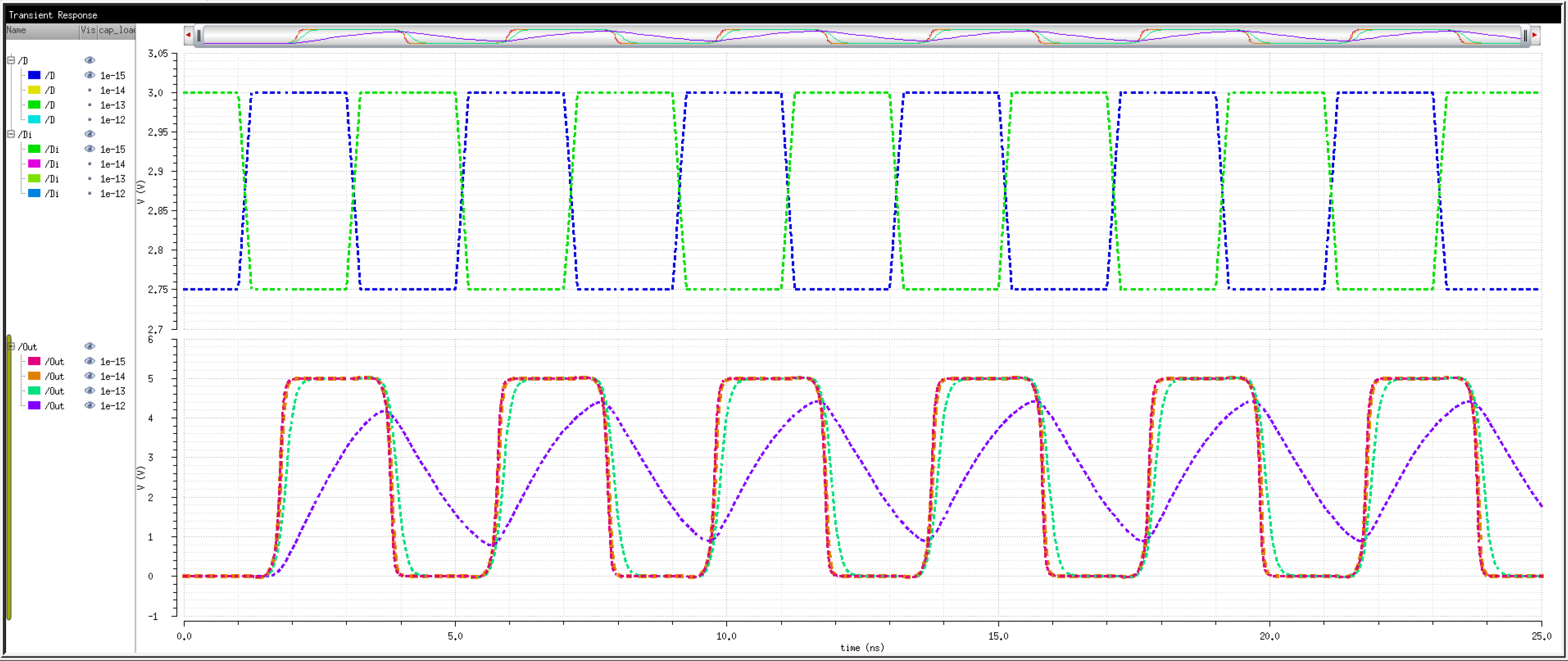

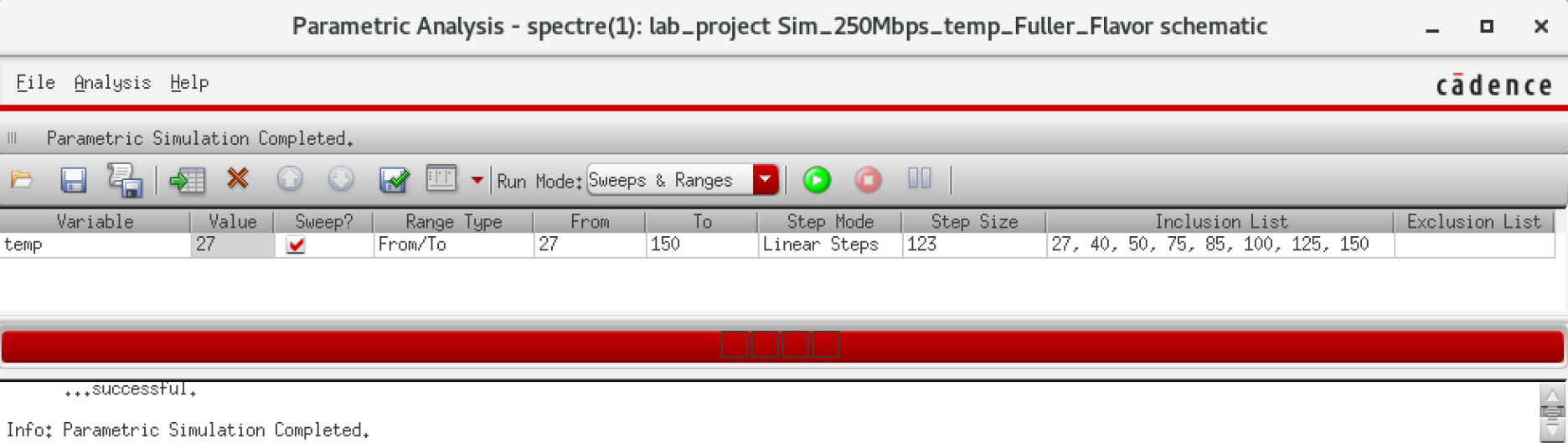

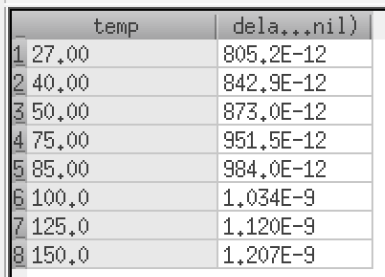

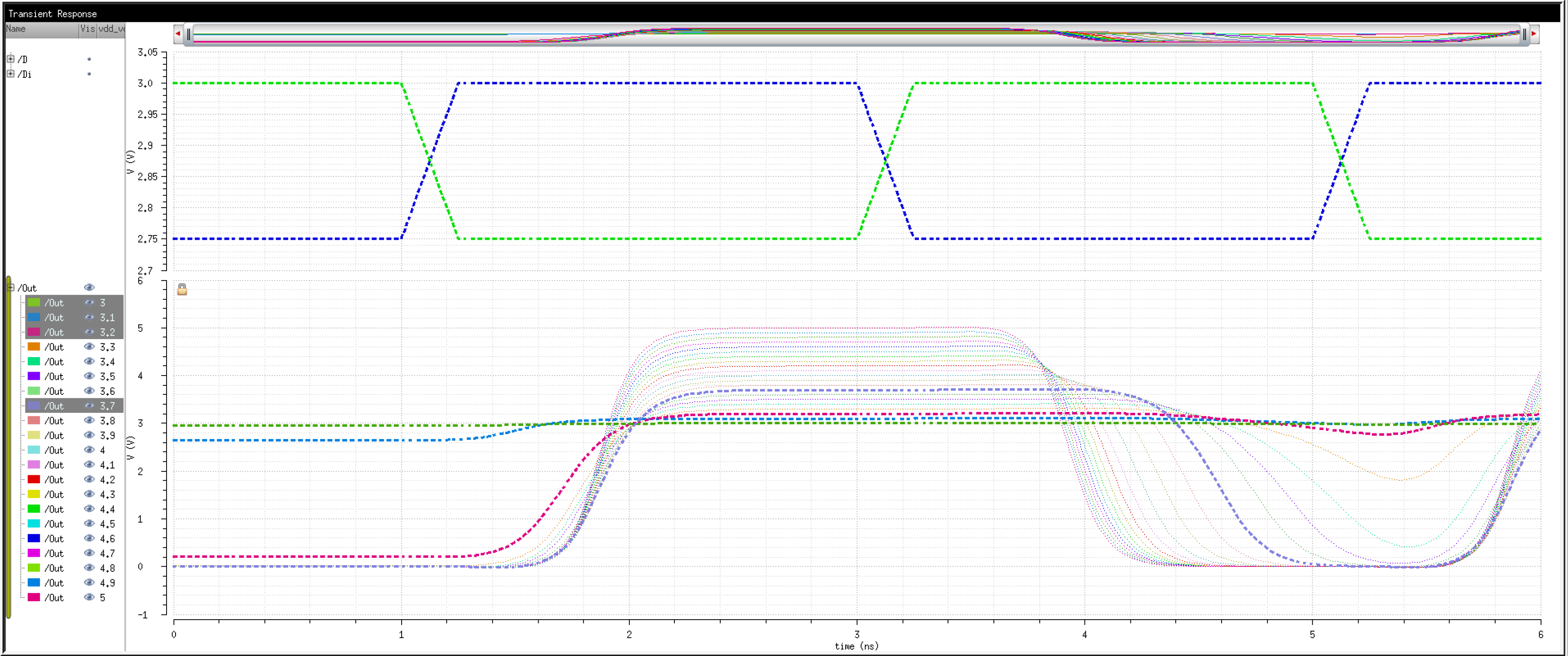

We know that transistors are real world devices and do not switch instantly. There is an associated delay contributed by the MOSFETs' resistances and capacitances.

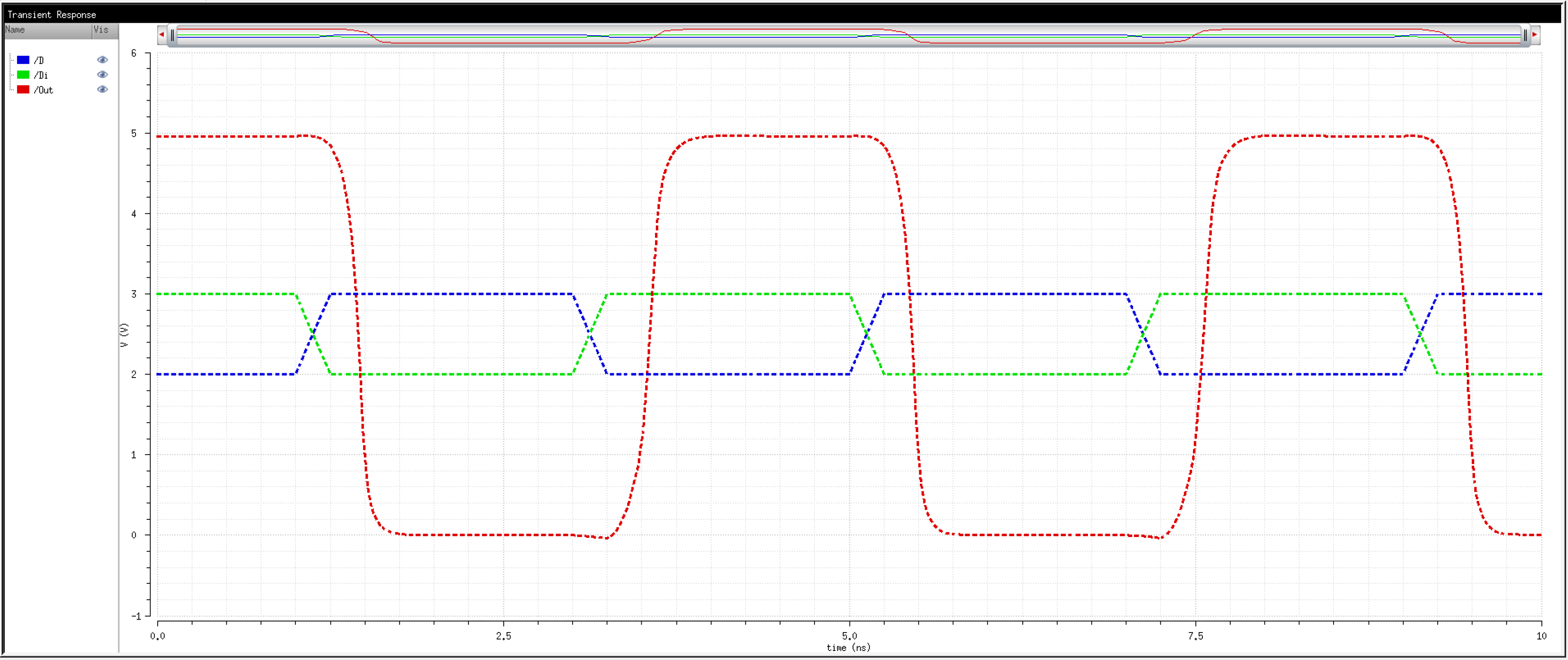

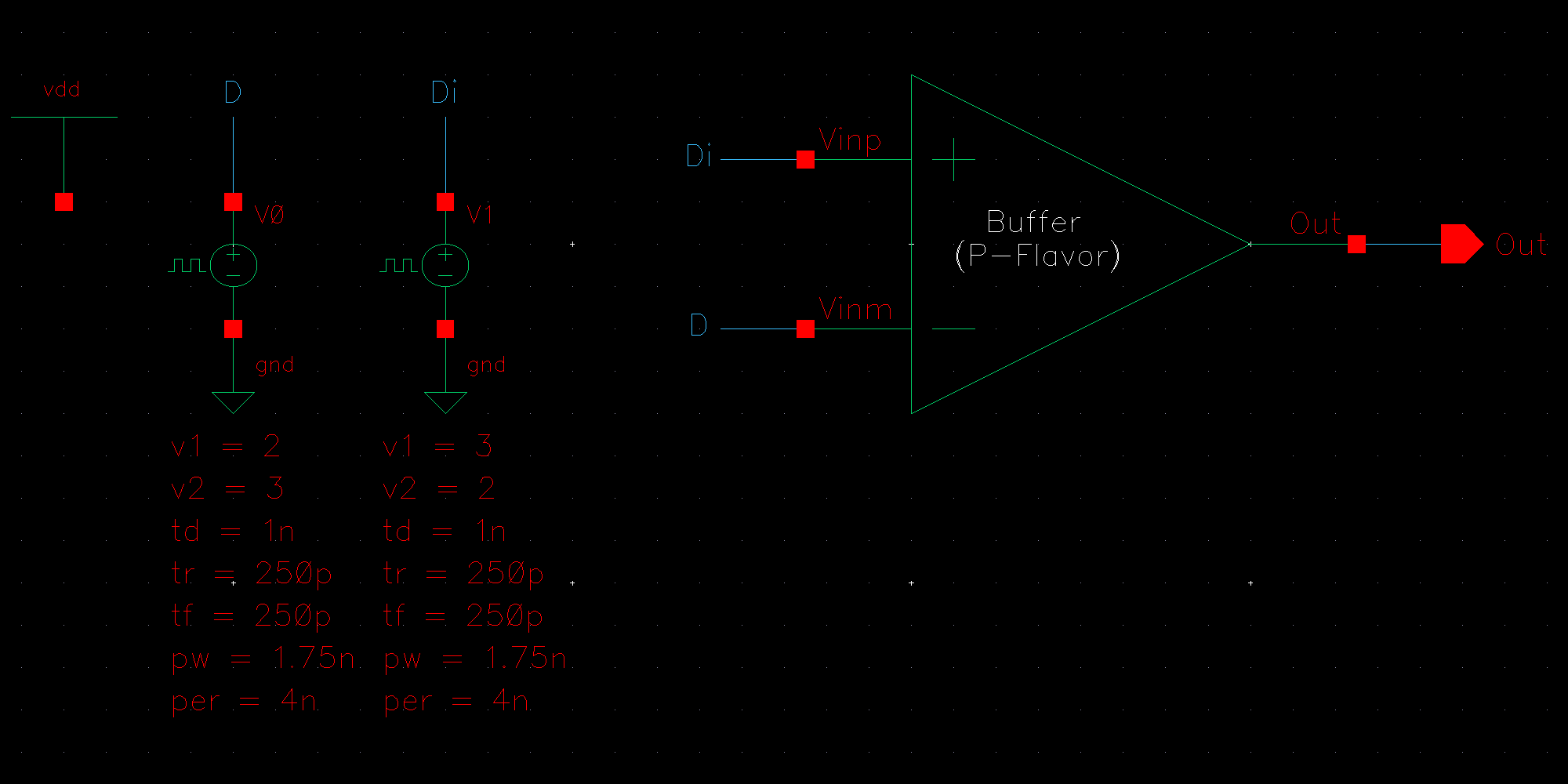

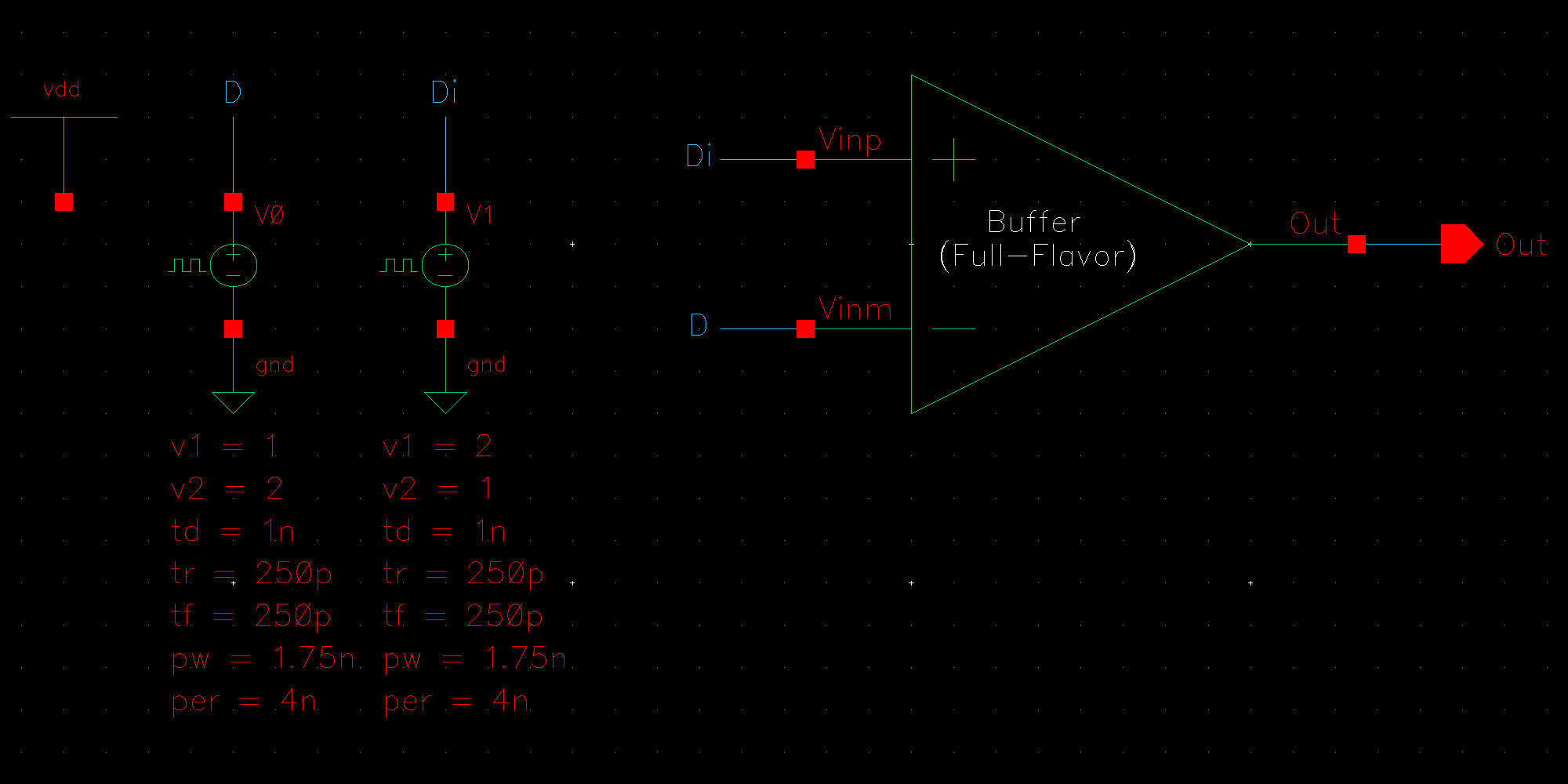

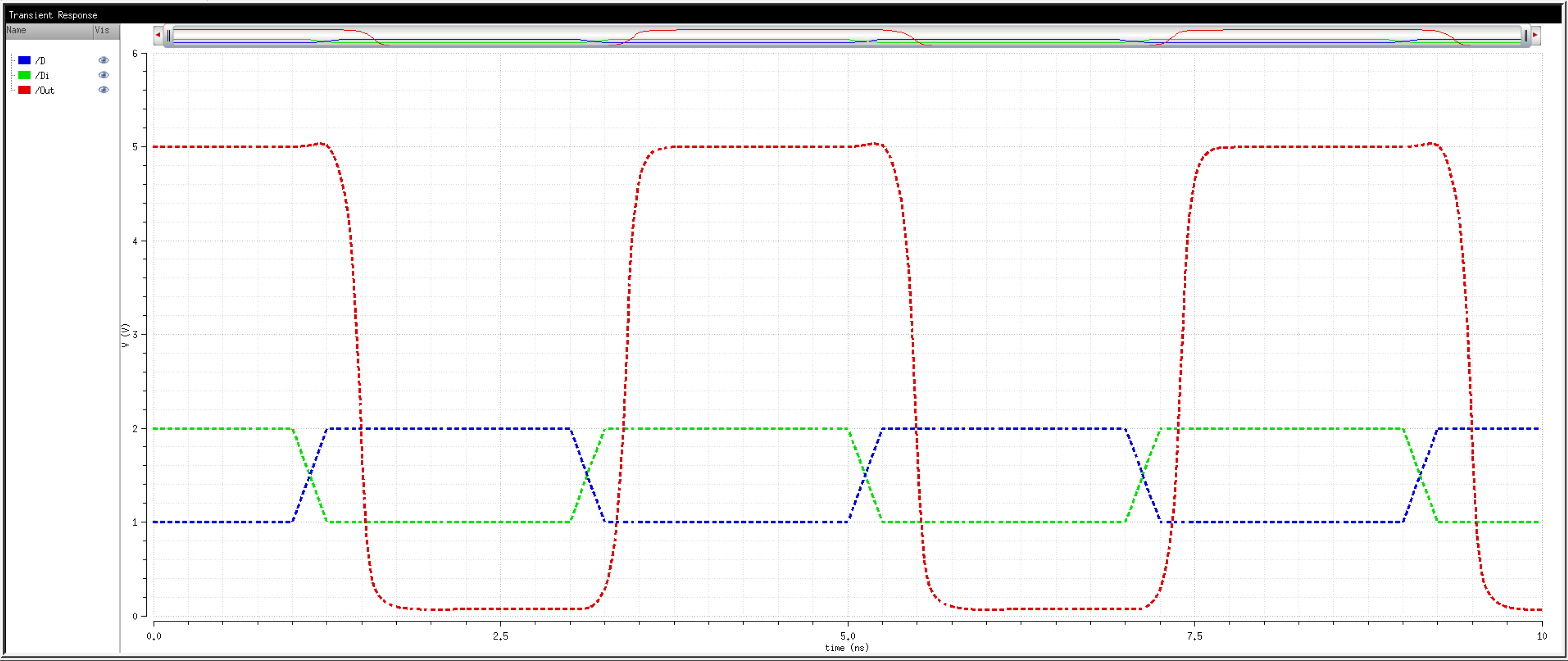

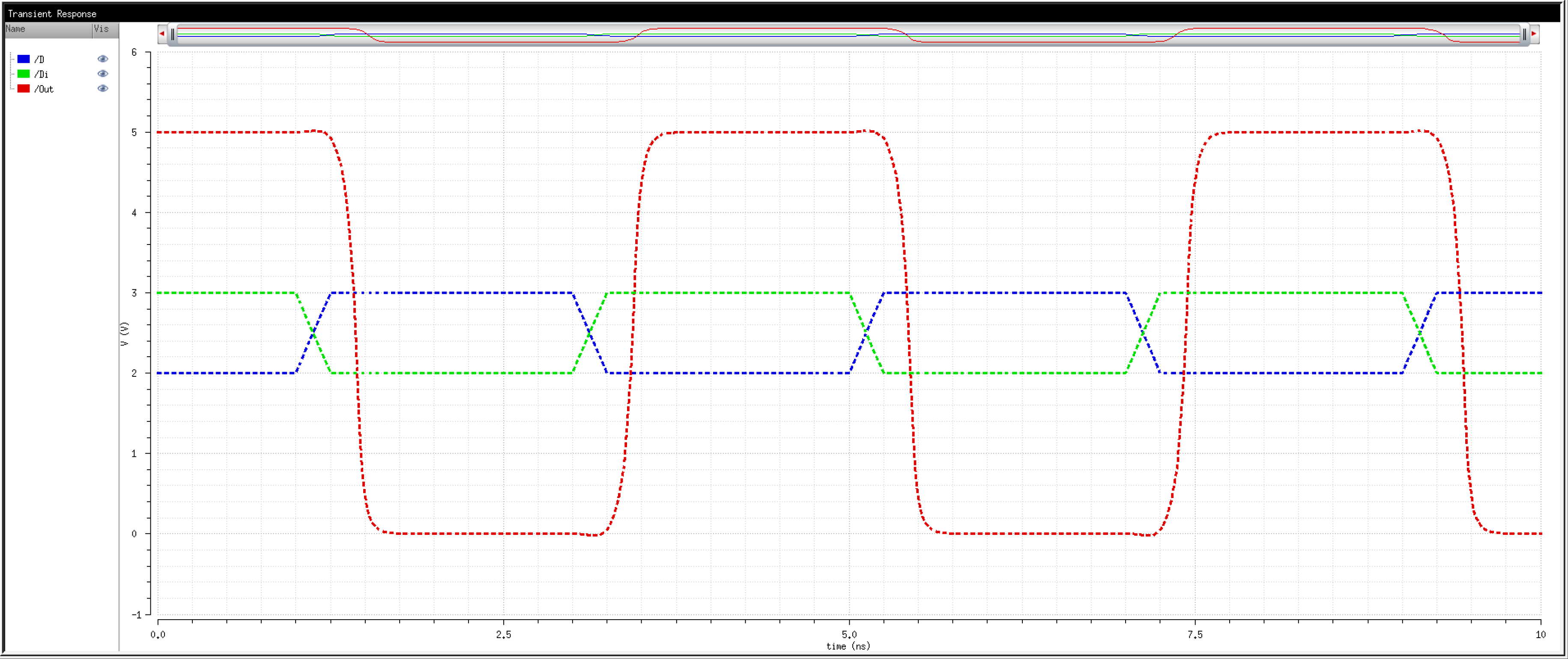

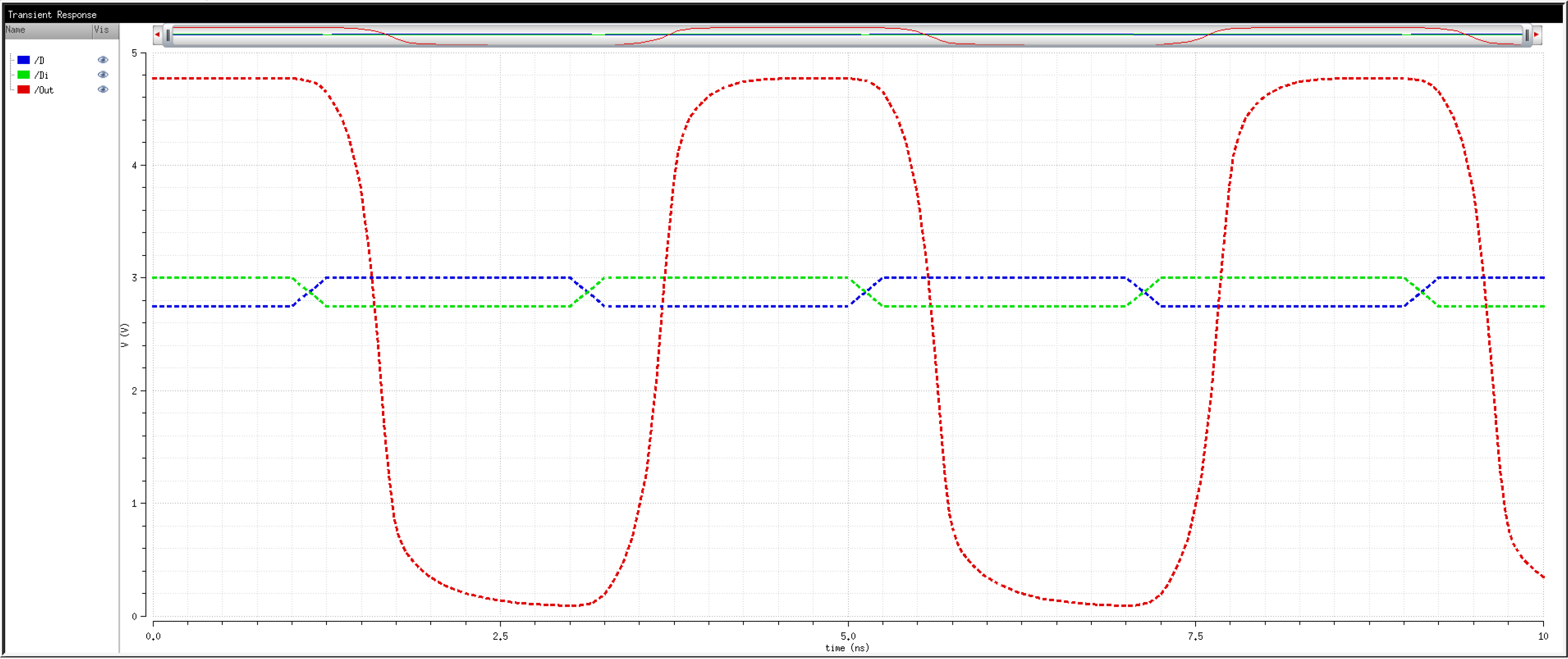

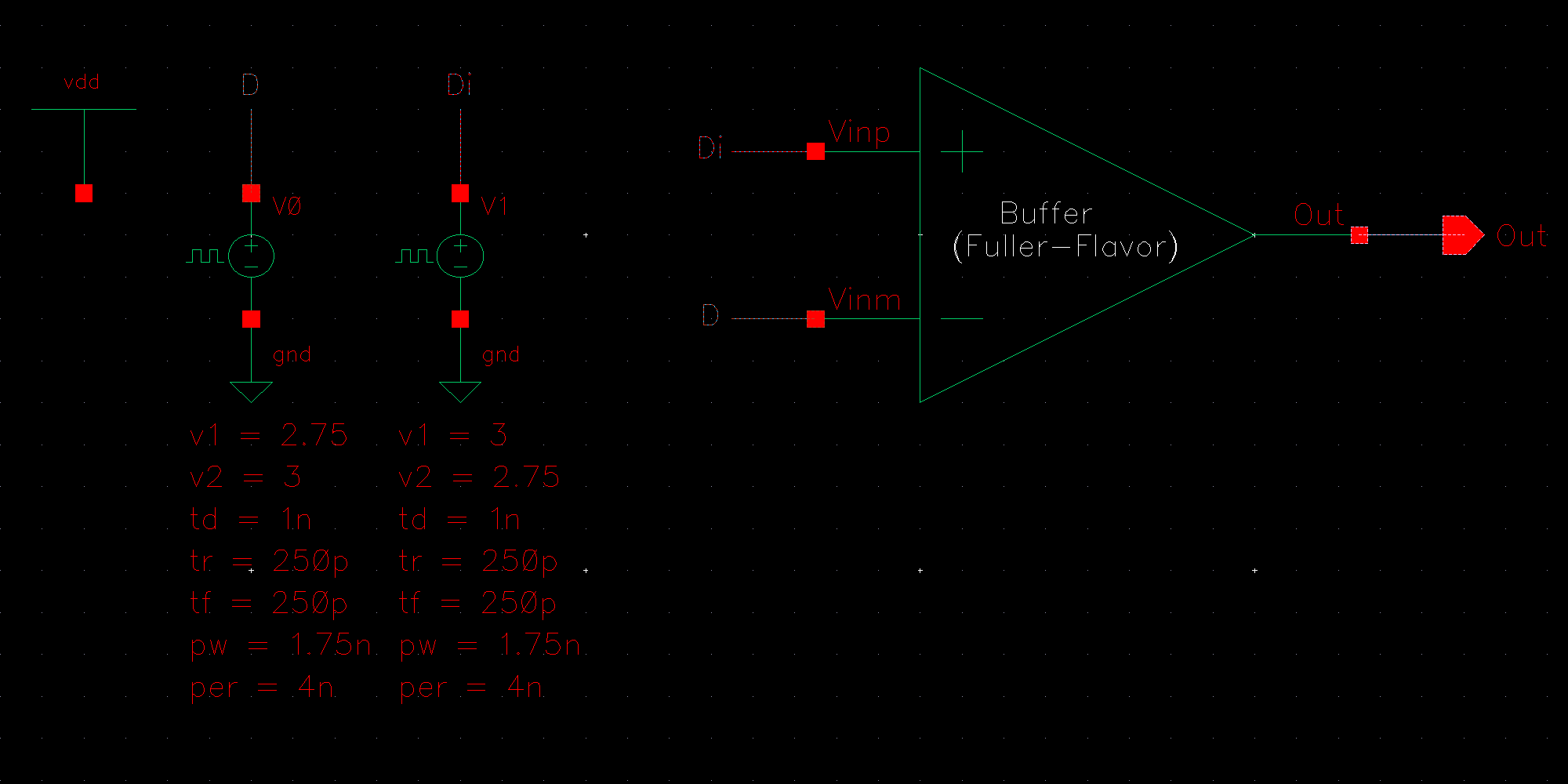

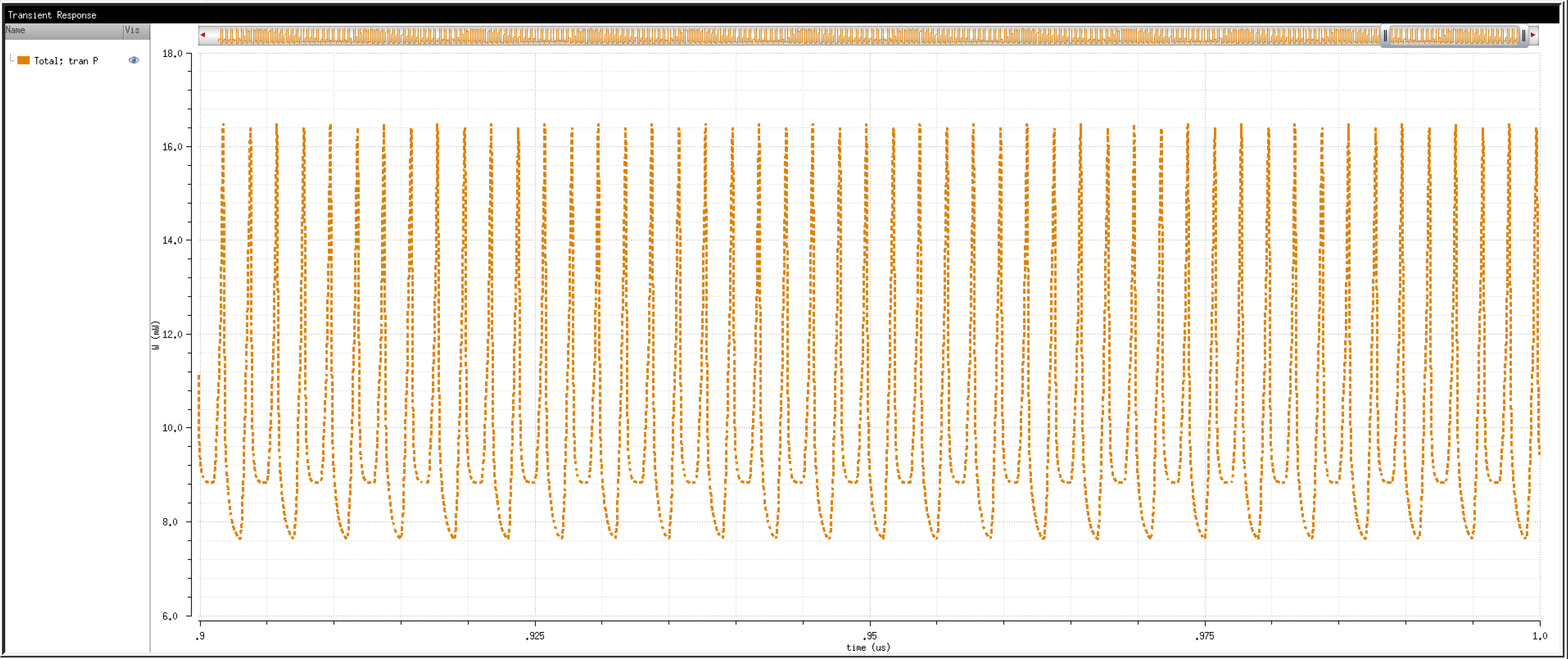

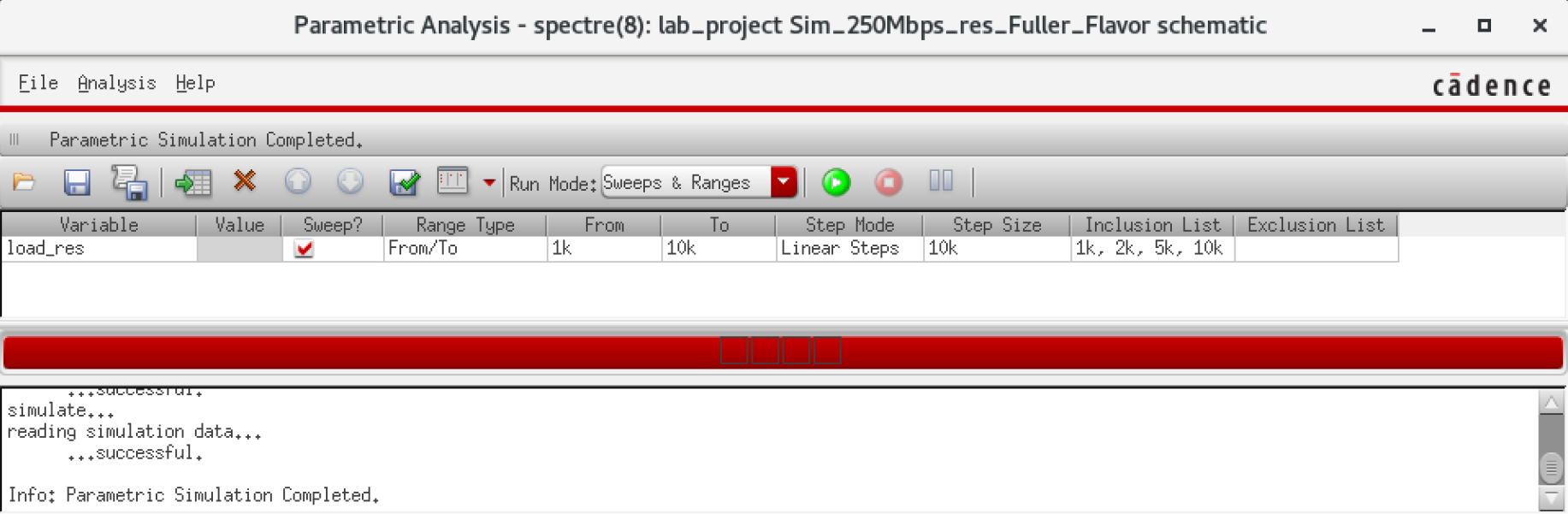

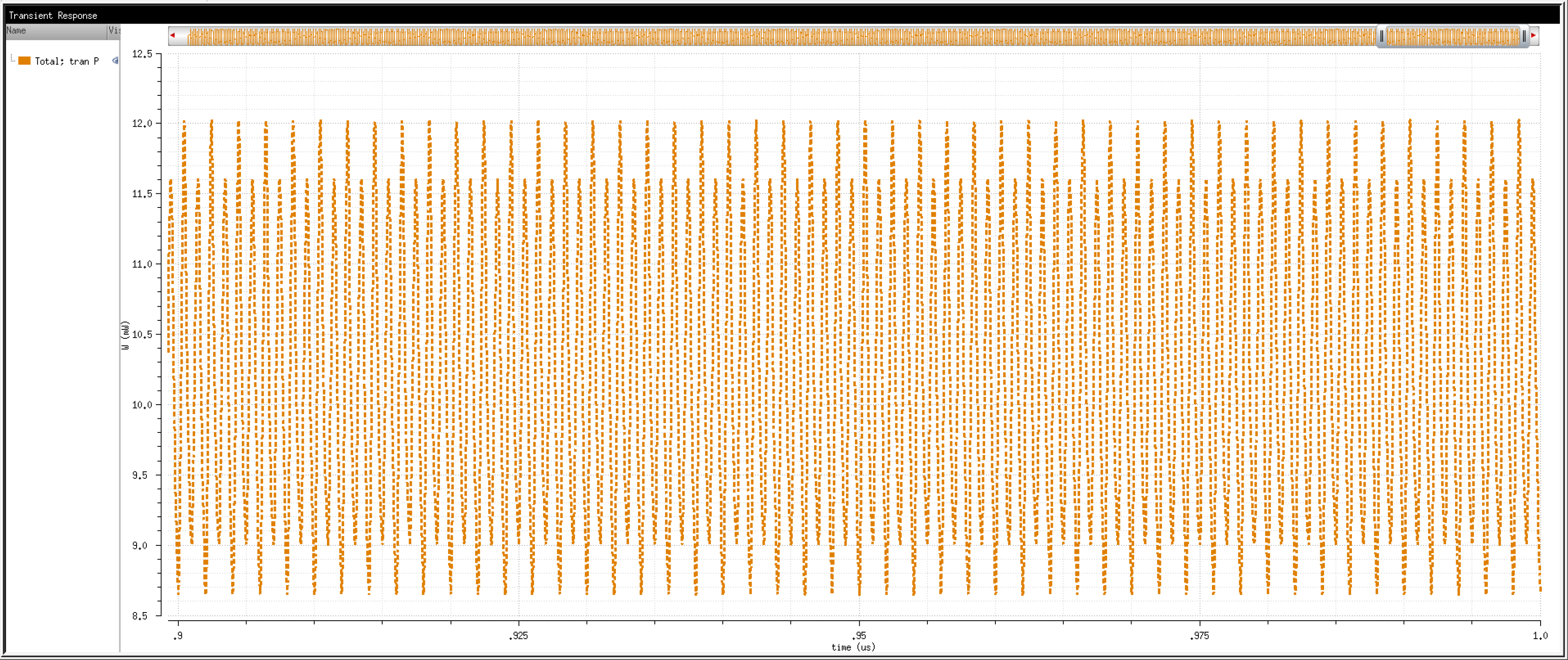

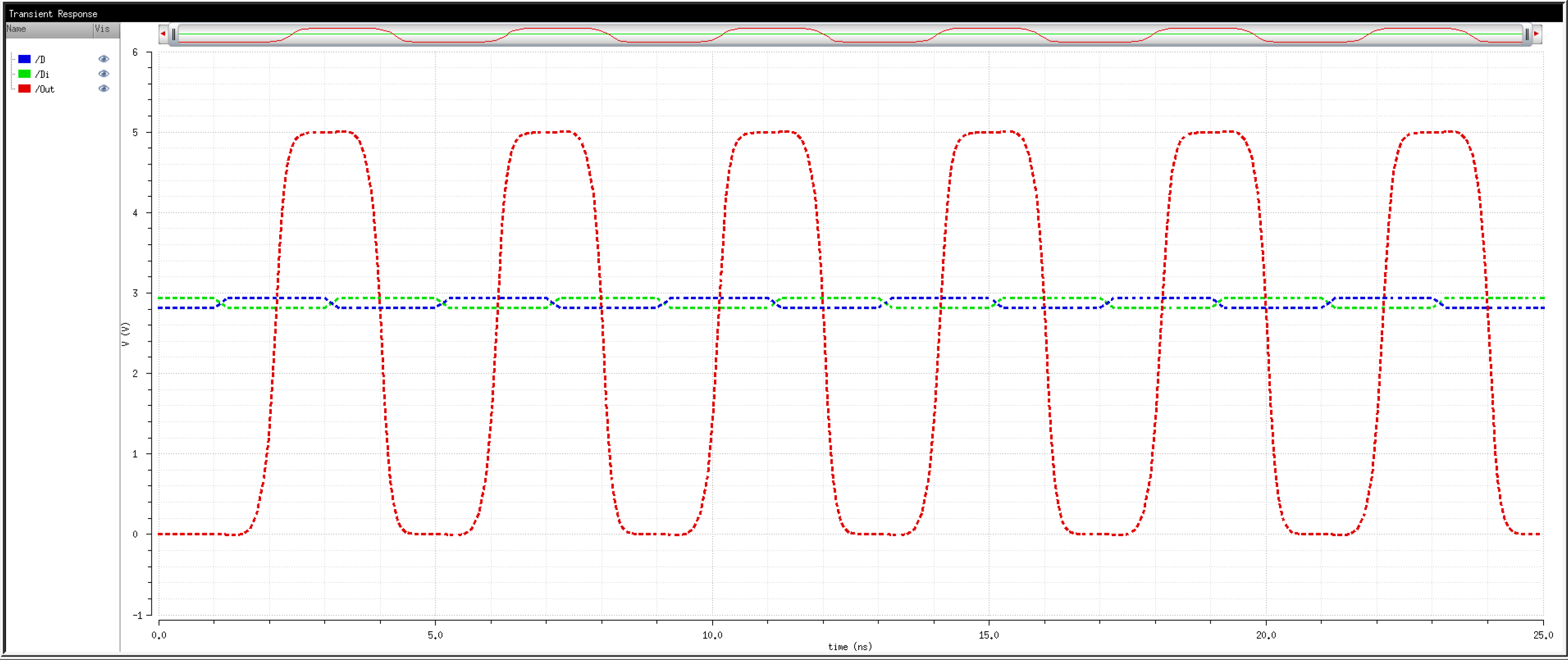

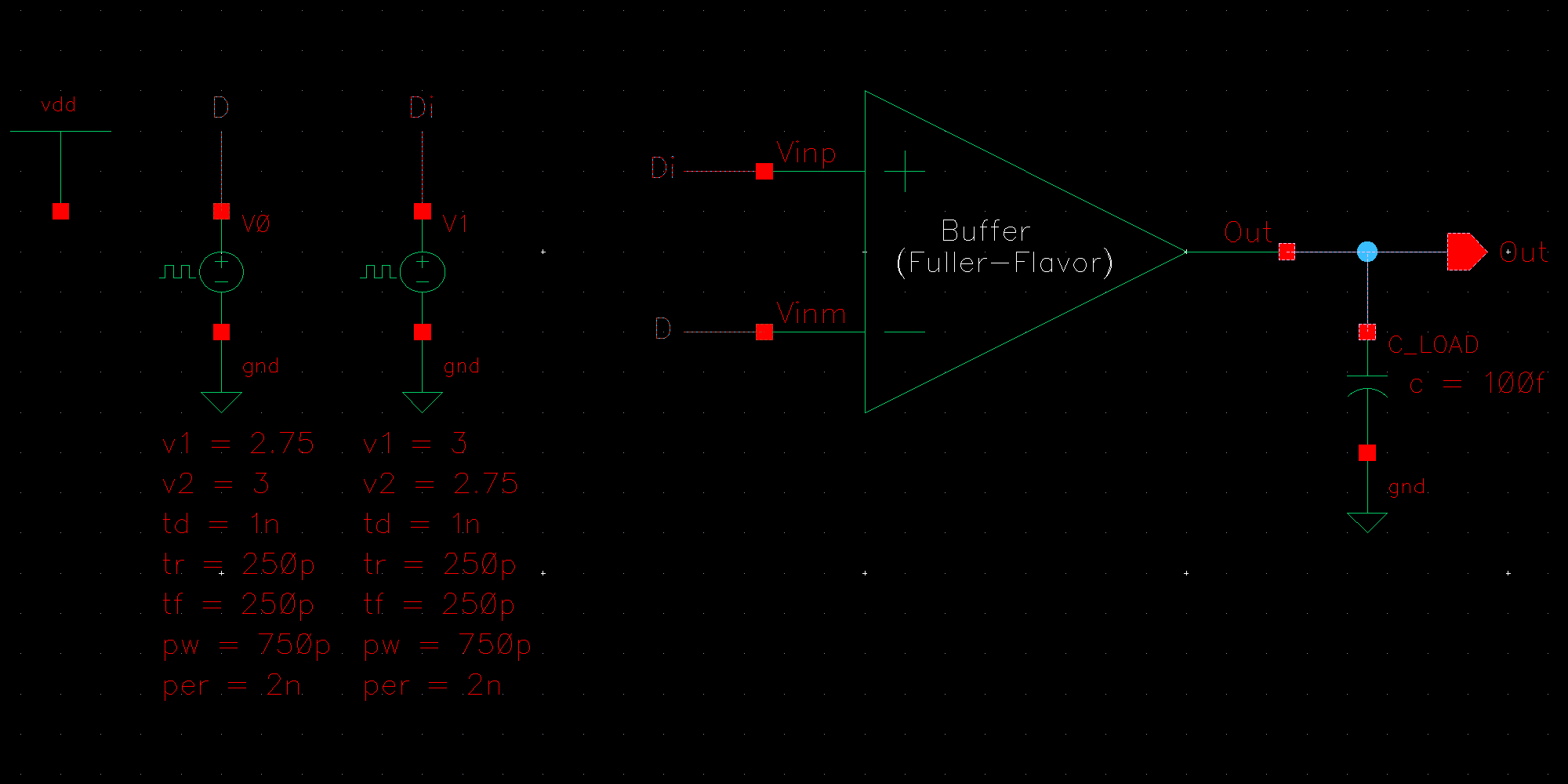

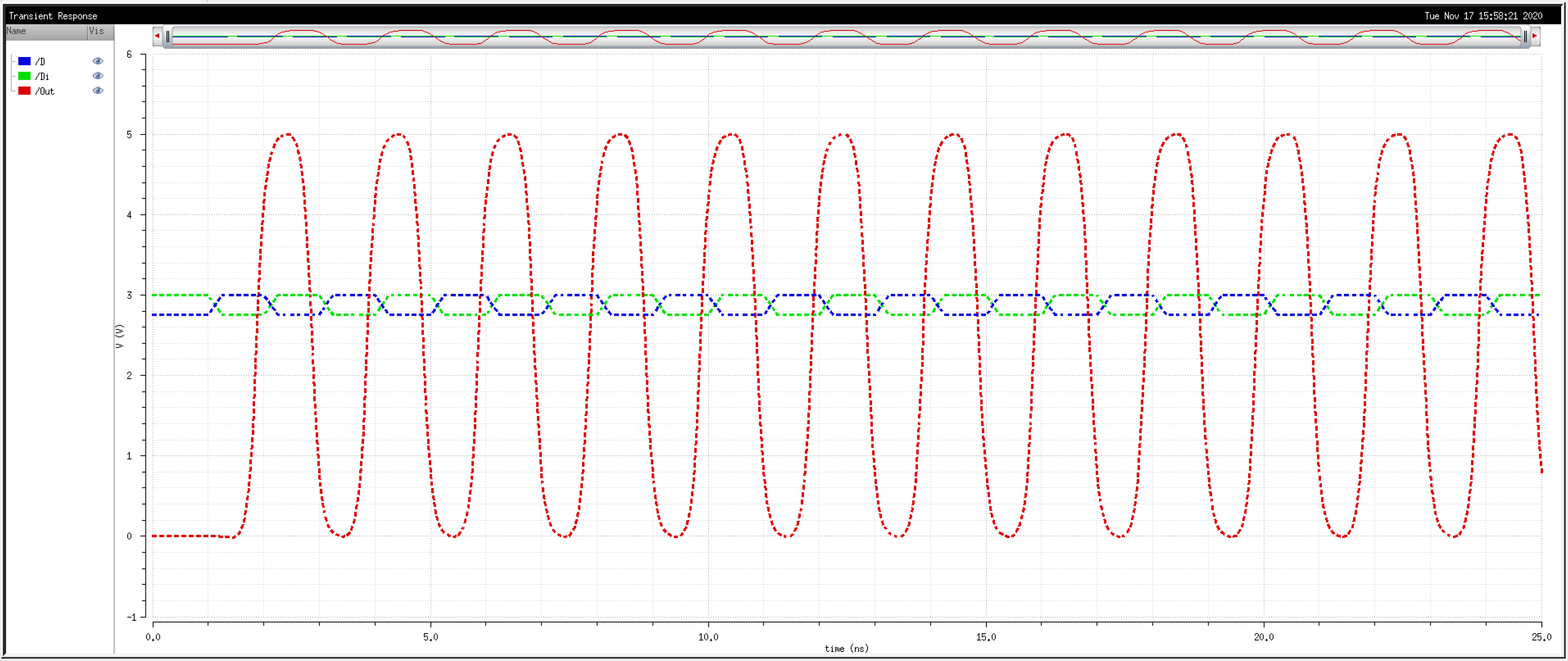

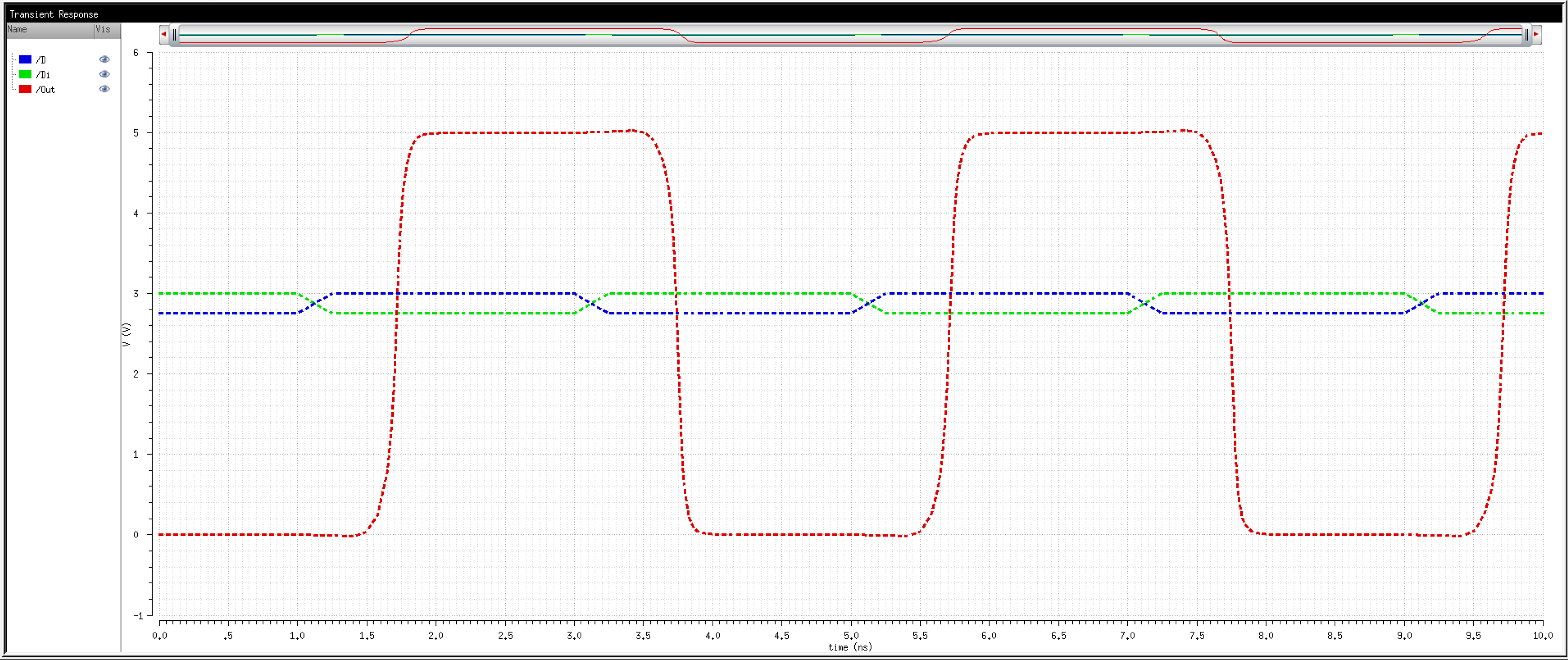

So, then, how fast can we operate the circuit? Let's try 2Gbps.