EE 421L – Digital IC Design Lab – Lab 6

Design, layout, and

simulation of a CMOS NAND gate, XOR gate, and Full-Adder

Author: Darryl Derico

E-Mail:

derico@unlv.nevada.edu

10/9/2019

Lab Description:

Our goal in this lab is to

create a 2-input NAND gate and a 2-input XOR gate using 6u/0.6u NMOS and PMOS

MOSFETs. Then, using these two gates, create a schematic and layout for a

Full-Adder.

Prelab:

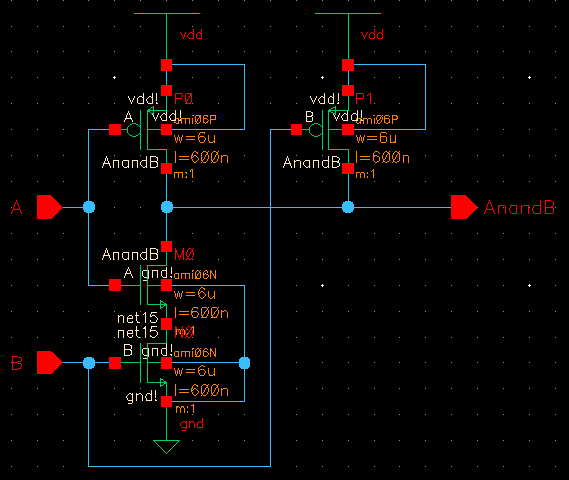

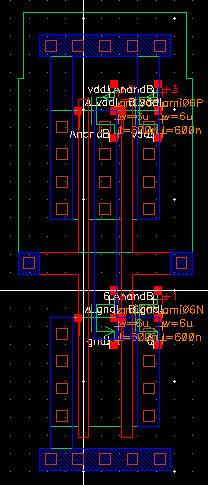

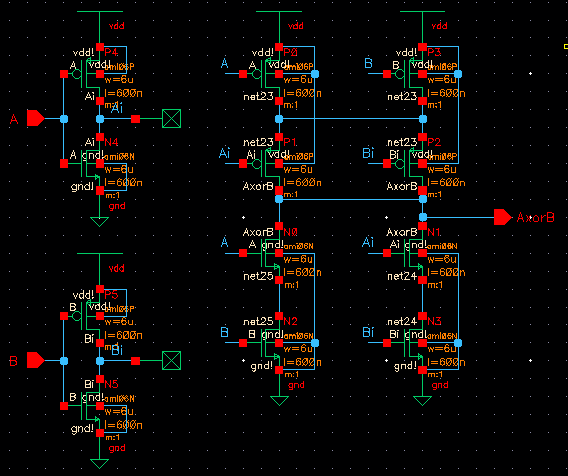

Went through and finished

Tutorial 4 creating a 2-input NAND gate in the process.

![]()

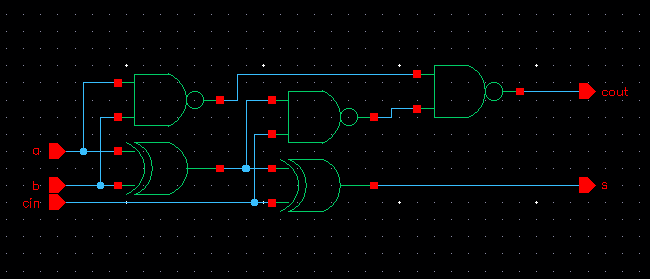

![]()

Lab:

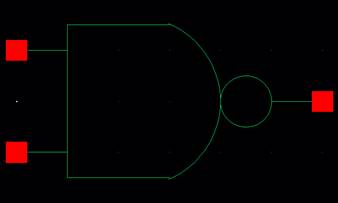

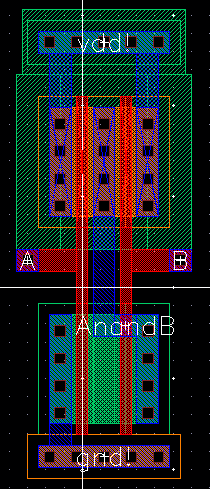

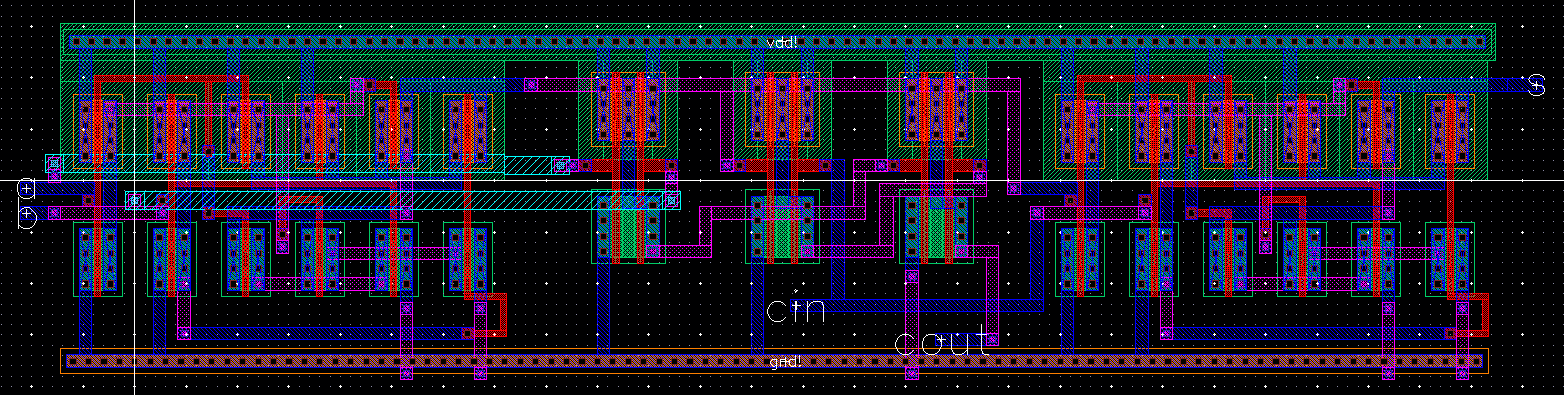

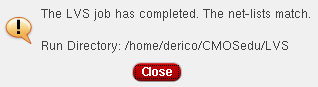

Create layout and symbol

views for these gates showing that the cells DRC and LVS without errors.

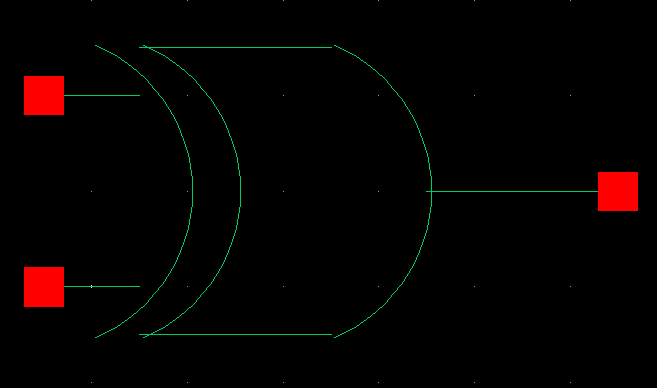

XOR:

![]()

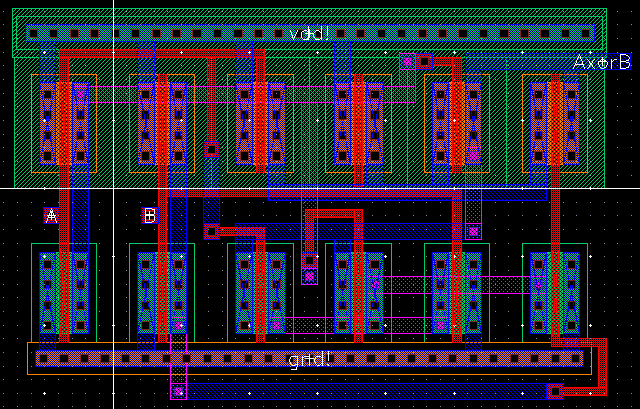

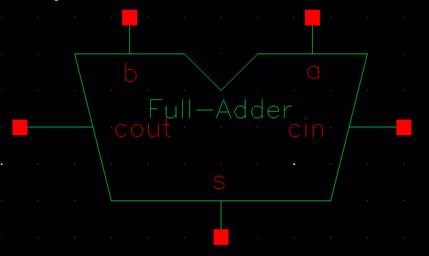

Full-Adder:

![]()

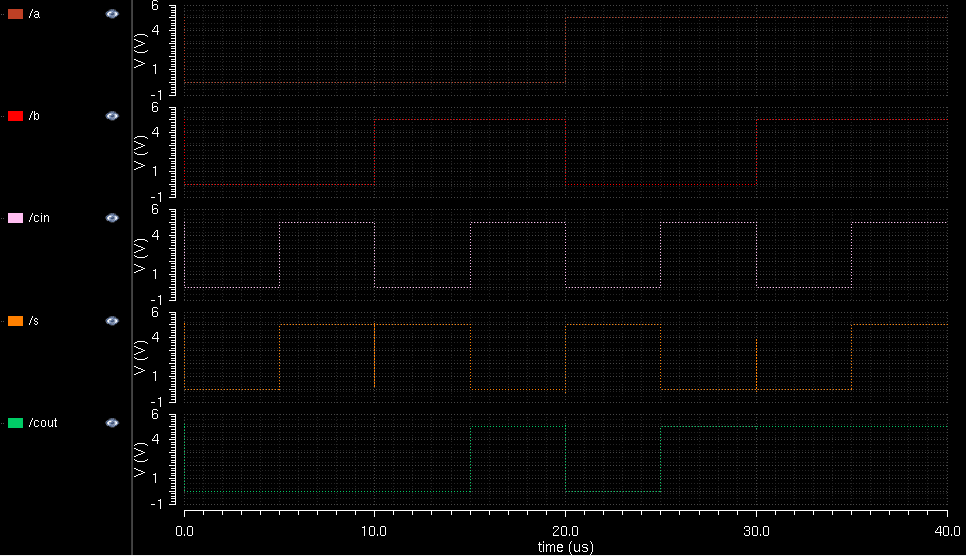

Simulated the Full-Adder: