Lab 7 - EE 421L

Authored

by Jeeno Doria,\

doriaj3@unlv.nevada.edu

11/07/2017

Lab

description: Cover all of the basic building blocks used in an ALU.

PreLab:

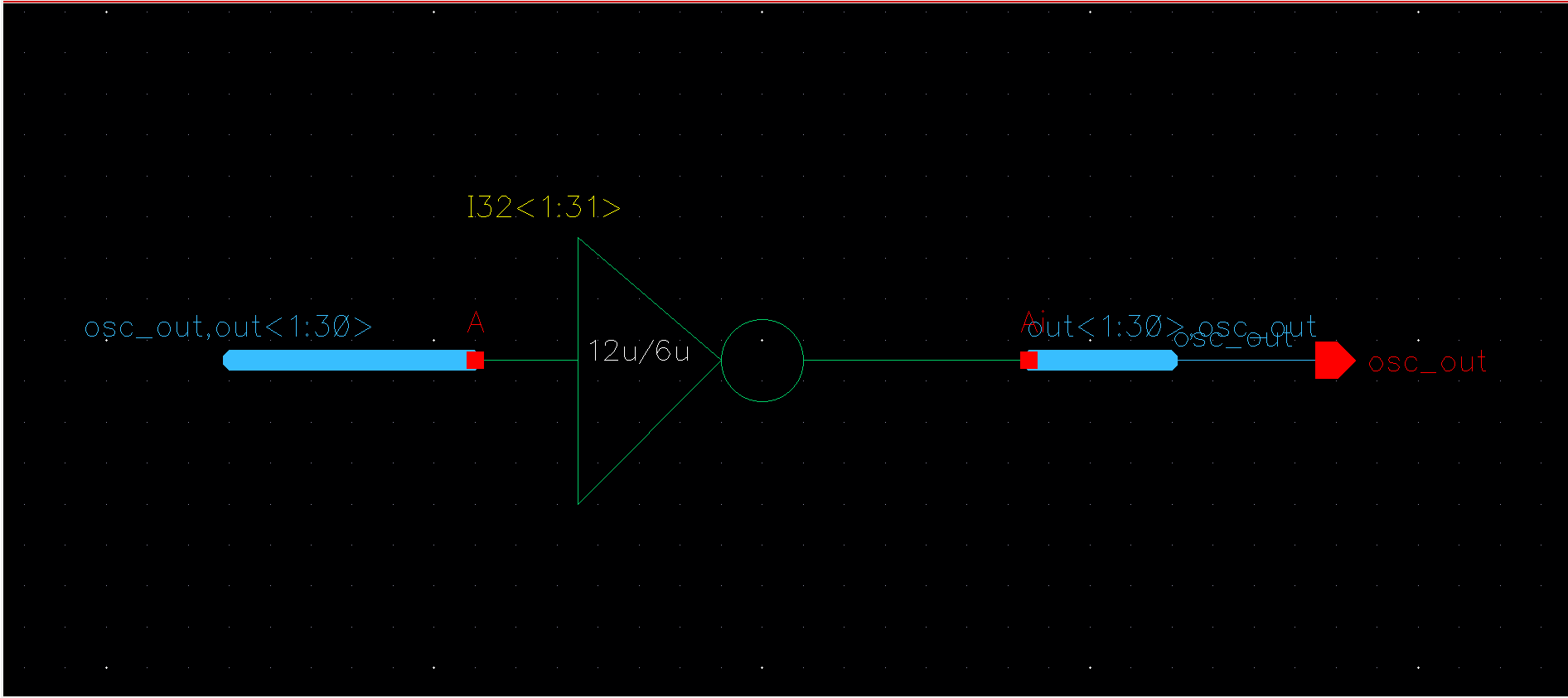

| Ring oscillator of 31 inverters | Symbol |

|  |

| Layout | Extracted |

|  |

| Schematic Simulation | Extracted Simulation |

|  |

Lab:

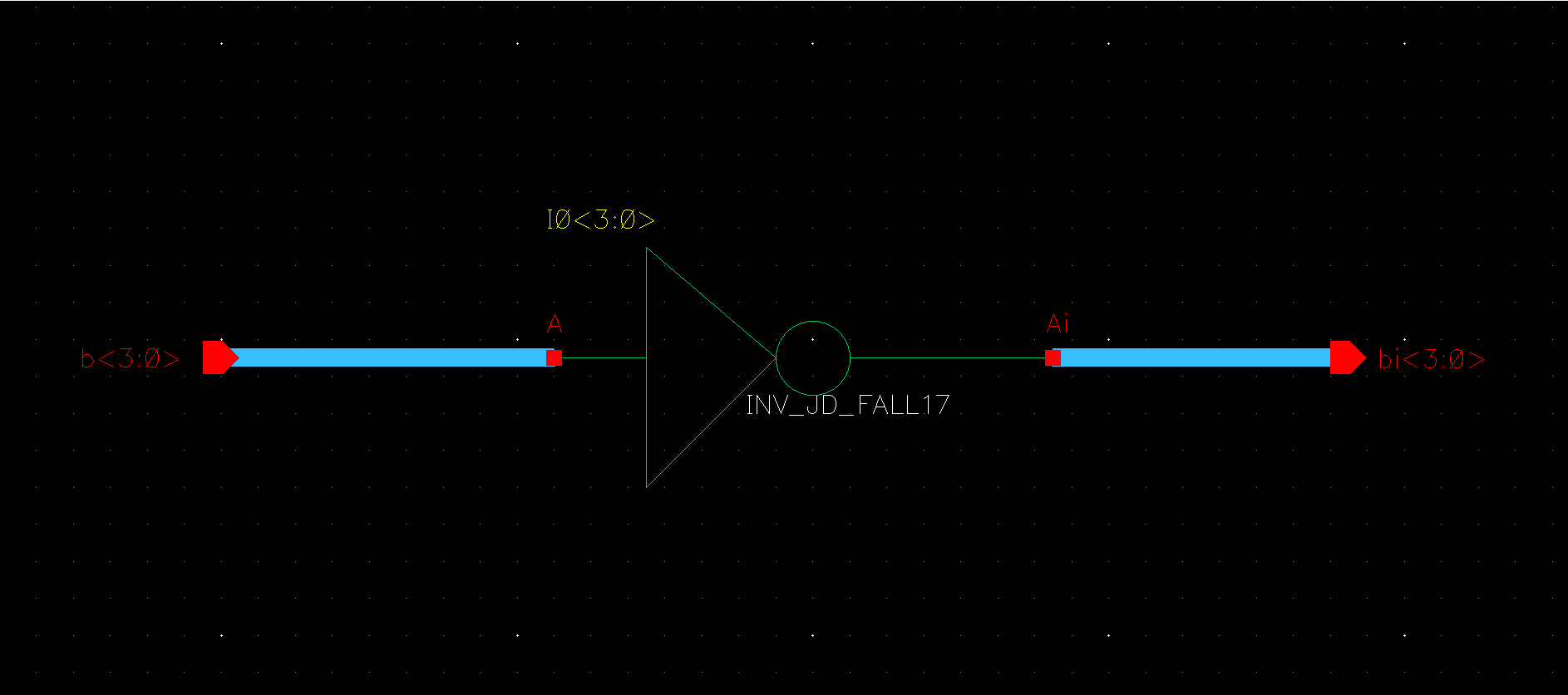

-Equivalent, more concise, schematic by instantiating an inverter and naming the inverter using an arrayed name (I0<3:0>)

| Inverter Schematic (of one) | The more concise schematic (of 4 of them) | Symbol (of 4 of them) |

|  |  |

-Creating a simulation schematic like the one seen in the prompt

-All four inverters' inputs are tied together to an input pulse source

| Schematic | Simulation |

|  |

-

The time delay will increase as the capacative load increases. If the

capacitor is large, the amount of chargers that could be stored gets

larger, which causes the voltage to take a longer time to rise and fall.

-Creating schematics and symbols for an 8-bit input/output array of: NAND, NOR, AND, inverter, and OR gates.

8-Bit NAND Gate:

| NAND Schematic | 8-Bit NAND Schematic | Symbol |

|  |  |

8-Bit NOR Gate:

| NOR Schematic | 8-Bit NOR Schematic | Symbol |

|  |  |

8-Bit AND Gate:

| AND Schematic | 8-Bit AND Schematic | Symbol |

|  |  |

8-Bit Inverter Gate:

| AND Schematic | 8-Bit Inverter Schematic | Symbol |

|  |  |

8-Bit OR Gate:| OR Schematic | 8-Bit OR Schematic | Symbol |

|  |  |

-Me providing a few simulation examples using these gates.

| Gate Simulation Schematic |

|

| NOR GATE |  |

NAND

GATE |  |

AND

GATE |  |

Inverter

GATE |  |

OR

GATE |  |

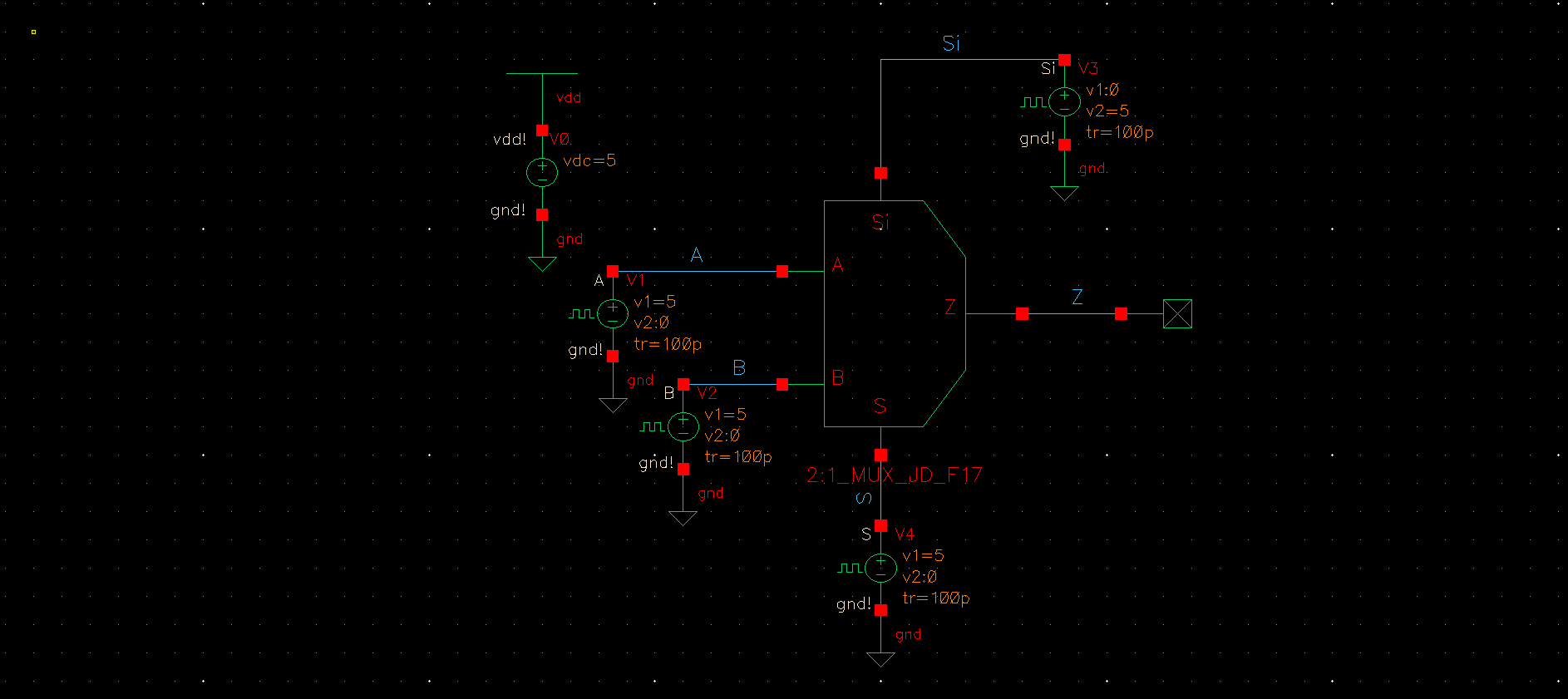

-Schematic of a 2-to-1 DEMUX/MUX (and the symbol)

| Schematic | Symbol |

|  |

| Schematic to simulate | Simulation |

|  |

-Including

an inverter in the design, so the cell only needs one select input, S

(the complement, Si, is generated using an inverter).

| Schematic with the included inverter | Symbol with one select input, S |

|  |

| Simulation Schematic | Simulation Results |

|  |

The inverter has no effect on the results, so it does not matter if its attached or not.

| 2-to-1 Demux Schematic | Simulation |

|  |

-An 8-bit wide word 2-to-1 DEMUX/MUX schematic and symbol

| Schematic | Symbol |

|  |

| Schematic Simulation | Simulation Results |

|  |

-A schematic of the full-adder seen in Fig. 12.20 using 6u/0.6u devices (both PMOS and NMOS)

| Schematic | Symbol | Layout | Extracted |

|  |  |  |

| Simulation Schematic | Results |

|  |

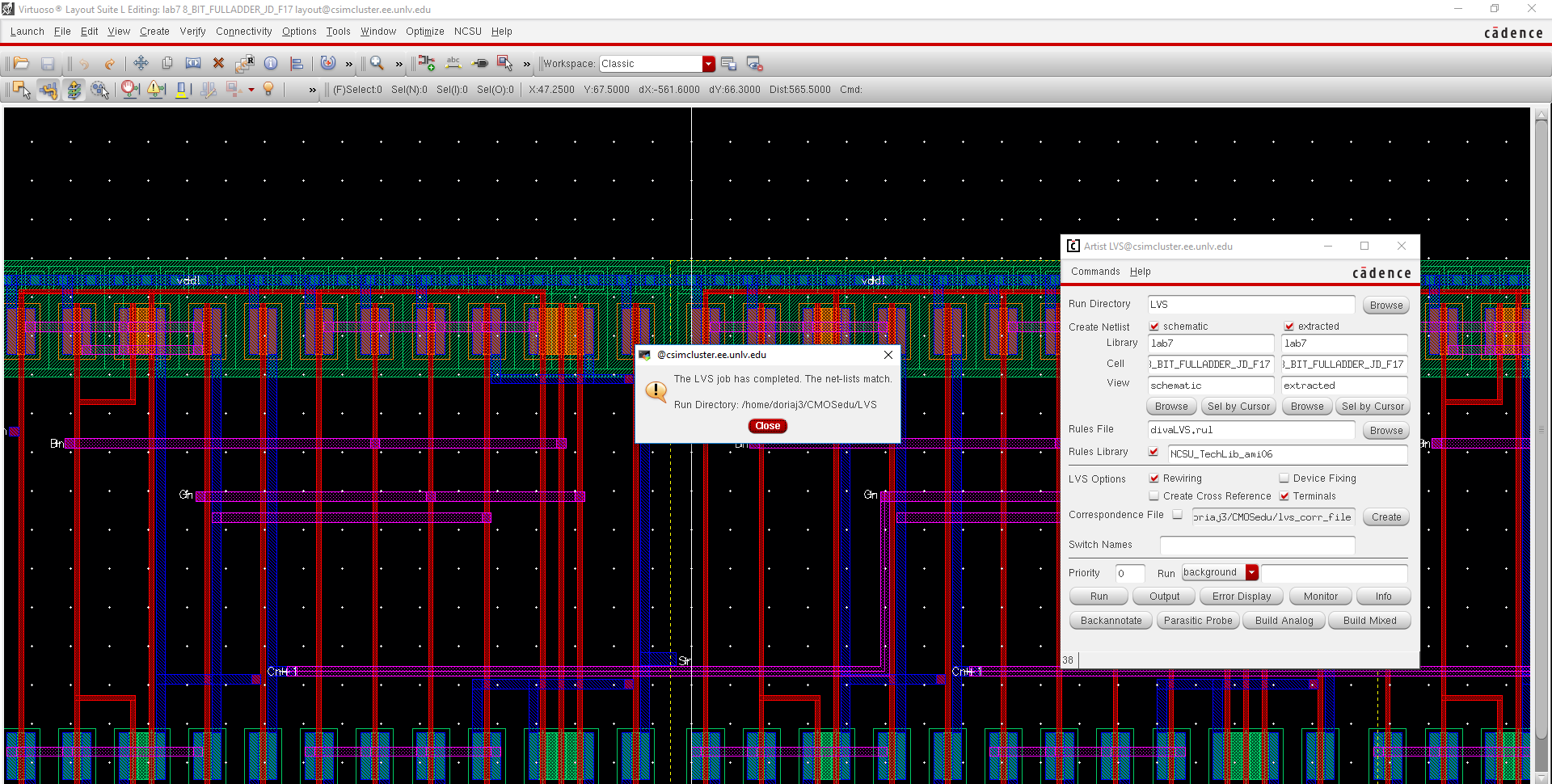

| LVS | DRC |

|  |

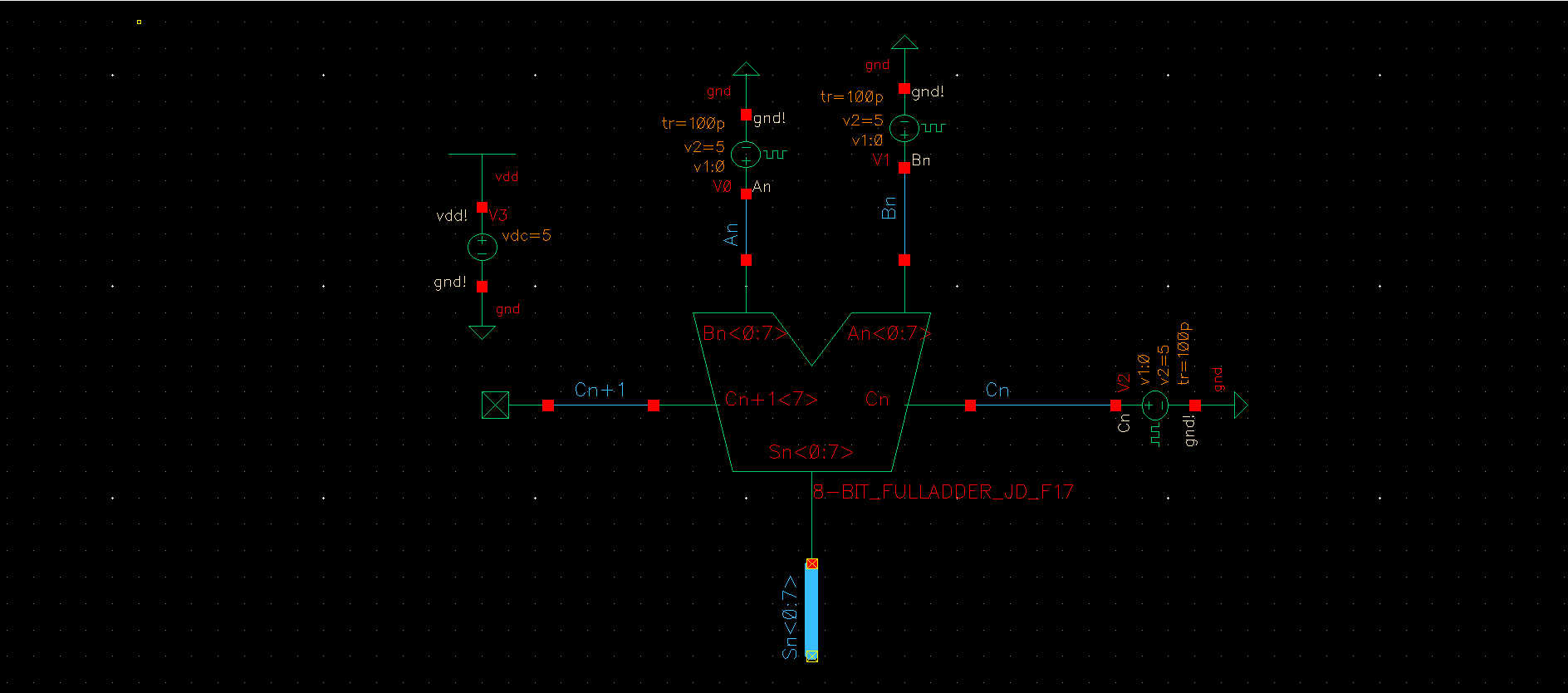

-Lay out this 8-bit adder cell

| Schematic | Symbol |

|  |

| Layout | Extracted |

|  |

| Schematic simulation | Results |

|  |

LVS:

DRC:

-Backing up files

Lab 7 Files Download

Return to not my lab 7