Lab Project - EE 421L

The goal of the project is design a even parity checking circuit that outputs a 1 when the total number of input bits that are '1' are even, and outputs a 0 if they are odd.

The circuit will have 9 input bits (8-bits of data and 1-bit parity) and 1 output bit.

The Schematic

The final even parity checking circuit is composed of XOR and XNOR gates, hence I will cover these two logic gates beforehand.

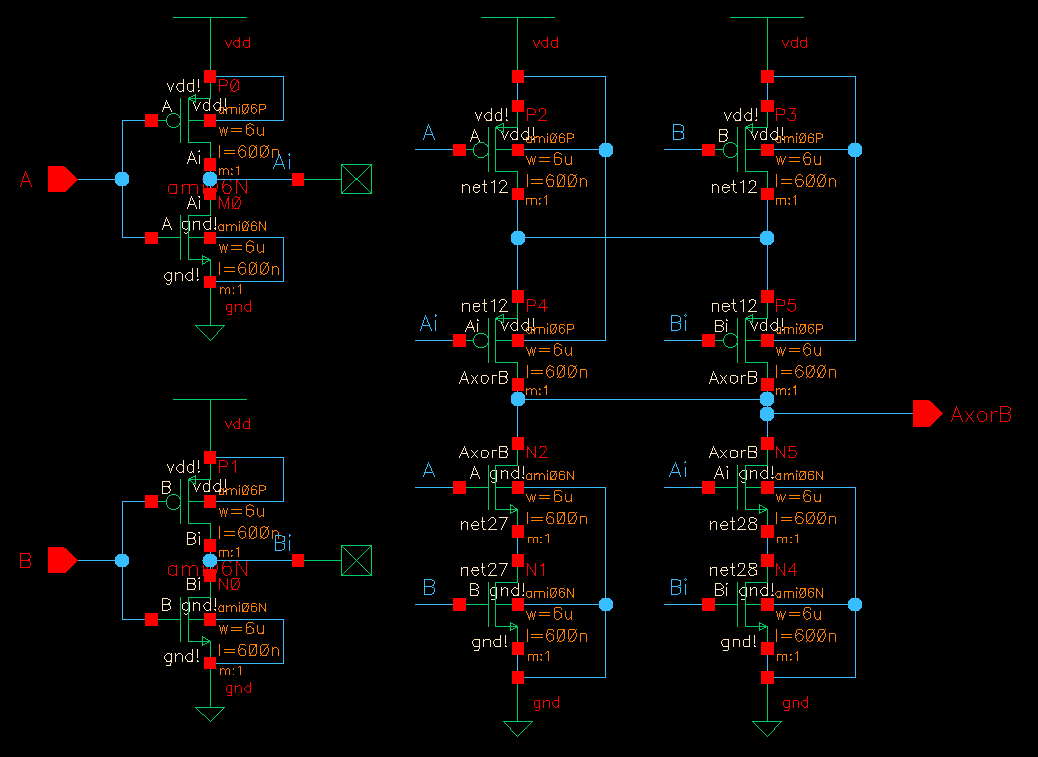

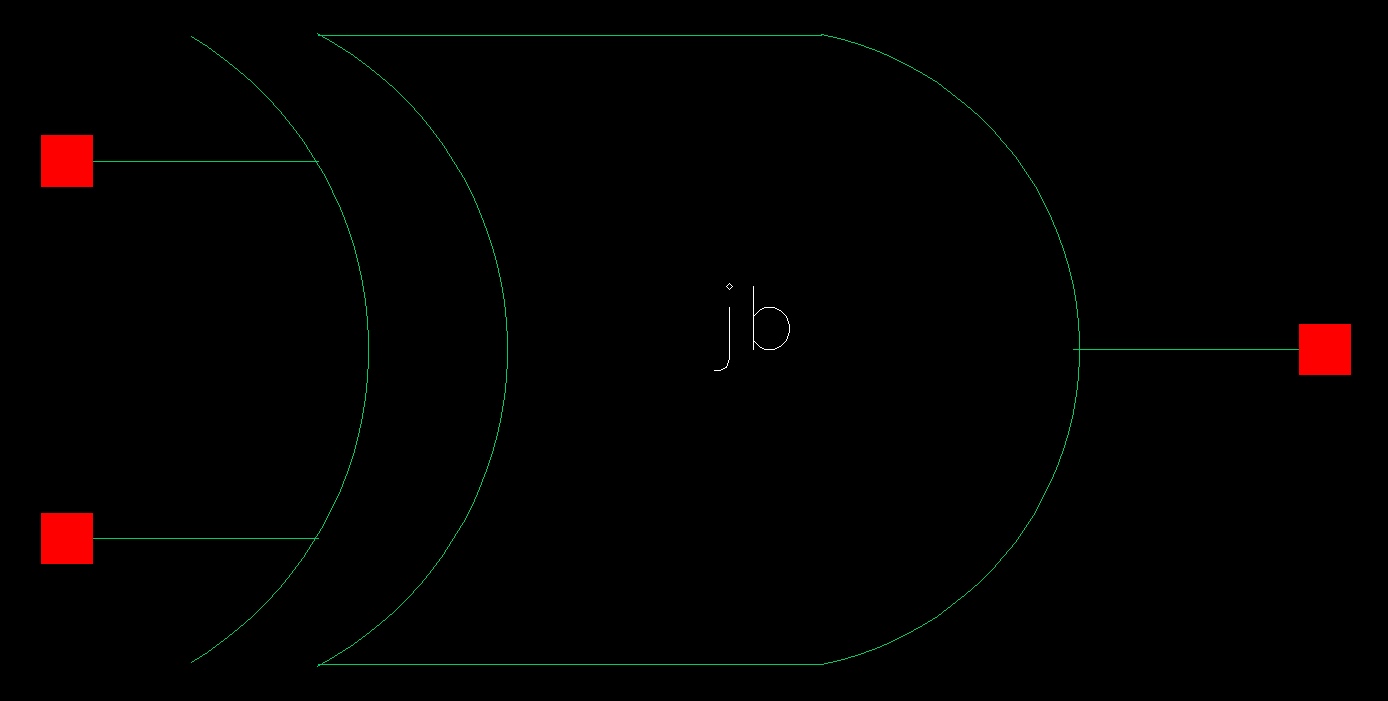

Designing a 2-input XOR gate

First I created a schematic and a symbol for the commonly used XOR gate. Below are the images of the XOR gate.

| Schematic | Symbol |

|

|

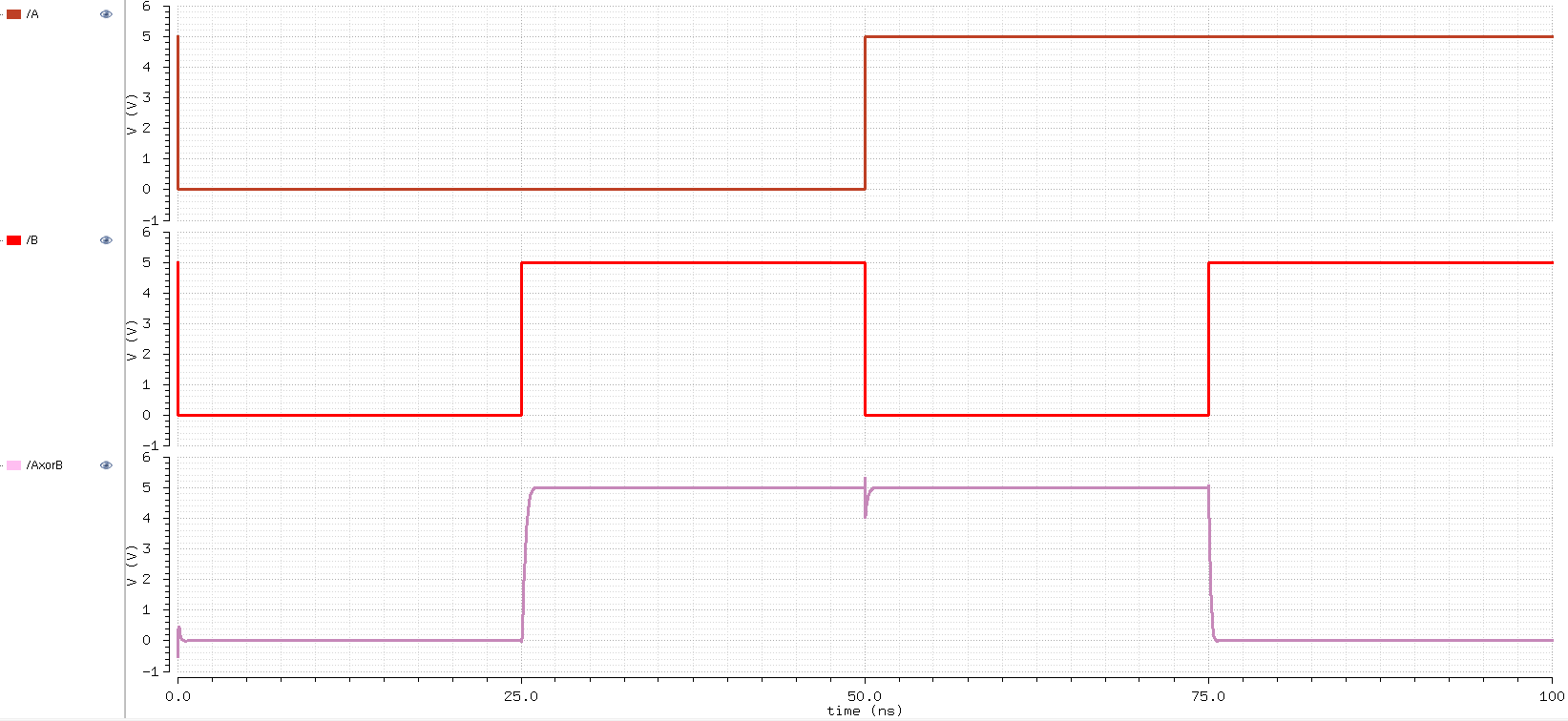

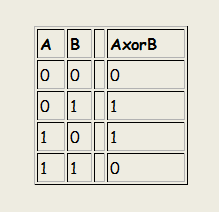

I simulated the XOR gate to ensure that the output matched the truth table of a 2-input XOR gate.

The output was a 1 when the inputs differed, and a 0 when the inputs were the same.

| Spectre Simulation Result | Truth Table |

|

|

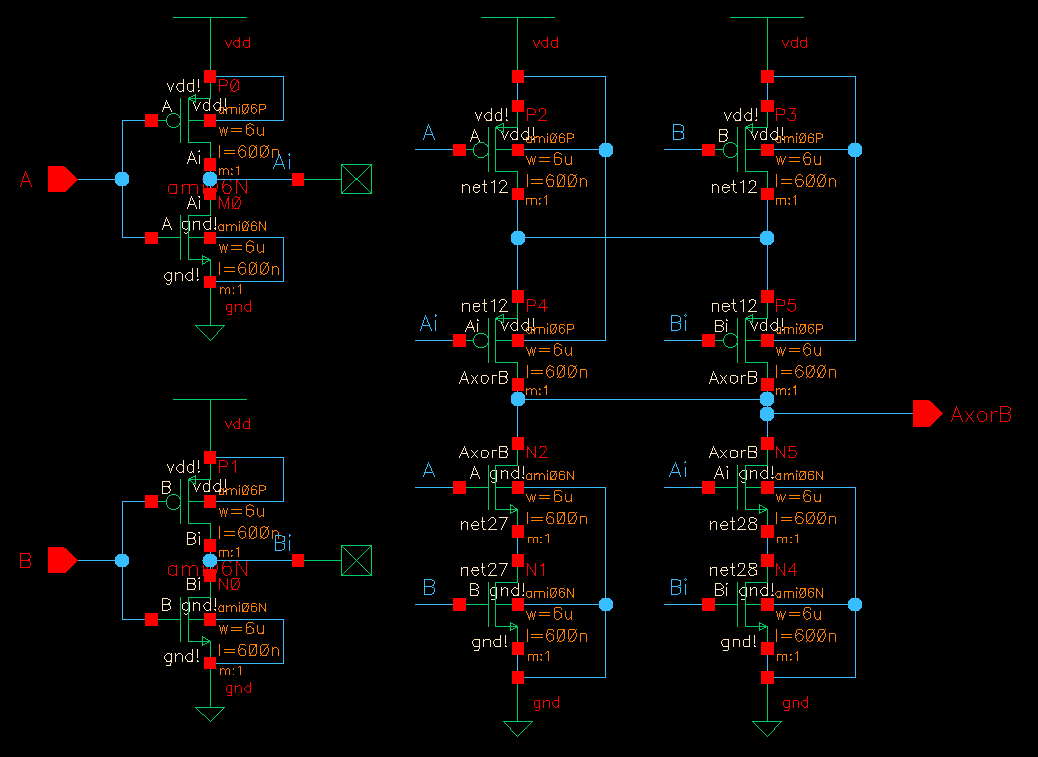

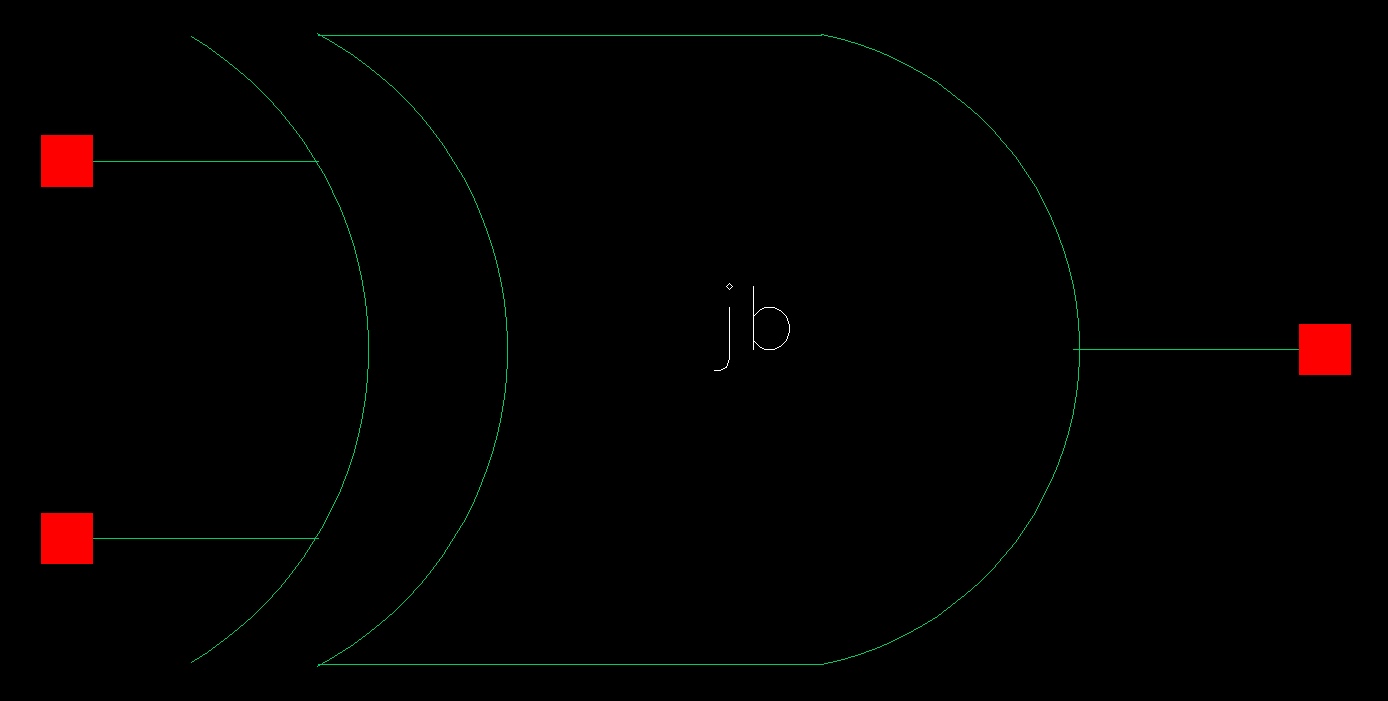

Designing a 2-input XNOR gate

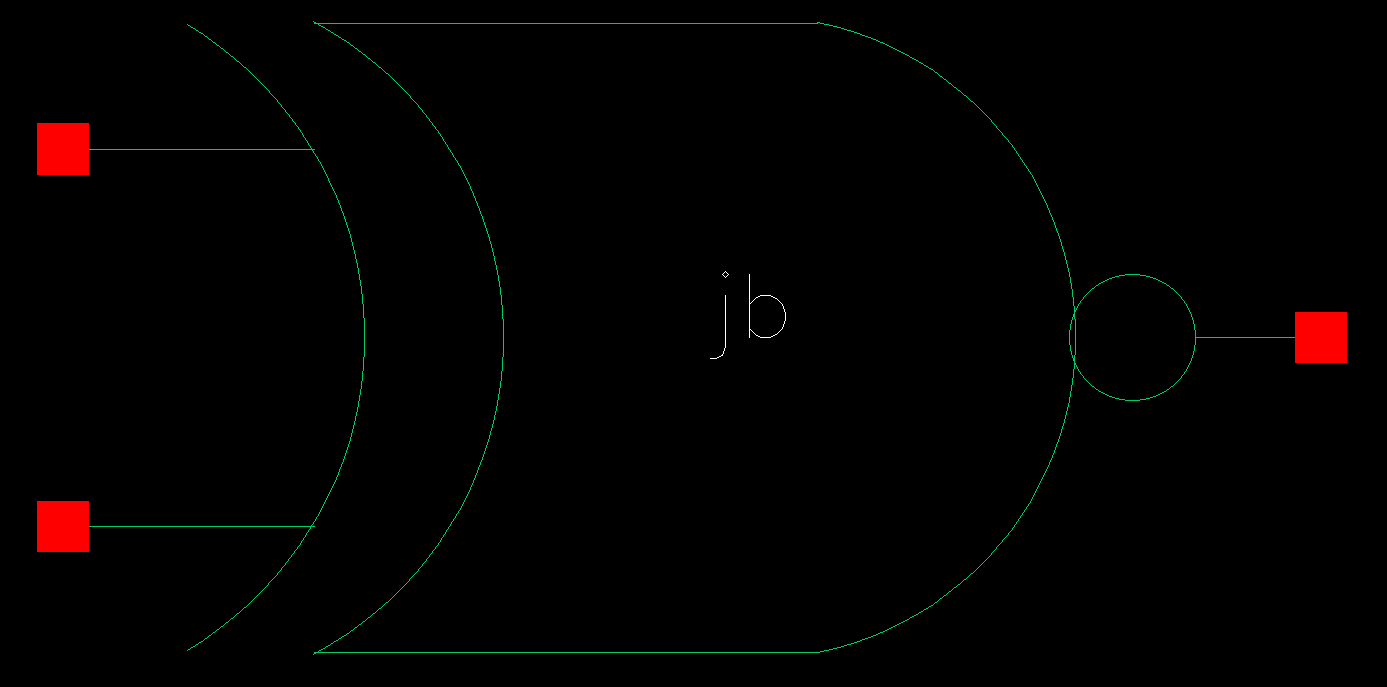

Likwise, I created a schematic and a symbol for the commonly used XNOR gate by attaching an inverter to the output of the XOR gate. Below are the images of the XNOR gate.

| Schematic | Symbol |

|

|

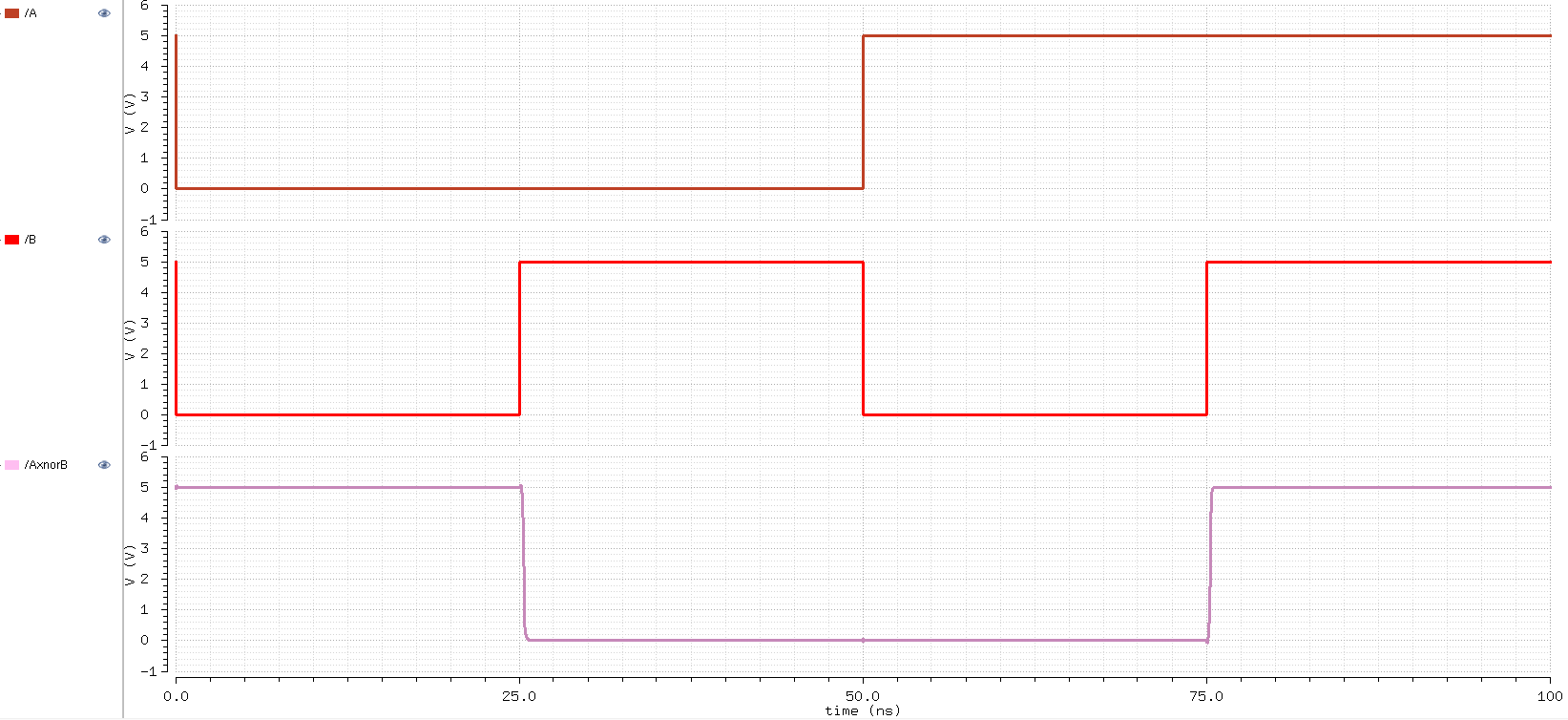

I simulated the XNOR gate to ensure that the output matched the truth table of a 2-input XNOR gate.

The output reflected the inverted signal of a XOR gate; the output was a 1 when the inputs were the same, and a 0 when the inputs were different.

| Spectre Simulation Result | Truth Table |

|

|

To drive loads off-chip, 2 inverters with increasing sizes were used to amplify the output signal before connecting to a pad.

| Schematic | Symbol |

Even Parity Checker Schematic

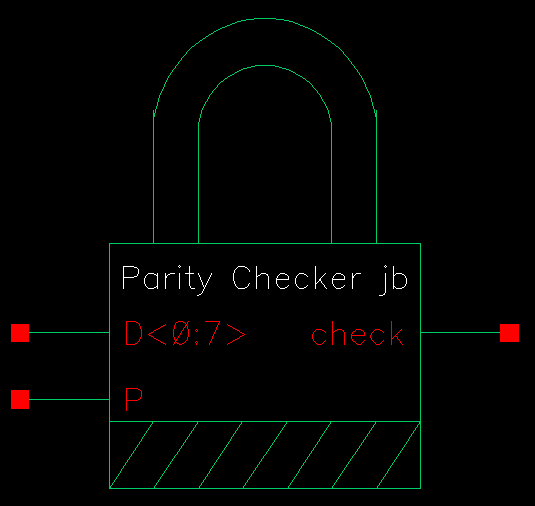

| Schematic | Symbol |

|

|

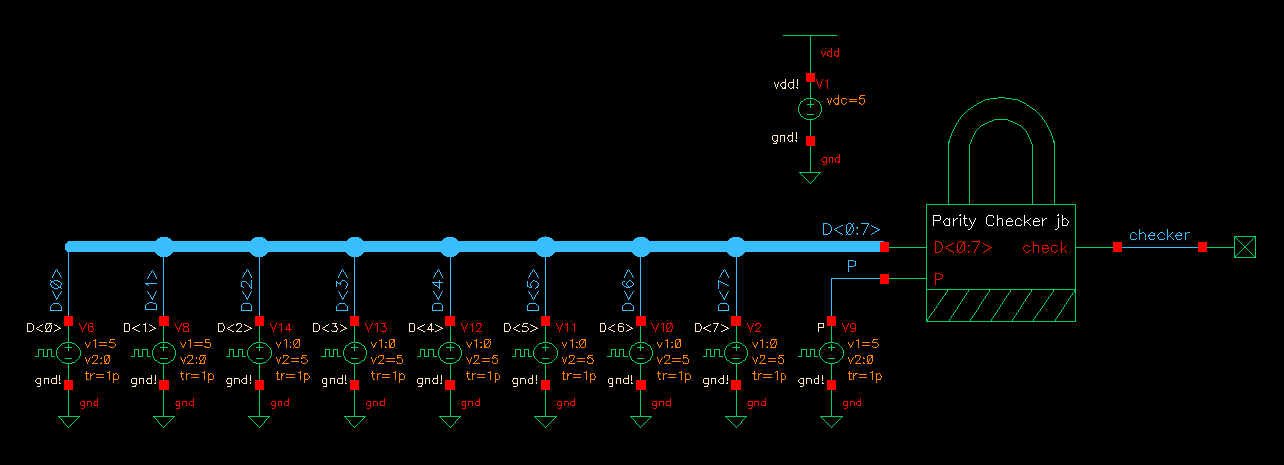

Even Parity Checker Simulations

I simulated the parity checker from above to verify that the parity checker functioned as expected.

I chose to vary only 3 input bits (D<0:1> and P) because the concept of XORing 2 input bits was the same throughout.

| Simulation Schematic |

|

* The veritcal lines correspond to different inputs that were tested and can be referenced in the table below

| Spectre Simulation Result |

|

| P (parity bit) | D<0:7> | check | ||

| V1 | 0 | 0 0 1 1 1 1 1 1 | 1 | |

| V2 | 1 | 0 0 1 1 1 1 1 1 | 0 | |

| V3 | 0 | 0 1 1 1 1 1 1 1 | 0 | |

| V4 | 1 | 0 1 1 1 1 1 1 1 | 1 | |

| V5 | 0 | 1 0 1 1 1 1 1 1 | 0 | |

| V6 | 1 | 1 0 1 1 1 1 1 1 | 1 | |

| V7 | 0 | 1 1 1 1 1 1 1 1 | 1 | |

| V8 | 1 | 1 1 1 1 1 1 1 1 | 0 |

*Click on the images to enlarge the layout and extracted views

| Layout | DRC successful | Extracted | LVS successful |

| Layout | DRC successful | Extracted | LVS successful |

| Layout | Close-up view of Layout | DRC successful |

| Extracted | Close-up view of Extracted | LVS successful |

| Layout | Close-up view of Layout | DRC successful |

| Extracted | Close-up view of Extracted | LVS successful |

I simulated the parity checker layout from above to verify that the parity checker functioned as expected.

This time around, I varied all the input bits to ensure the workings of all the gates.

The simulation netlist shows proof of simulating the extracted portion of the design.

* The veritcal lines correspond to different inputs that were tested and can be referenced in the table below

| Spectre Extracted Simulation Result | Simulation Netlist |

| P (parity bit) | D<0:7> | check | ||

| V1 | 0 | 0 0 1 1 0 1 0 1 | 1 | |

| V2 | 1 | 0 0 0 1 1 1 0 0 | 1 | |

| V3 | 0 | 0 1 1 0 0 1 1 1 | 0 | |

| V4 | 1 | 0 1 0 0 1 1 1 0 | 0 | |

| V5 | 0 | 1 0 1 1 0 0 0 1 | 1 | |

| V6 | 1 | 1 0 0 1 1 0 0 0 | 1 | |

| V7 | 0 | 1 1 1 0 0 0 1 1 | 0 | |

| V8 | 1 | 1 1 0 0 1 0 1 0 | 0 |