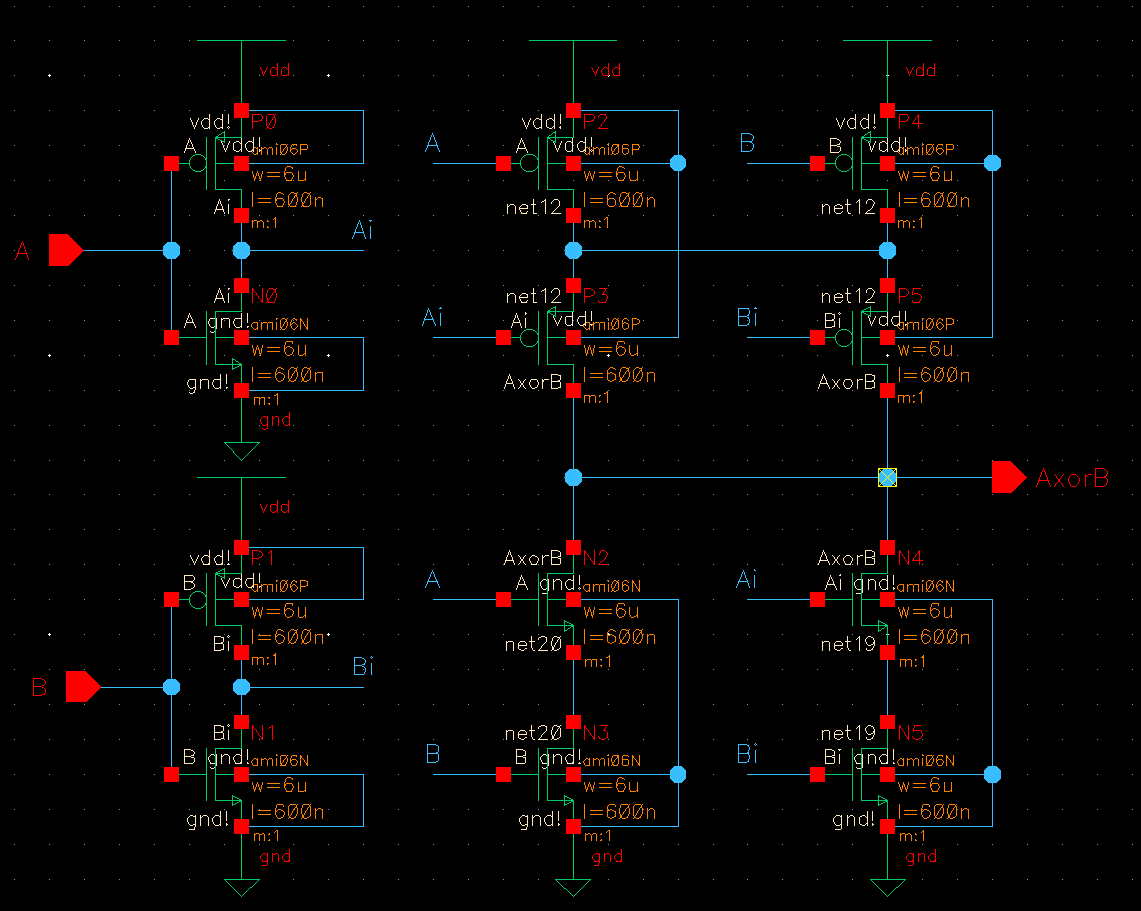

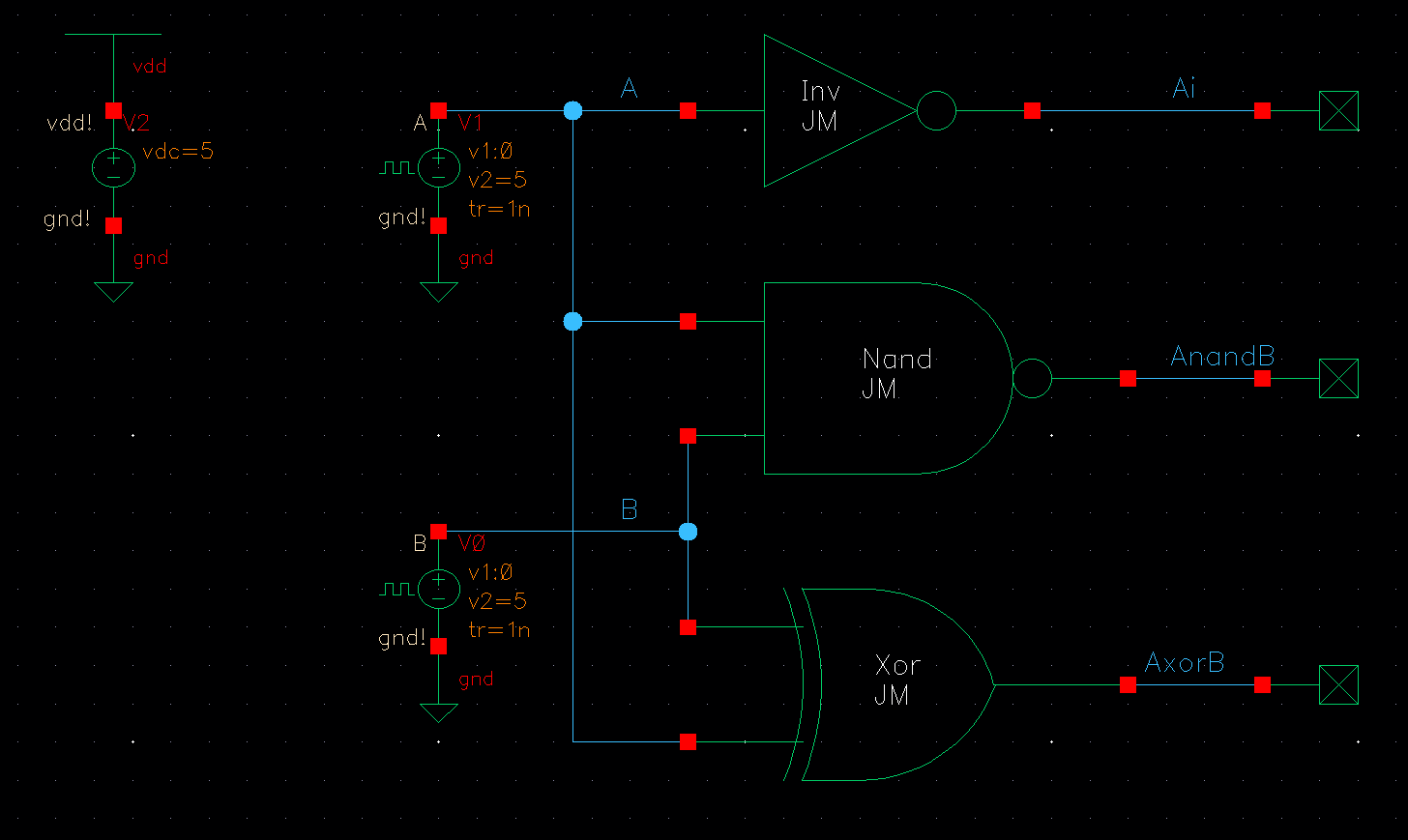

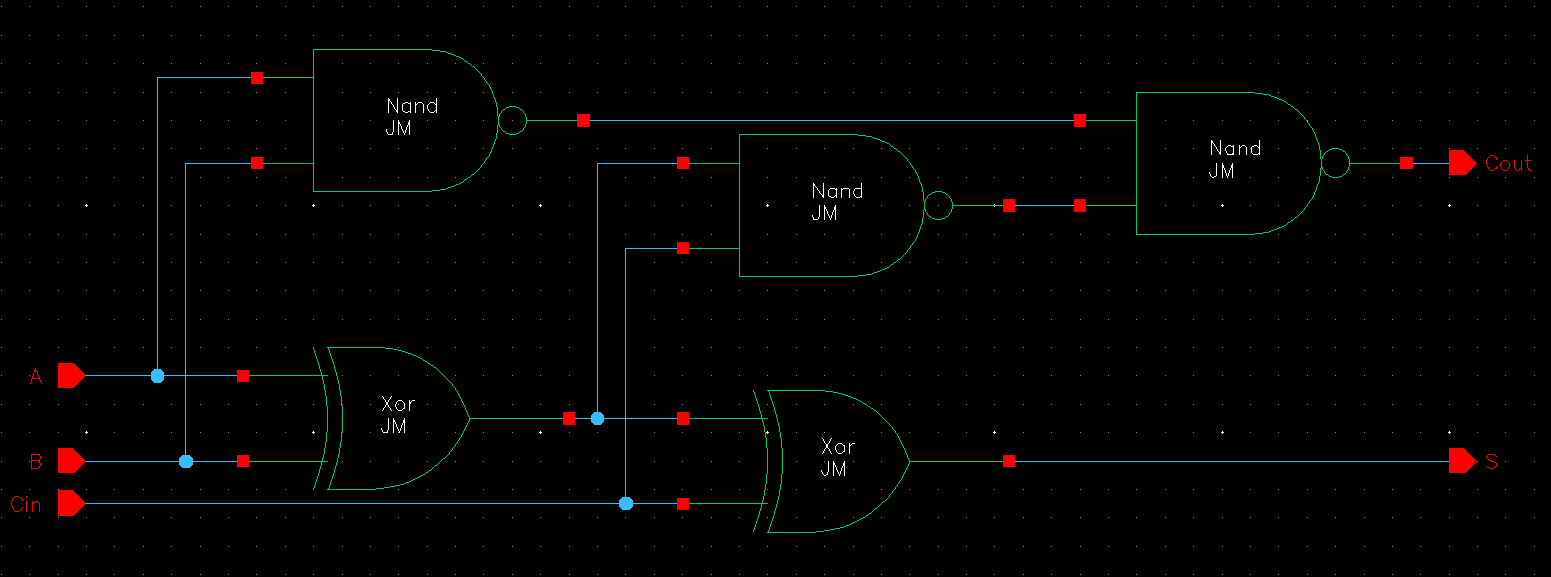

Schematic

|

|

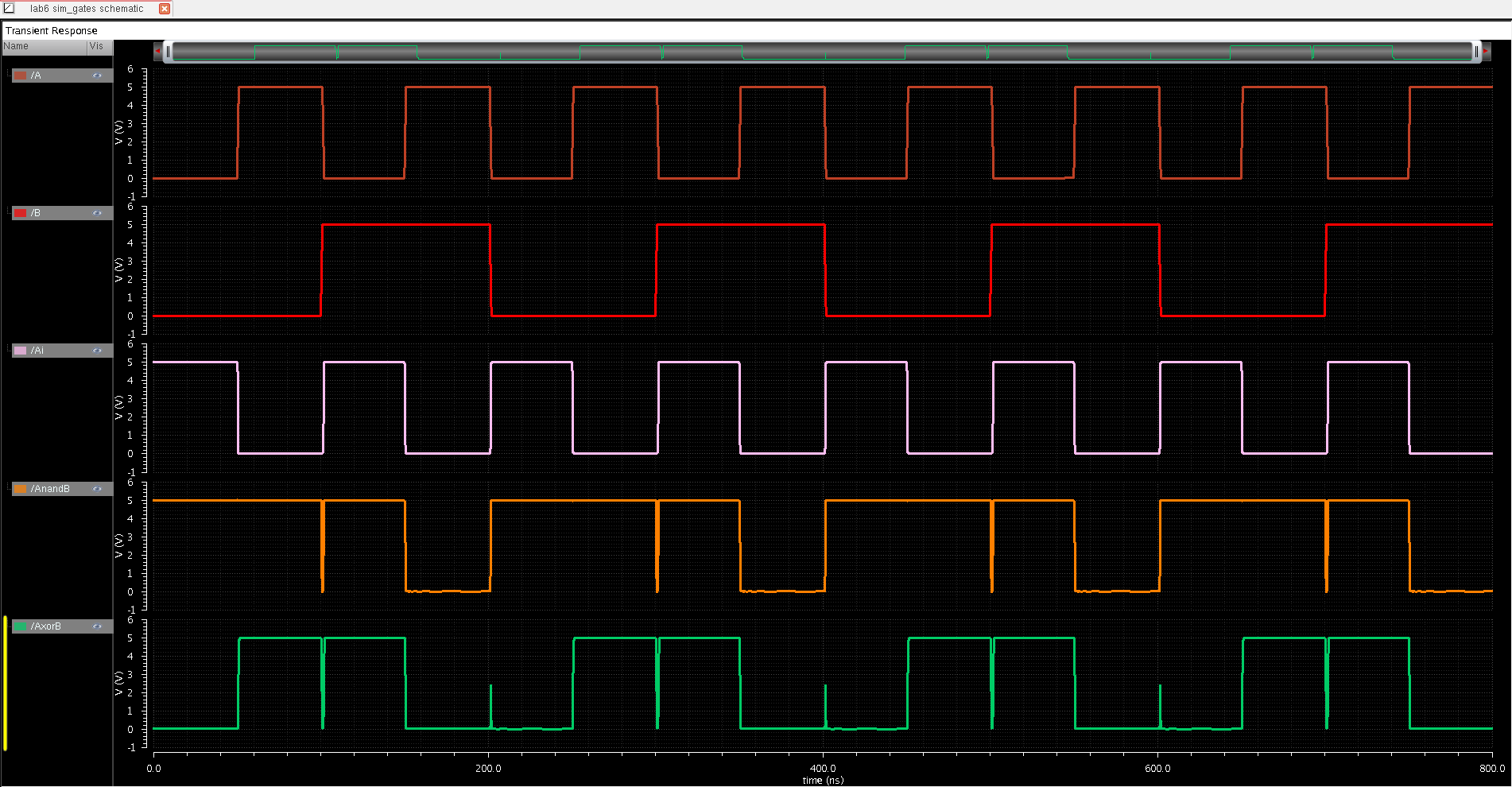

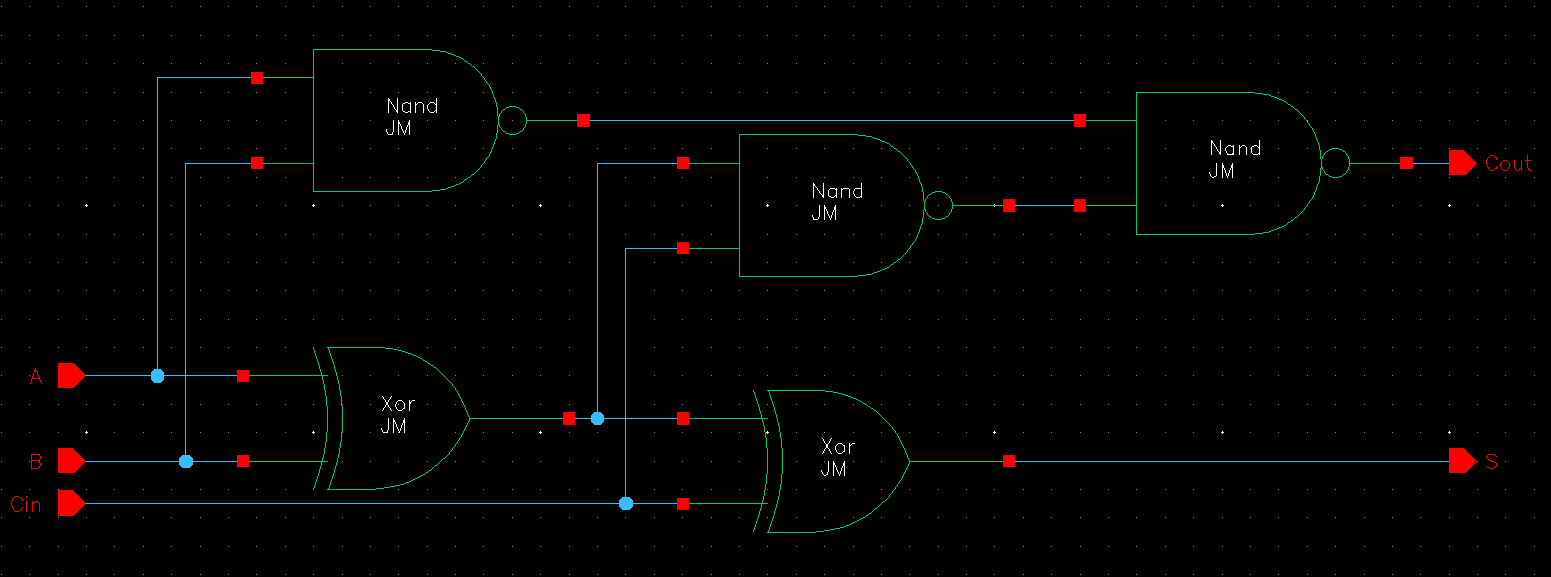

- After

all the gates have been simulated and verified

outputting correctly, I began drafting the Full Adder in schematic

view. This was based on the Full Adder schematic example. The Full

Adder is a common logic design. This specific Full Adder is a 1-bit

Full Adder. It has three inputs and two outputs. The inputs are A, B

and Carry In and the outputs are Sum and Carry Out. This Full Adder

takes in three 1-Bit inputs and add them together producing a sum and

that sum is split between an S and Cout. The gates that are used are

the ones I drafted and simulated earlier in this lab.

|

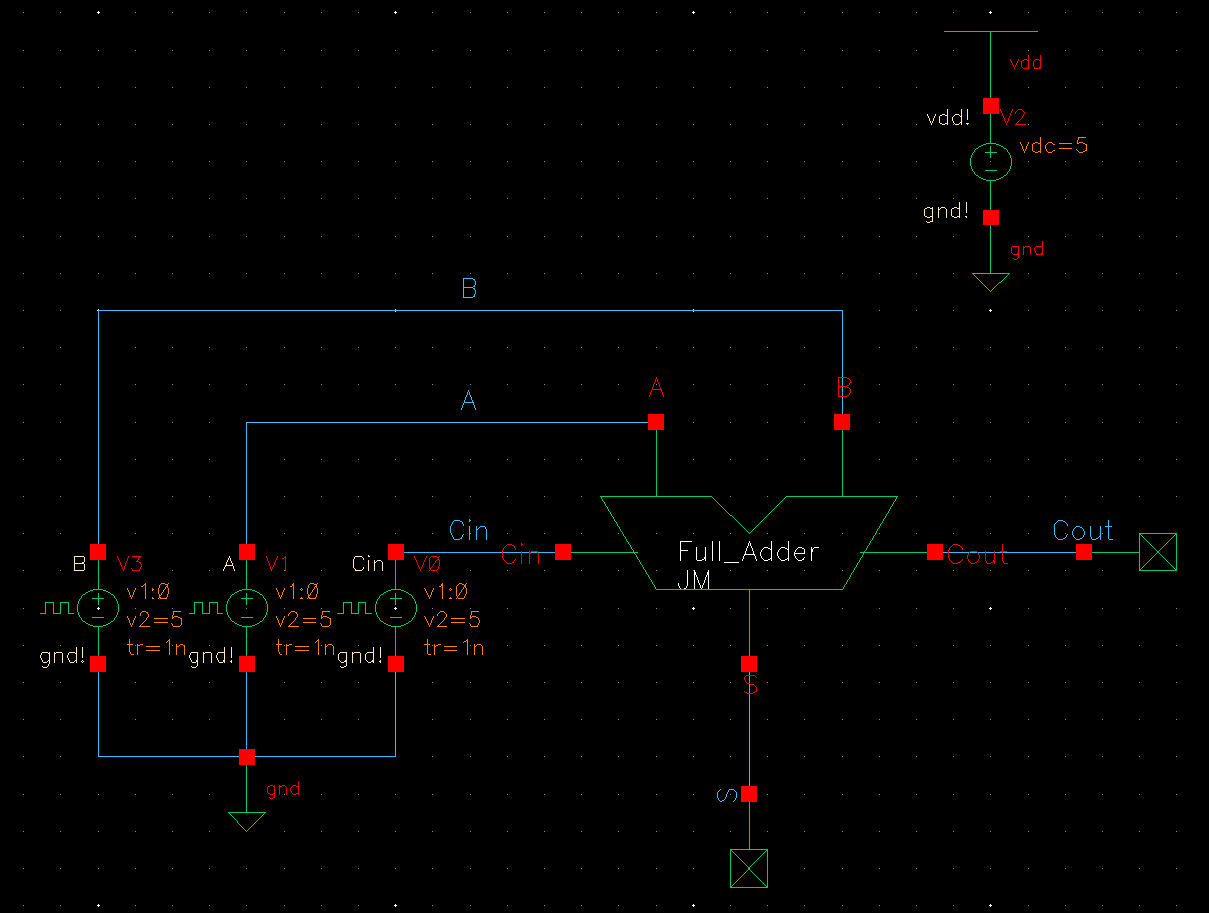

Symbol

|

|

- The next step, was to create a symbol for simulations later on and the symbol to the left is the common 1-bit Full Adder symbol.

|

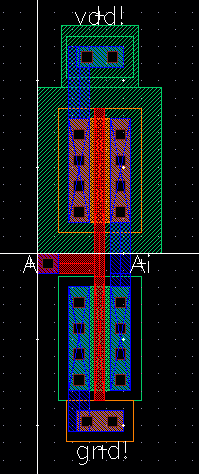

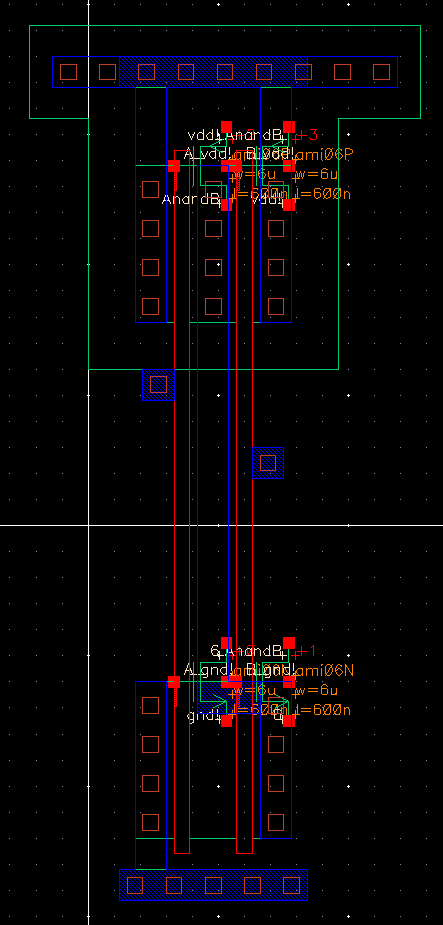

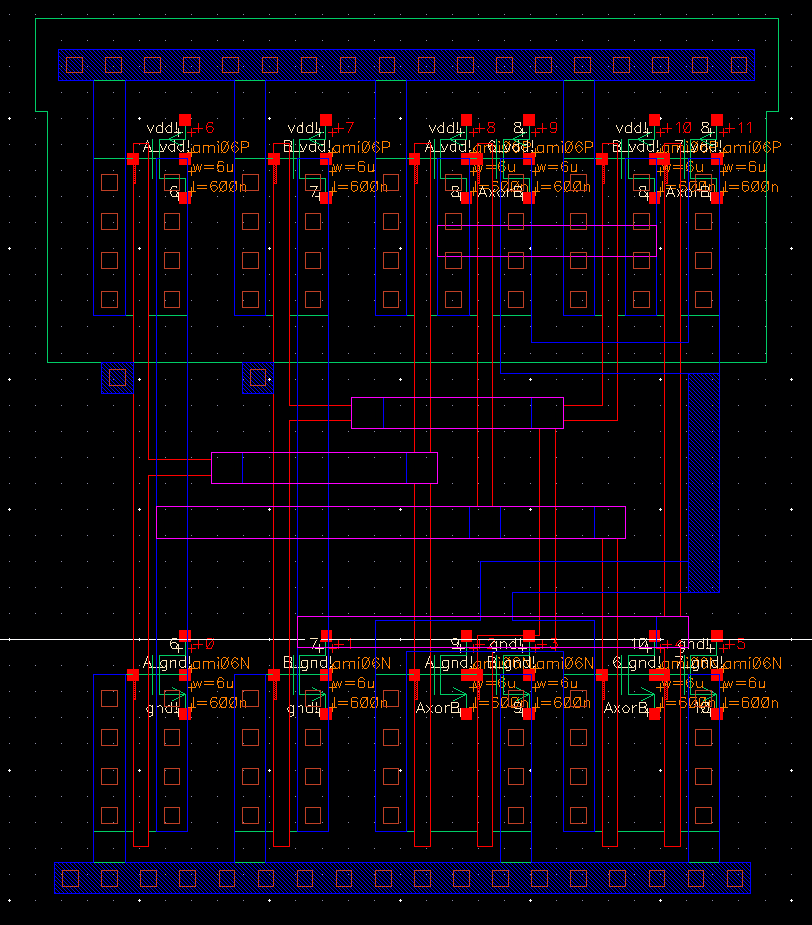

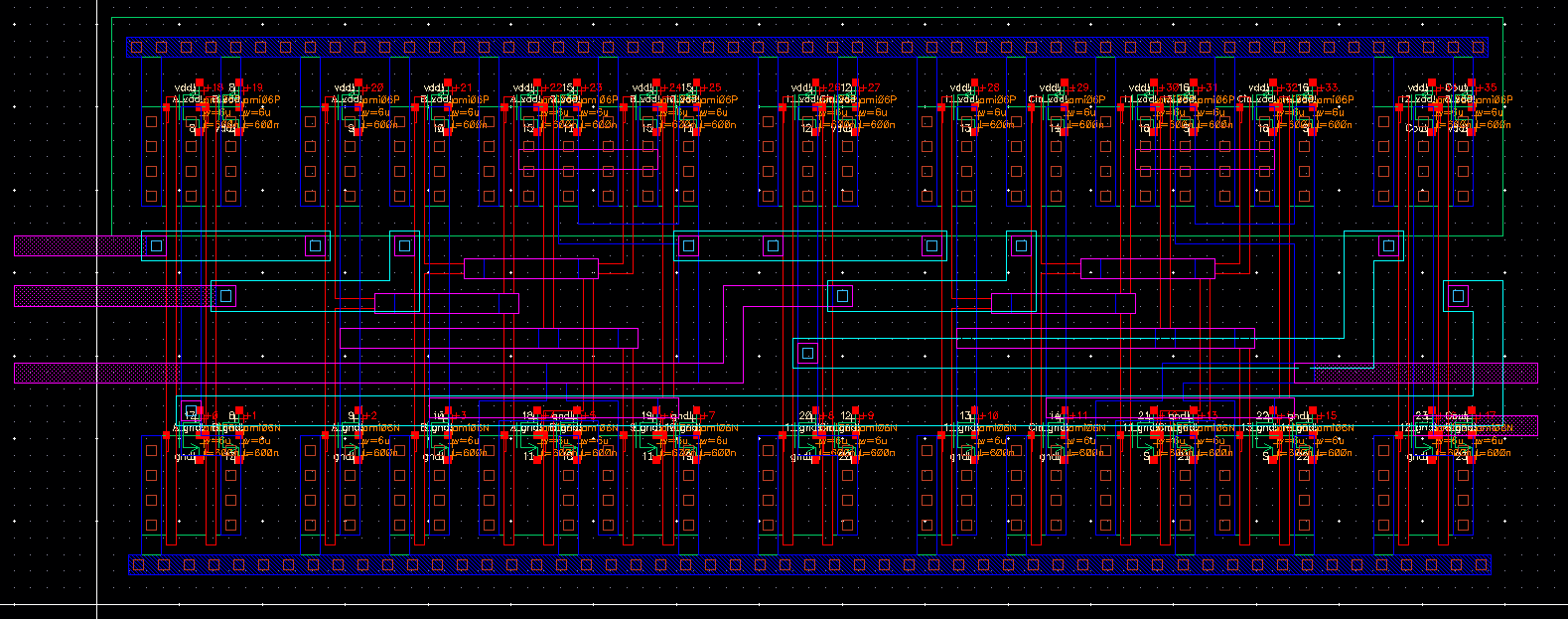

Layout

|

|

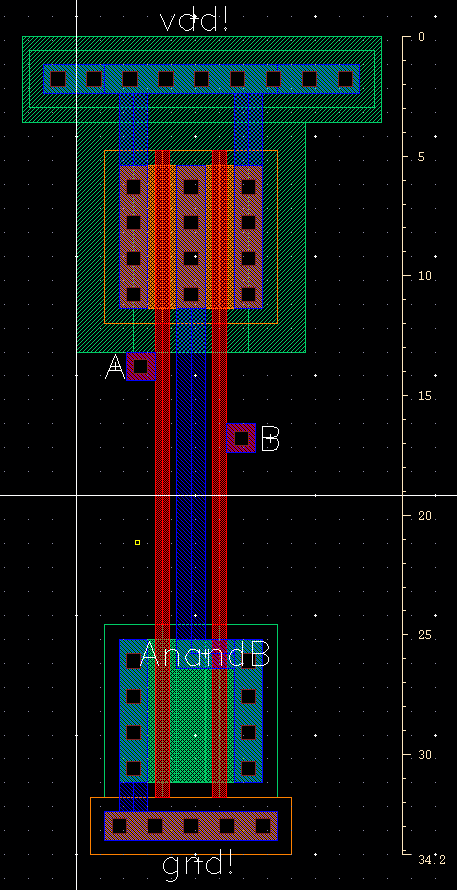

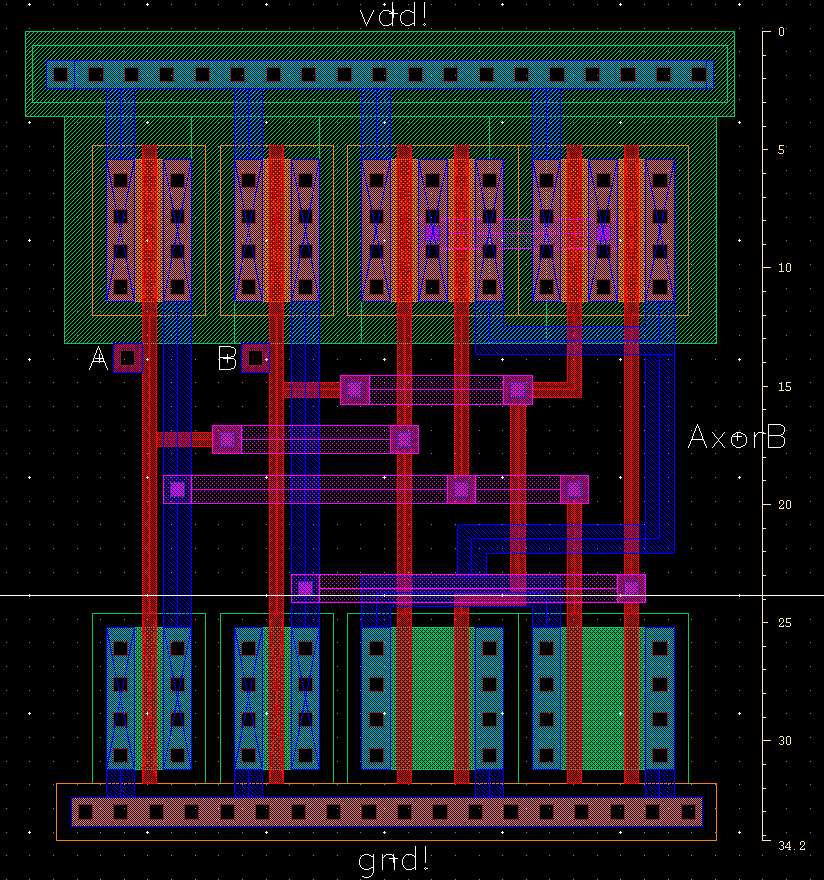

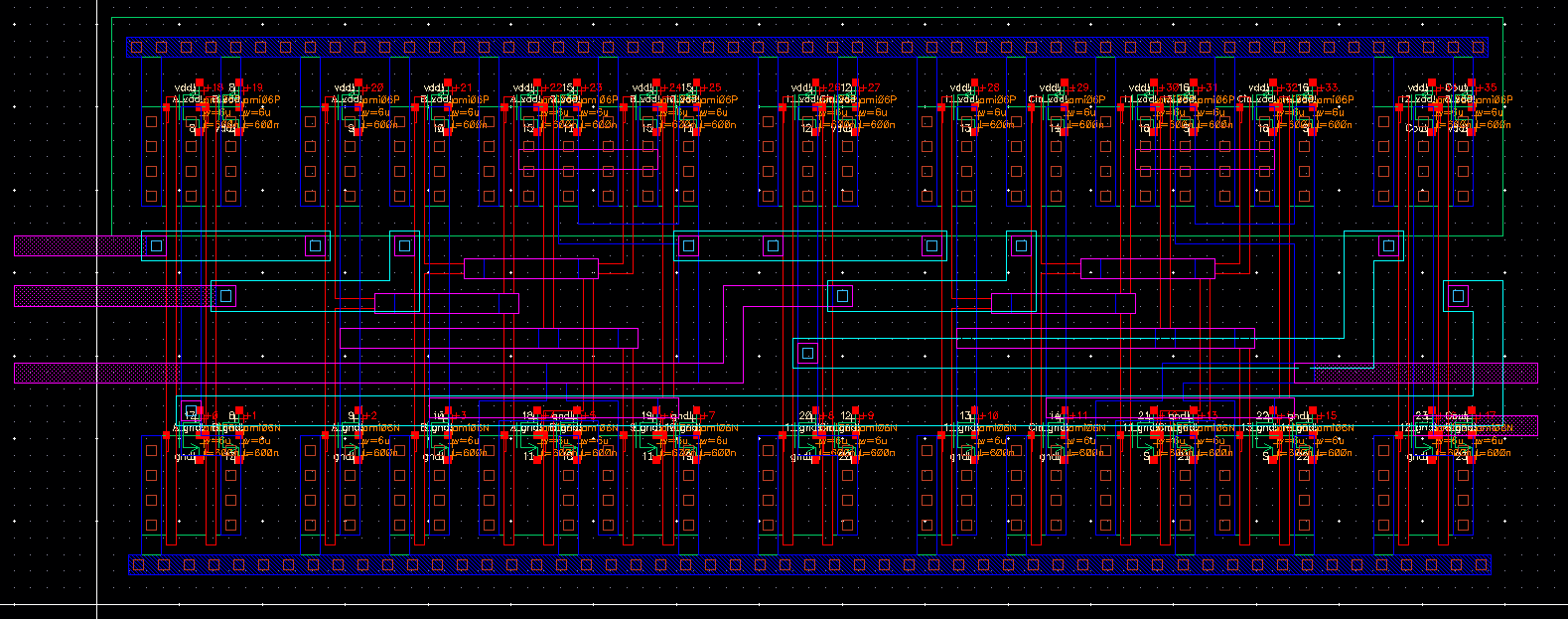

- Next,

I began laying out the Full Adder. I used the layouts of the of

the gates previously made and everything lined up thanks to the ruler

measurements made earlier. I connected all the gates according to the

schematic made earlier. With this designed, I tried to keep all the

wires in between all the PMOS's and NMOS's. All of the metal1 wires

connected the sources and draines that needed to be connected, metal2

connected all the gates and metal 3 connected all the logic gates

together. After everything was connected I flattened the logic gates in

order to have one long row of ntap and ptap for the vdd and ground. I

also added all the pins needed; vdd!, gnd!, A, B, Cin, S, Cout.The

white outlines in this final layout show the individual logic gates for

clarity.

|

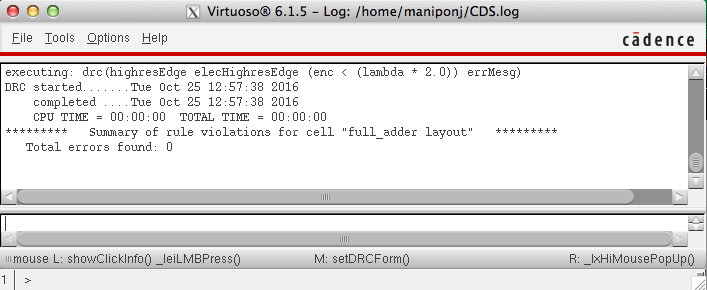

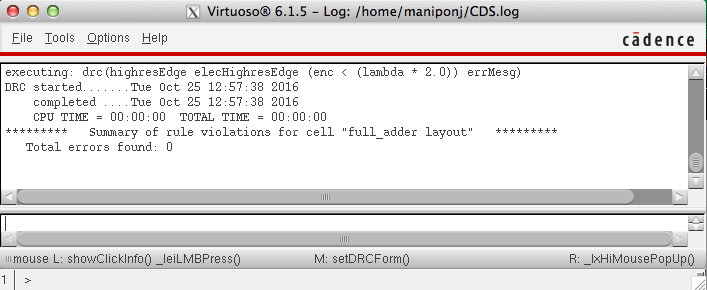

DRC

|

|

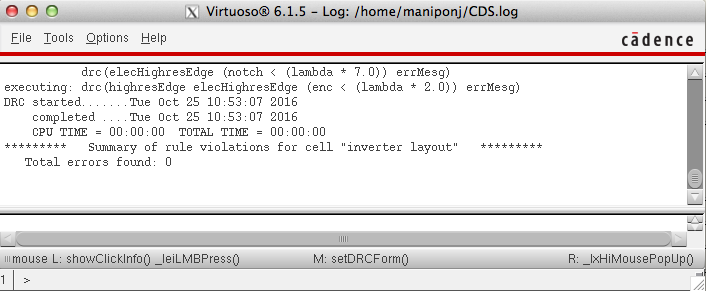

- I ran the DRC to make sure all of the cells were not violating any rules and there were no errors

|

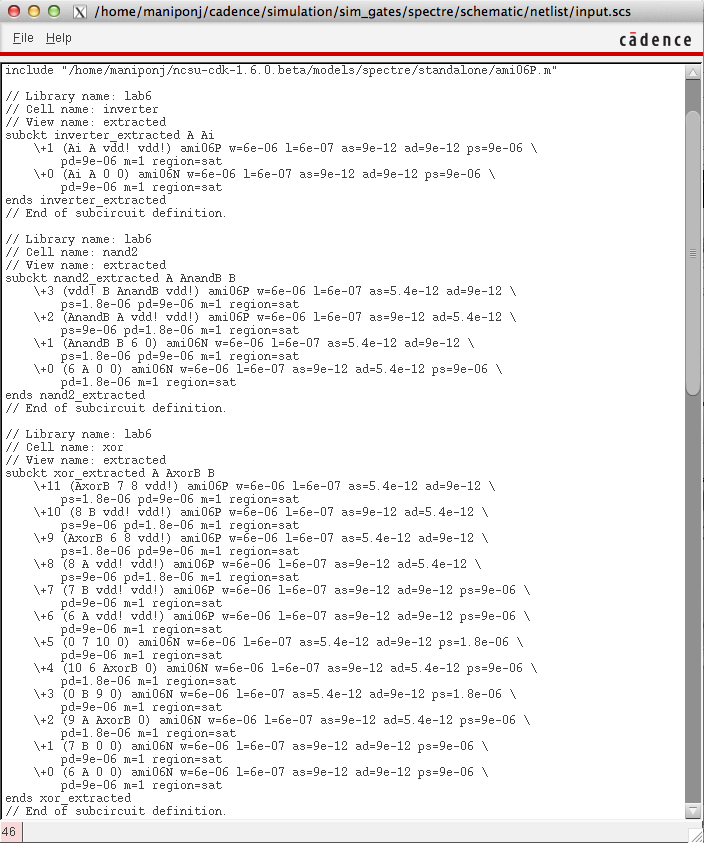

Extracted

|

|

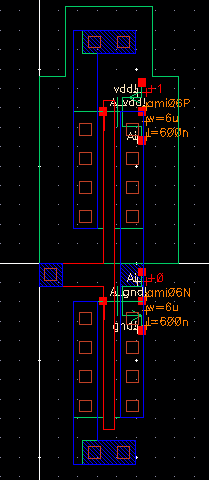

- After DRC, I extracted the layout so I can run the LVS

|

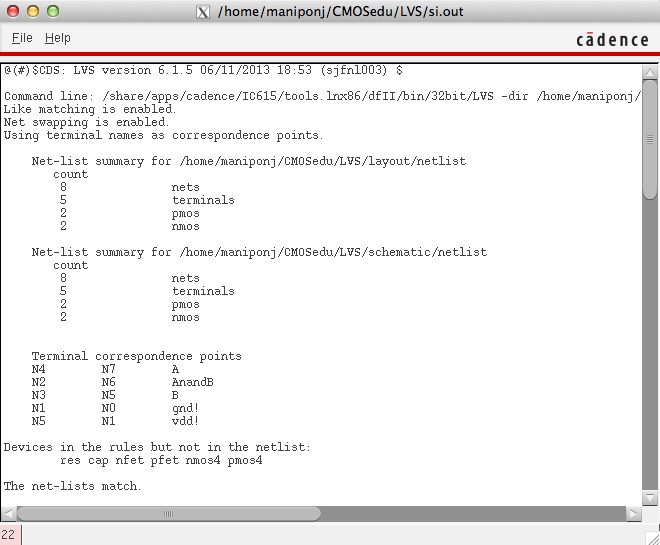

LVS

|

|

- I ran the LVS and netlists matched.

|